# OpenSPARC<sup>™</sup> T1 Processor External Interface Specification

Sun Microsystems, Inc. www.sun.com

Part No. 819-5014-10 March 2006, Revision A

Submit comments about this document at: <a href="http://www.sun.com/hwdocs/feedback">http://www.sun.com/hwdocs/feedback</a>

Copyright 2006 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, AnswerBook2, docs.sun.com, Sun4U, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2005 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, Californie 95054, Etats-Unis. Tous droits réservés.

Sun Microsystems, Inc. a les droits de propriété intellectuels relatants à la technologie qui est décrit dans ce document. En particulier, et sans la limitation, ces droits de propriété intellectuels peuvent inclure un ou plus des brevets américains énumérés à http://www.sun.com/patents et un ou les brevets plus supplémentaires ou les applications de brevet en attente dans les Etats-Unis et dans les autres pays.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a.

Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit pourront être dérivées des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, AnswerBook2, docs.sun.com, Sun4U, et Solaris sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une license non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciées de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ÉTAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFAÇON.

# Contents

#### Preface xi

| 1. | J-Bus              | : Overview and Philosophy 1–1        |                                         |      |

|----|--------------------|--------------------------------------|-----------------------------------------|------|

|    | 1.1                | Introd                               | uction 1–1                              |      |

|    | 1.2                | Goals                                | 1–3                                     |      |

|    | 1.3                | Signal List 1–4                      |                                         |      |

|    | 1.4                | Address and Data Flow Control 1-6    |                                         |      |

|    |                    | 1.4.1                                | Address OK 1–6                          |      |

|    |                    | 1.4.2                                | Data OK 1–7                             |      |

|    |                    | 1.4.3                                | Interrupt Flow Control 1–7              |      |

|    | 1.5                | Other Caching Issues 1–8             |                                         |      |

|    |                    | 1.5.1                                | I/O Data Cache 1–8                      |      |

|    |                    | 1.5.2                                | No-Snoop Pages 1–8                      |      |

|    |                    | 1.5.3                                | Encaching No-Snoop Data 1–9             |      |

|    | 1.6 Interrupts 1–9 |                                      |                                         |      |

|    | 1.7                | OpenSPARC T1 PCI Ordering Rules 1–10 |                                         |      |

|    |                    | 1.7.1                                | DMA Write Ordering 1–10                 |      |

|    |                    | 1.7.2                                | PIO Read Returns Compared to DMA Writes | 1–10 |

|    |                    |                                      |                                         |      |

1.7.3 Interrupts Compared to DMA Writes 1–11

- 1.7.4 DMA Reads Compared to DMA Writes Address Consistency 1– 11

- 1.7.5 PIO Request Ordering 1–11

- 1.7.6 PIO Writes Compared to DMA Read Returns Not Supported 1– 11

- 1.7.7 DMA Reads No Ordering Rules 1–12

- 1.8 Data Transfer Detail 1–12

- 1.8.1 DOK Flow Control for Writes 1–13

- 1.8.2 Read Data Flow Control 1–13

- 1.8.3 Memory Controller Reordering 1–13

- 1.9 Posted Coherency 1–13

- 1.9.1 J\_PACK Snoop Results 1–14

- 1.10 DTL Mode Programming 1–15

- 1.11 Error Code Correction and Parity 1–15

- 1.12 J\_PAR: Parity for J\_REQ\_L and J\_PACK0-6 1–16

- 1.13 Fatal Errors 1–18

#### 2. Interconnection Model 2–1

- 2.1 Overview 2–1

- 2.2 Data Flow 2–3

- 2.2.1 Read/Write 2-3

- 2.2.2 Noncached Slave Read Sequence 2–3

- 2.2.3 Noncached Slave Write Sequence 2–4

- 2.3 Flow Control Model 2–4

- 2.4 J-Bus Port Model 2–5

- 2.4.1 Master Interface 2–5

#### 3. J-Bus Transaction Set 3–1

- 3.1 Transaction Set Requirements 3–1

- 3.2 Transaction Set Terminology 3–2

- 3.3 Transaction Set Summary 3–3

- 3.4 Memory Transactions 3–4

- 3.4.1 ReadToShare 3–4

- 3.4.2 ReadToDiscard 3-5

- 3.4.3 WriteInvalidate 3-5

- 3.4.4 WriteMerge 3–6

- 3.5 Noncached Data Transactions 3–7

- 3.5.1 NonCachedRead 3–7

- 3.5.2 NonCachedBlockRead 3-8

- 3.5.3 NonCachedWrite 3-8

- 3.5.4 NonCachedWriteCompressible 3–10

- 3.5.5 NonCachedBlockWrite 3–10

- 3.6 Interrupt Control Transactions 3–10

- 3.6.1 Interrupt Request 3–10

- 3.6.2 InterruptAck 3-12

- 3.6.3 InterruptNack 3–13

- 3.7 J\_ADTYPE[7:0], J\_AD[127:0], J\_ADP[3:0] 3–14

- 3.7.1 Idle Cycle 3–14

- 3.7.2 Address Cycle 3–15

- 3.7.3 Read16 Data Return Cycle 3–16

- 3.7.4 Read64 Data Return Cycle 3–16

- 3.7.5 Read Data Error Cycle 3–18

- 3.7.6 Write Data Cycle 3–18

#### 4. Reset 4–1

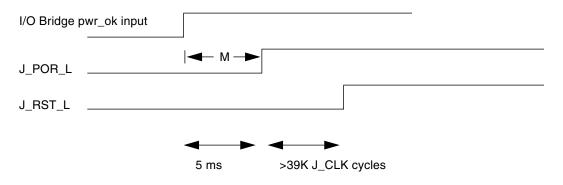

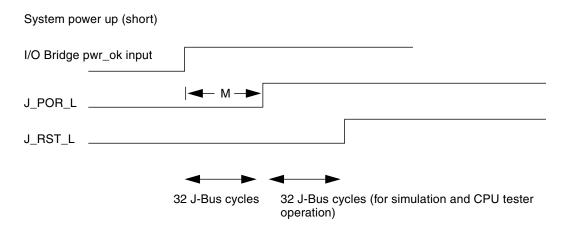

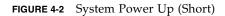

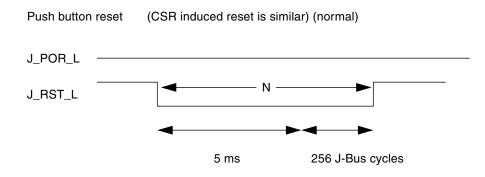

- 4.1 Reset Sequence 4–1

- 4.2 Exceptions to RST\_PIN\_EN 4–5

#### 5. J-Bus Arbitration Protocol 5–1

- 5.1 Overview 5–1

- 5.2 Possible IDs Used in a System 5–2

- 5.2.1 OpenSPARC T1 Implementation 5-4

- 5.3 J\_PACK Connectivity 5–5

- 5.4 Distributed Arbitration 5–5

- 5.4.1 Arbitration Signals 5–6

- 5.4.2 Arbitration Rules 5–6

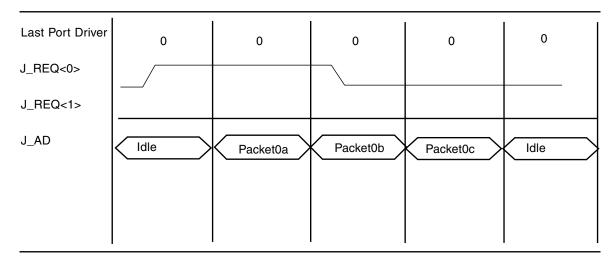

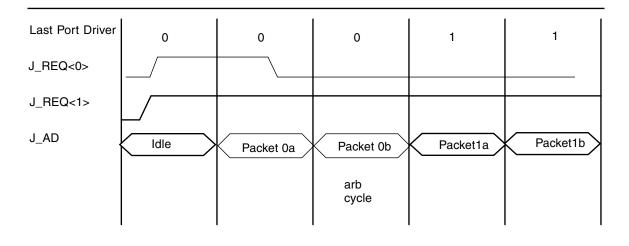

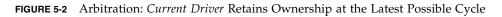

- 5.4.3 Timing Diagrams 5–9

#### 6. J-Bus Electrical Specification 6–1

- 6.1 Overview 6–1

- 6.2 Configurations 6–2

- 6.2.1 Topology Restrictions 6–2

- 6.2.2 Noise Margins 6–3

- 6.2.3 DTL Scheme 1 6-3

- 6.2.4 Output Driver Topology 6–3

- 6.3 Power Implications 6–5

- 6.3.1 1.5 V Supply 6–5

#### 7. Address Map 7–1

- 7.1 Address Map Table 7–1

- 7.2 Three Reserved Address Spaces Per Port 7–2

- 7.3 Address Mapping Errors 7–3

#### 8. Serial System Interface 8–1

- 8.1 Overview 8-1

- 8.2 Functional Interface 8–2

- 8.2.1 SSI Request 8-2

- 8.2.2 SSI Response 8-3

- 8.3 SSI Software Interface 8–3

- 8.3.1 SSI Register Interface 8–3

- 8.3.2 SSI Error Handling 8–4

- 8.3.3 SSI Interrupts 8-4

Glossary Glossary-1

Index Index-1

# Figures

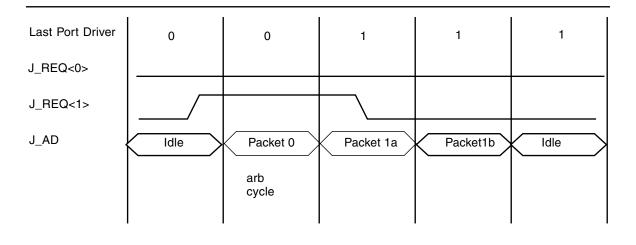

| FIGURE 1-1 | Non-pipelined J-Bus System 1–2                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 1-2 | J_PAR Generate and Check Pipeline 1–17                                                                                         |

| FIGURE 1-3 | J_PAR Generate and Check Timing Diagram 1–18                                                                                   |

| FIGURE 2-1 | Quadword Wrap Order for Block Reads on J_AD. 2-2                                                                               |

| FIGURE 4-1 | System Power Up (Normal Length) 4–3                                                                                            |

| FIGURE 4-2 | System Power Up (Short) 4–4                                                                                                    |

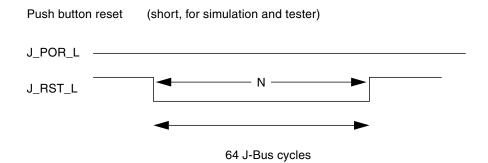

| FIGURE 4-3 | Push Button Reset (Normal) 4–4                                                                                                 |

| FIGURE 4-4 | Push Button Reset (Short, for Simulation and Tester) 4–5                                                                       |

| FIGURE 5-1 | Arbitration: J-Bus Port 0 Drives Multi-cycle Packet in the Absence of Another Request 5-10                                     |

| FIGURE 5-2 | Arbitration: Current Driver Retains Ownership at the Latest Possible Cycle 5–11                                                |

| FIGURE 5-3 | J-Bus Port 0 Drives Single-Cycle Packet Without Asserting Request, Right Before J-Bus Port 1 Drives a Multi-cycle Packet. 5–11 |

| FIGURE 6-1 | J-Bus Top-Only Motherboard 6-2                                                                                                 |

# Tables

| TABLE 3-1 | Transaction Set Summary 3–3                                   |

|-----------|---------------------------------------------------------------|

| TABLE 3-2 | J_ADTYPE[7:6] During First Cycle of Address or Data Read 3–14 |

| TABLE 5-1 | J-Bus Agent ID Assignments 5–3                                |

| TABLE 5-2 | J-Bus Requests Assignments 5–3                                |

| TABLE 5-3 | OpenSPARC T1 Implementation of Agent IDs 5–4                  |

| TABLE 5-4 | Arbitration Priority 5–8                                      |

| TABLE 5-5 | Arbitration Mode 5–9                                          |

| TABLE 6-1 | Other Non-DTL signals 6-1                                     |

| TABLE 7-1 | OpenSPARC T1 Processor Address Map 7-1                        |

| TABLE 8-1 | SSI Error Handling 8–4                                        |

### Preface

This document describes the external interfaces for the OpenSPARC<sup>™</sup> T1 processor from Sun<sup>™</sup> Microsystems, Inc. This processor is the first chip multiprocessor that fully implements the Sun Throughput Computing Initiative.

### How This Document Is Organized

This document is organized as described in the following paragraphs.

- Chapter 1 provides a complete description of the J-Bus system.

- Chapter 2 describes the Peripheral Component Interconnect (PCI) model for J-Bus, including data flow, flow control, and the master interface.

- Chapter 3 provides details of the J-Bus transaction set, memory transactions, noncached data transactions, interrupt control transactions and the J\_ADTYPE signal.

- Chapter 4 describes J-Bus reset sequence guidelines and RST\_PIN\_EN exceptions.

- Chapter 5 specifies the distributed arbitration protocol for driving any address or data onto J-Bus.

- Chapter 6 provides configuration descriptions and restrictions, along with power implications.

- Chapter 7 describes the required physical address map for J-Bus devices, along with how to handle address mapping errors.

- Chapter 8 provides details of the Serial System Interface (SSI).

# Using UNIX Commands

This document might not contain information about basic UNIX<sup>®</sup> commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

# Shell Prompts

| Shell                                 | Prompt        |  |

|---------------------------------------|---------------|--|

| C shell                               | machine-name% |  |

| C shell superuser                     | machine-name# |  |

| Bourne shell and Korn shell           | \$            |  |

| Bourne shell and Korn shell superuser | #             |  |

# **Typographic Conventions**

| Typeface* | Meaning                                                                                                                     | Examples                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AaBbCc123 | The names of commands, files,<br>and directories; on-screen<br>computer output                                              | Edit your.login file.<br>Use ls -a to list all files.<br>% You have mail.                                                                                                        |

| AaBbCc123 | What you type, when contrasted with on-screen computer output                                                               | % <b>su</b><br>Password:                                                                                                                                                         |

| AaBbCc123 | Book titles, new words or terms,<br>words to be emphasized.<br>Replace command-line variables<br>with real names or values. | Read Chapter 6 in the <i>User's Guide</i> .<br>These are called <i>class</i> options.<br>You <i>must</i> be superuser to do this.<br>To delete a file, type rm <i>filename</i> . |

\* The settings on your browser might differ from these settings.

# **Related Documentation**

The documents listed as online are available at:

http://www.opensparc.net

| Application                                                        | Title                                                                                  | Part Number | Format | Location |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------|--------|----------|

| OpenSPARC T1 instruction set                                       | UltraSPARC Architecture 2005<br>Specification                                          | 950-4895-03 | PDF    | Online   |

| OpenSPARC T1 processor internal registers                          | UltraSPARC T1 Supplement to<br>the UltraSPARC Architecture<br>2005                     | 819-3404-02 | PDF    | Online   |

| OpenSPARC T1 signal pin list                                       | OpenSPARC T1 Processor<br>Datasheet                                                    | 819-5015-10 | PDF    | Download |

| OpenSPARC T1 megacells                                             | OpenSPARC T1 Processor<br>Megacell Specification                                       | 819-5016-10 | PDF    | Download |

| Running simulations and synthesis<br>on the OpenSPARC T1 processor | <i>OpenSPARC T1 Processor</i><br><i>Design and Verification</i><br><i>User's Guide</i> | 819-5019-10 | PDF    | Download |

# Documentation, Support, and Training

| Sun Function  | URL                               |

|---------------|-----------------------------------|

| Documentation | http://www.sun.com/documentation/ |

| Support       | http://www.sun.com/support/       |

| Training      | http://www.sun.com/training/      |

### Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

### Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

OpenSPARC T1 Processor External Interface Specification, part number 819-5014-10

CHAPTER

### J-Bus: Overview and Philosophy

This chapter describes the following topics:

- Introduction

- Goals

- Signal List

- Address and Data Flow Control

- Other Caching Issues

- Interrupts

- OpenSPARC T1 PCI Ordering Rules

- Data Transfer Detail

- Posted Coherency

- DTL Mode Programming

- Error Code Correction and Parity

- J\_PAR: Parity for J\_REQ\_L and J\_PACK0-6

- Fatal Errors

### 1.1 Introduction

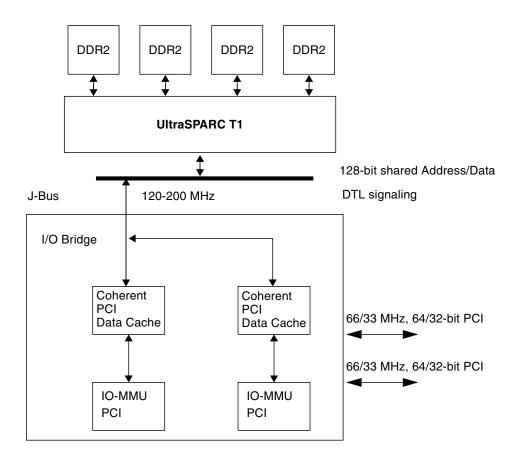

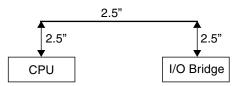

The J-Bus system shown in FIGURE 1-1 is composed of a central processing unit (CPU); memory; Peripheral Component Interconnect (PCI) mode; and an interconnect model that specifies architectural queues, caches, translation lookaside buffers (TLB), and overlapped and pipelined operations.

This specification provides the following level of detail:

- Specifies all behaviors that are visible between major functional areas

- Identifies major implementation decisions that are necessary to meet performance goals

J-Bus meets the following requirements:

- Correctness with respect to SPARC-V9 memory models

- Compatibility with Sun4U<sup>TM</sup> system architecture, including PCI extensions

J-Bus reflects ideas from a variety of bus implementations and is optimized to keep performance up for the 1–4 way CPU design point.

FIGURE 1-1 Non-pipelined J-Bus System

# 1.2 Goals

J-Bus architectural goals include the following:

- **Simple flow control.** Distributed variable latency for all producers and consumers of information.

- Shared address and data bus.

- I/O bridge (IOB) provides the PCI interface.

- 150-200 MHz J-Bus operation, with or without dead cycle, programmable for three J-Bus loads (one CPU, two I/O bridges). Signals always driven, except for bus turn-around cycle during dead cycle mode.

- No hard latency or throughput requirements in the protocols. This enables some simplification of the design, as opposed to a fixed-latency, fixed-throughput design. Some low-latency behavior is noted. Average-latency and throughput requirements do exist for performance reasons.

- Out-of-order data return for different cacheable addresses. In-order data return from a single noncacheable port. In-order data return for the same cacheable address. Order is determined by address bus order.

Blocking is done in a distributed fashion, with each port tracking its own reads. There is no system definition for a maximum number of outstanding reads. Any maximum would depend on the port designs.

There is a maximum number of eight outstanding reads per port ID due to the fixed width J\_ADTYPE signal, which includes read transaction ID information. Stores are not constrained.

- Minimize parallel control flow paths to eliminate sources of race conditions. This stipulation eliminates corner cases and makes the chip easier to design and debug.

- Interrupt delivery model matches Sun4U at the mondo vector and software visible points.

- PCI subsystems have queued input packets and delayed data return, so their activity is fully decoupled from J-Bus activity.

- Snooping is variable latency, but fully pipelined and overlapped. Snoops are initiated at the processors (and IO-cache) when the request address is presented on the shared J\_AD bus. The snoop latency must be less than the memory latency. Start the DRAM read and cancel the return data J-Bus drive if the snoop indicates a dirty line elsewhere.

# 1.3 Signal List

J-Bus control signals consist of the following:

#### ■ J\_REQ\_OUT\_L[1:0], J\_REQ\_IN\_L[5:4]

Used for distributed arbitration requests for J\_ADTYPE/J\_AD/J\_ADP. Typically, a maximum of one CPU plus two I/O bridges. Used to request bus for addresses, write data, and returning read data.

J\_REQ\_OUT\_L[1:0] is output only, two copies of this port's request.

J\_REQ\_IN\_L[5:4] are up to two possible other requests. The hookup order depends on agent ID and must be exactly to specification; otherwise, the arbitration will not work correctly.

Dead-cycle mode variants are used to reserve the global J-Bus for one more cycle than the ownership of a local bus segment to account for the J-Bus repeater delay, if used.

■ J\_AD[127:0]

Used for all address and data packets.

■ J\_ADP[3:0]

Used for word parity for all J\_AD transfers. J\_ADP[3] should also cover the eight extra bits of J\_ADTYPE, that is, ~(^AD[127:96] ^ ^ADTYPE[7:0]). ("^" represents Exclusive OR.) Ports receiving a data packet should check incoming parity. All ports should check parity on all address cycles.

All 1's on J\_AD/J\_ADP/J\_ADTYPE is correct parity (the not-driven dynamic termination logic (DTL) state).

#### ■ **J\_ADTYPE**[7:0]

Identifies the packet type on J\_AD/J\_ADP and signals the destination for the returning read data. Contains the read transaction ID for out-of-order read data return. The undriven J\_ADTYPE/J\_AD value of all 1's corresponds to an idle cycle.

#### ■ J\_PACK0,1,4,5[2:0]

Bused to all, but single driver (enable depends on agent ID). Contains encoded snoop information and flow control, plus read data flow control (consumption notice).

As input, only use J\_PACKs enabled by a control status register (CSR) to match system configuration. J\_PACK will still be 1's at reset deassertion if it should not be used.

Agent ID is used to decide which of the bidirectional J\_PACKs are driven by a port.

#### ■ J\_PAR

Driven by one I/O bridge every cycle.

XNOR of J\_REQ[5:4], J\_PACK0,1,4,5[2:0] from N cycles ago. See Section 1.12, "J\_PAR: Parity for J\_REQ\_L and J\_PACK0-6" on page 1-16 for details.

Used to check parity on these control signals. If I/O bridge is the source of a signal, it should pipe its output forward for use in the XNOR to avoid sampling the signals that it drives.

This J-PAR signal is driven N cycles after the relevant signals are active on J-Bus because I/O bridge must register inputs, compute, then register output.

Each device on the J-Bus should register this J\_PAR and compare it to the J\_PAR devices computed in the previous cycle (but these J\_PAR devices did not drive their J\_PAR value).

Each port should detect a local error, log, and report the error, if it detects a problem.

**Note** – Conditionally, a CSR can specify that a delayed version of a device's own J\_PACK and other devices be used to mimic the delayed propagation of J\_PACKs through the repeater, which depends on the system configuration.

**Note** – Another CSR bit will control whether, for this port, J\_PAR must be propagated through a repeater, thus requiring a further pipeline delay in the internal parity check. If this port is on the same J-Bus segment as the port driving J\_PAR, there is no additional delay.

■ J\_RST\_L

Non-power-up reset, active low.

■ J\_POR\_L

Power-up reset, active low. Actual name is PWRON\_RST\_L.

■ J\_CLK[+-]

Differential pseudo emitter-coupled logic (PECL) clock (120-200 MHz).

■ J\_ERR

Not used functionally but driven by any requestor that detects an error. This pin is used for scope and logic analyzer work only. Preferably not bussed.

All J-Bus address and control signals are DTL drivers and receivers. Unused J\_REQ\_L or J\_PACK pins should be connected so that a termination will pull them to the inactive state (1).

# 1.4 Address and Data Flow Control

Global address OK (AOK) and port and address-range specific data OK (DOK) state is maintained by each requestor to decide if there is room for address and write data at the targets for this transaction. The transaction is not driven on the bus if there is no room at the destination.

The start and stop window is symmetric.

- A port is not allowed to drive affected transactions starting in the second cycle after the J\_PACK that changed internal AOK/DOK state.

- A port can restart on the second cycle *after* a J\_PACK that re-enables the internal AOK/DOK state.

All masters track AOK and DOK states.

A simpler definition of the requirement for AOK/DOK affecting outputs is "as soon as physically possible" (assuming inputs and outputs are registered).

The same rule applies to turning AOK/DOK back on. New outputs are allowed "as soon as possible" (assuming inputs and outputs are registered).

For a port's own AOK/DOK state, the port should look at its own J\_PACKs as if it were another port for the correct timing. All ports should react at the same time. This helps fairness because all ports see the blocking removed at the same time.

#### 1.4.1 Address OK

Address OK (AOK) state assumes one address per cycle (worst case) and DOK state assumes 16 bytes of data per cycle (worst case) can be delivered to a port.

AOK state is global. Any port can disable AOK by asserting an encoded single-cycle "AOK off" on its J\_PACK signals. "AOK on" from the same port is required before addresses can continue.

**Note** – It's important that a bit of AOK state be maintained for each port. The global AOK state is the AND of all individual AOK states. This prevents race conditions in different ports setting AOK on and off at the same time.

**Note** – It is important to avoid livelock due to favoritism towards the last owner and all requests being forced off during AOK\_OFF (or DOK\_OFF).

After a port turns AOK off, it should not turn AOK back on until it can accept at least one address transaction without turning AOK back off. This means AOK should not go back on until you have free space equal to current overrun definition + 1 (worst case: handle read + writeback), rather than turning on at the current overrun definition. Use the following guidelines:

- Turn AOK off when the space available == overrun spec (4).

- Turn AOK back on when the space available == overrun spec + 2 (6).

These guidelines should solve the livelock issue of one port constantly and solely getting the bus after AOK off/on transitions and blocking out forever. The DOK case does not need special handling.

To avoid oscillation of AOK behavior, the turn on should be delayed until more room than the minimum is available.

### 1.4.2 Data OK

Data OK (DOK) state is tracked on an address-range basis. Address ranges are assigned to ports at power up based on their port-ID.

An encoded "DOK off" from a port will cause writes to that address range to be suspended (by the initiator) until an encoded "DOK on" by that port is broadcast (single-cycle events on the J\_PACK).

The granularity of address-range assignments is kept coarse so that the address matching, before a write is generated, is relatively easy.

The address space has a fixed partitioning to ports. A port's DOK status is used before initiating a write to an address belonging to that port.

Read plus writeback is an atomic transaction, so both the read and writeback request are held up by the initiator if room is not available for the writeback data (indicated by DOK state).

### 1.4.3 Interrupt Flow Control

Interrupt send is flow controlled with a separate protocol that has a oneoutstanding, token-based scheme.

Each CPU thread can queue one incoming interrupt packet. Threads receiving interrupts send an ACK back if the packet is accepted and NACK back if it is refused (because one has been received already, but not digested and unloaded by software).

**Note** – The J-Bus masters do not look at the AOK/DOK state for restricting interrupt delivery. The interrupt receivers must remember the state for receiving an interrupt address and data that is independent of any other address or data queues.

### 1.5 Other Caching Issues

Peripheral Component Interconnect (PCI) interfaces hang off the I/O bridge chip.

#### 1.5.1 I/O Data Cache

The PCI input/output caches (IO-cache) and input/output Memory Management Units (IO-MMU) are the initiators of all coherent activity from I/O bridge.

#### 1.5.2 No-Snoop Pages

The Solaris Operating System software guarantees that a page is flushed from all caches and is only used by one port at any time, so a page can be marked no-snoop in the IO-MMU, the CPU IO-MMU, or the data Memory Management Units (D-MMU).

No-snoop references will still cause J\_PACKs, but the caches do not need to be interrogated before J\_PACKing. Regard no-snoop J\_PACKs just like a normal operation.

**Note** – This is the UltraSPARC T1<sup>®</sup> processor's normal operating mode (Posted Coherency Mode).

Because both normal and no-snoop pages will have the early memory access start, and no-snoop addresses will still go out on J-Bus, there is *no performance advantage to marking pages as no-snoop*.

### 1.5.3 Encaching No-Snoop Data

If a non-snooped location is encached and modified, it must be flushed to memory when another port wants to see that data. Also, if another port modifies the data, other ports want to eventually see the update.

This arrangement works if the no-snoop data is installed as E (or M) in the caches. IO-caches will not have a direct flush mechanism. Software will handle any flushing necessary due to remapping.

### 1.6 Interrupts

An INT transaction is sent to CPUs with data as a multi-cycle packet that includes the Sun4U-specified mondo vector data. This transaction method is used for I/O interrupts sent by I/O bridge.

**Note** – The OpenSPARC T1 processor only looks at the first cycle (16 bytes) of mondo data because that is the only cycle of meaningful data driven by I/O bridge.

Each thread has queue for one interrupt receive address and data. The thread sends an InterruptAck (INT\_ACK) transaction out when the address and data is accepted. The thread sends an InterruptNack (INT\_NACK) if the interrupt is refused because the CPU is busy with one already.

**Note** – The OpenSPARC T1 processor has queues for receiving up to 16 interrupts (2x the 8 outstanding interrupts possible from I/O bridge). For more information, see Section 3.6, "Interrupt Control Transactions" on page 3-10.

The OpenSPARC T1 processor has dedicated registers for receiving mondo vector data.

Power-up and non-power-up reset are individually signaled with two dedicated pins.

The interrupt packet contains source and destination IDs so the target knows to accept the packet.

Because there is a dedicated mondo receive register at the processors to receive the interrupt data, the interrupt request and associated data does not go into the queue affected by AOK or DOK.

AOK flow control at the J-Bus CPU ports is only for outstanding memory request activity. They can fill only due to read and WriteInvalidate (WRI)/WriteMerge (WRM) requests.

AOK, however, can also fill due to I/O bridge input queue being full due to noncacheable activity.

# 1.7 OpenSPARC T1 PCI Ordering Rules

The PCI ordering rules supported by the OpenSPARC T1 Processor processor is a subset of the PCI ordering rules used by the Solaris Operating System.

### 1.7.1 DMA Write Ordering

PCI specifies that Posted Memory Writes (PMW) must be processed in order, which means that PMWs must become coherently visible in order. Since the OpenSPARC T1 Processor processor has an interleaved L2-cache, with four separate controllers for the four banks, this ordering requirement might not be met if the DMA writes were indicriminantly forwarded to the different banks without waiting for ACKs from the L2-cache.

Each L2 bank guarantees that it processes incoming requests in order for individual lines. Therefore, the J-Bus interface (JBI) in the OpenSPARC T1 Processor processor can issue multiple WR\* transactions to a single L2 bank, as long as they were generated from the same WRM. However, JBI will stall younger WR\*/WRIS transactions to a different bank, or to the same bank if from a different bus transaction, until all previous WRM/WriteInvalidateSelf (WRIS) transactions have been ACKed. Once all previous WRM/WRIS transactions have been ACKed, the oldest stalled WRM/WRIS transaction is sent to the L2 bank for which it is targeted.

### 1.7.2 PIO Read Returns Compared to DMA Writes

PIO Read Returns are guaranteed to force all older DMA writes to be complete before the PIO read data is returned to the processor. To implement this, the JBI stalls NonCachedRead (NCRD) return data until all previous WRM/WRIS transactions have been ACKed by the L2-cache, then forwards that return data to the requesting thread.

### 1.7.3 Interrupts Compared to DMA Writes

Interrupts are guaranteed to force all older DMA writes to be complete before the interrupt is delivered to the processor. The JBI stalls the INT transaction until all previous WRM/WRIS transactions have been ACKed by the L2-cache, then forwards that interrupt to the target thread. If multiple INTs are received, each one has state specifying how many WRM/WRISs must be processed and ACKed by the L2 before the INT can be forwarded to its target thread, so each INT waits "only as long as it has to."

### 1.7.4 DMA Reads Compared to DMA Writes – Address Consistency

The OpenSPARC T1 Processor processor does not guarantee that DMA writes and reads are kept in order, unless they are to the same cache line. The processor implements this by guaranteeing that all DMA writes and reads to the same L2 bank are issued in order, and the L2 bank processes writes and reads to the same line in order. DMA writes to one line can be processed out of order relative to DMA reads to a different line, and vice versa.

The OpenSPARC T1 Processor processor implements a mode bit that will force ordering of DMA reads in relationship to previous DMA writes regardless of the addresses. However, the mode bit is not intended to be turned on for normal system use. If an I/O driver/device pair does require read versus write ordering, the mode bit can be turned on.

### 1.7.5 PIO Request Ordering

All outgoing PIO requests, both PIO Reads and PIO Writes, are maintained in order for all threads, at least until they are issued on J-Bus. There is no bypass capability to enable younger writes to pass up older reads. PIOs are always issued strictly in order.

### 1.7.6 PIO Writes Compared to DMA Read Returns – Not Supported

PCI has a rule specifying that DMA read returns must not be able to bypass older PIO writes. This rule is only interesting if a driver issues a PIO write to a device, updates memory, and expects that the device cannot see the updated memory before it sees the PIO write. Because the Solaris Operating System requires a PIO read to ensure visibility of previous PIO writes and I/O bridge does not support this rule, the OpenSPARC T1 processor does not support this rule either.

Instead, the OpenSPARC T1 processor has separate queues for outgoing PIO requests compared to DMA read returns, so the two classes are in no particular order relative to each other.

### 1.7.7 DMA Reads – No Ordering Rules

PCI inflicts no ordering rules on one read compared to another read. The effective order of reads is defined by the order that the data crosses the bus. On the OpenSPARC T1 processor, read returns will be in an arbitrary order relative to the order in which they were issued on J-Bus with one exception – two reads to the same cache line will get their returns in address order.

**Note** – No ordering rules means that if there is a large DMA on PCI, which is translated into multiple ReadToDiscards (RDD) on J-Bus, there is no ordering guarantee based on address order. So, it would not work if software initialized a payload, immediately preceded it with a DMA\_READY flag, then interacted with a device that was reading the flag with a large transaction that also prefetched following lines of payload.

### 1.8 Data Transfer Detail

**J\_ADTYPE**[7:0] identifies address and data packets on J-Bus and provides additional information about coherent state and data packet size for data returns.

Flow control for data is explained in Section 1.4, "Address and Data Flow Control" on page 1-6. Flow control for both address and data is separate from the signaling of actual transfers.

Data is pushed by the J-Bus master on writes.

Error correction code (ECC) is checked and corrected inside the CPU at the memory controller. Parity is generated and checked for all data driven on J-Bus.

### 1.8.1 DOK Flow Control for Writes

All data is pushed by the transaction initiator.

I/O bridge and the memory controllers should unload the initial 64 bytes fast enough so DOK is kept asserted for back-to-back writes.

There is a four J-Bus cycle latency in detecting a write that will cross the high water mark in the data queues, thus making DOK==0 and requiring the processor to react to DOK==0.

All signals between chips must be registered.

Four cycles of race latency necessitate the following requirements:

- Worst case 4\*16 bytes of data overrun area (versus DOK high water mark)

- Four address input queue entries for overrun (at each processor and I/O bridge)

Because the CPUs do not support any noncacheable destinations, they do not need to enqueue incoming noncacheable addresses.

**Note** – The OpenSPARC T1 processor supports the 64-Gbyte noncacheable destinations and aliases them to the 64-Gbyte cacheable space.

### 1.8.2 Read Data Flow Control

Read data flow control supports enough read buffering to hold data for all of its outstanding reads.

### 1.8.3 Memory Controller Reordering

Memory ordering is arbitrary for outstanding transactions, except to maintain data consistency. Reads can pass reads. Reads can pass writes only if the addresses do not match. All reads must return data consistent with the results of all prior writes.

# 1.9 Posted Coherency

J-Bus was originally designed to be a central snoop bus, where all devices saw all coherent transactions. To meet OpenSPARC T1 requirements, the model is modified so that J-Bus becomes a coherent I/O bus, but processor traffic is kept strictly

internal to the processor. To do this, the system is designed so all I/O caches are effectively turned off, and the I/O bridge chips issue only "posted" coherent write transactions and only use "snapshot" coherent read transactions. This means that DMA is performed using the following transactions:

- RDD Read and Discard Line

- WRIS Write Invalidate Line

- WRM (New transaction) Write Merge

All coherent operations are performed at the OpenSPARC T1 L2-cache. For posted writes, the OpenSPARC T1 processor accepts the posted coherent writes (WRIS and WRM) from J-Bus and performs the writes in strict bus order in the L2- cache. Full line WRIS transactions will snoop-invalidate in the L2, but write only into main memory (to avoid cache pollution). ReadToDiscard (RDD) transactions will read coherent data from the L2 or memory (if not present in L2). The data can then be used once for DMA.

This strategy enables the OpenSPARC T1 processor to support a coherent I/O subsystem without the complexity of duplicate tags (of the I/O caches) or recalls. Performance is the same or a slightly better because the subline DMA writes will pipeline better and have reduced bandwidth impact on J-Bus. DMA read performance for I/O bridge is identical.

### 1.9.1 J\_PACK Snoop Results

J\_PACK*n*[2:0] is the bused snoop result from each J-Bus caching port to all other caching ports. The following information is returned:

- P\_IDLE: 0

- P\_COHACK: 1 Snoop completed, cache does not have to return dirty data. Cache state may have been changed as a side effect.

- P\_COHACKS: 2 Only used by ReadToShare (RDS) snoop. Snoop completed. This cache is keeping the line in S (was S or E). Not used if cache is returning data.

- P\_COHACKD: 3 Dirty line. Cache will return data to J-Bus. Memory controller will inhibit its response. This cache may change to I or O state, depending on the transaction.

**Note** – The OpenSPARC T1 processor will respond to all snoops immediately (without snooping any caches) with a P\_COHACK.

The following four encodings are used for address and data flow control:

- P\_AOK\_OFF: 4

- P\_AOK\_ON: 5

- P\_DOK\_OFF: 6

■ P\_DOK\_ON: 7

**Note** – The OpenSPARC T1 processor will never issue P\_DOK\_OFF.

The address and data flow control J\_PACKs should have higher priority than the snooping J\_PACKs; otherwise, the flow control model will be broken.

Specifically, the following priority should be used:

- 1. P\_AOK\_OFF (AOK off also blocks anything DOK off would block)

- 2. P\_DOK\_OFF

- 3. P\_AOK\_ON

- 4. P\_DOK\_ON

- 5. P\_COHACK\*

- 6. P\_IDLE

### 1.10 DTL Mode Programming

J\_PAR may need its own DTL termination mode control.

J\_AD/J\_ADP/J\_ADTYPE can share a mode control since they should be routed the same way on the motherboard.

J\_PACK0-6 has similar connectivity, so it makes sense to force it to have the same mode control as J\_AD/J\_ADP/J\_ADTYPE.

J\_REQ\_IN\_L[5:0] needs its own mode control, as does J\_REQ\_OUT\_L[5:0].

### 1.11 Error Code Correction and Parity

All error code correction (ECC) is handled inside the CPU/memory controller ports.

Word parity is used for all J\_AD transfers.

All detected uncorrectable errors (UE) and correctable errors (CE) errors are reported using interrupts. They were asynchronous traps for CPU-initiated errors in Sun4U.

Correct word parity is always driven on J\_AD.

UE/CE information is passed along with the data using J\_ADTYPE. This way J-Bus errors are uniquely identified with respect to memory errors. The syndrome of the memory error is not passed with the data and is logged at the memory controller that detected the error. Software should poll the memory controller after receiving an ECC trap to get the correct error syndrome.

**Note** – The OpenSPARC T1 processor will never indicate CE and ignores CE if signaled by I/O bridge.

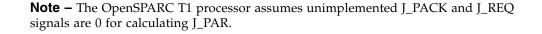

### 1.12

# J\_PAR: Parity for J\_REQ\_L and J\_PACK0-6

Most of the J-Bus signals do not have any latency requirements so complicated timing diagrams are not needed. Arbitration (J\_REQ\_L) does have specific timing descriptions. J\_PAR is the most complicated because of the varying propagation delay for J\_PACK0-6 and J\_PAR in a system, which depends on which port is driving the signals and whether the port is on a local or non-local J-Bus segment.

In addition, like all bidirectional signals, we do not want to sample as input any signals that we drive, so there must be bypasses that are specific to whether or not a port is driving a particular J\_PACK0-6 or J\_PAR.

FIGURE 1-2 and FIGURE 1-3 specify the J\_PAR generate and check pipeline. All ports should implement the pipeline as shown.

A pipeline stage is added to enable the parity generation to be distributed over two cycles to ensure that it does not become a long timing path from I/O pad input register to I/O pad output register.

I/O bridge needs 10 control status register (CSR) bits:

- Seven bits to delay JPACK0-6 by one cycle, if bit is set (0 after reset)

- One bit to delay generated parity by one cycle, before checking (0 after reset) This does not delay the output of J\_PAR by the driver.

- One bit to enable J\_PAR drive (disabled after reset)

- One bit to enable J\_PAR checking (disabled after reset)

Depending on which J\_PACK the port drives, do not clock the corresponding input register and bypass a copy of what the port drove out.

FIGURE 1-2 J\_PAR Generate and Check Pipeline

This logic should be implemented on both the OpenSPARC T1 processor and I/O bridge with CSRs. It enables any of the CPUs or I/O bridges to be the J\_PAR driver with arbitrary organization of which port is on which shared J-Bus segment.

At reset, no device should drive J\_PAR, and J\_PAR-related error checking should be disabled.

The following figure shows J\_PAR generate and check timing.

Timing Diagram (repeater case for both J\_PACKn and J\_PAR is worst case)

FIGURE 1-3 J\_PAR Generate and Check Timing Diagram

There is CSR programmable delay of information to selectively match the repeatercreated delay for chips that capture some information on a local J-Bus segment without a repeater delay. This CSR programmable delay is for J\_PACK0-6 and J\_PAR, but not for J\_REQ\_L[6:0], which are never driven by repeaters.

If all ports are on a single J-Bus segment (no repeaters), the CSRs must not delay J\_PAR. The J\_PACK*n* should be delayed to have uniformity of J\_PAR timing with repeater-based topologies. I/O bridge can assume J\_PACK*n* and J\_PAR are always delayed by repeater to avoid the need for CSRs.

### 1.13 Fatal Errors

Address cycle parity errors, arbitration timeout, JBI to L2-cache interface timeout, and J\_PAR parity errors (request and J\_PACK) are considered to be fatal.

We can log the error, but we cannot just say "continue" because some ports might see one thing, and the other ports another. This is typical for intermittent errors. A static (broken wire) error might or might not be visible to all ports, but the system would stop running in that case anyway.

These fatal "not possible to continue" errors will cause a system reset.

Any error logs that are set by these fatal errors are preserved.

A separate transaction cannot be used to signal a fatal error because the bus might be hung.

Because there are no free J\_PACK encodings, I/O bridge will look for four consecutive cycles of the DOK\_ON (7) J\_PACK encoding from any active J\_PACK.

To signal I/O bridge this way for fatal errors requires that ports only assert DOK\_ON for one cycle and assert a DOK\_OFF before asserting another DOK\_ON.

If any port detects a fatal error (address cycle parity error or J\_PAR parity error), the error should be logged, J\_ERR asserted (used only for debug), and DOK\_ON driven as soon as possible for four consecutive cycles. This assertion of DOK\_ON will cause I/O bridge to do a J\_RST\_L as soon as possible.

## Interconnection Model

This chapter describes the following topics:

- Overview

- Data Flow

- Flow Control Model

- J-Bus Port Model

## 2.1 Overview

The Peripheral Component Interconnect (PCI) model for J-Bus includes data flow, flow control, and the master interface. A J-Bus port is the interface to the single-bus interconnect.

The port is either a CPU or an I/O bridge.

A J-Bus port has a single address and data bus for the packet-switched read protocol. J-Bus supports up to seven ports, which are limited by the arbitration, and snoop and flow control pins. The OpenSPARC T1 processor uses four ports on J-Bus and only supports connecting to two other I/O bridge ports.

Because slave-only ports also must arbitrate for returning read data, this limit is not changed for slave-only ports.

Each J-Bus port should also be a slave port.

I/O bridge supports two logical J-Bus ports. There are two caching master ports and two slave ports for PCI. More than one I/O bridge is permitted in a system.

J-Bus is synchronous with a centrally distributed clock (system clock).

**J\_AD[127:0]** is a 128-bit bidirectional packet-switched request and data bus. This bus carries address bits PA[42:0] of a 43-bit physical address space. It also carries data for reads, writes, and interrupt packets.

**Note** – Internally, the OpenSPARC T1 processor only supports a 40-bit physical address.

**J\_ADP[3:0]** is word parity for J\_AD[127:0] (odd: = J\_ADP[0] = ~^J\_AD[31:0]). J\_ADP[3] should also cover the eight extra bits of J\_ADTYPE. Ports receiving a data packet should check incoming parity. All ports should check parity on all address cycles.

A valid packet on the J\_AD/J\_ADP is identified by the driver asserting the encoded J\_ADTYPE[7:0] signal. A J\_ADTYPE assertion may indicate multiple cycles of data drive.

A J-Bus caching master port snoops coherent address packets on the J\_AD using a write-invalidate cache-coherence protocol.

The transaction set supports block transfers of 64 bytes, cacheable writes of 0 to 64 bytes qualified with a 64-bit bytemask, and single-quadword, noncached transfers of 0 to 16 bytes qualified with a 16-bit bytemask.

Data is normally transferred in units of 16 bytes/clock cycle.

Slave ports signal read data return on the J\_AD with the encoded J\_ADTYPE[7:0] signal.

Byte ordering is big-endian. Bits [7:0] are bytes 15, 31, 47, and 63. Bits [127:120] are bytes 0, 16, 32, and 48.

For block read transactions of 64-byte data, the addressed 32 bytes specified by physical address bit PA[42:5] is delivered first. The successive quadwords are delivered in the wrap order shown in FIGURE 2-1.

Note that 16-byte alignment is not supported. Only 32-byte alignment is supported.

| Address<br>PA[5:4] | First Qword<br>on Databus | Second Qword<br>on Databus | Third Qword<br>on Databus | Fourth Qword<br>on Databus |

|--------------------|---------------------------|----------------------------|---------------------------|----------------------------|

| 0x0                | Qword 0                   | Qword 1                    | Qword 2                   | Qword 3                    |

| 0x2                | Qword 2                   | Qword 3                    | Qword 0                   | Qword 1                    |

FIGURE 2-1 Quadword Wrap Order for Block Reads on J\_AD.

## 2.2 Data Flow

Typical data flows for read/write, read sequence for dirty encached data, noncached slave read sequence, and noncached slave write sequence are described in this section.

#### 2.2.1 Read/Write

A typical read/write data flow to and from memory is as follows:

- 1. The J-Bus master port issues a read/write transaction request on J-Bus.

- 2. If it is a cacheable request, all J-Bus masters do a snoop on their local caches. At the same time, the addressed memory controller starts the memory cycle if the address is for main memory.

- 3. **Read** If the snoop (J\_PACK acknowledgements) determines that the data should come from memory, the memory controller arbitrates for J-Bus. Data is delivered to the requesting J-Bus port with an encoded J\_ADTYPE[7:0] during the first cycle of the data packet.

**Write** – Writeback transaction and data is sent atomically with the read. If a block store is initiating the coherent write, then snooping is done for possible invalidate. The address and data are queued at the memory control in order behind the victimizing read.

### 2.2.2 Noncached Slave Read Sequence

A typical noncached slave read sequence by a J-Bus port is as follows:

- 1. The J-Bus master port issues a read request on J-Bus.

- 2. After decoding the address, the addressed slave port forwards the request to the appropriate noncacheable domain controller. Typically I/O bridge will be responding to noncacheable transactions.

- 3. The J-Bus slave port proceeds with other work while waiting for read data to return. When data returns, the J-Bus slave port drives the data onto J-Bus to the requesting J-Bus port using an encoded J\_ADTYPE[7:0].

### 2.2.3 Noncached Slave Write Sequence

A typical noncached slave write sequence by a J-Bus port is as follows:

- 1. The J-Bus master port issues a write request that includes the write data on J-Bus.

- 2. After decoding the address, the addressed slave port forwards the request and data to the appropriate noncacheable domain controller.

## 2.3 Flow Control Model

Two logical states, AOK and DOK, are used to flow control all address and data packets:

- AOK throttles address delivery for both reads and writes.

- DOK throttles data delivery for writes. DOK is tracked on a per-port basis. DOK is not used for throttling read data or interrupts.

- Some special transactions ignore AOK and DOK.

Masters should not initiate read activity without having room for returning read data.

There is a latency in seeing AOK or DOK state transition for both seeing the transition and stopping any new data. The repeater chips *add* to the latency.

The input queues at all J-Bus ports are sized to accommodate between four and eight cycles worth of overflow. Address and data queues can be sized differently. The minimum overflow requirement for the data queue depends on the target writes a port can accept (64-byte only or mixed 64-byte and 16-byte writes). See Section 1.8.1, "DOK Flow Control for Writes" on page 1-13.

The J-Bus masters are required to have enough room here for the maximum number of outstanding caching requests they support.

The address space-to-agent ID mapping is fixed to make this port-dependent DOK check easy for a master. Having fully programmable base and bounds for all addresses would require that each master track all separate base and bound registers for each port.

## 2.4 J-Bus Port Model

A J-Bus port is identified by a 5-bit field called the *agent ID*. There are, however, a maximum of seven ports, restricted by the number of arbitration requests and J\_PACK wires.

I/O bridge can use more than one agent ID. The additional agent IDs may be useful for J-Bus to J-Bus bridge situations because the arbitration request and J\_PACK limitations may apply just to a local J-Bus.

The address map and interrupt forwarding decode assumes a 5-bit agent ID. The extra bits are software programmable with a reset state that depends on the particular chip. For example, I/O bridge only has two possible agent ID pairs that it can use.

A J-Bus CPU port has two functional interface properties (master and interrupt handler). A J-Bus I/O port has the master and interrupter properties.

The CPU ports include memory controller slave ports.

#### 2.4.1 Master Interface

The master interface property has the following characteristics:

- A J-Bus master has one outgoing request queue.

- Transactions within any destination domain are strongly ordered by the interconnect.

- A J-Bus master port is solely responsible for the ordering of its internal memory events based on its memory model.

## J-Bus Transaction Set

This chapter describes the following topics:

- Transaction Set Requirements

- Transaction Set Terminology

- Transaction Set Summary

- Memory Transactions

- Noncached Data Transactions

- Interrupt Control Transactions

- J\_ADTYPE[7:0], J\_AD[127:0], J\_ADP[3:0]

## 3.1 Transaction Set Requirements

Transaction set requirements follow these guidelines:

- Cacheable transactions are supported on 64-byte sized datums.

- Posted coherency protocol eliminates the need for atomic locks on main memory datums.

- Sun4U architecture interrupt semantics requires delivering some software-defined "opaque" state information from the interrupting source, requiring an interrupt packet with a non-blocking retry for reliable delivery.

- Sun4U system requirement of no atomic operations (CAS, SWAP) on noncached address space. Thus there is no transaction support for these atomic operations or any read-modify-writes because these operations must be performed in the cache on the J-Bus module.

- No systems requirement to support cacheable address space except main memory.

- No requirement for global cache flushing or TLB demap operations in hardware, hence no special transactions to support them. No requirement for posting interrupts to your own port or device.

- No requirement for synchronous reporting of an error on a write to a non-existent or illegal address. The writes are always accepted from the J-Bus master but are thrown away. Logging and reporting errors on writes is implementation specific and not specified by the architecture. Fatal errors, such as address parity errors, cause system reset.

- Sun4U requirement for reporting read data and time-out errors synchronously with the read transaction to the requesting J-Bus master port.

# 3.2 Transaction Set Terminology

The transaction set has four main categories. The asterisk (\*) indicates a wildcard for all transactions having the indicated initial letters.

RD\* (read)

Transaction generated by a master J-Bus port. These transactions initiate all cacheable read activity.

WR\* (write)

Transaction generated by a master J-Bus port. These transactions initiate all memory write activity. A memory controller always services the transaction.

NC\* (noncacheable)

Transactions used for noncacheable read/writes to PCI and I/O bridge CSRs. Although this could be inferred from the address space mapping, special transactions are used to avoid propagating all of the address space definition to all ports (NC\* transactions are not snooped).

INT\* (interrupt)

Generated by a master J-Bus port. Used for direct-to-CPU interrupt requests and handshakes indicating acceptance or refusal of an interrupt packet.

#### J\_PACK

Acknowledgment generated by a J-Bus port on bused unidirectional wires from the J-Bus port to all other J-Bus ports. Generated in response to a previous RD\* or WRI\* transaction.

# 3.3 Transaction Set Summary

Cache-coherent transactions are summarized in TABLE 3-1.

TABLE 3-1

Transaction Set Summary

| Transaction | TRANS[4:0] | Description                |

|-------------|------------|----------------------------|

| Reserved    | 0x00-01    |                            |

| RDD         | 0x02       | ReadToDiscard              |

| RDD         | 0x03       | ReadToDiscard              |

| RDS         | 0x04       | ReadToShare                |

| RDO         | 0x06       | Unsupported                |

| OWN         | 0x07       | Unsupported                |

| INV         | 0x08       | Unsupported                |

| Reserved    | 0x09       |                            |

| NCWRC       | 0x0A       | NonCachedWriteCompressible |

| WRM         | 0x0B       | WriteMerge                 |

| WRB         | 0x0C       | Unsupported                |

| WRBC        | 0x0D       | WritebackCancelled ignored |

| WRI         | 0x0E       | WriteInvalidate            |

| WRI         | 0x0F       | WriteInvalidate            |

| NCRD        | 0x10       | NonCachedRead              |

| NCBRD       | 0x11       | NonCachedBlockRead         |

| NCWR        | 0x12       | NonCachedWrite             |

| NCBWR       | 0x13       | NonCachedBlockWrite        |

| INT         | 0x14       | Interrupt Request          |

| INTACK      | 0x15       | InterruptAck               |

| INTNACK     | 0x16       | InterruptNack              |

| XIR         | 0x17       | Unsupported                |

| Reserved    | 0x18       |                            |

| Reserved    | 0x19       |                            |

| Transaction | TRANS[4:0] | Description |  |

|-------------|------------|-------------|--|

| CHANGE      | 0x1A       | Unsupported |  |

| Reserved    | 0x1B-1E    |             |  |

| IDLE        | 0x1F       | Idle        |  |

TABLE 3-1

Transaction Set Summary (Continued)

### 3.4 Memory Transactions

The section describes memory transactions.

#### 3.4.1 ReadToShare

ReadToShare (RDS) is a request for a cache line for read access (data or instructions). The data is returned by the current owner, if one exists, or the home for the memory location.

If another cache also has this datum, Ctag transitions to S. This S versus E information is provided by J\_ADTYPE during the data transfer, so this cache does not have to monitor J\_PACKs to determine the cache install state.

**Note** – The OpenSPARC T1 Processor processor will always return shared (J\_ADTYPE[2:0] == S).

The sourcing J-Bus port must provide the addressed quadword first and wrap modulo 32 bytes based on the physical address bit AD[5] for successive quadwords as shown in FIGURE 2-1 on page 2-2.

AD[4:0] are ignored, but may be used to output diagnostic information.

If this transaction displaces a dirty victim block in the cache (Ctag state is M or O), a Writeback transaction must be paired atomically with this transaction.

The same error checking applies as for an RD transaction.

Data packet errors detected by the initiating port are the following:

- AD/ADTYPE parity error.

- Timeout.

- Wrong/illegal coherency state for install.

- Illegal ADTYPE driven in any of the data packet cycles. Not necessary to check cycles when ADTYPE provides no additional information.

- Any memory detecting a case of bad J\_PACKs, where no other cache is returning data because of J\_COHACKD, should return a read data error.

### 3.4.2 ReadToDiscard

ReadToDiscard (RDD) is a memory read with intent to discard after first use. RDD is generated by a J-Bus master when that master does not keep the line in its cacheable domain.

The data is wrapped modulo 32 bytes on AD[5] such that the addressed quadword is delivered first.

AD[4:0] is ignored, but may be used to output diagnostic information.

The same error checking applies as for an RD transaction.

Address packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Address map violation. (PA[42]!=1), or address not in range supported by this device.

- Unused bits in AD not checked.

### 3.4.3 WriteInvalidate

WriteInvalidate (WRI) is a coherent write and invalidate request generated by a J-Bus master to write a data block coherently to its home location. It is used for coherent DMA writes. This transaction is used to inject new data into the coherent domain.

The data is written to memory after invalidating any copies in the L1 and L2 caches.

The write to memory can be started before all J\_PACKs for the invalidates have been received, but because J\_PACKs must be synchronized to maintain the in-order correspondence between them and transactions, a subsequent read will not return data until the invalidates have propagated.

In any case, this is not required, since all ports are required to complete all prior invalidates before enabling read return data to be used.

The same error checking applies as for a WRB transaction.

Address packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Address map violation. (PA[42]!=1), or address not in range supported by this device.

- AD[5:0] nonzero.

- Unused bits in AD not checked.

Data packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Illegal ADTYPE driven in any of the data packet cycles. Not necessary to check cycles when ADTYPE provides no additional information.

#### 3.4.4 WriteMerge

**Note** – This transaction is currently only supported by the OpenSPARC T1 Processor processor and I/O bridge, although the processor never masters a WRM.

WriteMerge (WRM) writes 0–64 bytes to cacheable memory. This transaction is the same as WriteInvalidateSelf, but with 64 bits of arbitrary byte enables.

WRM has a format similar to WRI, but with a different Transaction Type and a 64-bit byte-enable mask. WRM writes 0-64 bytes in an aligned line, using a byte-enable mask, to cacheable memory.

Format is:

Address cycle:

J\_AD[127:64] - Byte enables[63:0].

J\_AD[63:48] -- Reserved

$J_AD[47:43]$  -- Transaction Type == 0x0B (WRM)

J\_AD[42:00] -- Address (AD[5:0] effectively ignored)

Data Cycles:

J\_AD[127:0] -- Data payload, bytes 0-15.

J\_AD[127:0] -- Data payload, bytes 16-31.

J\_AD[127:0] -- Data payload, bytes 32-47.

J\_AD[127:0] -- Data payload, bytes 48-63.

Since the WRM is a coherent transaction, it is processed in the snoop queue, and produces COHACK responses. Arbitrary encodings on byte enables (BE[63:0]) are supported. The BE[63:0] field is in the same order as on NCRD/NCWR, which appears to be that BE[0] (on the right end of the field) corresponds to Byte[0] which is on the left end of the data (J\_AD[127:120]).

# 3.5 Noncached Data Transactions

No snooping is performed on these transactions, and data from these transactions is not cached by the requester.

#### 3.5.1 NonCachedRead

NonCachedRead (NCRD) reads non-DRAM locations within a 16-byte region. The bytes read within the 16-byte region are specified by the byte-enable field. Devices do not need to support all combinations of byte enables.

The CPU will read 1, 2, 4, 8, and 16 bytes with this transaction. The byte location is specified with a byte enable. The address is either byte, halfword, word, doubleword, or 16-byte aligned (points to the first byte enable).

PCI can initiate reads with random byte enables. Still, the address should point to the first valid byte enable.

No snoop lookup operation is done.

Main memory cannot be read with this transaction.

**Note** – The 64-Gbyte noncached spaces allocated for the OpenSPARC T1 Processor processor have been aliased to the 64-Gbyte cacheable spaces allocated for the OpenSPARC T1 Processor processor. As a result, OpenSPARC T1 Processor main memory *can* be read with this transaction using the aliased address space. This aliasing is intended only for design bring-up, and not for normal operation.

Address packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Address map violation. (PA[42]!=0) or address not in range supported by this device.

- Not checked unused bits in AD.

- Not checked byte-enable and PA[3:0] mismatch, or illegal byte enable.

Data packet errors detected by the initiating port are the following:

- AD/ADTYPE parity error.

- Timeout.

- Illegal ADTYPE driven in any of the data packet cycles. Not necessary to check cycles when ADTYPE provides no additional information.

### 3.5.2 NonCachedBlockRead

With a NonCachedBlockRead (NCBRD) request transaction, 64 bytes of non-DRAM data is read by the master J-Bus port.

This transaction is similar to NCRD, except for the following:

- No byte enable. The data is aligned on a 64-byte boundary (AD[5:0]== 0x0).

- AD[5:0] must be 0x0.

The same error checking applies as for an NCRD.

#### 3.5.3 NonCachedWrite

A NonCachedWrite (NCWR) writes non-DRAM locations within an aligned 16-byte region. The bytes written within the 16-byte region are specified by the byte-enable field. Devices do not need to support all combinations of byte enable, but they must complete the data transfer.

NCWR is generated by a J-Bus master port to write a noncached address space, including system registers and slave address space of other slave J-Bus ports.

NCWR is written as specified by a 16-bit byte enable to slave devices that support writes with arbitrary byte enables (mainly graphics devices).

An arbitrary number of 0–16 bytes are not allowed in the byte enables. All J-Bus masters that generate NCWR must comply with the following rule:

If both byte enable[15:8] and byte enable[7:0] are non-zero, they must be equal.

This requirement enables the CPU to compress successive 8-byte stores to 16 bytes, for example.

PA[3:0] should point to the byte indicated by the first non-zero byte enable, starting with byte 0. NCRDs also follow this rule.

Exception – PCI-initiated NCWRs from I/O bridge can just forward the same address that originally appeared on PCI. For some PCI transactions, the address is 8-byte or 4-byte aligned, but the byte enables are not. This means that the first byte enable, and PA[2:0], are accurate to the word or doubleword, depending on the width of the PCI bus source.

The implication is that SPARC VIS partial-store instructions, which use 8-byte aligned addresses with random byte enables, will show up on J-Bus with addresses that are no longer 8-byte aligned.

PCI will use [3:0] for its initial address and data beat.

Interpretation of arbitrary byte enables (that is, those that are not aligned on 1, 2, 4, 8, and 16-byte boundaries) by a slave J-Bus port that does not support that interpretation is implementation specific.

No snoop lookup operation is done.

Main memory cannot be written with this transaction.

**Note** – The 64-Gbyte noncached spaces allocated for the OpenSPARC T1 Processor processor have been aliased to the 64-Gbyte cacheable spaces allocated for the OpenSPARC T1 Processor processor. As a result, OpenSPARC T1 main memory *can* be read with this transaction using the aliased address space. This aliasing is intended only for design bring-up, and not for normal operation.

#### **Error Handling:**

Writes fail silently and errors are reported asynchronously. NCWR is dropped by the J-Bus slave port on any type of bus or timeout error. If the J-Bus slave port drops the transaction, the J-Bus slave port may log and report the transaction using an interrupt.

Address packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Address map violation. (PA[42]!=0), or address not in range supported by this device.

- Not checked unused bits in AD.

- Not checked byte-enable/PA[3:0] mismatch.

Data packet errors detected by the target port are the following:

- AD/ADTYPE parity error.

- Illegal ADTYPE driven in any of the data packet cycles. Not necessary to check cycles when ADTYPE provides no additional information.

### 3.5.4 NonCachedWriteCompressible

**Note** – The OpenSPARC T1 Processor processor does not support special handling of this transaction. If the processor is the target of an NCWRC transaction, it will be handled like an NCWR.

The NonCachedWriteCompressible (NCWRC) transaction is the same as NCWR, except downstream bus bridges are allowed to compress multiple NCWRCs to form fewer transactions with larger bursts. All NCWRCs are compressible. However, the compression logic should track J-Bus address order, so an intervening non-compressible operation (read or write) to that target space should break the compression.

#### 3.5.5 NonCachedBlockWrite

With the NonCachedBlockWriteRequest (NCBWR) transaction, 64 bytes of noncached data are written by the master J-Bus port. The transaction is generated by a J-Bus master port for block write to a noncached address space.

NCBWR is similar to NCWR except with no byte enables. The data is aligned on a 64-byte boundary (AD[5:0] = 0x0).

The same error checking applies as for NCWR.

### 3.6 Interrupt Control Transactions

Interrupt control transactions are unlike a data transaction in that the 64-byte datum does not have any address space associated with it. No snooping is performed, and the datum is not cached by the requestor.

#### 3.6.1 Interrupt Request

Interrupt (INT) request delivery is not stalled by AOK or DOK.

INT sends an interrupt. The target of the interrupt is specified in the address.

The CPUs are the only interrupt receivers and have a one-deep pipeline between acceptance and complete processing of the interrupt.

No J\_PACKs are associated with this transaction.

INT is generated by an interrupter master J-Bus port for delivering packetized interrupts consisting of a 16-byte block of data to a destination J-Bus CPU port. INT is used for sending interrupts from I/O devices, reporting asynchronous events and errors to interrupt handler J-Bus ports. An INT *cannot* be sent to itself.

The interrupt transaction packet does not contain a physical address. Instead, it carries an interrupt target ID, which is the same as the target's CPU thread ID.

In the OpenSPARC T1 Processor processor, there are 32 threads which effectively act as 32 software-visible processors. To be able to target interrupts to any processor or thread, the 5-bit interrupt target ID is defined as the CPU ID (thread ID) and the OpenSPARC T1 Processor processor becomes the target of all interrupts issued onto the J-Bus.

Address Cycle:

J\_AD[127:64] is a copy of J\_AD[63:0].

J\_AD[63:48] is reserved.

J\_AD[47:43] is 0x14 (INT transaction).

J\_AD[42:41] is reserved (zero).

J\_AD[40:36] is the CPU ID of the target port.

J\_AD[35:31] is the agent ID of the source port.

J\_AD[30:0] is reserved (zero).

Data cycle 1: J\_AD[127:64] has mondo data 0. J\_AD[63:0] has mondo data 1.

Data cycle 2: All zeros.

Data cycle 3: All zeros.

Data cycle 4: All zeros.

The OpenSPARC T1 CPU has mondo receive registers for receipt of 16 bytes of the interrupt write packet for each thread destination.

The following rules apply at the mondo receive interface of the destination interrupt handler J-Bus port:

If an InterruptAck (INTACK) transaction is subsequently sent from the target, the INT request has been ACKed by the destination. The sender can assume the interrupt has been sent, but complete processing by the target is not guaranteed. The only way ensure complete processing is to send another interrupt and wait for another InterruptAck. An interruptee will not InterruptAck a second interrupt, unless that interruptee has completed processing of the first interrupt.

- If an InterruptNack (INTNACK) transaction is subsequently sent from the target, the INT request has been NACKed by the destination. *NACKed* means the INT packet has been ignored because the CPU software is still processing a prior INT packet.

- The sender may try again by issuing another INT request. The retry is stateless. The target retains no information about the NACKed transaction. It is not required that the INT packet get sent again later, like PCI retry rules, but typically the INT packet will be sent again under software or hardware retry mechanisms.

This means the sender must retain enough state to possibly retry if the INT gets NACKed.