# OpenSPARC<sup>™</sup> T1 Microarchitecture Specification

Sun Microsystems, Inc. www.sun.com

Part No. 819-6650-11 April 2008

Submit comments about this document at: <a href="http://www.sun.com/hwdocs/feedback">http://www.sun.com/hwdocs/feedback</a>

Copyright © 2008 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology embodied in the product that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

U.S. Government Rights - Commercial software. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

Use is subject to license terms.

This distribution may include materials developed by third parties.

Sun, Sun Microsystems, the Sun logo, Solaris, OpenSPARC T1 and UltraSPARC are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon architecture developed by Sun Microsystems, Inc.

UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd.

The Adobe logo is a registered trademark of Adobe Systems, Incorporated.

Products covered by and information contained in this service manual are controlled by U.S. Export Control laws and may be subject to the export or import laws in other countries. Nuclear, missile, chemical biological weapons or nuclear maritime end uses or end users, whether direct or indirect, are strictly prohibited. Export or reexport to countries subject to U.S. embargo or to entities identified on U.S. export exclusion lists, including, but not limited to, the denied persons and specially designated nationals lists is strictly prohibited.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright © 2008 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, Etats-Unis. Tous droits réservés.

Sun Microsystems, Inc. détient les droits de propriété intellectuels relatifs à la technologie incorporée dans le produit qui est décrit dans ce document. En particulier, et ce sans limitation, ces droits de propriété intellectuelle peuvent inclure un ou plus des brevets américains listés à l'adresse http://www.sun.com/patents et un ou les brevets supplémentaires ou les applications de brevet en attente aux Etats - Unis et dans les autres pays.

L'utilisation est soumise aux termes de la Licence.

Cette distribution peut comprendre des composants développés par des tierces parties.

Sun, Sun Microsystems, le logo Sun, Solaris, OpenSPARC T1 et UltraSPARC sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exlusivement par X/Open Company, Ltd.

Le logo Adobe. est une marque déposée de Adobe Systems, Incorporated.

Les produits qui font l'objet de ce manuel d'entretien et les informations qu'il contient sont regis par la legislation americaine en matiere de controle des exportations et peuvent etre soumis au droit d'autres pays dans le domaine des exportations et importations. Les utilisations finales, ou utilisateurs finaux, pour des armes nucleaires, des missiles, des armes biologiques et chimiques ou du nucleaire maritime, directement ou indirectement, sont strictement interdites. Les exportations ou reexportations vers des pays sous embargo des Etats-Unis, ou vers des entites figurant sur les listes d'exclusion d'exportation americaines, y compris, mais de maniere non exclusive, la liste de personnes qui font objet d'un ordre de ne pas participer, d'une facon directe ou indirecte, aux exportations des produits ou des services qui sont regi par la legislation americaine en matiere de controle des exportations et la liste de ressortissants specifiquement designes, sont rigoureusement interdites.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON.

## Contents

### Preface xxiii

1.

| Oper | nSPARC | CT1 Overv                                 | view 1–1                         |  |

|------|--------|-------------------------------------------|----------------------------------|--|

| 1.1  | Introd | ntroducing the OpenSPARC T1 Processor 1-1 |                                  |  |

| 1.2  | Functi | onal Desci                                | ription 1–2                      |  |

| 1.3  | OpenS  | SPARC T1                                  | Components 1-4                   |  |

|      | 1.3.1  | SPARC C                                   | Core 1–4                         |  |

|      |        | 1.3.1.1                                   | Instruction Fetch Unit 1–6       |  |

|      |        | 1.3.1.2                                   | Execution Unit 1–6               |  |

|      |        | 1.3.1.3                                   | Load/Store Unit 1–6              |  |

|      |        | 1.3.1.4                                   | Floating-Point Frontend Unit 1–7 |  |

|      |        | 1.3.1.5                                   | Trap Logic Unit 1–7              |  |

|      |        | 1.3.1.6                                   | Stream Processing Unit 1-8       |  |

|      | 1.3.2  | CPU-Ca                                    | che Crossbar 1–8                 |  |

|      | 1.3.3  | Floating                                  | -Point Unit 1–9                  |  |

|      | 1.3.4  | L2-Cache                                  | e 1–10                           |  |

|      | 1.3.5  | DRAM C                                    | Controller 1–11                  |  |

|      | 1.3.6  | I/O Brid                                  | ge 1–11                          |  |

|      | 1.3.7  | J-Bus Int                                 | erface 1–11                      |  |

|      | 1.3.8  | Serial Sy                                 | stem Interface 1–12              |  |

1.3.9 Electronic Fuse 1–12

- 2. SPARC Core 2–1

- 2.1 SPARC Core Overview and Terminology 2–2

- 2.2 SPARC Core I/O Signal List 2–5

- 2.3 Instruction Fetch Unit 2–6

- 2.3.1 SPARC Core Pipeline 2–7

- 2.3.2 Instruction Fetch 2–9

- 2.3.3 Instruction Registers and Program Counter Registers 2–9

- 2.3.4 Level 1 Instruction Cache 2–10

- 2.3.5 I-Cache Fill Path 2–11

- 2.3.6 Alternate Space Identifier Accesses, I-Cache Line Invalidations, and Built-In Self-Test Accesses to the I-Cache 2–12

- 2.3.7 I-Cache Miss Path 2–12

- 2.3.8 Windowed Integer Register File 2–14

- 2.3.9 Instruction Table Lookaside Buffer 2–16

- 2.3.10 Thread Selection Policy 2–16

- 2.3.11 Thread States 2–17

- 2.3.12 Thread Scheduling 2–19

- 2.3.13 Rollback Mechanism 2–20

- 2.3.14 Instruction Decode 2–21

- 2.3.15 Instruction Fetch Unit Interrupt Handling 2–21

- 2.3.16 Error Checking and Logging 2–22

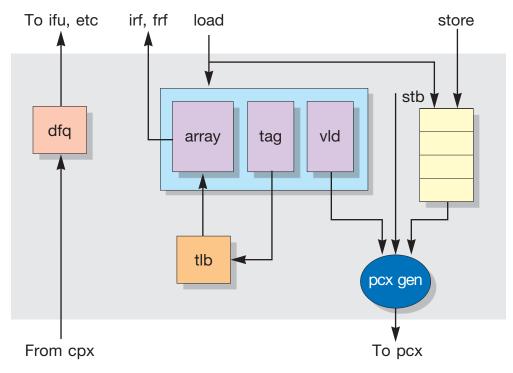

- 2.4 Load Store Unit 2–22

- 2.4.1 LSU Pipeline 2–23

- 2.4.2 Data Flow 2–23

- 2.4.3 Level 1 Data Cache (D-Cache) 2–24

- 2.4.4 Data Translation Lookaside Buffer 2–25

- 2.4.5 Store Buffer 2–26

- 2.4.6 Load Miss Queue 2–27

- 2.4.7 Processor to Crossbar Interface Arbiter 2–27

- 2.4.8 Data Fill Queue 2–28

- 2.4.9 ASI Queue and Bypass Queue 2–28

- 2.4.10 Alternate Space Identifier Handling in the Load Store Unit 2–29

- 2.4.11 Support for Atomic Instructions (CAS, SWAP, LDSTUB) 2–29

- 2.4.12 Support for MEMBAR Instructions 2–30

- 2.4.13 Core-to-Core Interrupt Support 2–30

- 2.4.14 Flush Instruction Support 2–30

- 2.4.15 Prefetch Instruction Support 2–31

- 2.4.16 Floating-Point BLK-LD and BLK-ST Instructions Support 2–31

- 2.4.17 Integer BLK-INIT Loads and Stores Support 2–32

- 2.4.18 STRM Load and STRM Store Instruction Support 2–32

- 2.4.19 Test Access Port Controller Accesses and Forward Packets Support 2–32

- 2.4.20 SPARC Core Pipeline Flush Support 2–33

- 2.4.21 LSU Error Handling 2–33

- 2.5 Execution Unit 2–34

- 2.6 Floating-Point Frontend Unit 2–36

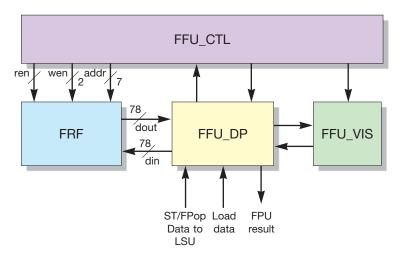

- 2.6.1 Functional Description of the FFU 2–36

- 2.6.2 Floating-Point Register File 2–37

- 2.6.3 FFU Control (FFU\_CTL) 2–37

- 2.6.4 FFU Data-Path (FFU\_DP) 2–38

- 2.6.5 FFU VIS (FFU\_DP) 2–38

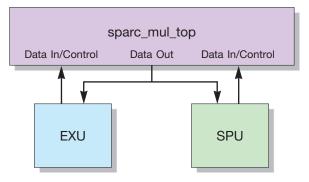

- 2.7 Multiplier Unit 2–38

- 2.7.1 Functional Description of the MUL 2–38

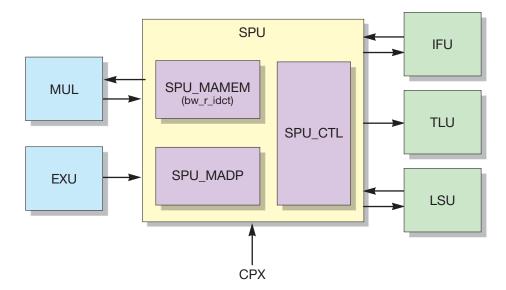

- 2.8 Stream Processing Unit 2–39

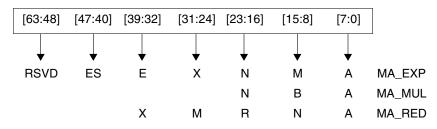

- 2.8.1 ASI Registers for the SPU 2–39

- 2.8.2 Data Flow of Modular Arithmetic Operations 2–41

- 2.8.3 Modular Arithmetic Memory (MA Memory) 2–41

- 2.8.4 Modular Arithmetic Operations 2–42

- 2.9 Memory Management Unit 2–44

- 2.9.1 The Role of MMU in Virtualization 2–45

- 2.9.2 Data Flow in MMU 2–46

- 2.9.3 Structure of Translation Lookaside Buffer 2–46

- 2.9.4 MMU ASI Operations 2–48

- 2.9.5 Specifics on TLB Write Access 2–49

- 2.9.6 Specifics on TLB Read Access 2–49

- 2.9.7 Translation Lookaside Buffer Demap 2–49

- 2.9.8 TLB Auto-Demap Specifics 2–50

- 2.9.9 TLB Entry Replacement Algorithm 2–50

- 2.9.10 TSB Pointer Construction 2–50

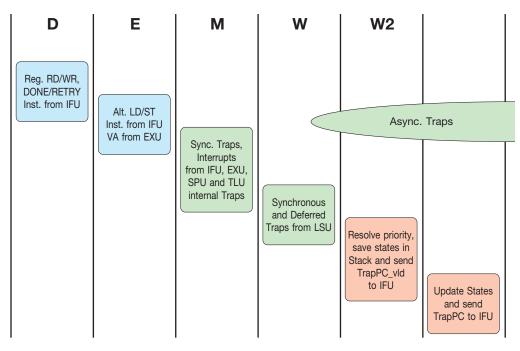

- 2.10 Trap Logic Unit 2–51

- 2.10.1 Architecture Registers in the Trap Logic Unit 2–53

- 2.10.2 Trap Types 2–54

- 2.10.3 Trap Flow 2–56

- 2.10.4 Trap Program Counter Construction 2–58

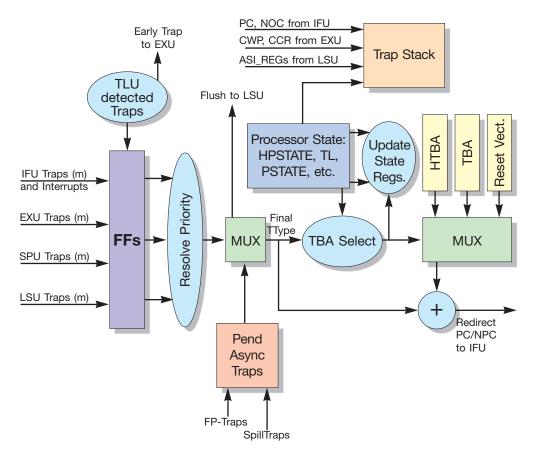

- 2.10.5 Interrupts 2-58

- 2.10.6 Interrupt Flow 2–59

- 2.10.7 Interrupt Behavior and Interrupt Masking 2–62

- 2.10.8 Privilege Levels and States of a Thread 2–62

- 2.10.9 Trap Modes Transition 2–63

- 2.10.10 Thread States Transition 2–64

- 2.10.11 Content Construction for Processor State Registers 2–65

- 2.10.12 Trap Stack 2–66

- 2.10.13 Trap (Tcc) Instructions 2–67

- 2.10.14 Trap Level 0 Trap for Hypervisor 2–67

- 2.10.15 Performance Control Register and Performance Instrumentation Counter 2–67

- 2.11 Core Debug Features 2–69

- 2.11.1 Resetting a Thread 2–69

- 2.11.2 Stopping and Starting a Thread 2–70

- 2.11.3 Interrupting a Thread 2–70

- 2.11.4 Shadow Scan 2-70

#### 3. CPU-Cache Crossbar 3–1

- 3.1 Functional Description 3–1

- 3.1.1 CPU-Cache Crossbar Overview 3–1

- 3.1.2 CCX Packet Delivery 3–2

- 3.1.3 Processor-Cache Crossbar Packet Delivery 3–3

- 3.1.4 Cache-Processor Crossbar Packet Delivery 3–4

- 3.1.5 CPX and PCX Packet Formats 3–5

#### 3.2 PCX Packet Fields 3–10

- 3.2.1 Request Type 3–10

- 3.2.2 Non-Cacheable Bit 3–10

- 3.2.3 CPU ID and Thread ID 3–11

- 3.2.4 Invalidate 3-11

- 3.2.5 Prefetch 3–11

- 3.2.6 Block-Init Store 3–11

- 3.2.7 Replacement L1 Way 3–11

- 3.2.8 Transaction Size 3–11

- 3.2.9 Transaction Address 3–12

- 3.2.10 Data 3–12

- 3.3 CPX Packet Fields 3–13

- 3.3.1 Valid 3-13

- 3.3.2 Transaction Type 3–13

- 3.3.3 L2 Miss 3–13

- 3.3.4 ERR 3–13

- 3.3.5 Non-Cacheable Bit 3–13

- 3.3.6 Thread ID 3-14

- 3.3.7 Way and Way Valid 3-14

- 3.3.8 Four-byte Fill 3–14

- 3.3.9 Atomic 3–14

- 3.3.10 Prefetch 3-14

- 3.3.11 Data 3–15

- 3.4 Processing of PCX Transactions 3–16

- 3.4.1 Load 3–16

- 3.4.2 Prefetch 3–16

- 3.4.3 D-cache Invalidate 3–17

- 3.4.4 Instruction Fill 3–17

- 3.4.5 I-cache Invalidate 3–17

- 3.4.6 Store 3–18

- 3.4.7 Block Store 3–18

- 3.4.8 Block Init Store 3–18

- 3.4.9 CAS (Compare and Swap) 3–19

- 3.4.10 Swap/Ldstub 3-19

- 3.4.11 Stream Load 3–19

- 3.4.12 Stream Store 3–19

- 3.4.13 External Floating-Point Operations 3–20

- 3.4.14 Interrupt Requests 3–20

- 3.4.15 L2 Evictions 3–21

- 3.4.16 L2 Errors 3–21

- 3.4.17 Forwarded Requests 3–21

- 3.4.18 Writes to the INT\_VEC\_DIS Register 3–21

- 3.4.19 Hardware Interrupts 3–22

- 3.5 CCX I/O List 3–23

- 3.6 CCX Timing Diagrams 3–27

- 3.6.1 Speculative Request from the Core 3–30

- 3.7 PCX Internal Blocks Functional Description 3–34

- 3.7.1 PCX Overview 3–34

- 3.7.2 PCX Arbiter Data Flow 3–36

- 3.7.3 PCX Arbiter Control Flow 3–37

- 3.8 CPX Internal Blocks Functional Description 3–38

- 3.8.1 CPX Overview 3–38

- 3.8.2 CPX Arbiters 3–38

- 4. Level 2 Cache 4–1

- 4.1 L2-Cache Functional Description 4–1

- 4.1.1 L2-Cache Overview 4–1

- 4.1.2 L2-Cache Single Bank Functional Description 4–2

- 4.1.2.1 Arbiter 4–4

- 4.1.2.2 L2 Tag 4–4

- 4.1.2.3 L2 VUAD States 4-4

- 4.1.2.4 L2 Data (scdata) 4–5

- 4.1.2.5 Input Queue 4–5

- 4.1.2.6 Output Queue 4–6

- 4.1.2.7 Snoop Input Queue 4–6

- 4.1.2.8 Miss Buffer 4–6

- 4.1.2.9 Fill Buffer 4–7

- 4.1.2.10 Writeback Buffer 4–8

- 4.1.2.11 Remote DMA Write Buffer 4–8

- 4.1.2.12 L2-Cache Directory 4–8

- 4.1.3 L2-Cache Pipeline 4–9

- 4.1.3.1 L2-Cache Transaction Types 4–9

- 4.1.3.2 L2-Cache Pipeline Stages 4–10

- 4.1.4 L2-Cache Instruction Descriptions 4–12

- 4.1.4.1 Loads 4–12 4.1.4.2 Ifetch 4–12 4.1.4.3 Stores 4–13 4.1.4.4 Atomics 4–13 4.1.4.5 J-Bus Interface Instructions 4–14 4.1.4.6 Eviction 4–16 4.1.4.7 Fill 4–16 4.1.4.8 Other Instructions 4–16

- 4.1.5 L2-Cache Memory Coherency and Instruction Ordering 4–17

- 4.2 L2-Cache I/O LIST 4–18

#### 5. Input/Output Bridge 5–1

- 5.1 Functional Description 5–1

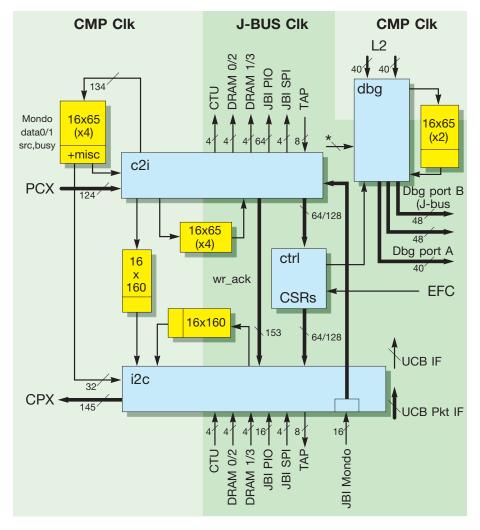

- 5.1.1 IOB Interfaces 5–2

- 5.1.2 UCB Interface 5-4

- 5.1.2.1 UCB Request and Acknowledge Packets 5–4

- 5.1.2.2 UCB Interrupt Packet 5–6

- 5.1.2.3 UCB Interface Packet Example 5–6

- 5.1.3 IOB Address Map 5–7

- 5.1.4 IOB Block Diagram 5–8

- 5.1.5 IOB Transactions 5–9

- 5.1.6 IOB Interrupts 5–10

- 5.1.7 IOB Miscellaneous Functionality 5–11

- 5.1.8 IOB Errors 5–11

- 5.1.9 Debug Ports 5–12

- 5.2 I/O Bridge Signal List 5–12

#### 6. J-Bus Interface 6–1

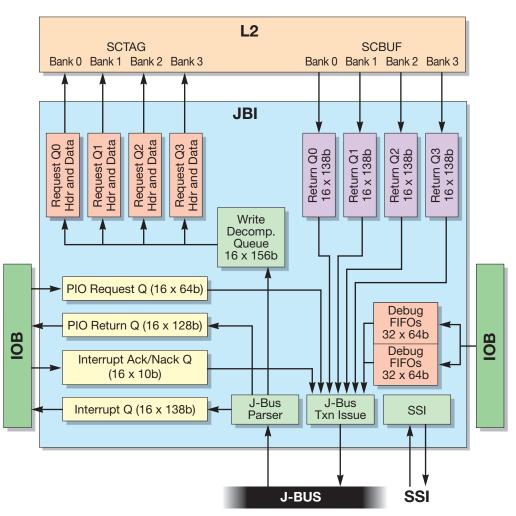

- 6.1 Functional Description 6–1

- 6.1.1 J-Bus Requests to the L2-Cache 6–3

- 6.1.1.1 Write Requests to the L2-Cache 6–3

- 6.1.1.2 Read Requests to the L2-Cache 6–4

- 6.1.1.3 Flow Control 6–4

- 6.1.2 I/O Buffer Requests to the J-Bus 6-4

- 6.1.3 J-Bus Interrupt Requests to the IOB 6–5

- 6.1.4 J-Bus Interface Details 6–5

- 6.1.5 Debug Port to the J-Bus 6–6

- 6.1.6 J-Bus Internal Arbitration 6–6

- 6.1.7 Error Handling in JBI 6–7

- 6.1.8 Performance Counters 6–7

- 6.2 I/O Signal list 6–8

#### 7. Floating-Point Unit 7–1

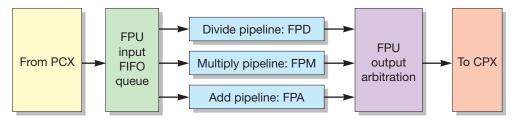

- 7.1 Functional Description 7–1

- 7.1.1 Floating-Point Instructions 7–4

- 7.1.2 FPU Input FIFO Queue 7–5

- 7.1.3 FPU Output Arbitration 7–6

- 7.1.4 Floating-Point Adder 7-6

- 7.1.5 Floating-Point Multiplier 7–7

- 7.1.6 Floating-Point Divider 7-8

- 7.1.7 FPU Power Management 7–9

- 7.1.8 Floating-Point State Register Exceptions and Traps 7–10

- 7.1.8.1 Overflow and Underflow 7–12

- 7.1.8.2 IEEE Exception List 7–13

- 7.2 I/O Signal list 7–15

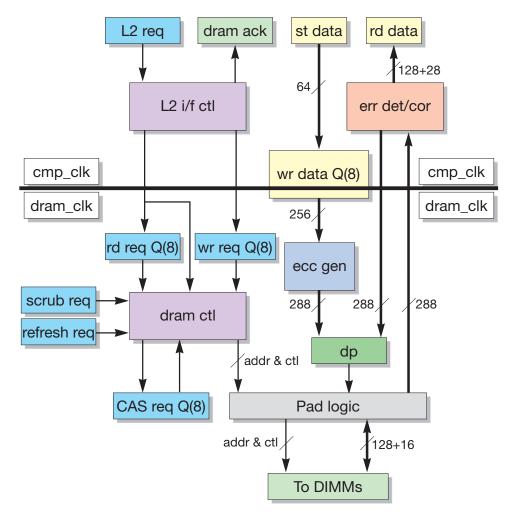

#### 8. DRAM Controller 8–1

| o.1 Functional Description o- | 8.1 | Functional Description | 8–1 |

|-------------------------------|-----|------------------------|-----|

|-------------------------------|-----|------------------------|-----|

- 8.1.1 Arbitration Priority 8–3

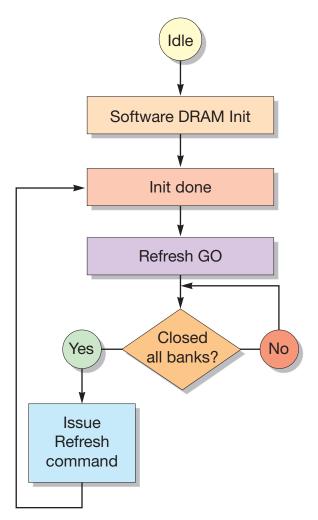

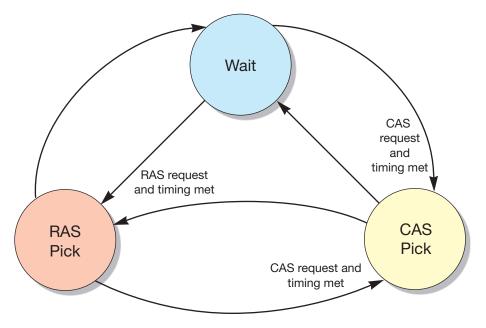

- 8.1.2 DRAM Controller State Diagrams 8–4

- 8.1.3 Programmable Features 8–5

- 8.1.4 Errors 8–6

- 8.1.5 Repeatability and Visibility 8–6

- 8.1.6 DDR-II Addressing 8–7

- 8.1.7 DDR-II Supported Features 8–8

- 8.2 I/O Signal List 8–9

#### 9. Error Handling 9–1

- 9.1 Error Handling Overview 9–1

- 9.1.1 Error Reporting and Logging 9–2

- 9.1.2 Error Traps 9–2

- 9.2 SPARC Core Errors 9–3

- 9.2.1 SPARC Core Error Registers 9–3

- 9.2.2 SPARC Core Error Protection 9–4

- 9.2.3 SPARC Core Error Correction 9–4

- 9.3 L2-Cache Errors 9–5

- 9.3.1 L2-Cache Error Registers 9–5

- 9.3.2 L2-Cache Error Protection 9–6

- 9.3.3 L2-Cache Correctable Errors 9–6

- 9.3.4 L2-Cache Uncorrectable Errors 9–7

- 9.4 DRAM Errors 9–8

- 9.4.1 DRAM Error Registers 9–8

- 9.4.2 DRAM Error Protection 9–9

- 9.4.3 DRAM Correctable Errors 9–9

- 9.4.4 DRAM Uncorrectable and Addressing Errors 9–9

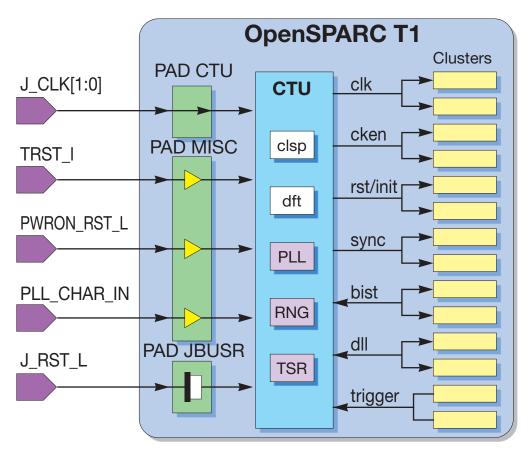

#### 10. Clocks and Resets 10–1

- 10.1 Functional Description 10–1

- 10.1.1 OpenSPARC T1 Processor Clocks 10-1

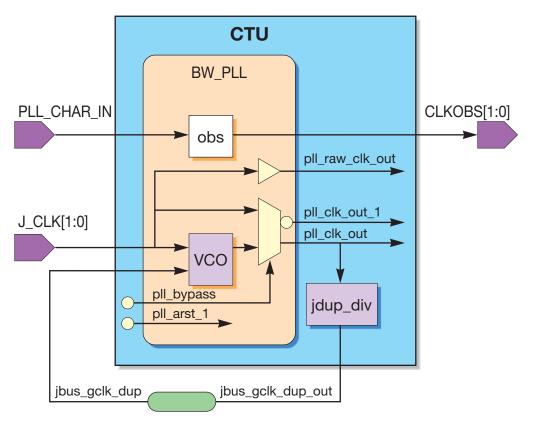

- 10.1.1.1 Phase-Locked Loop 10–3

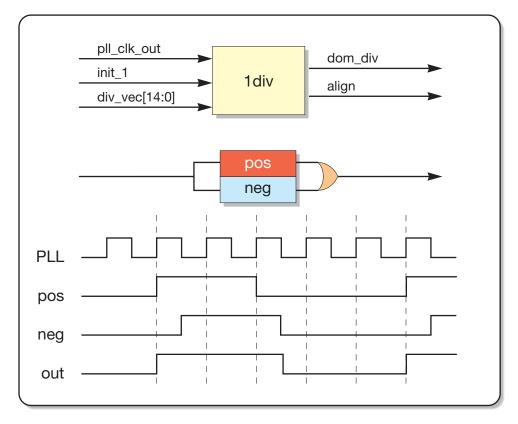

- 10.1.1.2 Clock Dividers 10-4

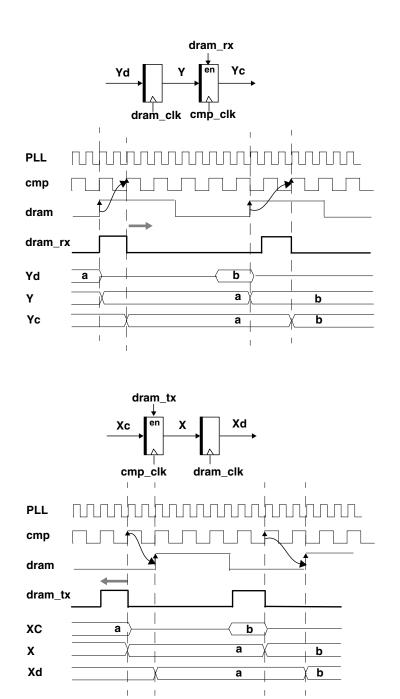

- 10.1.1.3 Clock Domain Crossings 10–5

- 10.1.1.4 Clock Gating 10–7

- 10.1.1.5 Clock Stop 10–7

- 10.1.1.6 Clock Stretch 10-8

- 10.1.1.7 Clock *n*-Step 10–8

- 10.1.1.8 Clock Signal Distribution 10–8

- 10.1.2 OpenSPARC T1 Processor Resets 10–10

- 10.1.2.1 Power-On Reset (PWRON\_RST\_L) 10–10

- 10.1.2.2 J-Bus Reset (J\_RST\_L) 10–11

- 10.1.2.3 Reset Sequence 10–11

- 10.1.2.4 Debug Initialization 10–15

- 10.2 I/O Signal list 10–15

# Figures

| FIGURE 1-1  | OpenSPARC T1 Processor Block Diagram 1-3                            |

|-------------|---------------------------------------------------------------------|

| FIGURE 1-2  | SPARC Core Pipeline 1–5                                             |

| FIGURE 1-3  | CCX Block Diagram 1–9                                               |

| FIGURE 2-1  | SPARC Core Block Diagram 2-2                                        |

| FIGURE 2-2  | Physical Location of Functional Units on an OpenSPARC T1 SPARC Core |

| FIGURE 2-3  | Virtualization of Software Layers 2–4                               |

| FIGURE 2-4  | SPARC Core Pipeline and Support Structures 2–8                      |

| FIGURE 2-5  | Frontend of the SPARC Core Pipeline 2–9                             |

| FIGURE 2-6  | I-Cache Fill Path 2–11                                              |

| FIGURE 2-7  | I-Cache Miss Path 2–13                                              |

| FIGURE 2-8  | IARF and IWRF File Structure 2–15                                   |

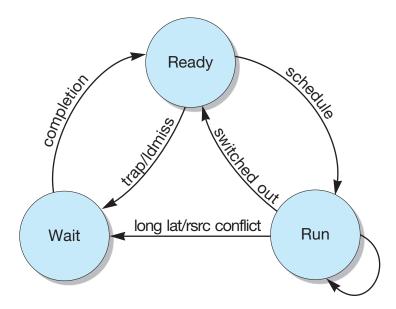

| FIGURE 2-9  | Basic Transition of Non-Active States 2–17                          |

| FIGURE 2-10 | Thread State Transition of an Active Thread 2–18                    |

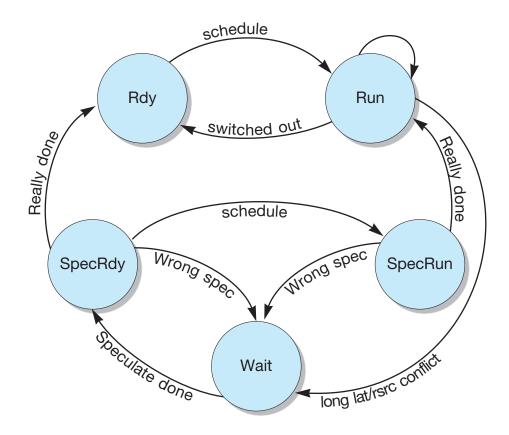

| FIGURE 2-11 | State Transition for a Thread in Speculative States 2–19            |

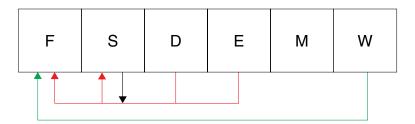

| FIGURE 2-12 | Rollback Mechanism Pipeline Graph 2-20                              |

| FIGURE 2-13 | LSU Pipeline Graph 2-23                                             |

| FIGURE 2-14 | LSU Data Flow Concept 2–24                                          |

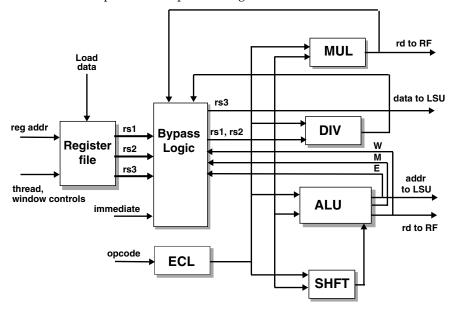

| FIGURE 2-15 | Execution Unit Diagram 2-34                                         |

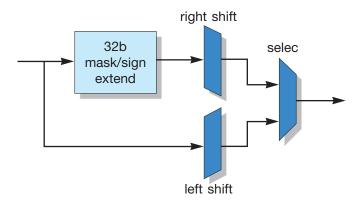

| FIGURE 2-16 | Shifter Block Diagram 2-35                                          |

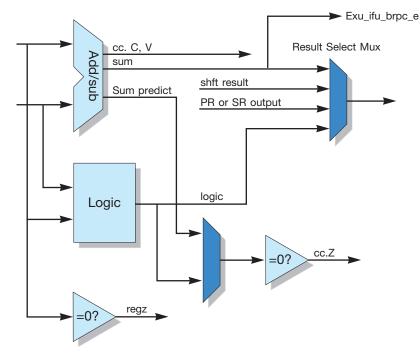

| FIGURE 2-17 | ALU Block Diagram 2–35                                              |

|             |                                                                     |

|             |                                                                     |

2–3

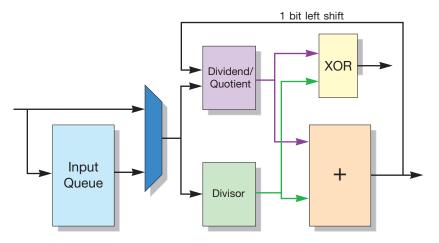

|             | IDIV Block Diagram 2–36                                                      |

|-------------|------------------------------------------------------------------------------|

| FIGURE 2-18 | -                                                                            |

| FIGURE 2-19 | Top-Level FFU Block Diagram 2–37                                             |

| FIGURE 2-20 | Multiplexor (MUL) Block Diagram 2–38                                         |

| FIGURE 2-21 | Layout of MA_ADDR Register Bit Fields 2–39                                   |

| FIGURE 2-22 | Data Flow of Modular Arithmetic Operations 2–41                              |

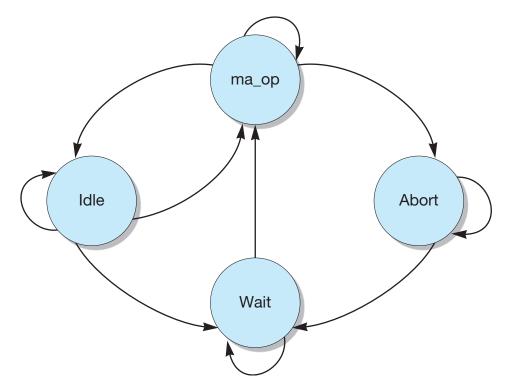

| FIGURE 2-23 | State Transition Diagram Illustrating MA Operations 2–42                     |

| FIGURE 2-24 | Multiply Function Result Generation Sequence Pipeline Diagram 2–44           |

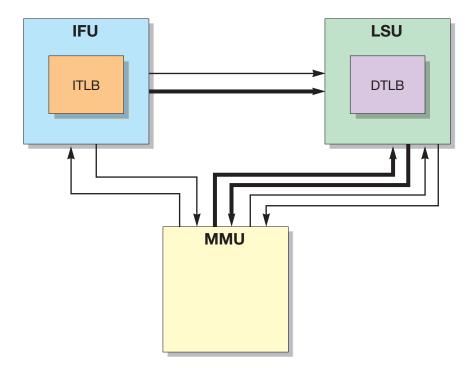

| FIGURE 2-25 | MMU and TLBs Relationship 2-45                                               |

| FIGURE 2-26 | Virtualization Diagram 2-45                                                  |

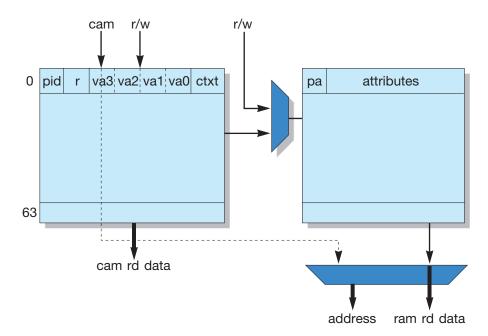

| FIGURE 2-27 | Translation Lookaside Buffer Structure 2-47                                  |

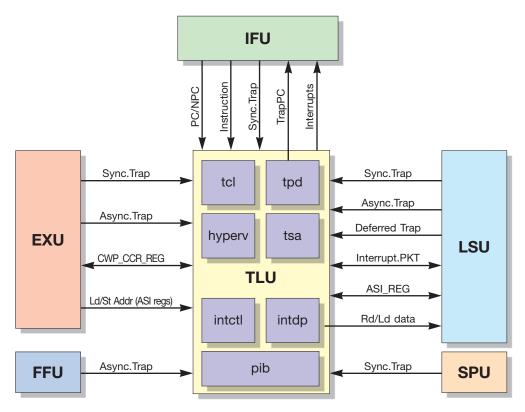

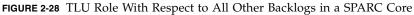

| FIGURE 2-28 | TLU Role With Respect to All Other Backlogs in a SPARC Core 2–52             |

| FIGURE 2-29 | Trap Flow Sequence 2-56                                                      |

| FIGURE 2-30 | Trap Flow With Respect to the Hardware Blocks 2–57                           |

| FIGURE 2-31 | Flow of Hardware and Vector Interrupts 2–59                                  |

| FIGURE 2-32 | Flow of Reset or Idle or Resume Interrupts 2–60                              |

| FIGURE 2-33 | Flow of Software and Timer Interrupts 2–61                                   |

| FIGURE 2-34 | Trap Modes Transition 2–63                                                   |

| FIGURE 2-35 | Thread State Transition 2–64                                                 |

| FIGURE 2-36 | PCR and PIC Layout 2–68                                                      |

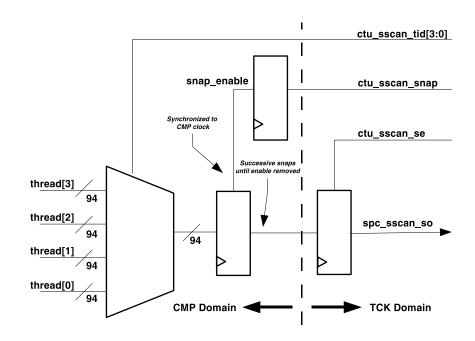

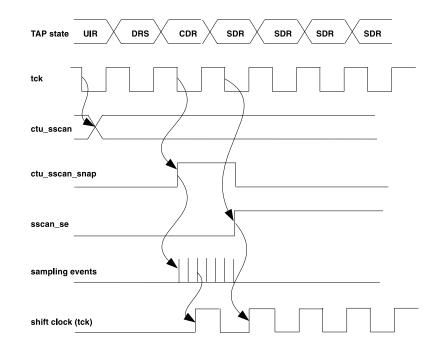

| FIGURE 2-37 | SPARC Shadow Scan Chain 2–71                                                 |

| FIGURE 2-38 | Shadow Scan Snap Timing Diagram 2–72                                         |

| FIGURE 3-1  | CPU Cache-Crossbar (CCX) Interface 3–2                                       |

| FIGURE 3-2  | Processor Cache-Crossbar (PCX) Interface 3–3                                 |

| FIGURE 3-3  | Cache-Processor Crossbar (CPX) Interface 3–5                                 |

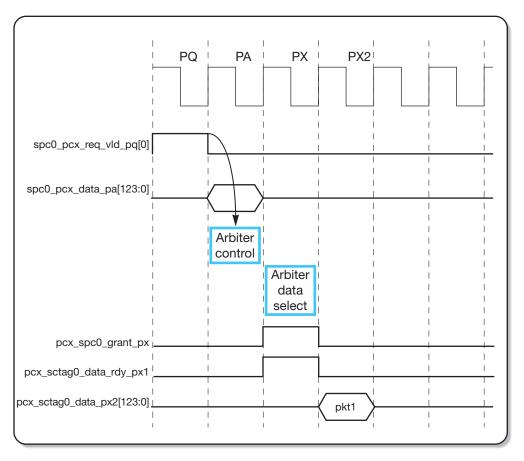

| FIGURE 3-4  | PCX Packet Transfer Timing – One Packet Request 3–27                         |

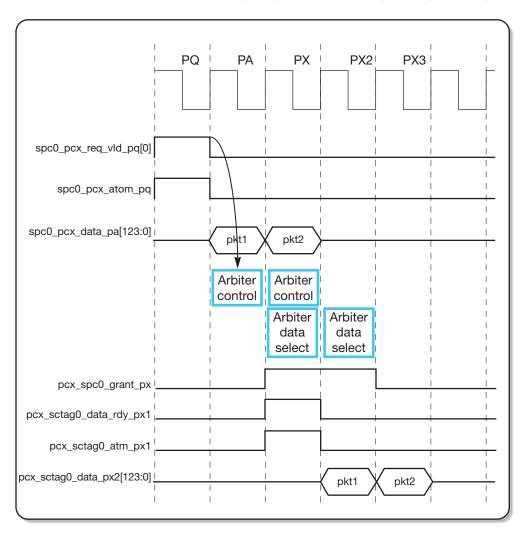

| FIGURE 3-5  | PCX Packet Transfer Timing – Two-Packet Request 3–28                         |

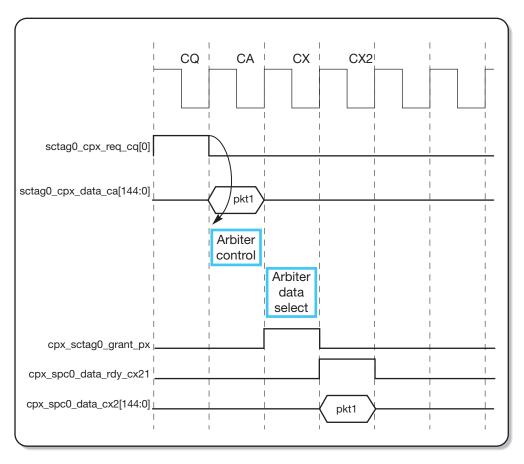

| FIGURE 3-6  | CPX Packet Transfer Timing Diagram – One Packet Request 3–29                 |

| FIGURE 3-7  | CPX Packet Transfer Timing Diagram – Two Packet Request 3–30                 |

| FIGURE 3-8  | Timing Diagram - Third Speculative request is accepted by CCX 3-31           |

| FIGURE 3-9  | Timing Diagram - Third Speculative request is rejected and resent later 3-34 |

|             |                                                                              |

- FIGURE 3-10 PCX and CPX Internal Blocks 3–35

- FIGURE 3-11 Data Flow in PCX Arbiter 3–36

- FIGURE 3-12 Control Flow in PCX Arbiter 3–37

- FIGURE 4-1 Flow Diagram and Interfaces for an L2-Cache Bank 4–3

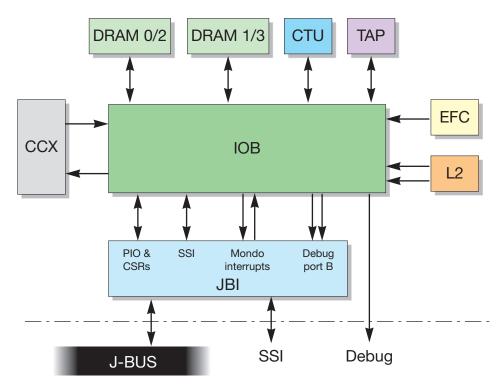

- FIGURE 5-1 IOB Interfaces 5–2

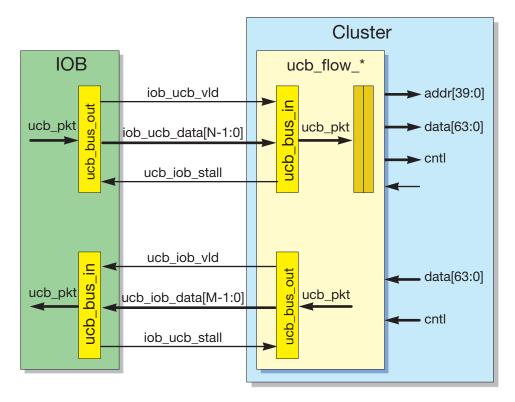

- FIGURE 5-2 IOB UCB Interface to and From the Cluster 5–4

- FIGURE 5-3 IOB Internal Block Diagram 5–8

- FIGURE 6-1 JBI Functional Block Diagram 6–2

- FIGURE 7-1 FPU Functional Block Diagram 7–2

- FIGURE 8-1 DDR-II DRAM Controller Functional Block Diagram 8–2

- FIGURE 8-2 DDR-II DRAM Controller Top-Level State Diagram 8–4

- FIGURE 8-3 DIMM Scheduler State Diagram 8–5

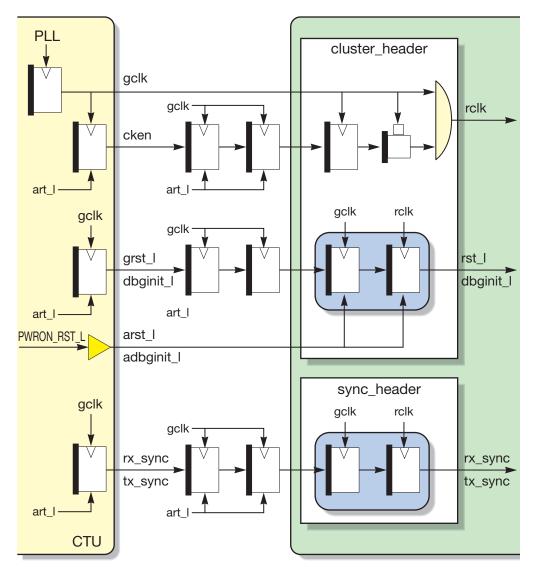

- FIGURE 10-1 Clock and Reset Functional Block Diagram 10–2

- FIGURE 10-2 PLL Functional Block Diagram 10–3

- FIGURE 10-3 Clock Divider Block Diagram 10–4

- FIGURE 10-4 Sync Pulses Waveforms 10–6

- FIGURE 10-5 Clock Signal Distribution 10–9

## Tables

| TABLE 2-1  | SPARC Core Terminology 2–4                       |

|------------|--------------------------------------------------|

| TABLE 2-2  | SPARC Core I/O Signal List 2–5                   |

| TABLE 2-3  | Modular Arithmetic Operations 2-40               |

| TABLE 2-4  | Error Handling Behavior 2–43                     |

| TABLE 2-5  | Supported OpenSPARC T1 Trap Types 2–55           |

| TABLE 2-6  | Privilege Levels and Thread States 2-62          |

| TABLE 2-7  | Interrupt Data Field - Reset 2-69                |

| TABLE 2-8  | Interrupt Data Field - Idle/Resume 2-70          |

| TABLE 2-9  | Interrupt Data Field - HW Int 2-70               |

| TABLE 2-10 | SPARC Physical Core Shadow Scan Chain 2–72       |

| TABLE 3-1  | CPX Packet Format – Part 1 3–7                   |

| TABLE 3-2  | CPX Packet Format – Part 2 3–8                   |

| TABLE 3-3  | PCX Packet Format – Part 1 3–9                   |

| TABLE 3-4  | PCX Packet Format – Part 2 3–10                  |

| TABLE 3-5  | Encoding of Transaction Size 3–11                |

| TABLE 3-6  | Floating-Point Address Field Usage 3–12          |

| TABLE 3-7  | Data Field Fill 3–12                             |

| TABLE 3-8  | Store ACK or Invalidate Data Field (1 of 2) 3–15 |

| TABLE 3-9  | Store ACK or Invalidate Data Field (2 of 2) 3–15 |

| TABLE 3-10 | Interrupt Packet Data Field (VINT) 3–15          |

| TABLE 3-11 | Floating-Point Return Data Field 3–16                         |

|------------|---------------------------------------------------------------|

| TABLE 3-12 | CCX I/O Signal List 3–23                                      |

| TABLE 4-1  | SCDATA I/O Signal List 4–18                                   |

| TABLE 4-2  | SCBUF I/O Signal List 4–19                                    |

| TABLE 4-3  | SCTAG I/O Signal List 4–21                                    |

| TABLE 5-1  | UCB interfaces to Clusters 5-3                                |

| TABLE 5-2  | UCB Request/Acknowledge Packet format 5-4                     |

| TABLE 5-3  | UCB Request/ACK Packet Types 5–5                              |

| TABLE 5-4  | UCB Data Size 5–5                                             |

| TABLE 5-5  | UCB Interrupt Packet Format 5–6                               |

| TABLE 5-6  | UCB Interrupt Packet Types 5-6                                |

| TABLE 5-7  | UCB No Payload Over an 8-Bit Interface Without Stalls 5-6     |

| TABLE 5-8  | UCB No Payload Over an 8-Bit Interface With Stalls 5–7        |

| TABLE 5-9  | IOB Address Map 5-7                                           |

| TABLE 5-10 | I/O Bridge I/O Signal List 5–12                               |

| TABLE 6-1  | JBI I/O Signal List 6–8                                       |

| TABLE 7-1  | OpenSPARC T1 FPU Feature Summary 7-3                          |

| TABLE 7-2  | SPARC V9 Single and Double Precision FPop Instruction Set 7-4 |

| TABLE 7-3  | FPA Datapath Stages 7–7                                       |

| TABLE 7-4  | FPM Datapath Stages 7–8                                       |

| TABLE 7-5  | FPD Datapath Stages 7–9                                       |

| TABLE 7-6  | IEEE Exception Cases 7–13                                     |

| TABLE 7-7  | FPU I/O Signal List 7–15                                      |

| TABLE 8-1  | DDR-II Addressing 8–7                                         |

| TABLE 8-2  | Physical Address to DIMM Address Decoding 8–7                 |

| TABLE 8-3  | DDR-II Commands Used by OpenSPARC T1 Processor 8–8            |

| TABLE 8-4  | DRAM Controller I/O Signal List 8–9                           |

| TABLE 9-1  | Error Protection for SPARC Memories 9–4                       |

| TABLE 9-2  | Error Protection for L2-Cache Memories 9–6                    |

| TABLE 10-1 | Clock Domain Dividers 10-5                                    |

|            |                                                               |

TABLE 10-2CTU I/O Signal List10–15

## Preface

This *OpenSPARC T1 Microarchitecture Specification* includes detailed functional descriptions of the core OpenSPARC<sup>™</sup> T1 processor components. This manual also provides the I/O signal list for each component. This processor is the first chip multiprocessor that fully implements the Sun<sup>™</sup> Throughput Computing initiative.

### How This Document Is Organized

Chapter 1 introduces the processor and provides a brief overview of each processor component.

Chapter 2 provides a detailed description of the functional units of a SPARC® Core.

Chapter 3 describes the CPU-cache crossbar (CCX) unit and includes detailed CCX block and timing diagrams.

Chapter 4 provides a functional description of the L2-cache and describes the L2-cache pipeline and instructions.

Chapter 5 describes the processor's input/output bridge (IOB).

Chapter 6 gives a functional description of the J-Bus interface (JBI) block.

Chapter 7 provides a functional description of the floating-point unit (FPU).

Chapter 8 describes the dynamic random access memory (DRAM) controller.

Chapter 9 provides a detailed overview of the processor's error handling mechanisms.

Chapter 10 gives a functional description of the processor's clock and test unit (CTU).

## Using UNIX Commands

This document might not contain information about basic UNIX<sup>®</sup> commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

### Shell Prompts

| Shell                                 | Prompt        |  |

|---------------------------------------|---------------|--|

| C shell                               | machine-name% |  |

| C shell superuser                     | machine-name# |  |

| Bourne shell and Korn shell           | \$            |  |

| Bourne shell and Korn shell superuser | #             |  |

# **Typographic Conventions**

| Typeface <sup>1</sup> | Meaning                                                                                                                     | Examples                                                                  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| AaBbCc123             | The names of commands, files,<br>and directories; on-screen<br>computer output                                              | Edit your.login file.<br>Use 1s –a to list all files.<br>% You have mail. |  |

| AaBbCc123             | What you type, when contrasted with on-screen computer output                                                               | % <b>su</b><br>Password:                                                  |  |

| AaBbCc123             | Book titles, new words or terms,<br>words to be emphasized.<br>Replace command-line variables<br>with real names or values. | These are called <i>class</i> options.                                    |  |

1 The settings on your browser might differ from these settings.

## **Related Documentation**

The documents listed as online or download are available at:

#### http://www.opensparc.net/

| Application                                        | Title                                                           | Part Number | Format | Location |

|----------------------------------------------------|-----------------------------------------------------------------|-------------|--------|----------|

| OpenSPARC T1 instruction set                       | UltraSPARC® Architecture 2005<br>Specification                  | 950-4895    | PDF    | Online   |

| OpenSPARC T1 processor's internal registers        | UltraSPARC T1 Supplement to the<br>UltraSPARC Architecture 2005 | 819-3404    | PDF    | Online   |

| OpenSPARC T1 megacells                             | OpenSPARC T1 Processor Megacell<br>Specification                | 819-5016    | PDF    | Download |

| OpenSPARC T1 signal pin list                       | OpenSPARC T1 Processor Datasheet                                | 819-5015    | PDF    | Download |

| OpenSPARC T1 microarchitecture                     | OpenSPARC T1 Microarchitecture<br>Specification                 | 819-6650    | PDF    | Download |

| OpenSPARC T1 processor<br>J-Bus and SSI interfaces | OpenSPARC T1 Processor External<br>Interface Specification      | 819-5014    | PDF    | Download |

## Documentation, Support, and Training

| Sun Function  | URL                               |

|---------------|-----------------------------------|

| OpenSPARC T1  | http://www.opensparc.net/         |

| Documentation | http://www.sun.com/documentation/ |

| Support       | http://www.sun.com/support/       |

| Training      | http://www.sun.com/training/      |

## Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

CHAPTER

## **OpenSPARC** T1 Overview

This chapter contains the following topics:

- Section 1.1, "Introducing the OpenSPARC T1 Processor" on page 1-1

- Section 1.2, "Functional Description" on page 1-2

- Section 1.3, "OpenSPARC T1 Components" on page 1-4

## 1.1 Introducing the OpenSPARC T1 Processor

The OpenSPARC T1 processor is the first chip multiprocessor that fully implements the Sun Throughput Computing Initiative. The OpenSPARC T1 processor is a highly integrated processor that implements the 64-bit SPARC V9 architecture. This processor targets commercial applications such as application servers and database servers.

The OpenSPARC T1 processor contains eight SPARC<sup>®</sup> processor cores, which each have full hardware support for four threads. Each SPARC core has an instruction cache, a data cache, and a fully associative instruction and data translation lookaside buffers (TLB). The eight SPARC cores are connected through a crossbar to an on-chip unified level 2 cache (L2-cache).

The four on-chip dynamic random access memory (DRAM) controllers directly interface to the double data rate-synchronous DRAM (DDR2 SDRAM). Additionally, there is an on-chip J-Bus controller that provides an interconnect between the OpenSPARC T1 processor and the I/O subsystem.

# 1.2 Functional Description

The features of the OpenSPARC T1 processor include:

- 8 SPARC V9 CPU cores, with 4 threads per core, for a total of 32 threads

- 132 Gbytes/sec crossbar interconnect for on-chip communication

- 16 Kbytes of primary (Level 1) instruction cache per CPU core

- 8 Kbytes of primary (Level 1) data cache per CPU core

- 3 Mbytes of secondary (Level 2) cache 4 way banked, 12 way associative shared by all CPU cores

- 4 DDR-II DRAM controllers 144-bit interface per channel, 25 GBytes/sec peak total bandwidth

- IEEE 754 compliant floating-point unit (FPU), shared by all CPU cores

- External interfaces:

- J-Bus interface (JBI) for I/O 2.56 Gbytes/sec peak bandwidth, 128-bit multiplexed address/data bus

- Serial system interface (SSI) for boot PROM

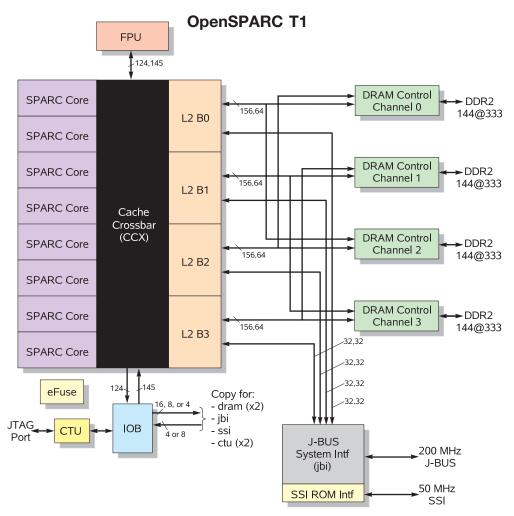

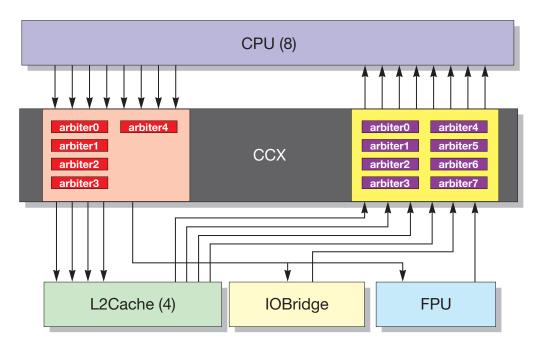

FIGURE 1-1 shows a block diagram of the OpenSPARC T1 processor illustrating the various interfaces and integrated components of the chip.

Notes:

- Blocks are not scaled according to physical size!

- Bus widths are labelled as in#,out# where in is into CCX or L2

FIGURE 1-1 OpenSPARC T1 Processor Block Diagram

## 1.3 OpenSPARC T1 Components

This section provides further details about the OpenSPARC T1 components.

### 1.3.1 SPARC Core

Each SPARC core has hardware support for four threads. This support consists of a full register file (with eight register windows) per thread, with most of the address space identifiers (ASI), ancillary state registers (ASR), and privileged registers replicated per thread. The four threads share the instruction, the data caches, and the TLBs. Each instruction cache is 16 Kbytes with a 32-byte line size. The data caches are write through, 8 Kbytes, and have a 16-byte line size. The TLBs include an autodemap feature which enables the multiple threads to update the TLB without locking.

Each SPARC core has single issue, six stage pipeline. These six stages are:

- 1. Fetch

- 2. Thread Selection

- 3. Decode

- 4. Execute

- 5. Memory

- 6. Write Back

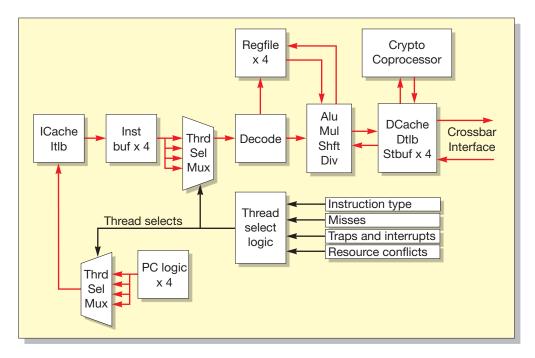

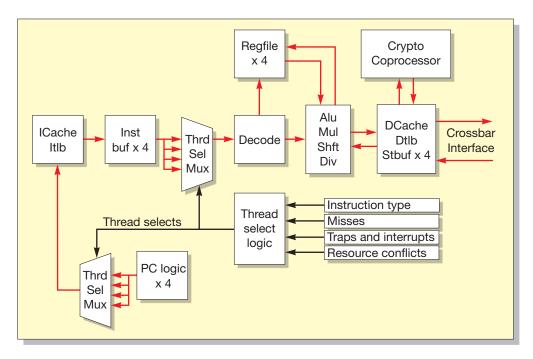

FIGURE 1-2 shows the SPARC core pipeline used in the OpenSPARC T1 Processor.

FIGURE 1-2 SPARC Core Pipeline

Each SPARC core has the following units:

- 1. Instruction fetch unit (IFU) includes the following pipeline stages fetch, thread selection, and decode. The IFU also includes an instruction cache complex.

- 2. Execution unit (EXU) includes the execute stage of the pipeline.

- 3. Load/store unit (LSU) includes memory and writeback stages, and a data cache complex.

- 4. Trap logic unit (TLU) includes trap logic and trap program counters.

- 5. Stream processing unit (SPU) is used for modular arithmetic functions for crypto.

- 6. Memory management unit (MMU).

- 7. Floating-point frontend unit (FFU) interfaces to the FPU.

### 1.3.1.1 Instruction Fetch Unit

The thread selection policy is as follows – a switch between the available threads every cycle giving priority to the least recently executed thread. The threads become unavailable due to the long latency operations like loads, branch, MUL, and DIV, as well as to the pipeline stalls like cache misses, traps, and resource conflicts. The loads are speculated as cache hits, and the thread is switched-in with lower priority.

Instruction cache complex has a 16-Kbyte data, 4-way, 32-byte line size with a single ported instruction tag. It also has dual ported (1R/1W) valid bit array to hold cache line state of valid/invalid. Invalidates access the V-bit array, not the instruction tag. A pseudo-random replacement algorithm is used to replace the cache line.

There is a fully associative instruction TLB with 64 entries. The buffer supports the following page sizes: 8 Kbytes, 64 Kbytes, 4 Mbytes, and 256 Mbytes. The TLB uses a pseudo least recently used (LRU) algorithm for replacement. Multiple hits in the TLB are prevented by doing an autodemap on a fill.

Two instructions are fetched each cycle, though only one instruction is issued per clock, which reduces the instruction cache activity and allows for an opportunistic line fill. There is only one outstanding miss per thread, and only four per core. Duplicate misses do not issue requests to the L2-cache.

The integer register file (IRF) of the SPARC core has 5 Kbytes with 3 read/2 write/1 transport ports. There are 640 64-bit registers with error correction code (ECC). Only 32 registers from the current window are visible to the thread. Window changing in background occurs under the thread switch. Other threads continue to access the IRF (the IRF provides a single-cycle read/write access).

### 1.3.1.2 Execution Unit

The execution unit (EXU) has a single arithmetic logic unit (ALU) and shifter. The ALU is reused for branch address and virtual address calculation. The integer multiplier has a 5 clock latency, and a throughput of half-per-cycle for area saving. One integer multiplication is allowed outstanding per core. The integer multiplier is shared between the core pipe (EXU) and the modular arithmetic (SPU) unit on a round-robin basis. There is a simple non-restoring divider, which allows for one divide outstanding per SPARC core. Thread issuing a MUL/DIV will be rolled back and switched out if another thread is occupying the MUL/DIV units.

### 1.3.1.3 Load/Store Unit

The data cache complex has an 8-Kbyte data, 4-way, 16-byte line size. It also has single ported data tag. There is a dual-ported (1R/1W) valid bit array to hold cache line state of valid or invalid. Invalidates access the V-bit array but not the data tag. A

pseudo-random replacement algorithm is used to replace the data cache line. The loads are allocating, and the stores are non-allocating. The data TLB operates similarly to the instruction TLB.

The load/store unit (LSU) has an 8 entry store buffer per thread, which is unified into a single 32 entry array, with RAW bypassing. Only a single load per thread outstanding is allowed. Duplicate requests for the same line are not sent to the L2-cache. The LSU has interface logic to interface to the CPU-cache crossbar (CCX). This interface performs the following operations:

- Prioritizes the requests to the crossbar for floating-point operation (Fpops), streaming operations, I\$ and D\$ misses, stores and interrupts, and so on.

- Request priority: imiss>ldmiss>stores,{fpu,stream,interrupt}.

- Assembles packets for the processor-cache crossbar (PCX).

The LSU handles returns from the CPX crossbar and maintains the order for cache updates and invalidates.

### 1.3.1.4 Floating-Point Frontend Unit

The floating-point frontend unit (FFU) decodes floating-point instructions and it also includes the floating-point register file (FRF). Some of the floating-point instructions like move, absolute value, and negate are implemented in the FFU, while the others are implemented in the FPU. The following steps are taken when the FFU detects a floating-point operation (Fpop):

- The thread switches out.

- The Fpop is further decoded and the FRF is read.

- Fpops with operands are packetized and shipped over the crossbar to the FPU.

- The computation is done in the FPU and the results are returned by way of the crossbar.

- Writeback completed to the FRF and the thread restarts.

### 1.3.1.5 Trap Logic Unit

The trap logic unit (TLU) has support for six trap levels. Traps cause pipeline flush and thread switch until trap program counter (PC) becomes available. The TLU also has support for up to 64 pending interrupts per thread.

### 1.3.1.6 Stream Processing Unit

The stream processing unit (SPU) includes a modular arithmetic unit (MAU) for crypto (one per core), and it supports asymmetric crypto (public key RSA) for up to a 2048-byte size key. It shares an integer multiplier for modular arithmetic operations. MAU can be used by one thread at a time. The MAU operation is set up by the store to control register, and the thread returns to normal processing. The MAU unit initiates streaming load/store operations to the L2-cache through the crossbar, and compute operations to the multiplier. Completion of the MAU can be checked by polling or issuing an interrupt.

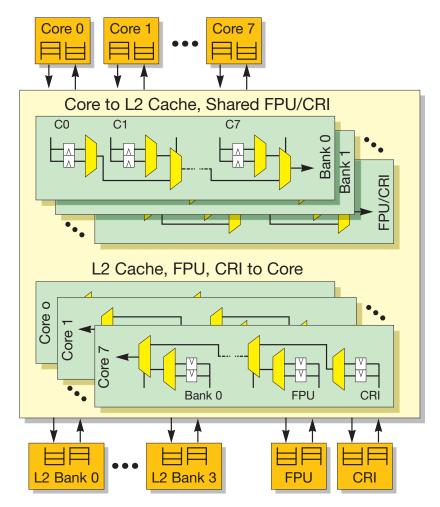

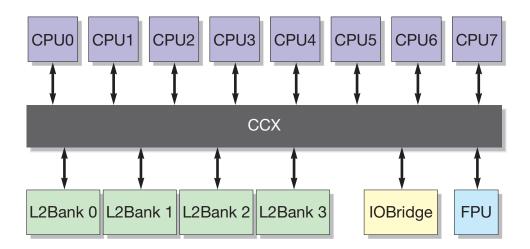

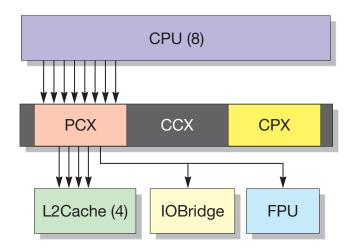

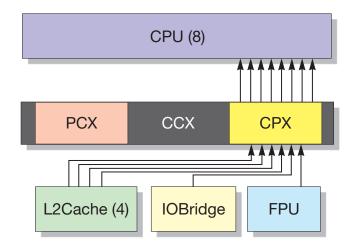

### 1.3.2 CPU-Cache Crossbar

The eight SPARC cores, the four L2-cache banks, the I/O Bridge, and the FPU all interface with the crossbar. FIGURE 1-3 displays the crossbar block diagram. The CPU-cache crossbar (CCX) features include:

- Each requester queues up to two packets per destination.

- Three stage pipeline request, arbitrate, and transmit.

- Centralized arbitration with oldest requester getting priority.

- Core-to-cache bus optimized for address plus doubleword store.

- Cache-to-core bus optimized for 16-byte line fill. 32-byte I\$ line fill delivered in two back-to-back clocks.

FIGURE 1-3 CCX Block Diagram

### 1.3.3 Floating-Point Unit

A single floating-point unit (FPU) is shared by all eight SPARC cores. The shared floating-point unit is sufficient for most commercial applications in which typically less than one percent of the instructions are floating-point operations.

### 1.3.4 L2-Cache

The L2-cache is banked four ways, with the bank selection based on the physical address bits 7:6. The cache is 3-Mbyte, 12-way set-associative with pseudo-least recently used (LRU) replacement (the replacement is based on a used bit scheme). The line size is 64 bytes. Unloaded access time is 23 cycles for an L1 data cache miss and 22 cycles for an L1 instruction cache miss.

L2-cache has a 64-byte line size, with 64 bytes interleaved between banks. Pipeline latency in the L2-cache is 8 clocks for a load, 9 clocks for an I-miss, with the critical chunk returned first. 16 outstanding misses per bank are supported for a 64 total misses. Coherence is maintained by shadowing the L1 tags in an L2-cache directory structure (the L2-cache is a point of global visibility). DMA from the I/O is serialized with respect to the traffic from the cores in the L2-cache.

The L2-cache directory shadows the L1 tags. The L1 set index and the L2-cache bank interleaving is such that one forth of the L1 entries come from an L2-cache bank. On an L1 miss, the L1 replacement way and set index identifies the physical location of the tag which will be updated by the miss address. On a store, the directory will be cammed. The directory entries are collated by set, so only 64 entries need to be cammed. This scheme is quite power efficient. Invalidates are a pointer to the physical location in the L1-cache, eliminating the need for a tag lookup in the L1-cache.

Coherency and ordering in the L2-cache are described as:

- Loads update directory and fill the L1-cache on return

- Stores are non-allocating in the L1-cache

- There are two flavors of stores: total store order (TSO) and read memory order (RMO).

Only one outstanding TSO store to the L2-cache per thread is permitted in order to preserve the store ordering. There is no such limitation on RMO stores.

- No tag check is done at a store buffer insert

- Stores check directory and determines an L1-cache hit

- Directory sends store acknowledgements or invalidates to the SPARC core

- Store updates happens to D\$ on a store acknowledge

- Crossbar orders the responses across cache banks.

## 1.3.5 DRAM Controller

The OpenSPARC T1 processor DRAM controller is banked four ways, with each L2 bank interacting with exactly one DRAM controller bank (a two-bank option is available for cost-constrained minimal memory configurations). The DRAM controller is interleaved based on physical address bits 7:6, so each DRAM controller bank must have identical dual in-line memory modules (DIMM) installed and enabled.

The OpenSPARC T1 processor uses DDR2 DIMMs and can support one or two ranks of stacked or unstacked DIMMs. Each DRAM bank/port is two-DIMMs wide (128bit + 16-bit ECC). All installed DIMMs must be identical, and the same number of DIMMs (that is, ranks) must be installed on each DRAM controller port. The DRAM controller frequency is an exact ratio of the core frequency, where the core frequency must be at least three times the DRAM controller frequency. The double data rate (DDR) data buses transfer data at twice the frequency of the DRAM controller frequency.

The OpenSPARC T1 processor can support memory sizes of up to 128 Gbytes with a 25 Gbytes/sec peak bandwidth limit. Memory access is scheduled across 8 reads plus 8 writes, and the processor can be programmed into a two-channel mode for a reduced configuration. Each DRAM channel has 128 bits of data and 16 bytes of ECC interface, with chipkill support, nibble error correction, and byte error detection.

## 1.3.6 I/O Bridge

The I/O bridge (IOB) performs an address decode on I/O-addressable transactions and directs them to the appropriate internal block or to the appropriate external interface (J-Bus or the serial system interface). Additionally, the IOB maintains the register status for external interrupts.

## 1.3.7 J-Bus Interface

The J-Bus interface (JBI) is the interconnect between the OpenSPARC T1 processor and the I/O subsystem. The J-Bus is a 200 MHz, 128-bit wide, multiplexed address or data bus, used predominantly for direct memory access (DMA) traffic, plus the programmable input/output (PIO) traffic used to control it.

The J-Bus interface is the functional block that interfaces to the J-Bus, receiving and responding to DMA requests, routing them to the appropriate L2 banks, and also issuing PIO transactions on behalf of the processor threads and forwarding responses back.

## 1.3.8 Serial System Interface

The OpenSPARC T1 processor has a 50 Mbyte/sec serial system interface (SSI) that connects to an external application-specific integrated circuit (ASIC), which in turn interfaces to the boot read-only memory (ROM). In addition, the SSI supports PIO accesses across the SSI, thus supporting optional control status registers (CSR) or other interfaces within the ASIC.

## 1.3.9 Electronic Fuse

The electronic fuse (e-Fuse) block contains configuration information that is electronically burned-in as part of manufacturing, including part serial number and core available information.

## SPARC Core

An OpenSPARC T1 processor contains eight SPARC cores, and each SPARC core has several function units. These SPARC core units are described in the following sections:

- Section 2.1, "SPARC Core Overview and Terminology" on page 2-2

- Section 2.2, "SPARC Core I/O Signal List" on page 2-5

- Section 2.3, "Instruction Fetch Unit" on page 2-6

- Section 2.4, "Load Store Unit" on page 2-22

- Section 2.5, "Execution Unit" on page 2-34

- Section 2.6, "Floating-Point Frontend Unit" on page 2-36

- Section 2.7, "Multiplier Unit" on page 2-38

- Section 2.8, "Stream Processing Unit" on page 2-39

- Section 2.9, "Memory Management Unit" on page 2-44

- Section 2.10, "Trap Logic Unit" on page 2-51

- Section 2.11, "Core Debug Features" on page 2-69

## 2.1 SPARC Core Overview and Terminology

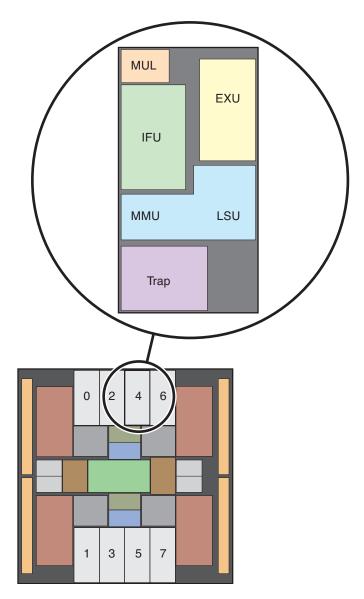

FIGURE 2-1 presents a high-level block diagram of a SPARC core, and FIGURE 2-2 shows the general physical location of these units on an example core.

FIGURE 2-1 SPARC Core Block Diagram

TABLE 2-1 defines acronyms and terms that are used throughout this chapter.

| Term                           | Description                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thread                         | A thread is a hardware strand ( <i>thread</i> and <i>strand</i> will be used interchangeably in this chapter). Each thread, or strand, enjoys a unique set of resources in support of its execution while multiple threads, or strands, within the same SPARC core will share a set of common resources in support of their execution. |

|                                | The per-thread resources include registers, a portion of I-fetch data-path, store<br>buffer, and miss buffer. The shared resources include the pipeline registers and<br>data-path, caches, translation lookaside buffers (TLB), and execution unit of the<br>SPARC Core pipeline.                                                     |

| ST                             | Single threaded.                                                                                                                                                                                                                                                                                                                       |

| MT                             | Multi-threaded.                                                                                                                                                                                                                                                                                                                        |

| Hypervisor (HV)                | The hypervisor is the layer of system software that interfaces with the hardware.                                                                                                                                                                                                                                                      |

| Supervisor (SV)                | The supervisor is the layer of system software such as operation system (OS) that executes with privilege.                                                                                                                                                                                                                             |

| Long latency instruction (LLI) | LLI represents an instruction that would take more than one SPARC core clock cycle to make its results visible to the next instruction.                                                                                                                                                                                                |

TABLE 2-1

SPARC Core Terminology

FIGURE 2-3 shows the view from virtualization, which illustrates the relative privileges of the various software layers.

| Applications  |               |  |  |  |

|---------------|---------------|--|--|--|

| OS instance 1 | OS instance 2 |  |  |  |

| Hypervisor    |               |  |  |  |

| OpenSPARC T1  |               |  |  |  |

FIGURE 2-3 Virtualization of Software Layers

## 2.2 SPARC Core I/O Signal List

TABLE 2-2 lists and describes the SPARC Core I/O signals.

| TABLE 2-2 | SPARC Core I/O Signal List |

|-----------|----------------------------|

|-----------|----------------------------|

|                         |     | Source/     |                                      |

|-------------------------|-----|-------------|--------------------------------------|

| Signal Name             | I/O | Destination | Description                          |

| pcx_spc_grant_px[4:0]   | In  | CCX:PCX     | PCX to processor grant info          |

| cpx_spc_data_rdy_cx2    | In  | CCX:CPX     | CPX data in-flight to SPARC          |

| cpx_spc_data_cx2[144:0] | In  | CCX:CPX     | CPX to SPARC data packet             |

| const_cpuid[3:0]        | In  | Hard wired  | CPU ID                               |

| const_maskid[7:0]       | In  | CTU         | Mask ID                              |

| ctu_tck                 | In  | CTU         | To IFU of sparc_ifu.v                |

| ctu_sscan_se            | In  | CTU         | To IFU of sparc_ifu.v                |

| ctu_sscan_snap          | In  | CTU         | To IFU of sparc_ifu.v                |

| ctu_sscan_tid[3:0]      | In  | CTU         | To IFU of sparc_ifu.v                |

| ctu_tst_mbist_enable    | In  | CTU         | To test_stub of test_stub_bist.v     |

| efc_spc_fuse_clk1       | In  | EFC         |                                      |

| efc_spc_fuse_clk2       | In  | EFC         |                                      |

| efc_spc_ifuse_ashift    | In  | EFC         |                                      |

| efc_spc_ifuse_dshift    | In  | EFC         |                                      |

| efc_spc_ifuse_data      | In  | EFC         |                                      |

| efc_spc_dfuse_ashift    | In  | EFC         |                                      |

| efc_spc_dfuse_dshift    | In  | EFC         |                                      |

| efc_spc_dfuse_data      | In  | EFC         |                                      |

| ctu_tst_macrotest       | In  | CTU         | To test_stub of test_stub_bist.v     |

| ctu_tst_scan_disable    | In  | CTU         | To test_stub of test_stub_bist.v     |

| ctu_tst_short_chain     | In  | CTU         | To test_stub of test_stub_bist.v     |

| global_shift_enable     | In  | CTU         | To test_stub of test_stub_two_bist.v |

| ctu_tst_scanmode        | In  | CTU         | To test_stub of test_stub_two_bist.v |

| spc_scanin0             | In  | DFT         | Scan in                              |

| spc_scanin1             | In  | DFT         | Scan in                              |

| Signal Name            | I/O | Source/<br>Destination | Description                      |

|------------------------|-----|------------------------|----------------------------------|

| cluster_cken           | In  | CTU                    | To spc_hdr of cluster_header.v   |

| gclk                   | In  | CTU                    | To spc_hdr of cluster_header.v   |

| cmp_grst_l             | In  | CTU                    | Synchronous reset                |

| cmp_arst_l             | In  | CTU                    | Asynchronous reset               |

| ctu_tst_pre_grst_l     | In  | CTU                    | To test_stub of test_stub_bist.v |

| adbginit_l             | In  | CTU                    | Asynchronous reset               |

| gdbginit_l             | In  | CTU                    | Synchronous reset                |

| spc_pcx_req_pq[4:0]    | Out | CCX:PCX                | processor to pcx request         |

| spc_pcx_atom_pq        | Out | CCX:PCX                | processor to pcx atomic request  |

| spc_pcx_data_pa[123:0] | Out | CCX:PCX                | processor to pcx packet          |

| spc_sscan_so           | Out | DFT                    | Shadow scan out                  |

| spc_scanout0           | Out | DFT                    | Scan out                         |

| spc_scanout1           | Out | DFT                    | Scan out                         |

| tst_ctu_mbist_done     | Out | CTU                    | MBIST done                       |

| tst_ctu_mbist_fail     | Out | CTU                    | MBIST fail                       |

| spc_efc_ifuse_data     | Out | EFC                    | From IFU of sparc_ifu.v          |

| spc_efc_dfuse_data     | Out | EFC                    | From IFU of sparc_ifu.v          |

#### TABLE 2-2 SPARC Core I/O Signal List (Continued)

## 2.3 Instruction Fetch Unit

The instruction fetch unit (IFU) is responsible for maintaining the program counters (PC) of different threads and fetching the corresponding instructions. The IFU also manages the level 1 I-cache (L1I) and the instruction translation lookaside buffer (ITLB), as well as managing and scheduling the four threads in a SPARC core. The SPARC core pipeline resides in the IFU, which controls instruction issue and instruction flow in the pipeline. The IFU decodes the instructions flowing through the pipeline, schedules interrupts, and it implements the idle/resume states of the pipeline. The IFU also logs the errors and manages the error registers.

## 2.3.1 SPARC Core Pipeline

There are six stages in a SPARC core pipeline:

- Fetch F-stage

- Thread selection S-stage

- Decode D-stage

- Execute E-stage

- Memory M-stage

- Writeback W-stage

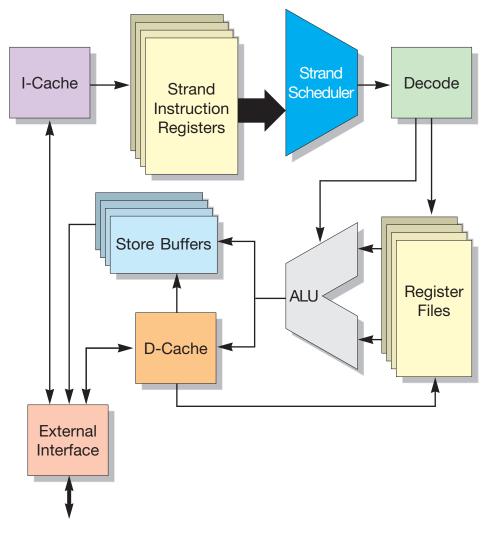

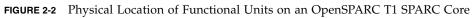

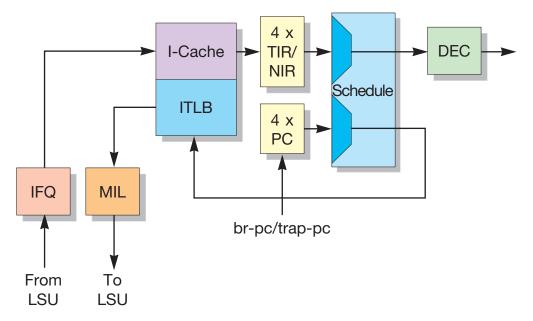

The I-cache access and the ITLB access take place in fetch stage. A selected thread (hardware strand) will be picked in the thread selection stage. The instruction decoding and register file access occur in the decode stage. The branch evaluation takes place in the execution stage. The access to memory and the actual writeback will be done in the memory and writeback stages. FIGURE 2-4 illustrates the SPARC core pipeline and support structures.

FIGURE 2-4 SPARC Core Pipeline and Support Structures

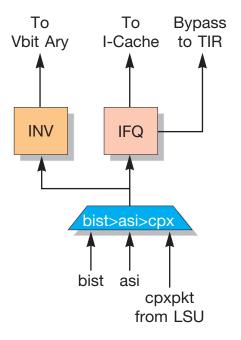

The instruction fill queue (IFQ) feeds into the I-cache. The missed instruction list (MIL) stores the addresses that missed the I-cache and the ITLB, and the MIL feeds into the load store unit (LSU) for further processing. The instruction buffer is two levels deep, and it includes the thread instruction (TIR) and next instruction (NIR) unit. Thread selection and scheduler (S-stage) resolves the arbitration among the TIR, NIR, branch-PC, and trap-PC to pick one thread send it to the decode stage (D-stage). FIGURE 2-5 shows the support structure for this portion of the thread pipeline.

FIGURE 2-5 Frontend of the SPARC Core Pipeline

## 2.3.2 Instruction Fetch

The instruction fetch unit (IFU) maintains the program counters (PC) and the nextprogram counters (NPC) of all live instructions executed on the OpenSPARC T1 processor. For every SPARC core clock cycle, two instructions are fetched for every instruction issued. This two fetches per one issue relationship is intended to reduce the I-cache access in order to allow the opportunistic I-cache line fill. Each thread is allowed to have one outstanding I-cache miss, and the SPARC core allows a total of four I-cache misses. Duplicated I-cache misses do not induce the redundant fill request to the level 2 cache (L2-cache).

## 2.3.3 Instruction Registers and Program Counter Registers

In the instruction buffer, there are two instruction registers per thread – the thread instruction register (TIR) and the next instruction register (NIR). The TIR contains the current thread instruction in the thread selection stage (S-stage), and the NIR contains the next instruction. An I-cache miss fill bypasses the I-cache and writes directly to the TIR, but it never writes to the NIR.

The thread scheduler selects a valid instruction from the TIR. After selecting the instruction, the valid instruction will be moved from the NIR to the TIR. If no valid instruction exists in the TIR, a no operation (NOP) instruction will be inserted.

There is one program counter (PC) register per thread. The next-program counter (NPC) could come from one of these sources:

- 1. Branch

- 2. TrapPC

- 3. Trap NPC

- 4. Rollback (a thread rolled back due to a load miss)

- 5. PC + 4

The IFU tracks the PC and NPC through W-stage. The last retired PC will be saved in the trap logic unit (TLU), and, if a trap occurs, it will also be saved in the trap stack.

## 2.3.4 Level 1 Instruction Cache

The instruction cache is commonly referred to as the level 1 instruction cache (L1I). The L1I is physically indexed and tagged and is 4-way set associative with 16 Kbytes of data. The cache-line size is 32 bytes. The L1I data array has a single port, and the I-cache fill size is 16 bytes per access. The characteristics of cached data include – 32-bit instructions, 1-bit parity, and 1-bit predecode. The tag array also has a single port.

There is a separate array for valid bit (V-bit). This V-bit array holds the cache line state of either valid or invalid, and the array has one read port and one write port (1R1W). The cache line invalidation only accesses the V-bit array, and the cache line replacement policy is pseudo-random.

The read access to the I-cache has a higher priority over the write access. The ASI read and write accesses to the I-cache are set to lower priorities. The completion of the ASI accesses are opportunistic, and there is fairness mechanism built in to prevent the starvation of service to ASI accesses.

The maximum wait period for a write access to the I-cache is 25 SPARC core clock cycles. A wait longer than 25 clock cycles will stall the SPARC core pipeline in order to allow the I-cache write access completion.

## 2.3.5 I-Cache Fill Path

I-cache fill packets come from the level 2 cache to processor interface (CPX) by way of the load store unit (LSU). Parity and predecode bits will be calculated before the I-cache fills up. CPX packets include invalidations (invalidation packets are nonblocking), test access point (TAP) reads and writes, and error notifications. The valid bit array in the I-cache has a dedicated port for servicing the invalidation packets.

FIGURE 2-6 illustrates the I-cache fill path.

FIGURE 2-6 I-Cache Fill Path

The I-cache line size is 32 bytes, and a normal I-cache fill takes two CPX packets of 16 bytes each. The instruction fill queue (IFQ) has a depth of two. An I-cache line will be invalidated when the first CPX packet is delivered and filled in the I-cache. That cache line will be marked as valid when the second CPX packet is delivered and filled. I-cache control guarantees the atomicity of the I-cache line fill action between the two halves of the cache line being filled.

An instruction fetch from the boot PROM, by way of the system serial interface (SSI), is a very slow transaction. The boot prom is a part of the I/O address space. All instruction fetches from the I/O space are non-cacheable. The boot PROM fetches only one 4-byte instruction at a time. This 4-byte instruction is replicated four times during the formation of the CPX packet. Only one CPX packet of non-cacheable

instructions will be forwarded to the IFQ. The non-cacheable instructions fetched from the boot PROM will not be filled in the I-cache. They will be sent to (or, bypassed to) the thread instruction register (TIR) directly.

2.3.6

## Alternate Space Identifier Accesses, I-Cache Line Invalidations, and Built-In Self-Test Accesses to the I-Cache

Alternate space identifiers (ASI) accesses to the I-cache, and the built-in self-test (BIST) accesses to the I-cache, go through the IFQ data-path to the I-cache. All ASI accesses and BIST accesses will cause the SPARC core pipeline to stall, so these accesses are serviced almost immediately.

The load store unit (LSU) initiates all ASI accesses. The LSU serializes all ASI accesses so that the second access will not be launched until the first access has been acknowledged. ASI accesses tend to be slow, and data for an ASI read will be sent back later.

A BIST operation requires atomicity, and it assumes and accommodates no interruptions until it completes.

Level 2 cache invalidations will always undergo a CPU-ID check in order to ensure that this invalidation packet is indeed meant for the specified SPARC core. In the following cases, an invalidation could be addressing anyone:

- A single I-cache line invalidation due to store acknowledgements, or due to a load exclusivity requiring that the invalidation of the other level 1 I-caches resulted from the self-modifying code.

- Invalidating two I-cache lines because of a cache-line eviction in the level 2 cache (L2-cache).

- Invalidating all ways in a given set due to error conditions, such as encountering a tag ECC error in a level 2 cache line.

## 2.3.7 I-Cache Miss Path

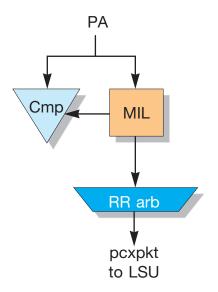

A missed instruction list (MIL) is responsible for sending the I-cache miss request to the level 2 cache (L2-cache) in order to get an I-cache fill. The MIL has one entry per thread, which supports a total of four outstanding I-cache misses for all four threads in the same SPARC core at the same time. Each entry in the MIL contains the physical address (PA) of an instruction that missed the I-cache, the replacement way information, the MIL state information, the cacheability, the error information, and so on. The PA tracks the I-fetch progress from the indication of an I-cache miss until the I-cache has been filled. The dispatch of I-cache miss requests from different threads follow a fairness mechanism based on a round-robin algorithm.

FIGURE 2-7 illustrates the I-cache miss path.

FIGURE 2-7 I-Cache Miss Path

The MIL keeps track of the physical address (PA) of an instruction that missed the I-cache. A second PA that matches the PA of an already pending I-cache miss will cause the second request to be put on hold and marked as a *child* of the pending I-cache miss request. The child request will be serviced when the pending I-cache miss receives its response. The MIL uses a linked list to track and service the duplicated I-cache miss request. The depth for such a linked list is four.

The MIL cycles through the following states:

- 1. Make request.

- 2. Wait for an I-cache fill.

- 3. Fill the first 16 bytes of data. The MIL sends a speculative completion notification to the thread scheduler at the completion of filling the first 16 bytes.

- 4. Fill the second 16 bytes of data. The MIL sends a completion notification to the thread scheduler at the completion of filling the second 16 bytes.

- 5. Done.

An I-cache miss request could be canceled because of, for example, a trap. The MIL still goes through the motions of filling a cache line but it does not bypass it to the thread instruction register (TIR). A pending child request must be serviced even if the original parent I-cache miss request was cancelled.

When a child I-cache miss request crosses with a parent I-cache miss request, the child request might not be serviced before the I-cache fill for the parent request occurs. The child instruction fetch shall be retired (rolled back) to the F-stage to allow it to access the I-cache. This kind of case is referred to as miss-fill crossover.

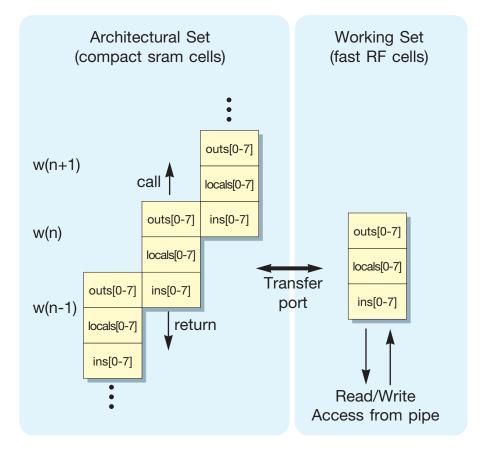

## 2.3.8 Windowed Integer Register File

The integer register file (IRF) contains 5 Kbytes of storage, and has three read ports, 2 write ports, and one transfer port (3R/2W/1T). The IRF houses 640 64-bit registers that are protected by error correcting code (ECC). All read or write accesses can be completed in one SPARC core clock cycle.

FIGURE 2-8 illustrates the structure of an integer architectural register file (IARF) and an integer working register file (IWRF).

FIGURE 2-8 IARF and IWRF File Structure

Each thread requires 128 registers for the eight windows (with 16 registers per window), and four sets of global registers with eight global registers per set. There are 160 registers per thread, and there are four threads per SPARC core. There are a total of 640 registers per SPARC core.

Only 32 registers from the current window are visible to the thread. A window change occurs in the background under thread switching while the other threads continue to access integer register file.

Please refer to *OpenSPARC T1 Processor Megacell Specification* for additional details on the IRF.

## 2.3.9 Instruction Table Lookaside Buffer

The instruction table lookaside butter (ITLB) is responsible for address translation and tag comparison. The ITLB is always turned-on for non-hypervisor mode operations, and the ITLB is always turned-off for hypervisor mode operations.

The ITLB contains 64 entries. The replacement policy is a pseudo least recently used (pseudo-LRU) policy, which is the same policy as that for the I-cache.

The ITLB supports page sizes of 8 Kbytes, 64 Kbytes, 4 Mbytes, and 256 Mbytes. Multiple hits in the ITLB are prevented by the autodemap feature in an ITLB fill.

## 2.3.10 Thread Selection Policy

Thread switching takes place during every SPARC core clock cycle. At the time of a thread selection, the priority is given to the least recently executed yet available thread. Load instructions will be speculated as cache hits and the thread executing a load instruction will be deemed as available and allowed to be switched-in with a low priority.

A thread could become unavailable due to one of these reasons:

- 1. The thread is executing one of the long latency instructions, such as load, branch, multiplication, division, and so on.

- 2. The SPARC core pipeline has been stalled due to one of the long latency operations, such as encountering a cache miss, taking a trap, or experiencing a resource conflict.

## 2.3.11 Thread States

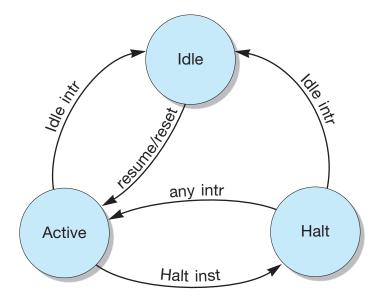

A thread cycles through these three different states – idle, active, and halt. FIGURE 2-9 illustrates the basic transition of non-active states.

FIGURE 2-9 Basic Transition of Non-Active States

A thread is in an idle state at power-on. An active thread will only be transitioned to an idle state after a wait mask for an I-cache fill has been cleared.

A thread in the idle state should not receive the *resume* command without a previous reset. When a thread is violated, the integrity of the hardware behavior cannot be guaranteed.

FIGURE 2-10 illustrates the thread state transition of an active thread.

FIGURE 2-10 Thread State Transition of an Active Thread

An active thread could be placed in the wait state because of any of the following reasons:

- 1. Wait for an I-cache fill.

- 2. Wait due to store buffer full.

- 3. Wait due to long latency, or a resource conflict where all resource conflicts arise because of long latency.

- 4. Wait due to any combination of the preceding reasons.

The current wait state is tracked in the IFU wait masks.

FIGURE 2-11 illustrates the state transition for a thread in speculative states.

FIGURE 2-11 State Transition for a Thread in Speculative States

### 2.3.12 Thread Scheduling

A thread can be scheduled when it is in one of the following five states – idle (which happens infrequently, and generally results from a reset or resume interrupt), Rdy, SpecRdy, Run, and SpecRun. The thread priority in each state is different at the time for scheduling. The priority scheme can be characterized as follows:

Idle > Rdy > SpecRdy > (Run = SpecRun)

The fairness scheme for threads in the Run state or the SpecRun state is a roundrobin algorithm with the least recently executed thread winning the selection.

Within Idle threads, the priority scheme is as follows:

T0 (thread 0) > T1 (thread 1) > T2 (thread 2) > T3 (thread 3)

## 2.3.13 Rollback Mechanism

The rollback mechanism provides a way of recovering from a scheduling error. The two reasons for performing a rollback include:

- 1. All of the stall conditions, or switch conditions, were not known at the time of the scheduling.

- 2. The scheduling was done speculatively on purpose.

For example, after issuing a load, the scheduler will speculate a level 1 D-cache hit performance reasons. If the speculation was incorrect (because of encountering a load miss), all of the instructions after the speculative load instruction must be rolled back. Otherwise, the performance gain would be a substantial.

Rolled back instructions must be restarted from the S-stage or F-stage of the SPARC core pipeline. FIGURE 2-12 illustrates the pipeline graph for the rollback mechanism.

FIGURE 2-12 Rollback Mechanism Pipeline Graph

The three rollback cases include:

- 1. E to S and D to F

- 2. D to S and S to F

- 3. W to F

The possible conditions causing a rollback case 1 or a case 2 include:

- Instruction(s) following a load miss

- Resource conflict due to long latency

- Store buffer full

- I-cache instruction parity error

- I-fetch retry

The possible conditions causing rollback case 3 include:

- Encountering an ECC error during the instruction register file access.

- The floating-point store instruction encountering an ECC error during the floating-point register file access.

- Instruction(s) following a load hits the store buffer and the level 1 D-cache, where the data has not been bypassed from the store buffer to the level 1 D-cache.

- Encountering D-cache parity errors.

- Launching an idle or resume interrupt where the machine states must be restored.

- An interrupt has been scheduled but not yet taken.

#### 2.3.14 Instruction Decode

The IFU decodes the SPARC V9 instructions, and the floating-point frontend unit (FFU) decodes the floating-point instructions. Unimplemented floating-point instructions will cause an fp\_exception\_other trap with a FSR.ftt=3 (unimplemented\_FPop). These operations will be emulated by the software.

The privilege is checked in D-stage of the SPARC core pipeline. Some instructions can only be executed with hypervisor privilege or with supervisor privilege.

The branch condition is also evaluated in the D-stage, and the decision for annulling a delay slot is made in this stage as well.

## 2.3.15 Instruction Fetch Unit Interrupt Handling

All interrupts are delivered to the instruction fetch unit (IFU). For each received interrupt, the IFU shall check the bit's pstate.ie (the interrupt enable bit in the processor state register) and hpstate (the hypervisor state) before scheduling the interrupt. All interrupts will be prioritized (refer to the *Programmer's Reference Manual* for these priority assignments). Once prioritized, the interrupts will be scheduled just like the instructions.

When executing in the hypervisor (HV) state, an interrupt with a supervisor (SV) privilege will not be serviced at all. An hypervisor state execution shall not be blocked by anything with supervisor privilege.

Nothing could block the scheduling of a reset, idle, or resume interrupt.

Some interrupts are asserted by a level while others are asserted by a pulse. The IFU remembers the form the interrupts were originated in order to preserve the integrity of the scheduling.

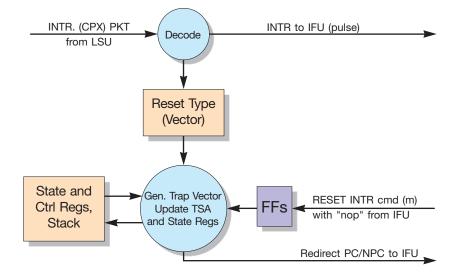

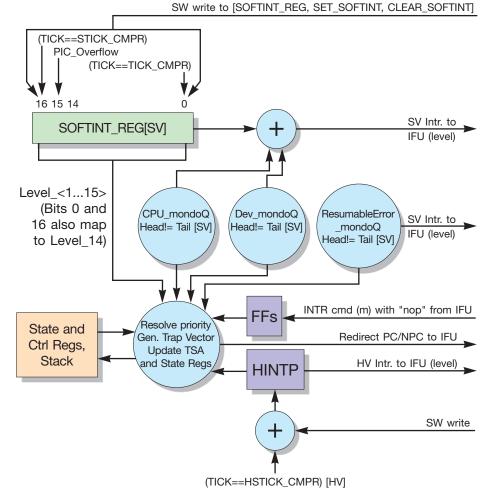

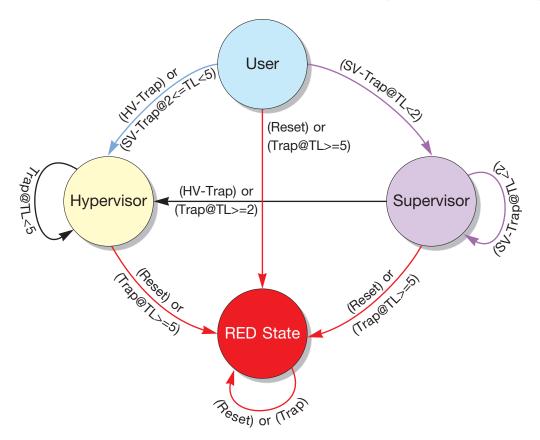

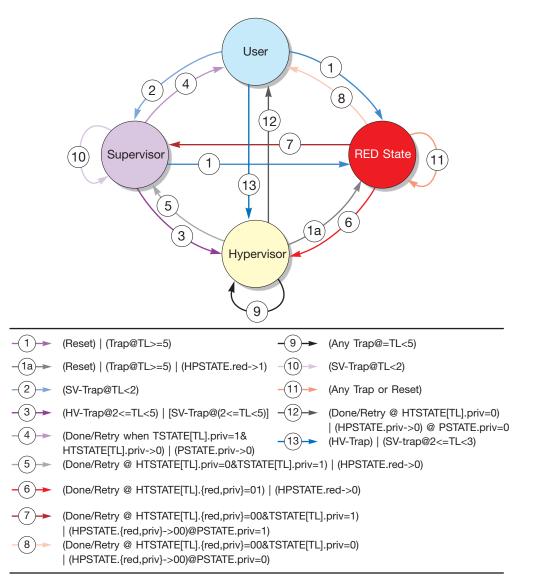

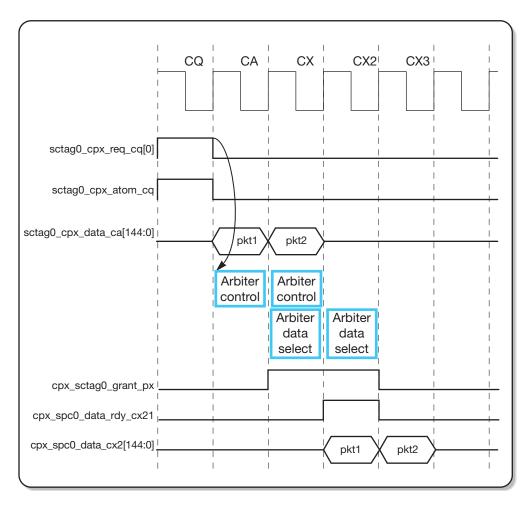

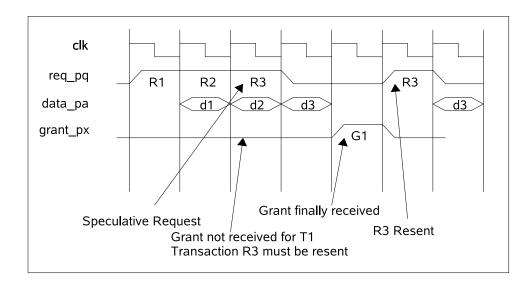

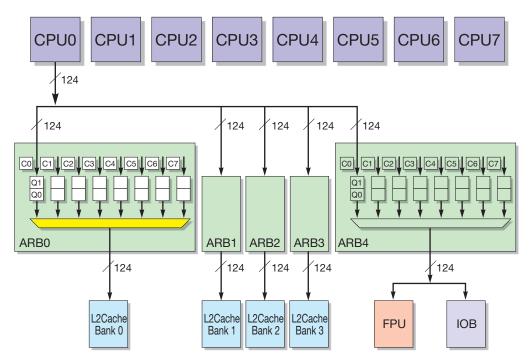

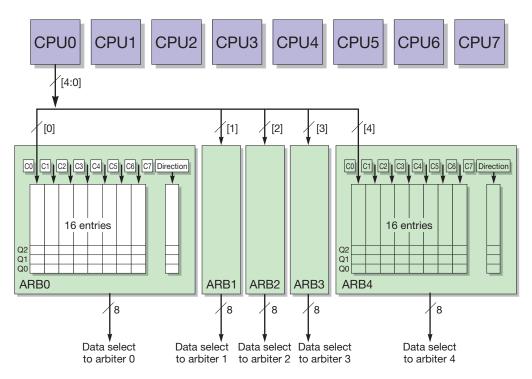

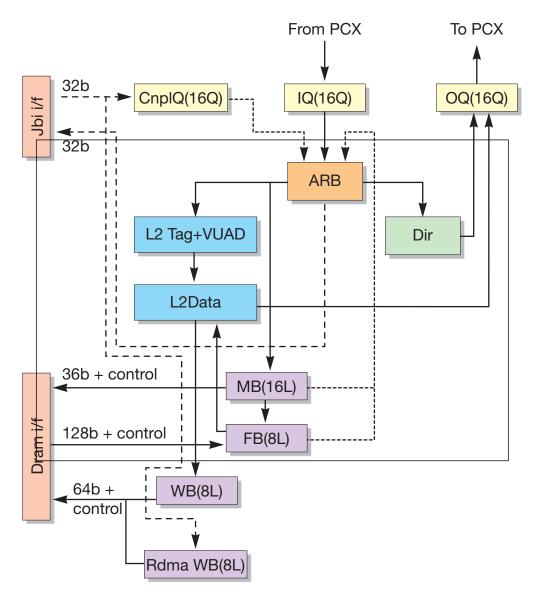

## 2.3.16 Error Checking and Logging