# *Cadence Interface/ Tutorial Guide*

Introduction

**Getting Started**

**Design Entry**

**Functional Simulation**

**Design Implementation**

**Timing Simulation**

Design and Simulation Techniques

**Manual Translation**

**Tutorial**

Glossary

**Program Options**

Processing Designs with LogiBLOX

Synopsys/Verilog Design Flow

**Files**

XILINX.PFF Property Filter File Format

Printed in U.S.A.

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

XILINX, XACT, XC2064, XC3090, XC4005, XC5210, XC-DS501, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, and TRACE are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAPP, XAM, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, XPP, XSI, BITA, Configurable Logic Cell, CLC, Dual Block, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, Plus Logic, Plustran, P+, PowerGuide, PowerMaze, Select-RAM, SMARTswitch, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, WebLINX, XABEL, Xilinx Foundation Series, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx. Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,897; 5,670,896; RE 34,363, RE 34,444, and RE 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1997 Xilinx, Inc. All Rights Reserved.

### Preface

#### About This Manual

This manual explains how to use the Xilinx/Cadence Interface software with Cadence Concept and Verilog-XL.

Before using this manual, you should be familiar with the operations that are common to all Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

Other publications you can consult for related information are the Cadence manuals, *Concept Schematic User Guide* and *Xilinx FPGA Designer (Concept) User Guide*.

#### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," describes the Xilinx/Cadence design flow, Xilinx-supplied libraries, Xilinx architecture support, and major features.

- Chapter 2, "Getting Started," explains how to set up Xilinx and Cadence files and environment variables.

- Chapter 3, "Design Entry," describes Cadence design entry in relation to the Xilinx software.

- Chapter 4, "Functional Simulation," explains how to perform functional simulation of your designs using Cadence's Verilog-XL simulator.

- Chapter 5, "Design Implementation," explains how to use CONCEPT2XIL to translate your design into an EDIF file.

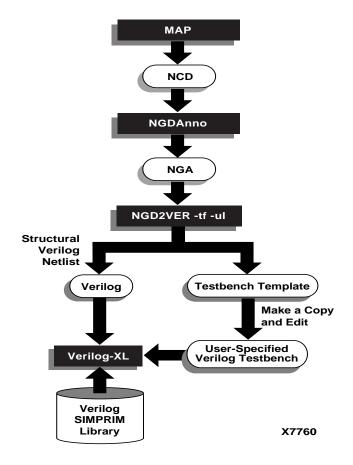

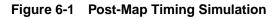

- Chapter 6, "Timing Simulation," describes how to prepare for timing simulation using the NGD2VER command. The chapter then explains how to conduct timing simulation using the Cadence Verilog-XL software.

- Chapter 7, "Design and Simulation Techniques," describes various design and simulation techniques.

- Chapter 8, "Manual Translation," summarizes how to do design implementation, functional simulation, and timing simulation from the UNIX command line.

- Chapter 9, "Schematic Design Tutorial," guides you through a typical field-programmable gate array (FPGA) and complex programmable logic device (CPLD) design process from schematic entry to completion of a functioning device.

- Appendix A, "Glossary," describes the basic terminology for the Xilinx/Cadence interface.

- Appendix B, "Program Options," describes Xilinx and Cadence command line programs that pertain to the Xilinx/Cadence interface.

- Appendix C, "Processing Designs with LogiBLOX Components," explains how to translate LogiBLOX modules for use within the Cadence Concept editor.

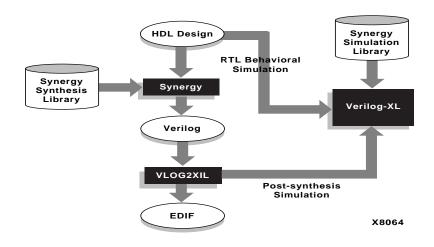

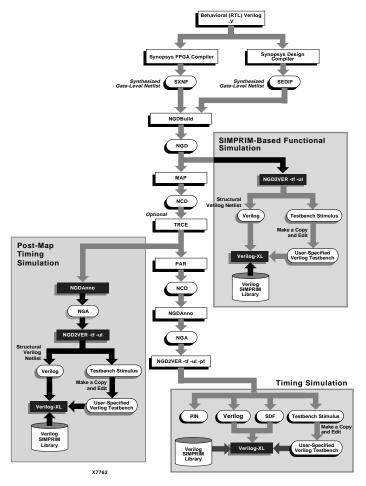

- Appendix D, "Synopsys/Verilog Design Flow," provides a flow chart that illustrates how to process designs described in Verilog HDL using Synopsys and simulate them with the Cadence Verilog-XL simulator.

- Appendix E, "Files," contains annotated testbench templates.

- Appendix F, "XILINX.PFF Property Filter File Format," describes the structure of the xilinx.pff file.

## Conventions

### **Typographical**

This manual uses the following conventions. An example illustrates each convention.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: -100

• Courier bold indicates literal commands that you enter in a syntactical statement.

rpt\_del\_net=

Courier bold also indicates commands that you select from a menu.

$\texttt{File} \rightarrow \texttt{Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Square brackets also enclose footnotes in tables that are printed out as hardcopy in  $DynaText^{®}$ .

• Braces "{ }" enclose a list of items from which you choose one or more.

lowpwr ={on|off}

• A vertical bar "|" separates items in a list of choices.

symbol editor\_name [bus|pins]

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2 ... locn;

### **Online Document**

Xilinx has created several conventions for use within the DynaText online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click on the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click on the blue-underlined text to open the specified cross-reference.

- There are several types of icons.

Iconized figures are identified by the figure icon.

#### Figure 1-1 Naming Conventions

Iconized tables are identified by the table icon.

Table 13-14 Carry Modes

The Copyright icon displays in the upper left corner on the first page of every Xilinx online document.

$\square$

The DynaText footnote icon displays next to the footnoted text.

#### Macro 😎

Double-click on these icons to display figures, tables, copyright information, or footnotes in a separate window.

• Inline figures display within the text of a document. You can display these figures in a separate window by clicking on the figure.

## Contents

#### Preface

| About This Manual<br>Manual Contents                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                 |

| Typographical<br>Online Document                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                 |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                 |

| Architecture Support<br>Platform Support<br>Features<br>Xilinx/Cadence Interface<br>Libraries<br>Schematic and Verilog Design Entry<br>Direct Generation of Structural Verilog Netlist from Concept<br>Schematics<br>Standard EDIF Netlist<br>Concept<br>Verilog-XL<br>CONCEPT2XIL<br>XIL2CDS<br>NGD2VER<br>Simulation of Synopsys Designs<br>Automatic Library Specification<br>Waveform Viewer Support<br>LogiBLOX<br>Timing Constraints<br>Synergy Support<br>Design Flows | $\begin{array}{c} 1\text{-1} \\ 1\text{-2} \\ 1\text{-3} \\ 1\text{-4} \\ 1\text{-4} \\ 1\text{-4} \\ 1\text{-5} \\ 1\text{-5} \\ 1\text{-5} \\ 1\text{-6} \\ 1\text{-6} \\ 1\text{-6} \\ 1\text{-6} \\ 1\text{-6} \end{array}$ |

| Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Manual Contents                                                                                                                                                                                                                 |

| Tutorials                                 | 1-11 |

|-------------------------------------------|------|

| Online Help                               | 1-11 |

| Design Approaches                         |      |

| Schematic Entry                           | 1-11 |

| Verilog HDL Entry (Synergy)               | 1-12 |

| Mixed-mode Entry, Top Level Schematic     | 1-13 |

| Mixed-Mode Entry, Top Level HDL (Verilog) | 1-14 |

#### Chapter 2 Getting Started

| Required Software                              | 2-1 |

|------------------------------------------------|-----|

| Setting Up Your Environment                    |     |

| Required Environment Variables (All Platforms) | 2-2 |

| Concept Environment Setup                      | 2-3 |

| Concept Environment Variables                  | 2-4 |

| Concept Setup Library Files                    | 2-4 |

| Verilog Environment Setup                      | 2-7 |

| Dynatext Environment Variables                 | 2-8 |

| Invoking Concept                               | 2-8 |

| Exiting Concept                                | 2-8 |

#### Chapter 3 Design Entry

|                                                               | Concept                                              | 3-2  |

|---------------------------------------------------------------|------------------------------------------------------|------|

|                                                               | Requirements For HDL Direct Compliance               | 3-3  |

|                                                               | Using the Xilinx Concept Unified Schematic Libraries | 3-5  |

|                                                               | FPGA and CPLD Libraries                              | 3-6  |

|                                                               | PAD Library                                          | 3-6  |

|                                                               | Renamed Components                                   | 3-6  |

|                                                               | Verilog/Concept HDL Direct Naming Conventions        | 3-7  |

|                                                               | VCC and GND Components                               | 3-8  |

|                                                               | Using the LogiBLOX Libraries                         | 3-8  |

| Specifying Xilinx Properties and Constraints in Concept       |                                                      |      |

|                                                               | Adding Xilinx Properties                             | 3-9  |

| Rules and Restrictions For Using Xilinx Properties in Concept |                                                      | 3-10 |

|                                                               | SIZE Property                                        | 3-11 |

|                                                               | CONCEPT2XIL Property Filter File                     | 3-11 |

|                                                               | Xilinx Properties Without Values                     | 3-13 |

|                                                               | Xilinx Properties on Pads                            | 3-13 |

|                                                               | Supported Xilinx Properties                          | 3-14 |

|                                                               | Obsolete Xilinx Properties                           | 3-14 |

|                                                               | Entering Timing Specifications in Schematics         | 3-14 |

|                                                               | Creating New Groups from Existing Groups             | 3-15 |

|                                                               |                                                      |      |

| Attaching Signal Names                          | 3-15 |

|-------------------------------------------------|------|

| Creating Bus Taps                               | 3-15 |

| Using the BSCAN Symbol                          | 3-18 |

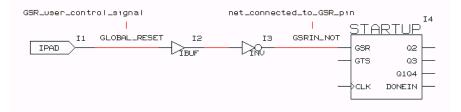

| Using the STARTUP Symbol                        | 3-19 |

| Using the CONFIG Symbol to Specify Part Type    | 3-19 |

| Using HDL Direct Methodology                    | 3-20 |

| Creating Bodies for Non-Schematic Design Blocks |      |

| Creating a Body for a Verilog Netlist           | 3-21 |

| Generating a Body for a Schematic               | 3-22 |

| Generating a Body for an XNF, NGO, or EDIF      |      |

| File                                            | 3-22 |

| Verilog HDL Design Entry                        | 3-22 |

| Translating Your Design                         |      |

#### Chapter 4 Functional Simulation

| Introduction                                             | 4-1    |

|----------------------------------------------------------|--------|

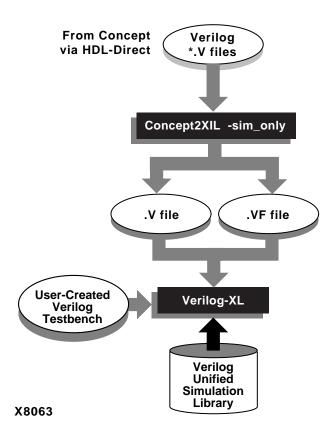

| Unified Library Based Functional Simulation              | 4-2    |

| Pure Concept Schematic Without LogiBLOX Elements         | 4-3    |

| Creating HDL Views for the Design/ Netlisting the Design | n. 4-3 |

| Creating a Testbench File                                | 4-4    |

| Running the Functional Simulation                        | 4-5    |

| Adding SimWave Support to the Testbench File             | 4-7    |

| Global Reset                                             | 4-8    |

| Pure Concept Schematic Designs With LogiBLOX             | 4-8    |

| Mixed Mode Designs                                       | 4-8    |

| Running the Simulation                                   | 4-9    |

| Global Reset                                             | 4-11   |

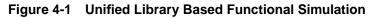

| SIMPRIM Library Based Functional Simulation              | 4-11   |

| Using NGD2VER                                            | 4-13   |

| Running a Verilog Functional Simulation                  | 4-14   |

| Global Reset                                             | 4-14   |

|                                                          |        |

#### Chapter 5 Design Implementation

| Converting the Concept Design to an EDIF File | 5-3 |

|-----------------------------------------------|-----|

| Implementing the Design                       | 5-5 |

#### Chapter 6 Timing Simulation

| Post-Map Timing Simulation (FPGAs)    | 6-1 |

|---------------------------------------|-----|

| Mapping and Back-Annotation           | 6-3 |

| Running NGD2VER                       | 6-4 |

| Running the Verilog Timing Simulation | 6-5 |

| Global Reset                          | 6-8 |

|---------------------------------------|-----|

| Post-Implementation Timing Simulation | 6-8 |

| Running NGD2VER                       | 6-9 |

#### Chapter 7 Design and Simulation Techniques

| Replicating Components in a Design (SIZE)                  | 7-1    |

|------------------------------------------------------------|--------|

| Retargeting a Design to a Different Family                 | 7-2    |

| Merging Design Files from Other Sources                    | 7-4    |

| XC4000 Flip-flop Initialization                            | 7-5    |

| IOB Flip-flop Initialization                               | 7-5    |

| CLB Flip-flop Initialization                               | 7-5    |

| XC9500 Flip-flop Initialization                            | 7-5    |

| IOB Flip-flop Initialization                               |        |

| Macrocell Flip-flop Initialization                         | 7-5    |

| Setting Global Set/Reset and Tri-state Signals (FPGAs)     | 7-6    |

| Setting Global Set/Reset                                   |        |

| Designs with No STARTUP Block                              | 7-8    |

| Designs With STARTUP block (XC4000E/L/EX/XL/XV and 2       | XC5200 |

| Devices Only)                                              |        |

| Setting Global Tri-state (XC4000 and XC5200 Outputs Only). | 7-15   |

| Designs with No STARTUP Block                              | 7-17   |

| Designs With STARTUP block (XC4000E/L/EX/XL/XV and 2       | XC5200 |

| Devices Only)                                              | 7-18   |

| Setting Global PRLD (CPLD Designs)                         | 7-21   |

| Unified Library Functional Simulation                      | 7-21   |

| Post-NGDBuild and Post-Implementation Timing Simulation    | 7-22   |

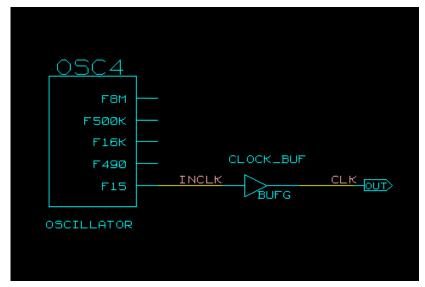

| Oscillator Functions (OSC, OSC4, OSC5)                     | 7-22   |

|                                                            |        |

#### Chapter 8 Manual Translation

| 8-1 |

|-----|

| 8-1 |

| 8-1 |

| 8-2 |

| 8-2 |

| 8-3 |

| 8-3 |

| 8-4 |

| 8-5 |

| 8-5 |

| 8-6 |

| 8-6 |

|     |

|           | Post-Implementation Timing Simulation     | 8-6  |

|-----------|-------------------------------------------|------|

| Chapter 9 | Schematic Design Tutorial                 |      |

|           | Introduction                              | 9-2  |

|           | Required Background Knowledge             | 9-3  |

|           | Design Flow                               |      |

|           | Software Installation                     | 9-4  |

|           | Required Software                         |      |

|           | Before Beginning the Tutorial             |      |

|           | Standard Directory Structure              | 9-5  |

|           | Tutorial Directory and Files              | 9-5  |

|           | Copying the Tutorial Files                | 9-7  |

|           | Setting Up for Concept                    | 9-7  |

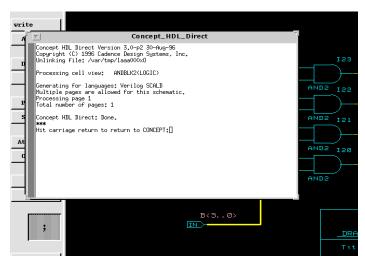

|           | Using HDL Direct                          | 9-9  |

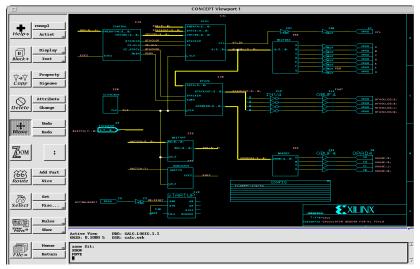

|           | Starting Concept                          | 9-10 |

|           | Using the Mouse in Concept                | 9-11 |

|           | Left Mouse Button                         | 9-11 |

|           | Middle Mouse Button                       | 9-11 |

|           | Right Mouse Button                        | 9-12 |

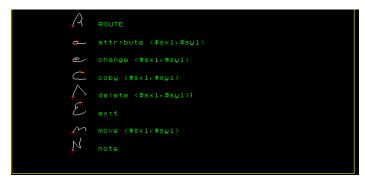

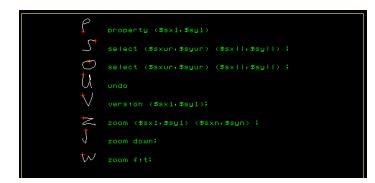

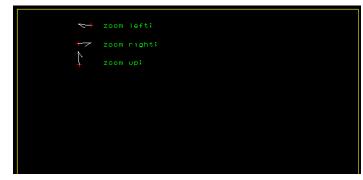

|           | Strokes                                   | 9-12 |

|           | Selecting Commands from the Menu Bar      | 9-13 |

|           | Entering Commands from the Keyboard       |      |

|           | Cancelling Commands                       | 9-13 |

|           | Manipulating the Screen                   | 9-13 |

|           | Saving a Design Directory                 |      |

|           | Quitting Concept                          |      |

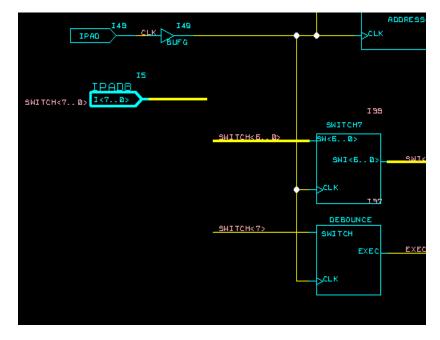

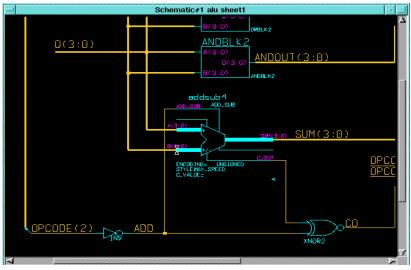

|           | Completing the Calc Design                | 9-14 |

|           | Design Description                        |      |

|           | Targeting XC9500 Devices                  |      |

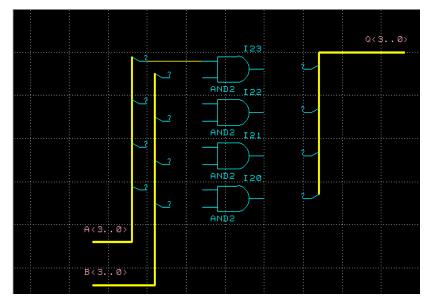

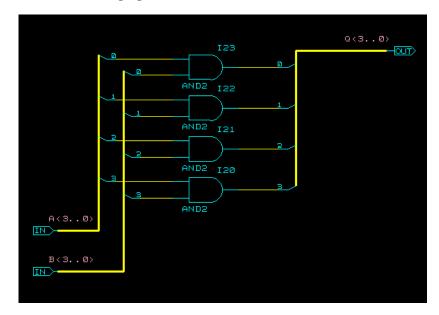

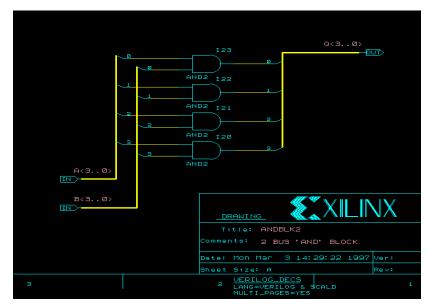

|           | Creating Schematics for ANDBLK2 Symbol    |      |

|           | Opening a Schematic                       |      |

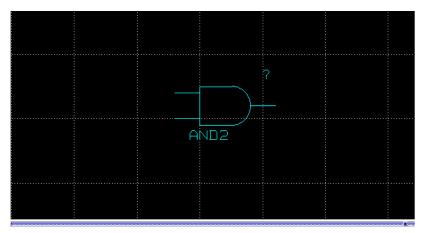

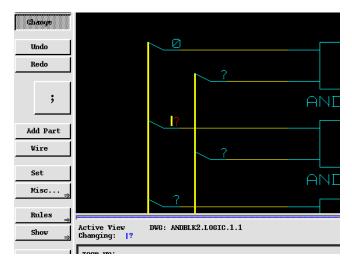

|           | Adding the First Component to a Schematic |      |

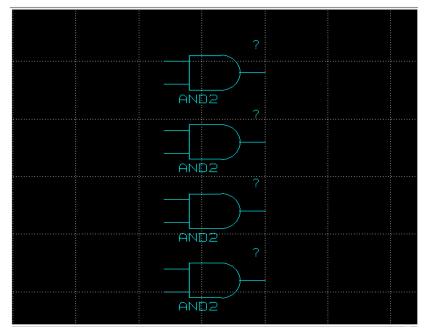

|           | Placing Additional Components             |      |

|           | Copying a Component                       |      |

|           | Moving a Component                        |      |

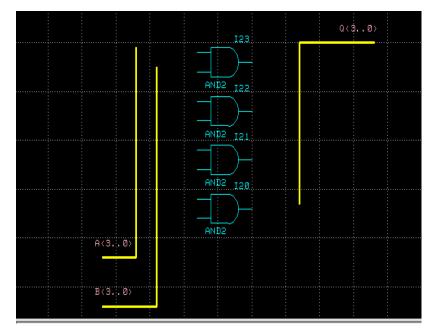

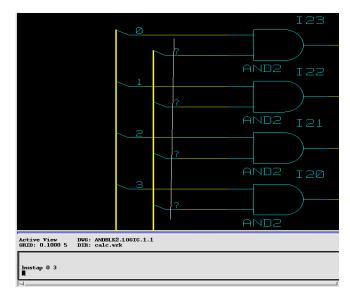

|           | Adding and Labeling Buses in a Schematic  |      |

|           | Adding Wires and SLICEs to a Schematic    |      |

|           | Adding Values to SLICE Symbols            |      |

|           | Adding Ports                              |      |

|           | Saving the Schematic                      |      |

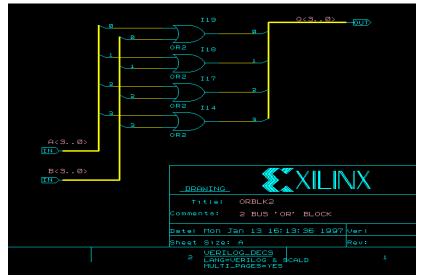

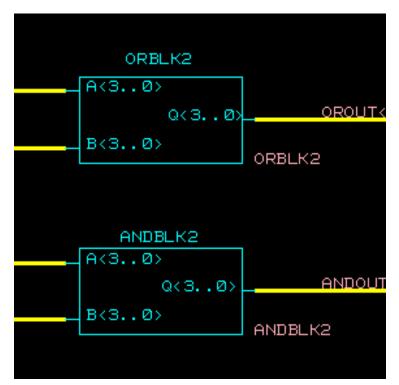

|           | Creating Schematics for ORBLK2 Symbol     |      |

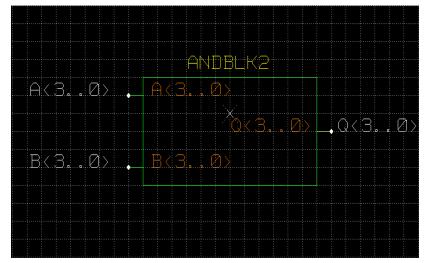

|           | Creating the ANDBLK2 Symbol               | 9-29 |

| Creating the Symbol Outline                           | 9-29 |

|-------------------------------------------------------|------|

| Adding Text                                           | 9-30 |

| Creating the ORBLK2 Symbol                            | 9-31 |

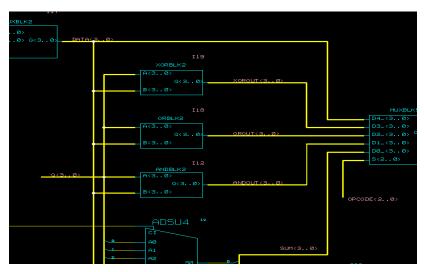

| Editing the ALU1 Schematic                            | 9-31 |

| Placing User-Created Components                       |      |

| Adding Nets, Buses, Ports and Labels                  |      |

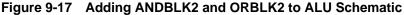

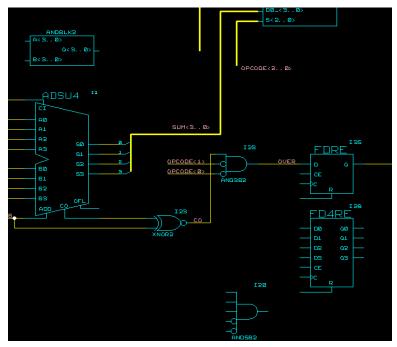

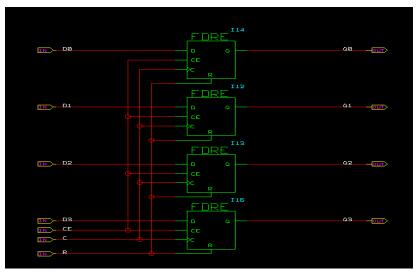

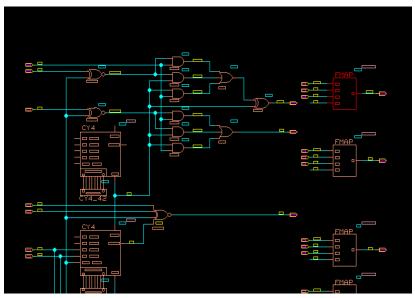

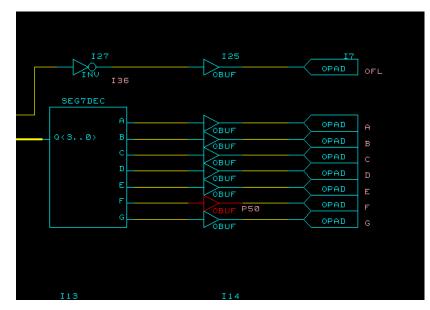

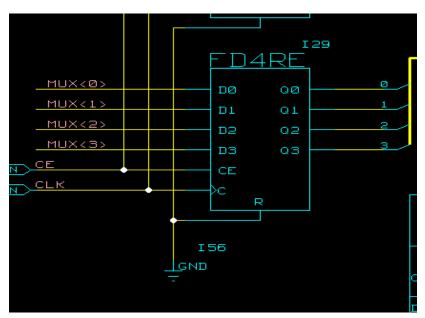

| FD4CE and AND5B2                                      | 9-35 |

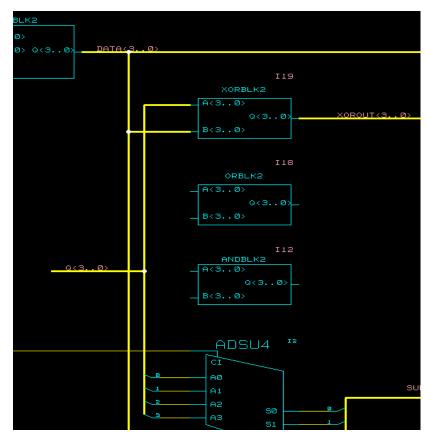

| ANDBLK2 and ORBLK2                                    | 9-36 |

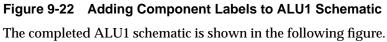

| Adding Labels to Components                           |      |

| Saving the ALU1 Schematic                             | 9-40 |

| Exploring Xilinx Library Elements                     | 9-40 |

| Viewing a Xilinx Soft Macro Schematic                 | 9-41 |

| Viewing a Xilinx RPM (XC4000E Family Only)            | 9-41 |

| Opening the Calc Schematic                            | 9-44 |

| Using the XC4000E Oscillator                          | 9-44 |

| Controlling FPGA/CPLD Layout from the Schematic       | 9-45 |

| Assigning Pin Locations                               | 9-45 |

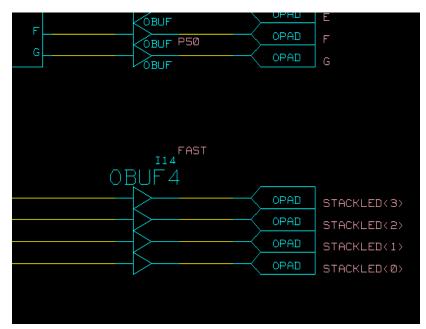

| Designating FAST Pads                                 | 9-47 |

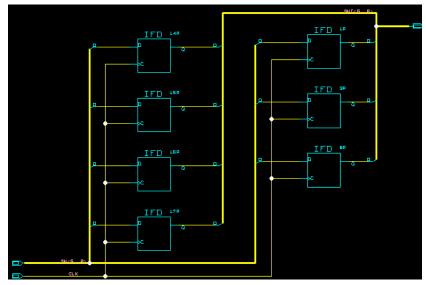

| Using the I/O Flip-Flops                              | 9-48 |

| Saving the Calc Schematic                             |      |

| Modifying the Design for non-XC4000E/EX Devices       | 9-49 |

| Targeting the Design for the XC9500 Family            |      |

| Targeting the Design for the 3000A and 5200 Family    | 9-51 |

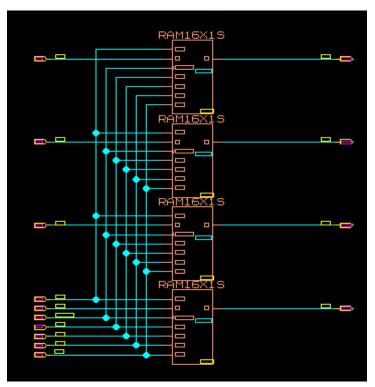

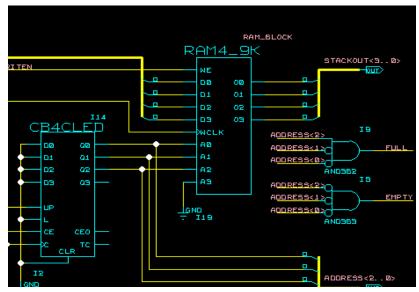

| RAM Stack Implementation                              | 9-51 |

| Using the Device-Independent Register File            | 9-52 |

| Removing the XC4000E Oscillator                       | 9-53 |

| Using LogiBLOX                                        |      |

| Creating a LogiBLOX Module                            |      |

| Creating a Symbol for the LogiBLOX Module             |      |

| Other Special Components                              |      |

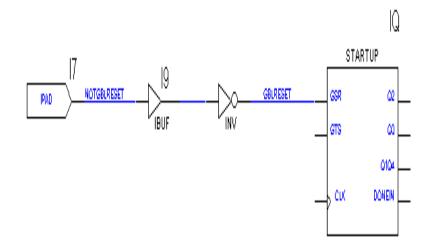

| The STARTUP Block (Optional, XC4000E/EX and XC5200 on |      |

| Adding the CONFIG Symbol (Optional)                   |      |

| Using a Constraints File                              |      |

| Performing Functional Simulation                      |      |

| Using CONCEPT2XIL                                     |      |

| Creating a Verilog Test Fixture                       |      |

| Timescale                                             |      |

| Test Fixture Module Declaration                       |      |

| Displaying Values                                     |      |

| Opening a Waveform Database for SimWave               |      |

| Defining a Clock                                      |      |

| Asserting the Global Set/Reset                        | 9-69 |

| Assigning Values to the Inputs                     | 9-71 |

|----------------------------------------------------|------|

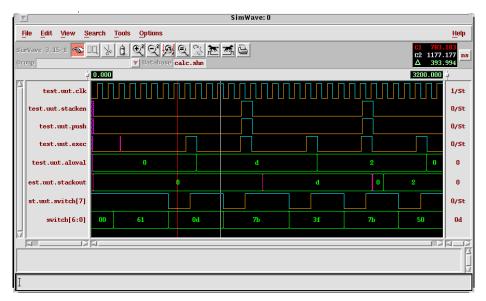

| Invoking the Verilog-XL simulator                  | 9-73 |

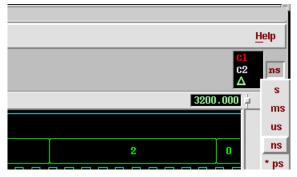

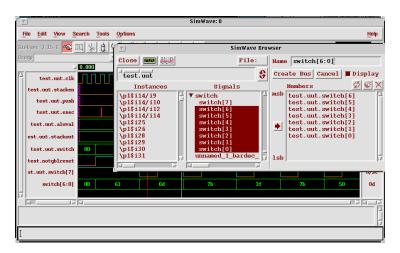

| Using SimWave                                      | 9-75 |

| Invoking SimWave                                   | 9-75 |

| Changing the View in SimWave                       | 9-76 |

| Splitting Up and Bundling a Bus in SimWave         | 9-77 |

| Using CONCEPT2XIL for Implementation               | 9-79 |

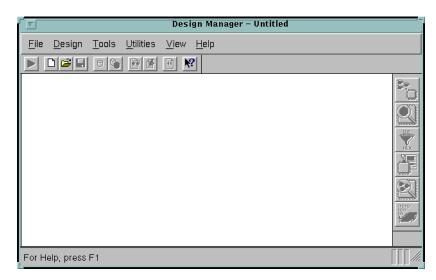

| Using the Xilinx Design Manager                    | 9-80 |

| Performing Timing Simulation                       | 9-86 |

| Invoking Verilog-XL for Timing Simulation          | 9-86 |

| Examining Routed Designs with EPIC                 | 9-87 |

| Verifying the Design Using a Demonstration Board   | 9-87 |

| Creating and Downloading the Bitstream             | 9-88 |

| Making Incremental Design Changes                  | 9-88 |

| Making an Incremental Schematic Change             | 9-89 |

| Translating the Incremental Design                 | 9-90 |

| Verifying the Change in the Demonstration Board    | 9-91 |

| Command Summaries                                  | 9-92 |

| Functional Simulation for XC4000E Family Designs   | 9-92 |

| Basic Translation for XC4000E Family Designs       | 9-92 |

| Timing Simulation for XC4000E Family Designs       | 9-93 |

| Incremental Translation for XC4000E Family Designs | 9-93 |

| Further Reading                                    | 9-93 |

|                                                    |      |

### Appendix A Glossary

| body                              | A-1 |

|-----------------------------------|-----|

| cds_action = "ignore";            | A-1 |

| cds.lib                           | A-1 |

| chips_prt                         | A-1 |

| CONCEPT2XIL                       | A-1 |

| Concept                           | A-2 |

| Concept Setup Files               | A-2 |

| Concept Unified Schematic Library | A-2 |

| CPLD                              | A-2 |

| EDIF                              | A-2 |

| EDIF2NGD                          |     |

| genview                           | A-3 |

| global.cmd                        |     |

| HDL                               | A-3 |

| HDLConfig                         | A-3 |

| HDL Direct                        | A-3 |

| iterated instances                | A-4 |

| logic drawing                      | A-4 |

|------------------------------------|-----|

| LogiBLOX                           | A-4 |

| MAP                                | A-4 |

| master.local                       | A-4 |

| mixed mode design                  | A-4 |

| NGDAnno                            | A-5 |

| NGDBuild                           | A-5 |

| NGD2VER                            | A-5 |

| PAR                                | A-5 |

| SCALD                              | A-5 |

| SIR2EDF                            | A-6 |

| SIZE                               | A-6 |

| Synergy                            | A-6 |

| testbench file                     |     |

| Unified Library                    | A-6 |

| VAN                                | A-6 |

| Verilog                            | A-7 |

| Verilog SIMPRIM Library            | A-7 |

| Verilog Unified Simulation Library | A-7 |

| Verilog-XL                         | A-7 |

| VLOG2XIL                           | A-7 |

| .wrk file                          | A-8 |

| XIL2CDS                            | A-8 |

| Xilinx Design Manager              | A-8 |

| XNF                                | A-8 |

|                                    |     |

### Appendix B Program Options

| CONCEPT2XIL                | B-1 |

|----------------------------|-----|

| Syntax                     | B-1 |

| Options                    | B-1 |

| -cdslib filename           | B-1 |

| -family family_name        | B-2 |

| -gcmd filename             |     |

| -help                      | B-2 |

| -log filename              | B-2 |

| -rundir dir_name           | B-2 |

| -sim_only                  |     |

| Files                      |     |

| Input Files                | B-2 |

| Output Files               |     |

| Error and Warning Messages |     |

| Error Message              |     |

| Error Message                              | B-4  |

|--------------------------------------------|------|

| Error Message                              | B-5  |

| CPLD                                       | B-5  |

| DSGNMGR                                    | B-5  |

| LBGUI                                      | B-6  |

| NGDAnno                                    | B-6  |

| NGDBuild                                   | B-6  |

| NGD2VER                                    | B-6  |

| Syntax                                     | B-7  |

| Options                                    | B-7  |

| -tf                                        | B-7  |

| -ul                                        | B-7  |

| -pf                                        | B-8  |

| Files                                      | B-8  |

| Input Files                                | B-8  |

| Output Files                               | B-8  |

| PAR                                        | B-9  |

| VERILOG                                    | B-9  |

| Syntax                                     | B-9  |

| Options                                    | B-10 |

| +delay_mode_unit                           | B-10 |

| -f full_path_to_verilog_configuration_file |      |

| -y full_path_to_library_name               |      |

| +libtext+                                  | B-10 |

| +gui                                       | B-10 |

| Files                                      | B-11 |

| Input Files                                | B-11 |

|                                            | B-12 |

| XIL2CDS                                    | B-12 |

| - )                                        | B-13 |

|                                            | B-13 |

| -family architecture                       |      |

| -mode mode_type                            |      |

| -pkg pkg_file                              |      |

| -lwbverilog                                | B-14 |

| Files                                      | B-14 |

| Input Files                                | B-14 |

| Output Files                               | B-14 |

|                                            |      |

#### Appendix C Processing Designs with LogiBLOX Components

| Generating the LogiBLOX module            | C-1 |

|-------------------------------------------|-----|

| Creating a Symbol for the LogiBLOX module | C-5 |

| Netlisting the Design for the Functional Simulation | C-6 |

|-----------------------------------------------------|-----|

| Functional Simulation                               | C-6 |

| The testbench file                                  | C-7 |

| Global Reset                                        | C-7 |

#### Appendix D Synopsys/Verilog Design Flow

#### Appendix E Files

| Testbench Template E-1                                               |    |

|----------------------------------------------------------------------|----|

| Sample Test Fixture - XC4000EX Unified Library Functional Simulation |    |

| (GSR and GTS simulation) E-4                                         | •  |

| Sample Test Fixture - XC4000EX Post-NGDBuild Simulation (GSR and     | ∩d |

| GTS simulation) E-6                                                  | ;  |

| Sample Test Fixture, No Startup Block in the Design E-8              |    |

#### Appendix F XILINX.PFF Property Filter File Format

## **Chapter 1**

## Introduction

This chapter contains the following sections:

- "Architecture Support" section

- "Platform Support" section

- "Features" section

- "Design Flows" section

- "Files" section

- "Tutorials" section

- "Online Help" section

- "Design Approaches" section

### **Architecture Support**

You can use the Cadence interface with the XC3000A/L, XC3100A/L, XC4000E/L, XC4000EX/XL/XV, XC5200, and XC9500 Xilinx architectures.

### **Platform Support**

The Cadence design tools are supported on Sun SPARC and HP Series 9000 workstations.

See the following table for a listing of supported operating systems.

Table 1-1 Platforms Supported by Xilinx/Cadence Interface

| Sun 4                      | Solaris     | HP Series 9000 |

|----------------------------|-------------|----------------|

| SunOS 4.1.3<br>SunOS 4.1.4 | Solaris 2.5 | HP-UX 10.20    |

Operating system versions listed in this table are based on the setups required to run the Cadence 97A netlisters, CONCEPT2XIL and XIL2CDS. On the HP-UX platform, only version 10.20 is supported. On Solaris, only version 2.5 is supported.

You may use the Xilinx/Cadence interface with either the Cadence release 97A or later.

### **Features**

The following sections describe the major features available in this release.

#### Xilinx/Cadence Interface

The following table summarizes software supplied by Cadence and Xilinx.

| Product                            | Supplied by<br>Xilinx | Supplied<br>by<br>Cadence |

|------------------------------------|-----------------------|---------------------------|

| Concept Unified Schematic Library  | Х                     |                           |

| Verilog Unified Simulation Library | Х                     |                           |

| Verilog SIMPRIM Library            | Х                     |                           |

| VAN-Analyzed Verilog Library       | Х                     |                           |

| Xilinx Core Tools                  | Х                     |                           |

| Concept (schematic editor)         |                       | X                         |

| Verilog-XL (Verilog simulator)     |                       | X                         |

| Synergy (synthesis tool)           |                       | Х                         |

| CONCEPT2XIL                        |                       | Х                         |

| XIL2CDS                            |                       | X                         |

#### Table 1-2 Xilinx and Cadence Software

#### Libraries

The Xilinx/Cadence interface supports the Cadence 97A and 97B software releases. However, to process Xilinx designs in conjunction with the 97A and 97B releases, you will also need:

CONCEPT2XIL from Cadence to generate EDIF netlists from Concept designs plus the following libraries from Xilinx:

- Concept Unified Libraries for schematic entry

- xce3000

- xce4000e (encompasses XC4000E/L)

- xce4000x (encompasses XC4000EX/XL/XV)

- xce5200

- xce9000

- xcepads

- VAN-Analyzed Verilog libraries (xc\*\*\*\*\_syn) for use by CONCEPT2XIL to create EDIF netlists

- xce3000\_syn

- xce4000e\_syn (encompasses XC4000E/L)

- xce4000x\_syn (encompasses XC4000EX/XL/XV)

- xce5200\_syn

- xce9000\_syn

- Verilog Unified Library simulation models for Verilog functional simulation

- verilogxce3000

- verilogxce4000e (encompasses XC4000E/L)

- verilogxce4000x (encompasses XC4000EX/XL/XV)

- verilogxce5200

- verilogxce9000

- SIMPRIM-based Verilog simulation models for Verilog timing simulation and post-NGDBuild functional simulation.

### Schematic and Verilog Design Entry

The Xilinx/Cadence interface supports these design entry methodologies:

- Concept schematic entry

- Verilog HDL entry (Supported by Cadence)

#### Direct Generation of Structural Verilog Netlist from Concept Schematics

You can generate a Xilinx Unified Library-based structural Verilog netlist for your design directly from a Concept schematic using the Concept HDL Direct design methodology. See the "Concept Setup Library Files" section of the "Getting Started" chapter for details on how to set up your system for HDL Direct.

### **Standard EDIF Netlist**

The Xilinx core tools read a standard EDIF 2.0.0 netlist as input. EDIF2NGD is the Xilinx tool that translates the EDIF file to a Xilinx NGD (Native Generic Database) file. This netlisting capability makes it easy for you to integrate third party design entry and simulation tools. If you want to implement your design using the Xilinx software, you must first generate a structural Verilog netlist for your design directly from a Concept schematic using HDL Direct. (HDL Direct must be set to On in Concept.) The resulting Verilog netlists are then converted to a standard EDIF netlist using the CONCEPT2XIL netlister.

#### Concept

Concept is one of the two schematic editors supported by Cadence; Composer is the other schematic entry platform. The Xilinx/Cadence interface for M1 supports only the Concept schematic editor.

#### Verilog-XL

Verilog-XL is Cadence's Verilog HDL simulator. This simulator is used in the Xilinx/Cadence design flow to verify the functionality of your design. You can use Verilog-XL to perform Unified Library based functional simulation and SIMPRIM-based functional simulation. You may also use Verilog-XL for SIMPRIM-based timing simulation. Timing simulation is performed using a structural Verilog netlist and an SDF file created by NGD2VER. The SDF file contains the timing data for the design.

This release supports the use of Verilog-XL to simulate behavioral Verilog, as well as Verilog gate level netlists composed of SIMPRIM elements. This release also supports gate-level simulation of Logi-BLOX components. Gate level netlists are generated by NGD2VER.

#### CONCEPT2XIL

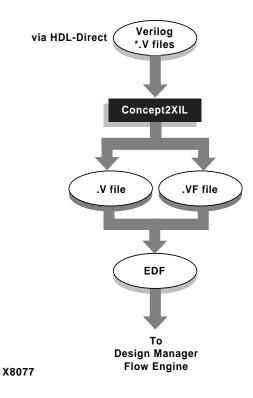

The command line program, CONCEPT2XIL, is the Cadence Concept EDIF netlister. The CONCEPT2XIL program converts the Verilog (.V) file produced by Concept to an EDIF (.EDF) file, which can then be input to the Xilinx core implementation tools. CONCEPT2XIL is shipped and supported by Cadence Design Systems.

#### XIL2CDS

XIL2CDS is a command line utility shipped by Cadence that allows you to integrate your chip-level design into a board level schematic.

Contact Cadence for more information about XIL2CDS.

#### NGD2VER

NGD2VER generates a structural SIMPRIM library-based Verilog netlist that points to the SIMPRIM library when the -ul option is specified. A *design*.tv testbench template file can also be created by specifying the -tf option.You can use the template to create a testbench to verify your design. If there is timing information available in a mapped or routed NGA file, an SDF file is also generated.

#### Simulation of Synopsys Designs

The Xilinx/Cadence interface supports post-synthesis and timing simulation of Synopsys designs entered in Verilog HDL through the generic Verilog HDL netlister, NGD2VER, which is shipped with the Xilinx core tools. For more information, refer to the "Synopsys/Verilog Design Flow" appendix.

#### Automatic Library Specification

NGD2VER will generate the Verilog-XL `uselib statement in your Verilog netlist referencing the SIMPRIM library when you specify the -ul option.

#### **Waveform Viewer Support**

NGD2VER can add support for the Cadence SimWave Waveform Viewer by writing out \$shm\_open and \$shm\_probe directives to your Verilog netlist to create a Simulation History Manager (SHM) database. The SHM directives are incorporated into the test fixture (.tv) created by NGD2VER.

#### LogiBLOX

LogiBLOX is a Xilinx tool that you can use to create high-level functional modules that can be incorporated into a schematic or an HDLbased design. LogiBLOX is only supported in standalone mode for the Cadence interface. After you create your modules, you must use the Concept genview command to generate bodies for your modules. See the "Processing Designs with LogiBLOX Components" appendix for details.

#### **Timing Constraints**

You can specify timing constraints in your Concept schematic to guide the place and route tools; timing constraints can be added as properties. For details about timing constraints, refer to the "Using Timing Constraints" chapter in the *Development System Reference Guide*.

You can also place constraints in an external constraints file (\*.ucf extension) that EDIF2NGD can process. For details on user constraint files, refer to the "The User Constraints (UCF) File" chapter in the *Development System Reference Guide*.

#### Synergy Support

Synergy is Cadence's synthesis tool. Synergy can synthesize designs entered in either Verilog HDL or VHDL. The Xilinx interface to Synergy is available only from Cadence Design Systems.

### **Design Flows**

The design flow you use for performing design entry and simulation depends on whether you use schematic design entry or HDL design entry.

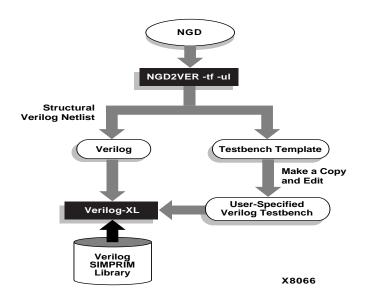

In either case, the easiest and most automatic way to implement your design is to use the Xilinx Design Manager graphical interface. You can also run the various programs in the design flow manually from a UNIX command prompt. The programs in the FPGA design implementation flow are described in the "Program Options" appendix. These commands are also described in detail in the *Development System Reference Guide*.

The programs from the CPLD design flow are described in the *CPLD Schematic Design Guide* and *CPLD Synthesis Design Guide*.

The Xilinx/Cadence interface supports the following design flows:

- Schematic entry with the Unified Libraries components, Logi-BLOX components, or both;

- Schematic entry with Concept Unified Library schematic components plus Xilinx-compliant EDIF or NGO blocks

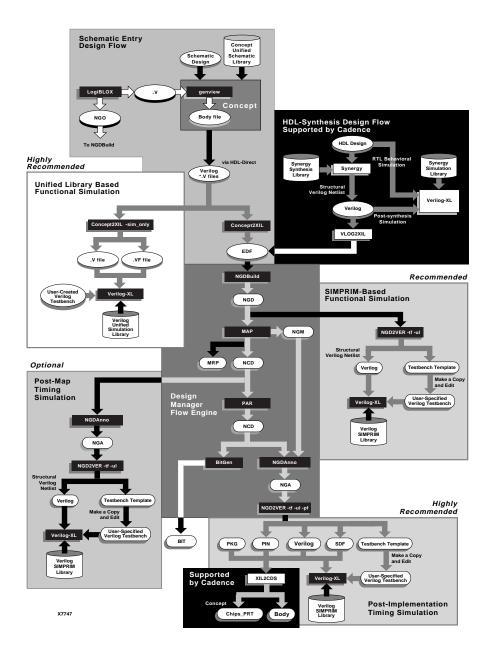

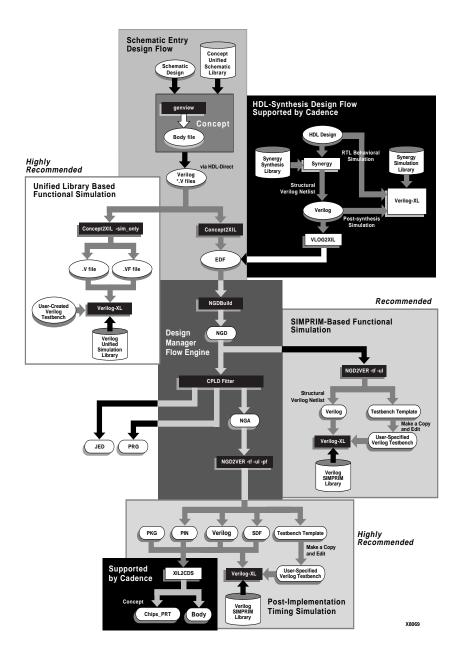

The following two figures show the highlights of the design process for: FPGA design and CPLD design. Note that many of the details in both figures are the same except within the blocks labelled "Design Manager Flow Engine" and "Schematic Entry Design Flow."

Figure 1-1 Overall Cadence Design Flow — FPGA Design

Figure 1-2 Overall Cadence Design Flow — CPLD Design

### Files

The following files are involved in the processing of a design through the Cadence interface:

- CONCEPT2XIL creates an .EDF file, which is an EDIF netlist file.

- EDIF2NGD creates an .NGO file, which contains netlist information in a proprietary data base format; it is a binary file.

- A .UCF file, an input file to NGDBuild, contains user-specified constraints for the map, place, and route tools. This file contains I/O locations and maximum timing delays.

- NGDBuild creates an .NGD file, which is a Native Generic Database file; it contains a gate-level logical description of the design.

- MAP or PAR create an .NCD file, which is a Native Circuit Design file; it contains a physical description of the design.

- NGDAnno creates an .NGA file, which contains physical timing delay information.

- NGD2VER creates a .v file, .tv, .pin, and .SDF file if the input file is a .NGA file when invoked with the -tf and -pf options.

The -tf option creates a .tv file, which is a Verilog test bench or stimulus file template.

The -pf option creates a .pin file which contains pinout information for a design. The -pf option cannot be used if the input to NGD2VER is an NGD file. The .pin file correlates each signal in the design to a pin on a particular Xilinx FPGA package.

The .v and .sdf files are always created when NGD2VER is run with an NGA file input.

An .SDF file is a Standard Delay Format file containing delay information.

• A .PKG file defines the pins on a Xilinx FPGA or CPLD package. These files, which are supplied by Xilinx, are located in \$XILINX/cadence/data.

### **Tutorials**

Xilinx recommends that you perform the tutorials provided in this manual to become familiar with the basic concepts of design, verification, and implementation.

### **Online Help**

Online help is available in the Concept schematic editor by entering help in the Concept command window. You can also access information on Cadence tools (for example, Concept or Verilog-XL) in Open-Book, Cadence's online documentation system, which is shipped by Cadence. To start up OpenBook, simply enter the command openbook at the UNIX prompt.

### **Design Approaches**

You can enter a design using schematics or a hardware description language (HDL) such as Verilog.

### **Schematic Entry**

This general procedure describes the schematic entry flow.

1. Enter your design using the Concept schematic editor.

**Note:** You must have Concept's HDL Direct mode enabled. For details, see the "Getting Started" chapter. With HDL Direct enabled, Concept generates a Verilog netlist automatically when you save a drawing.

- 2. Process the Verilog files that Concept produces with the CONCEPT2XIL netlister using the -sim\_only command line option.

- 3. Functionally simulate your design using Verilog-XL.

- 4. Translate your design into EDIF format using CONCEPT2XIL.

- 5. Use NGDBuild in the Xilinx Design Manager or the command line tool to convert the EDIF file to an NGD file.

- 6. Implement your design with the Xilinx Design Manager/Flow Engine. (You can also use the command line versions of these programs.)

If you perform a manual translation of your design, you can also do a post-MAP simulation to obtain a rough timing simulation before routing delays are added. Alternatively, you can run TRCE after mapping to evaluate timing before net delays are added. For an explanation of TRCE, see the "TRACE" chapter in the *Development System Reference Guide*.

- 7. Perform timing simulation on the design using Verilog-XL and a test bench stimulus file.

- 8. Download your design to the FPGA, or program the CPLD.

- 9. Optionally, use the XIL2CDS program to integrate your chiplevel design into a board level schematic.

### Verilog HDL Entry (Synergy)

Verilog HDL entry flows are supported by Cadence Design Systems.

The steps you follow when using HDL to process a design are similar to those you follow for schematic entry.

- 1. Create the design in Verilog.

- 2. Conduct an RTL (Register Transfer Level) behavioral simulation of your design.

RTL level simulation allows you to verify or simulate a description at the system or chip level. At this level designers generally describe the system or chip by using high-level RTL language constructs.

- 3. Synthesize the design. With Synergy, the output is a .V file.

- 4. Translate your design into EDIF format using VLOG2XIL.

- 5. Use NGDBuild in the Xilinx Design Manager or the command line tool to convert the EDIF file to an NGD file, and merge the NGO files with the rest of the design.

- 6. Optionally, you may generate a post-synthesis Verilog netlist using NGD2VER and perform a SIMPRIM-based functional simulation.

- 7. Implement your design with the Xilinx Design Manager/Flow Engine. You can also use the command line versions of the individual tools to process the design.

If you use the command line flow, optionally, you can also perform a post-map timing simulation of your design before routing delays are added. Alternatively, you can run TRCE after mapping to evaluate timing before net delays are added.

- 8. Perform timing simulation on the design using Verilog-XL and a test bench stimulus file.

- 9. Download your design to the FPGA, or program the CPLD.

- 10. Optionally, use the XIL2CDS program to integrate your chiplevel design into a board level schematic.

#### Mixed-mode Entry, Top Level Schematic

- 1. Capture the top level schematic in Concept.

- 2. Make sure that each non-schematic block is processed to either an NGO, XNF, or EDIF format file. If you have HDL blocks, these must be synthesized first and translated to one of these three formats.

- 3. Generate a Concept body for each non-schematic block, either manually, or using the genview utility in Concept.

- 4. Instantiate the body into the appropriate sheet (page) of your schematic design.

- 5. Save your design. (You must have Concept's HDL Direct mode enabled; for details, see the "Getting Started" chapter.)

- 6. Add the following line after the part list in your Verilog netlist:

parameter cds\_action="ignore";

- 7. Translate your design into EDIF format using CONCEPT2XIL.

- 8. Use NGDBuild in the Xilinx Design Manager or the command line tool to convert the EDIF file to an NGD file and merge the NGO files with the rest of the design.

- 9. Optionally, generate an unrouted post-NGDBuild Verilog netlist using NGD2VER and perform a SIMPRIM-based functional simulation.

If you conduct a manual translation, you may also want to perform a functional simulation to obtain a rough estimate of delays in the unrouted design. 10. Implement your design with the Xilinx Design Manager/Flow Engine, or perform these steps manually if you prefer.

If you perform a manual translation, you may also perform a post-Map simulation to get an approximate estimate of delays in the unrouted design.

- 11. Place and route (PAR) and conduct a back-annotation (NGDAnno) on your design before performing timing simulation.

- 12. Perform timing simulation on the design using Verilog-XL and a test bench stimulus file.

- 13. Download your design to the FPGA, or program the CPLD.

- 14. Optionally, use the XIL2CDS program to integrate your chiplevel design into a board level schematic.

### Mixed-Mode Entry, Top Level HDL (Verilog)

- 1. Edit the top level in Verilog

- 2. Instantiate each non-Verilog block in the design, and specify a "preserve" property on each block that corresponds to a schematic block.

- 3. Synthesize the design.

- 4. Write out a Verilog netlist for the design.

- 5. Translate your design into EDIF format with VLOG2XIL.

- 6. Implement your design with the Xilinx Design Manager/Flow Engine, or perform these steps manually, if you prefer. If you process your design manually, you can also do a post-MAP timing simulation to obtain a rough idea of whether your timing requirements can be met.

- 7. Perform timing simulation on the design using Verilog-XL.

- 8. Download your design to the FPGA or program the CPLD.

## **Chapter 2**

## **Getting Started**

This chapter lists the required software and describes how to configure your system to use the Cadence design tools for creating and processing Xilinx designs. The Xilinx/Cadence Interface supports the following Cadence programs: Concept and Verilog-XL. For Synergy synthesis support, contact Cadence Design Systems.

This chapter contains the following sections:

- "Required Software" section

- "Setting Up Your Environment" section

- "Invoking Concept" section

- "Exiting Concept" section

### **Required Software**

To enter designs using schematics and program Xilinx FPGAs and CPLDs, you need the following software programs:

- Cadence Release 97A or later; see the "Platform Support" section of the "Introduction" chapter for a list showing which version you should use on your particular platform. Your installation of Cadence should include the following components:

- a) Concept

- b) Verilog-XL

- c) CONCEPT2XIL (EDIF netlister)—available from the Cadence ftp site

- d) XIL2CDS (for optional board-level integration)—available from the Cadence ftp site

- Libraries supplied by Xilinx:

- a) For schematic entry: Concept Unified Libraries

- b) For Verilog functional simulation: Verilog Unified Library simulation models

- c) For Verilog timing simulation: SIMPRIM-based Verilog simulation models

- Xilinx Development System software; your installation of Xilinx products must include at least the following executables:

- a) EDIF2NGD

- b) NGDBuild

- c) MAP

- d) PAR

- e) TRCE (Optional for static timing analysis)

- f) NGDAnno

- g) NGD2VER

- h) BitGen

For a description of Xilinx/Cadence platform support, refer to the "Platform Support" section of the "Introduction" chapter.

#### Setting Up Your Environment

When you have finished the installation of the Xilinx software, verify that your .cshrc or setup file contains lines similar to those outlined in the following subsections.

**Note:** In the following variable settings, *platform* is **sun** (Sun4), **sol** (Solaris), or **hp** (HP-UX).

#### **Required Environment Variables (All Platforms)**

Verify that the following variables are set up;

setenv XILINX path\_to\_Xilinx\_root\_dir

where *path\_to\_Xilinx\_root\_dir* is the location of the Xilinx software.

If you are using the Motif version of DynaText or the EPIC editor, you must set an environment variable to access the set of Key bindings used by a Motif application. You will find an XKeysymDB file has been installed into your \$XILINX/bin/*platform* directory by the Xilinx install. You must do the following to access this file:

#### setenv XKEYSYMDB \$XILINX/bin/platform/XKeysymDB

Failure to set up this environment variable will result in the following types of messages being displayed when you attempt to start up the DynaText viewer. The listed keys are not usable:

```

Warning: translation table syntax error: Unknown

keysym name: osfActivate

Warning: ... found while parsing ':

<Key>osfActivate:ManagerParentActivate()fDown

```

Set your LM\_LICENSE\_FILE variable to point to the Xilinx license file (license.dat):

```

setenv LM_LICENSE_FILE path_to_Xilinx_license_file ;\

path_to_Cadence_license_file

```

Make sure the LD\_LIBRARY\_PATH is set up to point to the Xilinx software. Add the path to your current path for Sun or Solaris.

```

setenv LD_LIBRARY_PATH \

${LD_LIBRARY_PATH}:$XILINX/bin/platform

```

**Note:** The backslash ( $\setminus$ ) at the end of a line is a continuation character indicating that the line wraps to the next line. If you use the backslash character, it *must* be the last character on the line.

If you are using a Sparc station, set LD\_LIBRARY\_PATH as follows:

```

setenv LD_LIBRARY_PATH \

${LD_LIBRARY_PATH}:$XILINX/bin/platform: \

/usr/openwin/lib

```

If you are using an HP workstation, set the SHLIB\_PATH.

setenv SHLIB\_PATH \${XILINX}/bin/hp:lib:/usr/lib

#### **Concept Environment Setup**

In addition, you must set your Concept environment variables in your .cshrc shell or setup file and configure your Concept startup and library files.

#### **Concept Environment Variables**

1. Set the CDS\_INST\_DIR environment variable to the location of your Cadence installation directory in your .cshrc or setup file.

setenv CDS\_INST\_DIR location\_of\_Cadence\_tools

**Note:** It is common to create a soft link called "tools" under **\$CDS\_INST\_DIR**, and to link it to the directory **\$CDS\_INST\_DIR**/ tools. *platform*, where *platform* is "hppa" (for the HP), "sun4" (for SunOS), or "sun4v" (for Solaris). For example, to create a link called "tools" to your "tools.sun4" Cadence subdirectory (SunOS), use the following commands:

cd \$CDS\_INST\_DIR

ln -s tools.sun4 tools

If your Cadence installation directory does not have a link called "tools", you can either add the link yourself, or substitute "tools.*platform*" wherever you see "tools" in the settings.

2. Add CDS\_INST\_DIR to your path in your .cshrc or setup file.

```

set path = ($CDS_INST_DIR/tools/bin \

$CDS_INST_DIR/tools/pic/picdesigner/bin \

$CDS_INST_DIR/tools/editor/lib $path)

```

#### **Concept Setup Library Files**

Before you begin design entry, verify that your Concept setup files are set up properly. These four files include *startup.concept*, *cds.lib*, *global.cm*d, and *master.local*. The files should be located in your current working Concept directory. Xilinx has provided examples of each of these files in \$XILINX/cadence/examples.

1. Use a text editor to modify your startup.concept file so that you are set up to run HDL Direct. Xilinx recommends that you add the following lines to the file to enable HDL Direct.

```

set hdl_direct on

set hdl_checks on

set check_signames on

set check_net_names_hdl_ok on

set check_port_names_hdl_ok on

set check_symbol_names_hdl_ok on

set capslock_off

```

HDL Direct will run automatically when you write your design. Error and warning messages are written to the Concept HDL Direct window and to the hdldir.log file.

These commands can also be set directly in Concept by entering them in the Concept command window.

Xilinx also recommends that you include the command, set capslock\_off, in the startup.concept file.

```

set capslock_off

```

With this command, Concept maintains the case of the property strings that you add to the design. This setting is important when you define linked properties that reference other pre-defined properties, as in linked timespecs. The referencing of pre-defined timespec properties is case-sensitive. When HDL Direct writes out these properties to the viewprp file for the specific Concept drawing being saved, it will preserve the case of all properties when the capslock key is set to "off", maintaining case, to the viewprps.prp file in the logic view (directory) for the appropriate Concept drawing.

It is not required that you enter this command in the startup file. However, if you do not enter the command, make sure that you enter the command at the command line prompt in Concept *before* you assign property values. If you do not enter the capslock\_off command first, the values will be converted to upper case by default. This may cause problems when defining new TIMEGRPS from existing groups declared in lower case.

2. Create a cds.lib file in your current working Concept directory that points to the VAN-compiled library for the Xilinx architecture you will be using. Concept and CONCEPT2XIL scripts require cds.lib file configuration.

CONCEPT2XIL writes out an EDIF netlist for you based on library components it reads out of the appropriate library in cds.lib. The library it reads depends on the value you specify for the -family option. Following is an example cds.lib file for the xce4000x architecture.

XC4000EX devices.

3. Update your global.cmd file to point to the appropriate Xilinx Concept libraries and define the default name of the SCALD mapping file with the "use" command.

For more details about the global.cmd file, refer to the section "Global.cmd file" in Chapter 2, The Editing Environment, in the *Concept Schematic User Guide*. Following is an example file for the an XC4000ex device:

```

master_library "./master.local" ;

library "xce4000x"

"hdl_direct_lib" ,

"xcepads" ,

"standard" ;

use "design.wrk" ;

root_drawing "unnamed" ;

```

Following is a brief description of each of the library elements:

- xce4000x This text points to the architecture-specific Concept XC4000EX/XL/XV library.

- hdl\_direct\_lib This library contains various components to support HDL Direct methodology, including inports and outports.

- xcepads This text points to the generic Xilinx pad library.

- standard

The standard library contains standard Concept components such as drawing and border symbols.

All four libraries are required.

When accessing a library, Concept searches through the libraries following a "last read, first out" scheme. For the sample global.cmd file, the libraries are searched in the following order: standard, xcepads, hdl\_direct\_lib, and finally xce4000x.

The **use** command specifies the work or project library listing file from which existing design names can be read and viewed in Concept, and to which listings for new design blocks can be written into from Concept. For example, **use** "design.wrk"; indicates that design.wrk is the work file:

FILE\_TYPE = LOGIC\_DIR;

"DESIGN1" 'design1'; "DESIGN2" 'design2';

END.

*design1* and *design2* are the names of the design blocks for this project.

4. Enter the references to any user libraries into the master.local file. For more details about the master.local file, see the section "master.local Abbreviations file" in Chapter 2, The Editing Environment in the *Concept Schematic User Guide*. For M1, it is recommended that you list all Xilinx architecture libraries for Concept in the master.local file. Following is an example user library file for M1 Xilinx designs.

```

file_type = master_library;

"xce9000" 'full path to Xilinx softway

```

```

"xce9000" 'full_path_to_Xilinx_software/cadence/data/xce9000/xce9000.lib';

"xce5200" 'full_path_to_Xilinx_software/cadence/data/xce5200/xce5200.lib';

"xce4000x" 'full_path_to_Xilinx_software/cadence/data/xce4000e/xce4000x.lib';

"xce3000" 'full_path_to_Xilinx_software/cadence/data/xce3000/xce3000.lib';

"xcepads" 'full_path_to_Xilinx_software/cadence/data/xcepads.lib';

```

end.

The xce4000x supports the XC4000EX/XL/XV architectures. The xce4000e supports the XC4000E/L architectures.

## **Verilog Environment Setup**

Set up your Verilog environment so that you can perform functional simulation.

• Set the Verilog environment variable, VERILOGEXE, to point to the location of your Verilog executables.

```

setenv VERILOGEXE $CDS_INST_DIR/tools/\

verilog/bin/verilog

```

• Set VENVHOME to the location where the Verilog 2.0 hierarchy is installed. This variable is used only to assist you with setting the VENV\_PATH and VENV\_LD\_LIB\_PATH variables, and is usually the same as CDS\_INST\_DIR.

#### setenv VENVHOME /tools/cadence97A

• Set VENV\_PATH to the location of the Verilog executables.

```

setenv VENV_PATH "${VENVHOME}/\

tools/bin:${VENVHOME}/tools/dfII/bin"

```

Set VENV\_LD\_LIB\_PATH to the location of libraries used by Verilog.

```

setenv VENV_LD_LIB_PATH ${VENVHOME}/\

tools/lib:${VENVHOME}/tools/verilog/lib

```

• Reset your PATH variable to add the Verilog executables.

```

set PATH="${VENV_PATH}:$PATH"

```

• Add the Verilog libraries to the LD\_LIBRARY\_PATH environment variable.

```

setenv LD_LIBRARY_PATH \

"${VENV_LD_LIB_PATH}:$LD_LIBRARY_PATH"

```

If you are using an HP platform, use the SHLIB\_PATH instead of LD\_LIBRARY\_PATH.

• (Optional) Set up the environment variable CDSDIR. This variable is required by the Verilog Language Sensitive Editor (LSE).

setenv CDSDIR \$CDS\_INST\_DIR/tools

### **Dynatext Environment Variables**

Set up the EBTRC variable to point to the DynaText browser.

setenv EBTRC \$XILINX/bin/platform/ebtrc\_CD

## **Invoking Concept**

To enter Concept from the operating system command line, type concept.

## **Exiting Concept**

To exit Concept, select  $\texttt{File} \rightarrow \texttt{Quit}$ . You may also enter "quit" in the Concept command line window.

## **Chapter 3**

## **Design Entry**

This chapter describes Cadence design entry in relation to the Xilinx Development software. This chapter does *not* discuss in any detail how to use the design tools Concept or Synergy. Design entry procedures are described only for Xilinx-specific software, libraries, and features.

For a detailed description of the Concept design entry tools and procedures, refer to the *Concept Schematic User Guide*. For a list of the manuals that describe the Synergy tool, see the "Verilog HDL Design Entry" section in this chapter.

Before using the design entry tools, ensure that you have set up your environment as described in the "Required Software" section of the "Getting Started" chapter.

This chapter contains the following sections.

- "Concept" section

- "Requirements For HDL Direct Compliance" section

- "Using the Xilinx Concept Unified Schematic Libraries" section

- "Renamed Components" section

- "Verilog/Concept HDL Direct Naming Conventions" section

- "VCC and GND Components" section

- "Using the LogiBLOX Libraries" section

- "Specifying Xilinx Properties and Constraints in Concept" section

- "Attaching Signal Names" section

- "Creating Bus Taps" section

- "Using the BSCAN Symbol" section

- "Using the STARTUP Symbol" section

- "Using the CONFIG Symbol to Specify Part Type" section

- "Using HDL Direct Methodology" section

- "Creating Bodies for Non-Schematic Design Blocks" section

- "Verilog HDL Design Entry" section

- "Translating Your Design" section

## Concept

Concept is a Cadence schematic entry tool. You can capture designs for implementation in the XC3000A/L, XC3100A/L, XC4000E/L, XC4000EX/XL/XV, XC5200, and XC9500 Xilinx architectures.

The Concept libraries include the following:

- Libraries for designing Xilinx FPGAs and CPLDs named xcexxxx

- LogiBLOX modules, which are generated by the lbgui (Logi-BLOX GUI) standalone command for use with Concept, include Verilog and NGO files. The Verilog modules generated by lbgui are used as the input to the Concept genview command to create body files. The NGO files created by lbgui are used to implement the LogiBLOX module in your design.

- VAN-analyzed Verilog libraries for Concept HDL Direct Verilog netlist generation support

For a complete description of how to use Concept, see the *Concept Schematic User Guide*. Also see the *Concept Getting Started Tutorial*.

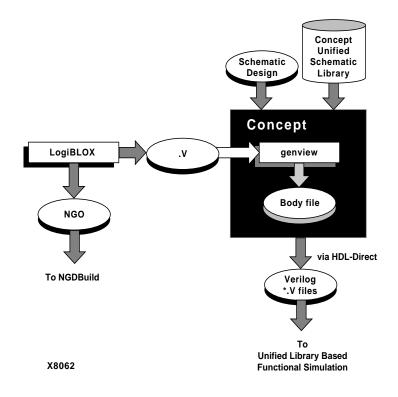

The following illustration shows the schematic entry flow using Concept with the Xilinx-supplied Concept Unified Schematic Libraries. Note that LogiBLOX is not supported for use with CPLDs.

Figure 3-1 Schematic Entry Design Flow

## **Requirements For HDL Direct Compliance**

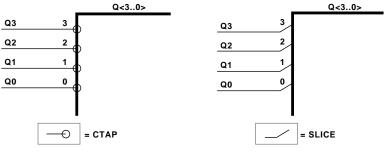

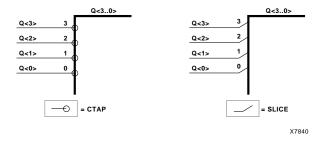

The Xilinx/Cadence schematic design flow requires that SCALD (Structured Computer Aided Logic Design) schematic designs be converted to HDL Direct compliant.

Your SCALD schematic drawings must adhere to the following rules:

- SCALD BIT TAP symbols must be replaced with the HDL Direct SLICE symbols.

- HDL Direct TAP symbols must be used in place of SCALD LSB TAP and MSB TAP symbols.

- Instead of the SCALD convention of attaching an "\I" suffix to interface signals, HDL Direct port symbols from hdl\_direct\_lib

must be attached to the signals in a schematic which correspond to pins on a symbol body at an upper-level of hierarchy in the design. INPORTS should be attached to the inputs, OUTPORTS to the outputs, and IOPORTS to the bidirectional signals of the schematic.

- SIGN EXTEND and SLASH symbols must be replaced with the equivalent wiring.

- The "\I" must be removed from all signal names.

- FLAG symbols must be removed from schematics.

- For signals that end with  $\G$  (which designates them as global signals), remove the  $\G$  and place a forward slash (/) at the beginning of the signal.

- Wires or signals must not be connected to pass-thru pins on pads. Connect them only to the main pin. Use the "bubble\_check off" option with the SCALD compiler.

- NOT bodies must be replaced with wires.

- All signals and symbol names starting with numbers must be renamed to valid Verilog identifiers. For example, replace 1MYSIGNAL with MYSIGNAL1.

- SUPPLY\_0 and SUPPLY\_1 are not supported. Use the GND and VCC symbols from the appropriate Xilinx architecture library.

- The HDL Direct signal concatenation operator ampersand (&) replaces the SCALD signal concatenation operator colon (:).

- The signal replication operator "\R number" and the REPLI-CATE symbol must be replaced with a concatenation of the required number of signals. The SCALD REPLICATE symbol should be replaced in the same way.

- The HDL Direct ALIAS symbols replace the SCALD SYNONYM symbols; however, ALIAS symbols are not supported by Xilinx.

- Signals and bodies may not share the same name.

- Property values must adhere to Verilog naming rules.

For more detailed and up-to-date information, refer to the "Converting SCALD Schematics into HDL Direct Schematics" of the "Using HDL Direct With SCALD Applications" chapter of the Cadence manual, *HDL Direct User Guide*.

## Using the Xilinx Concept Unified Schematic Libraries

Xilinx supplies the Concept Unified Schematic Libraries as part of the Xilinx Development software release. To design Concept schematics using Xilinx devices, you must install the Libraries. In addition, you must also set up your Concept setup files to access these Libraries. Refer to the "Concept Environment Setup" section of the "Getting Started" chapter for details. To verify that Concept is installed and set up so that you can access the Concept Unified Schematic Libraries, perform the following steps.

- 1. Open Concept by entering the command concept at the prompt.

- 2. Select Add Part.

- 3. When the Component Browser dialog box displays, click the list box to the right of the Library field. The list of libraries should display the xce series parts (xce4000e, xce4000ex, etc.) including the pads (xcepads).

To create a Xilinx FPGA or CPLD design with Concept, you can use the XC3000A, XC4000E/L, XC4000EX/XL/XV, XC5200, or XC9000 libraries. The corresponding name for these Xilinx families in Concept are xce3000, xce4000e (XC4000E/L), xce4000ex, xce4000x (XC4000EX/XL/XV), xce5200, and xce9000. In addition, the xcepads library contains the basic pads, such as IOPAD, IPAD, OPAD, and UPAD. You can also use the LogiBLOX modules for designs targeting Xilinx architectures that support LogiBLOX. Your design must contain primitives and macros.

You can only use the libraries for one family when creating your design. For example, you cannot use elements from both the XC4000 and the XC5200 libraries in a single design. Also components in these libraries are no longer sizable. See the "SIZE Property" section.

You can specify design libraries by editing the global.cmd file. The first line of the global.cmd file list of libraries begins with the keyword, "library":

library "lib\_name",["lib\_name"];

*Lib\_name* is a library name like XC4000E. Specify multiple libraries by using a comma (,) to separate each library name. Be sure that a semi-

colon (;) follows your last entry. Refer to the example in \$XILINX/ cadence/examples.

## **FPGA and CPLD Libraries**