Exemplar Logic

**Xilinx Corporation**

Model Technology

# **Applications Note**

Large Device Design Methodology

July 15, 1998

**Revision 2.1**

| OVERVIEW                                                  | 5 |

|-----------------------------------------------------------|---|

| Exemplar, Model Technology & Xilinx Toolflow Overview     | 5 |

| SYNTHESIS PROCESS DESIGN FLOW                             | 6 |

| EXAMPLE SESSION                                           | 7 |

| Example ModelSim RTL Simulation Session                   |   |

| Example Leonardo Session                                  |   |

| Example Alliance Series Place and Route Session           |   |

| Example ModelSim Gate-Level Simulation (with SDF) Session |   |

| ENVIRONMENT SETUP                                         |   |

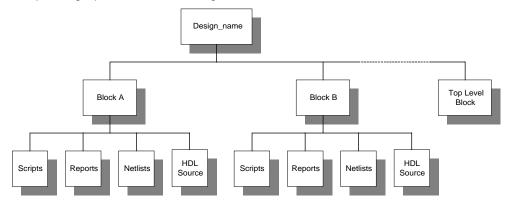

| DIRECTORY STRUCTURE                                       |   |

| SETTING ALIASES                                           |   |

| LEONARDO STARTUP FILES                                    |   |

| Example "exemplar.ini" Startup File                       |   |

| Startup files for UNIX                                    |   |

| Startup files for Windows                                 |   |

| DESIGN METHODOLOGY                                        |   |

| DESIGN PARTITIONING                                       |   |

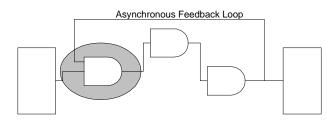

| Asynchronous Feedback Loops                               |   |

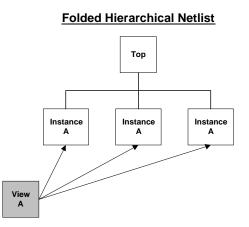

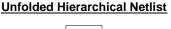

| NETLIST UNFOLDING                                         |   |

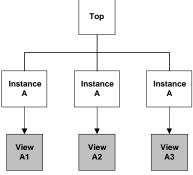

| TOP-DOWN METHODOLOGY                                      |   |

| Block Area Considerations                                 |   |

| Initial Methodology                                       |   |

| Area Critical Designs                                     |   |

| Timing Critical Designs                                   |   |

| Procedure                                                 |   |

| BOTTOM-UP METHODOLOGY                                     |   |

| Register Placement within Blocks                          |   |

| Constraining Sub-blocks for Timing                        |   |

| Constraining sub-block Pins for Loading                   |   |

| Saving Intermediate Netlists                              |   |

| Design Stitching                                          |   |

| Final Optimization                                        |   |

| SYNTHESIZING DESIGNS                                      |   |

| STATE MACHINE SYNTHESIS                                   |   |

| Supported State Machine Styles                            |   |

| Setting State Machine Encoding in Leonardo                |   |

| Reading Designs                                           |   |

| Design Input Commands                                     |   |

| VHDL Synthesis                                            |   |

| Verilog Synthesis                                         |   |

| Synthesizing Operators - ModGen vs LogiBlox               |   |

| SYNTHESIZING DESIGNS WITH BLACK BOXES                     |   |

| RESOURCE SHARING                                          |   |

| HANDLING SPECIAL CELLS                                    |   |

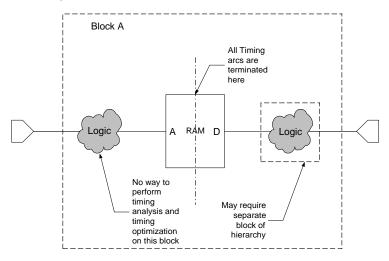

| RAMs                                                      |   |

| Inference                                               |    |

|---------------------------------------------------------|----|

| Timing                                                  |    |

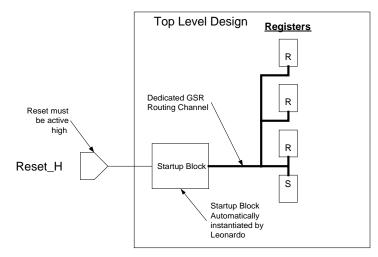

| GSR Resets                                              |    |

| DWANDS                                                  |    |

| Procedure for Using DWANDs                              |    |

| SETTING CONSTRAINTS                                     |    |

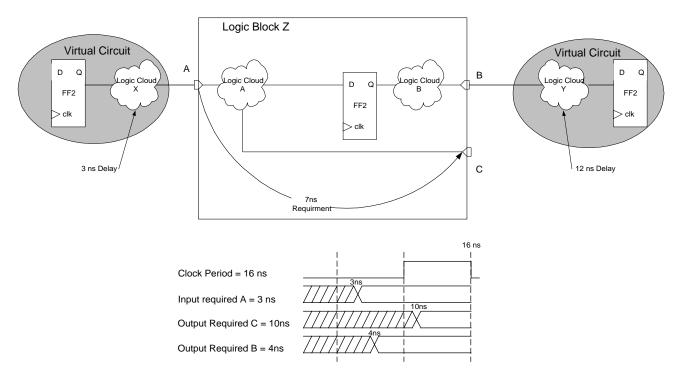

| INTRODUCTION:                                           |    |

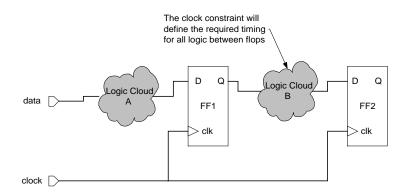

| CLOCKS                                                  |    |

| Maximum Frequency Constraint:                           |    |

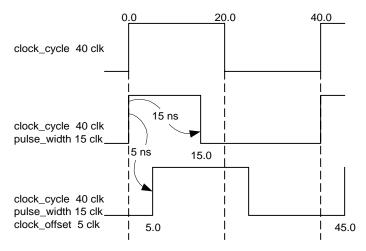

| Clock Constraints:                                      |    |

| Multiple Synchronous Clocks per Block                   |    |

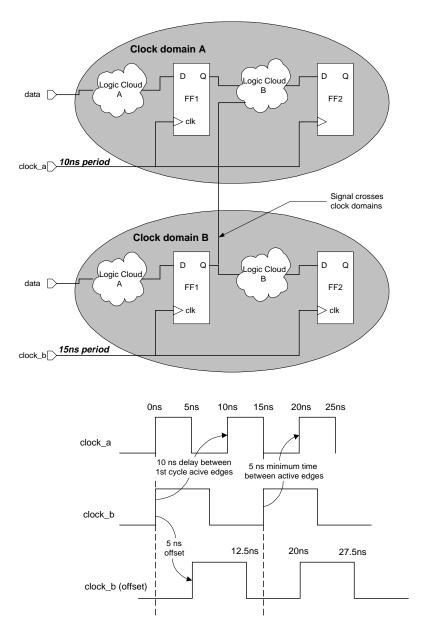

| Multiple Asynchronous Clocks                            |    |

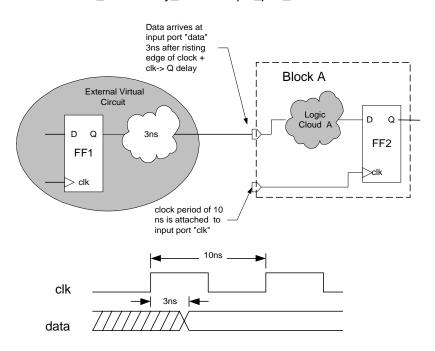

| INPUT ARRIVAL TIME                                      |    |

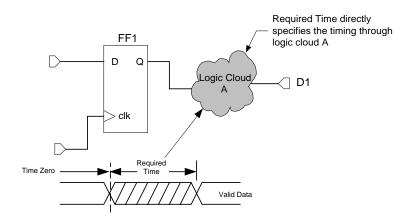

| OUTPUT REQUIRED TIMES:                                  |    |

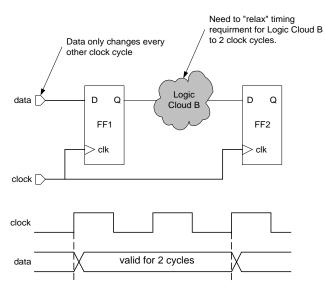

| Multicycle Path Constraints:                            |    |

| FALSE PATH CONSTRAINTS:                                 |    |

| CONSTRAINING PURELY COMBINATORIAL DESIGNS               |    |

| CONSTRAINING MIXED SYNCHRONOUS AND ASYNCHRONOUS DESIGNS |    |

| Procedure for Setting Constraints on Mixed Designs      |    |

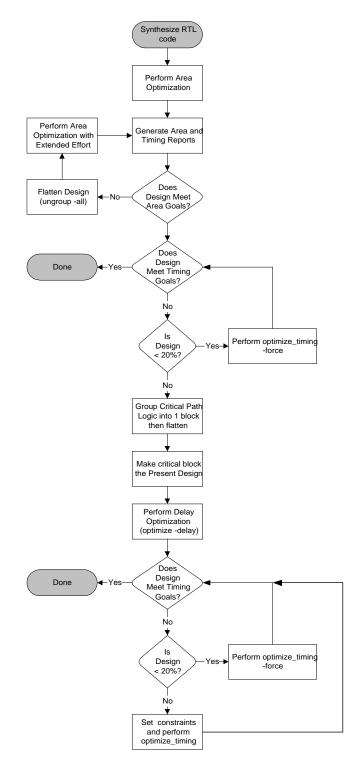

| OPTIMIZATION STRATEGY                                   |    |

| Optimization Flow diagram                               | 42 |

| AREA OPTIMIZATION STRATEGY                              |    |

| TIMING CRITICAL OPTIMIZATION STRATEGY                   |    |

| XILINX OPTIMIZATION                                     |    |

|                                                         |    |

| DECOMPOSE LUTS                                          |    |

| GENERATE TIMESPECS                                      |    |

| PACK CLBS<br>Assigning Pin Numbers                      |    |

|                                                         |    |

| PLACE AND ROUTE WITH ALLIANCE SERIES                    |    |

| GETTING QUICK RESULTS                                   |    |

| THE BALANCE BETWEEN RUN TIMES AND CIRCUIT PERFORMANCE   |    |

| GETTING THE FASTEST CIRCUITS                            |    |

| Tips for Obtaining Faster Circuits                      |    |

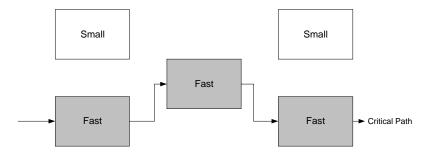

| ROUTING VS. BLOCK DELAY ESTIMATION                      |    |

| APPENDIX A - REFERENCING NETLIST OBJECTS                |    |

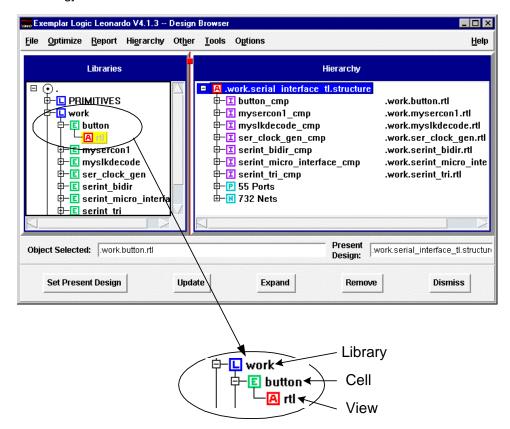

| LIBRARY OBJECTS                                         |    |

| <br>Library                                             |    |

| Cells                                                   |    |

| View                                                    |    |

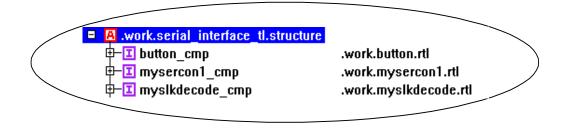

| HIERARCHY OBJECTS                                       |    |

| Instances                                               |    |

| Ports                                                   |    |

| Nets                                                    |    |

| APPENDIX B - HIERARCHY MANIPULATION                     |    |

|                                                         |    |

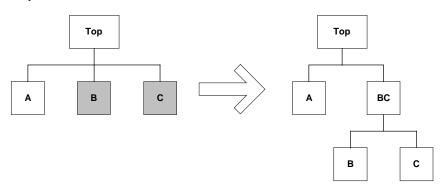

| Grouping                                                |    |

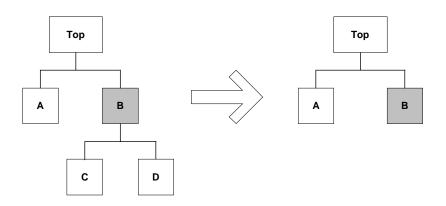

| Ungrouping                                              |    |

| APPENDIX C - COMMAND REFERENCE                          |    |

| APPENDIX D - VARIABLE REFERENCE |

|---------------------------------|

|---------------------------------|

# **Overview**

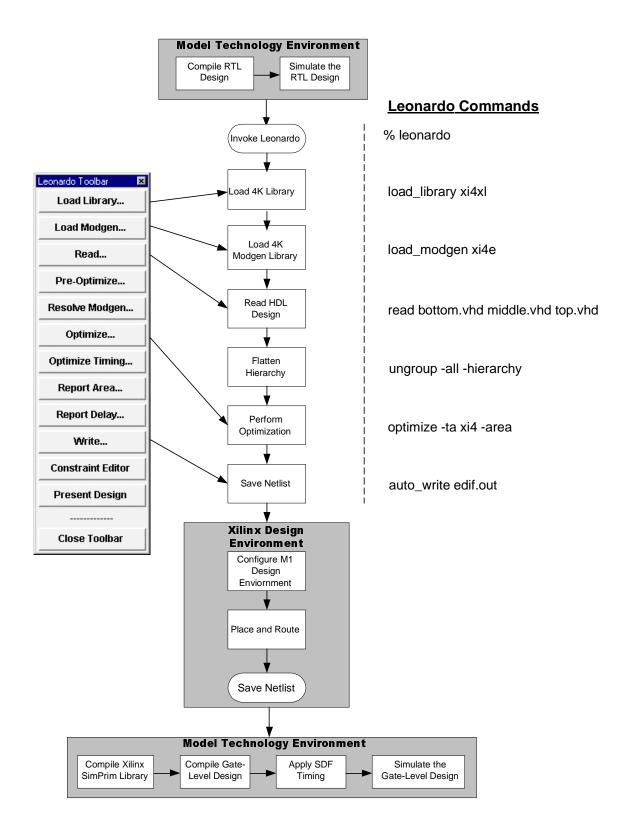

*Leonardo* performs architecture specific synthesis and optimization for all Xilinx devices. *Xilinx Alliance Series* performs placement and routing of the synthesized netlist. *ModelSim* performs pre-synthesis RTL simulation and post-place and route gate-level timing simulation with SDF backannotation of timing. This applications note discusses methodology and optimization settings for Leonardo, Alliance Series and ModelSim when targeting all Xilinx devices. The intent of this appnote is not to exhaustively explore all the different options in the Leonardo, Alliance Series and ModelSim to present a single methodology that works. For information beyond the scope of this document, refer to the following web pages:

| www.exemplar.com | Exemplar Logic   |

|------------------|------------------|

| www.model.com    | Model Technology |

| www.xilinx.com   | Xilinx           |

When targeting all Xilinx devices, Leonardo will map the design into Xilinx lookup tables. Both Galileo Extreme and Alliance Series offer configuration options that dictate how this mapping takes place. In some cases both tools can perform the same functions but, as we'll see, with different results.

The Alliance Series allows the creation of VHDL or Verilog of the placed and routed design along with timing information in a SDF file. This gate-level timing design can then be compiled (along with the Xilinx SIMPRIM library) and simulated in Model*Sim*.

# Exemplar, Model Technology & Xilinx Toolflow Overview

# Synthesis Process Design Flow

# **Example Session**

# Example Model Sim RTL Simulation Session

This section describes the basic steps to compiling and simulating the pre-synthesis RTL design. It is in this step that the functionality of the design is verified prior to synthesis.

1) Invoke Model Sim

# % vsim -or- Programs > Model Tech > ModelSim

| ModelSim PE/Plus                                                  |

|-------------------------------------------------------------------|

| <u>File View Library Project Run Signals Options Window H</u> elp |

| VCOM VLOG VSIM RUN CONT BREAK STEP OVER                           |

| Transcript                                                        |

| ModelSim>                                                         |

|                                                                   |

| Line 1 of 1                                                       |

2) Set Model *Sim* to the directory where the RTL design resides.

|    | -                                                                  |              | -                                                                       |

|----|--------------------------------------------------------------------|--------------|-------------------------------------------------------------------------|

|    | ModelSim> cd c:\mydesign                                           | -or-         | File > Directory                                                        |

| 3) | Create a working library to store the                              | ne compileo  | I RTL design.                                                           |

|    | ModelSim> vlib work                                                | -or-         | Library > New                                                           |

| 4) | Compile the RTL design.                                            |              |                                                                         |

|    | ModelSim> vcom bottom.vh                                           | nd middle.v  | /hd top.vhd                                                             |

|    |                                                                    | -or-         | VCOM button                                                             |

| 5) | Start the Model Sim simulator.                                     |              |                                                                         |

|    | ModelSim> vsim top                                                 | -0           | r- VSIM button                                                          |

| 6) | View all the Model Sim debugging                                   | windows.     |                                                                         |

|    | VSIM> view *                                                       | -or-         | View > All                                                              |

| 7) | Wave and list signals of interest in                               | n the desigr | I.                                                                      |

|    | VSIM> <b>wave /*</b> A<br>VSIM> <b>list /*</b>                     |              | evel signals to the wave window<br>top level signals to the list window |

| 8) | Unless you have a VHDL testber to force the inputs of the RTL desi |              | timulates the RTL design, you will need                                 |

|    | VSIM> force /clk 0 @ 0 n<br>VSIM> force /input 0                   | s, 1 @ 50    | 0 ns –repeat 100 ns                                                     |

| 9) | Run the simulation and analyze th                                  | ne informati | on in the Model <i>Sim</i> debugging windows.                           |

|    | VSIM> run –all                                                     | -or-         | Run > Run Forever                                                       |

### **Example Leonardo Session**

This section provides a detailed example of using Leonardo with the Xilinx Alliance Series toolset targeting the XC4000XL device family. All commands are easily accessible via the toolbar, pulldown menus or the Xilinx specific flow guide. This example will demonstrate Leonardo shell commands.

10) Invoke leonardo

#### % leonardo

LEONARDO{1}

11) Load the Xilinx xi4e library. This will load cell data only

#### LEONARDO{1} load\_library xi4xl

12) Load the Xilinx Modgen library. Modgen is a library of handcrafted implementations for all the inferred design elements. This includes operators, RAMs and counters. There are typically multiple architectures for each element. If this library is not loaded Leonardo will use a generic Modgen library which will not be able to take advantage of Xilinx specific cells.

#### LEONARDO{2} load\_modgen xi4e

13) Read in the HDL files. VHDL design files must be listed in their bottom-up order. Verilog users enjoy "auto-top detection" which means that Leonardo will automatically detect the top-level module from files listed in any order.

**Note:** Leonardo uses file suffixes to figure out file formats; VHDL files = .vhd, .vhdl; Verilog files = .v, .ver; EDIF files = .edn, .edf, .edif.

### LEONARDO{3} read bottom.vhd middle.vhd top.vhd

14) Flatten the design. Hierarchical boundaries prevent or limit important optimizations from occuring. Sometimes there are good reasons to preserve hierarchy, i.e., design size or to separate out speed critical blocks. Only a minimum of hierarchy should be kept. It is recommended to have no more than 50K gates per hierarchical block.

#### LEONARDO{4} ungroup -all -hierarchy

15) Perform optimization. Leonardo can perform both area and timing optimization. In this example we will be performing optimization to achieve the smallest design. Additionally, the effort level can be specified. Quick performs 1 pass and standard performs 4 passes and will take 4 times longer to complete.

#### LEONARDO{5} optimize -ta xi4e -area -effort quick

16) Generate area and timing reports. The optimization runs will display a single area and worst case timing number. Reports are only necessary if more information is required.

#### LEONARDO{6} report\_area

#### LEONARDO{7} report\_delay

Generate an EDIF netlist for Alliance Series. A Netlist pre-processor is built into Leonardo. Because the Xilinx XC4000E technology is specified the correct netlist pre-processing will take place.

# **Example Alliance Series Place and Route Session**

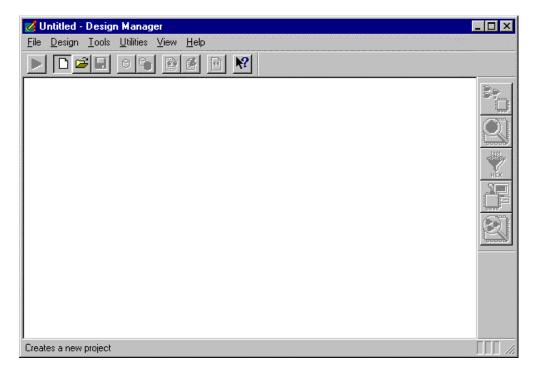

The Xilinx graphical tools are designed to behave, look, and feel like the XACT 6.0 tools. So despite the fact that the core technology algorithms have been redesigned, the graphical tools allow users to run the software in the same way as previous PC versions. For PC customers, the learning curve should be short.

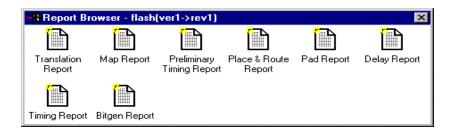

The Design Manger (DM) is the graphical tool that manages the design files that are created during design implementation. The DM also provides push button access to the following Xilinx tools: Flow Engine, Prom File Formatter, Timing Analyzer, Hardware Debugger, and JTAG Programmer.

Start the Design Manager from the Windows 95 or NT desktop by executing the command:

### Selecting Start > Programs > Xilinx > Design Manager

From a shell invoke Design Manager by typing:

#### dsgnmgr

1) Create a New Project in Alliance Series. From the Design Manager toolbar, execute the pulldown menu command

FILE > New Project

Push the *"input design"* button and navigate to the EDIF file generated by Leonardo. This file should have the extension, ".edn".

| 😹 Uart xpj - Design Manager   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |         |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|

| Design Look Utilites 3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | 1       |

| New Project.                  | DM+N<br>Dri+O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |         |

|                               | and the second se |                | (and    |

| Save Project                  | DH+S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 10      |

| Delete Ploject                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | 1731    |

| Enferences.                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |         |

| 1 D ^Training@Giles/dab1.gofo | proj-U art.upj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                | ⊠H=4⊡0° |

| Eyt                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | 1500    |

|                               | New Project<br>Input Design<br>Work Deectory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |         |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OK Cancel Help |         |

| Deales a new project          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Uar            | Uat     |

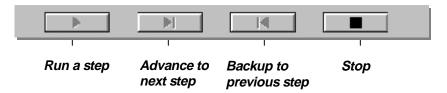

2) Perform "Implement" on the design. From the pulldown menu, execute the command,

Design > Implement

- Select a specific Xilinx part

- Push the Select button. In the "Part Selector" dialog and choose the appropriate member, speed and package combination from those available for the XC4000XV family

**Note:** If the Leonardo command, "generate\_timespec" is issued after optimization and before saving the EDIF netlist then clock frequency timing data is included in the EDIF netlist.

| apj - Dazign Manager                                                                                         | 210 St.                                                                                                                                                                                                        |     |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Icols Litities Yew                                                                                           | Rep                                                                                                                                                                                                            |     |

| TT35NUTPWERVEED                                                                                              |                                                                                                                                                                                                                |     |

|                                                                                                              |                                                                                                                                                                                                                |     |

| New Yestion.                                                                                                 |                                                                                                                                                                                                                |     |

|                                                                                                              |                                                                                                                                                                                                                |     |

| Experies                                                                                                     | Alt+Erles                                                                                                                                                                                                      |     |

| Qelete                                                                                                       | Del                                                                                                                                                                                                            |     |

| <b>Note:</b> The family<br>specified in Alliance<br>Series must match<br>the family specified<br>in Leonardo | Bar       XC4005XL-3-PC84         Sear ver1->rev1 guide data to proje         Overwrite Jast revision: ver1->rev1         New version name:         New revision name:         Run       Cancel         Option |     |

| implementation flow                                                                                          |                                                                                                                                                                                                                | Uat |

3) Click "OK, but do not hit "Run" on the Implement dialog box

**Note:** The first step in implementing a design is the selection of a target device. If a valid PART has been specified in Leonardo, it will be pre-selected in the Part selection dialog box. For designs that do not have the PART specified in the netlist (or the Design Manager is unable to detect its presence), the user must identify the target part using this dialog box. Users may define the part in Leonardo by setting the "part" variable, i.e., "set part xc4005xl-3-PC84". Setting the part variable is a step of convenience and will not effect optimization results

Setup Alliance Series to generate VITAL VHDL Simulation Model

- 1) From the Implement dialog box select the "*Options*" button. This will bring up the "Options" dialog box.

- 2) In the "Optional Targets" field, check the box labeled, "Produce Timing Simulation Data"

- In the "Program Option Templates" field, select the "*Edit Template*" button for "Implementation". This will bring up the "XC4000 Implementation Options: Default" dialog box.

- Once up Select the "Interface" tab and Set the simulation data output to "VHDL"

| Eat              | X Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| E Comvert        | vervit guide data to project clipboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| 1000000000       | there is a second |   |

| Newgenetine      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| New jevition na  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| teres Texandrian |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| Run              | ConceHeb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| - 9 G            | Oprion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|                  | Control Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|                  | Annowski law T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|                  | Uter Carolinette                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|                  | Program Option Templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|                  | Implementation Contract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|                  | Europeantos Telinut NE4000 Implemento Configurational default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|                  | Operate & Mag Place & Place & Taring Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|                  | Optional Tagets Tservice Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|                  | F Poduce Tiring Seculation Date Marro Search Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|                  | P Podace Conjugation Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|                  | Buten File: Drogon .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                  | Part-In Infiliation Anno Statements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|                  | Eamat AHEL T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                  | Aliveran Canada Power On Receit Post                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|                  | 1 genge under rund untreter run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

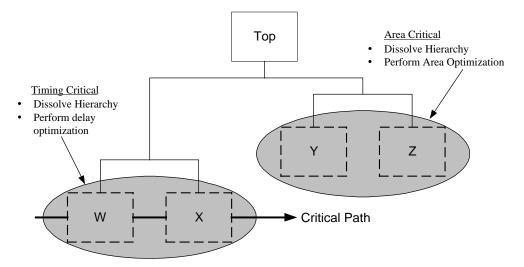

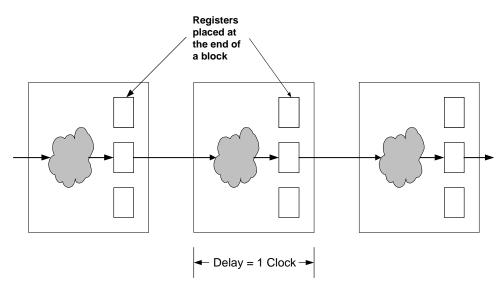

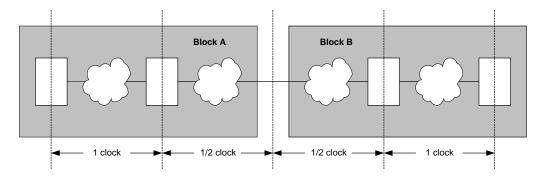

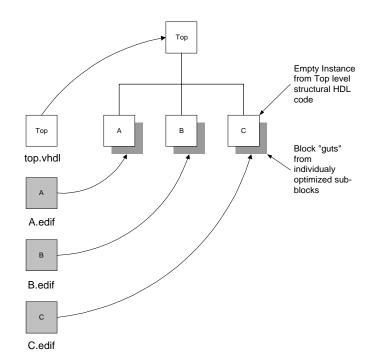

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |