## **DESIGN HINTS AND ISSUES**

## Looking for the Best HDL Design Flow?

Xilinx has the easiest, most efficient HDL design flow, as proven by customers in independent trials. To make the point, here is one story about the HDL Design Seminar that was held at Designcon, in San Jose (January 1998).

The objective of the design seminar was to demonstrate HDL design flows to designers that are new to HDL design methodologies and tools by having multiple design teams (a total of 16) design a thermostat controller. The following design flows and tool combinations were used:

| Simulation | Synthesis     | FPGA<br>Technology |

|------------|---------------|--------------------|

| Veribest   | FPGA Express  | Xilinx             |

| MTI        | Exemplar      | Xilinx             |

| MTI        | Synplicity    | Xilinx             |

| MTI        | Exemplar      | Altera             |

| Viewlogic  | Viewsynthesis | Altera             |

| MTI        | Synplicity    | Altera             |

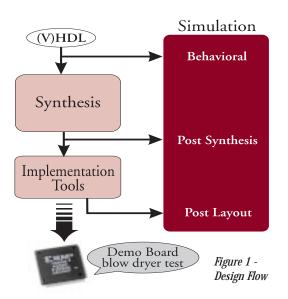

Each team was given the design specification and algorithm so they could describe the behavior of the design in either Verilog or VHDL, simulate, synthesize, place and route, and finally download the design bitstream into an FPGA. The target device and speed grade was based on the designers' best judgement. The FPGA would then be inserted into a demo

**•• Each team** was given the design specification and algorithm so they could describe the behavior of the design...\*

- by Mary Brown,

- Product Marketing,

- Alliance Series,

- maryb@xilinx.com

- and

- Paul Ingersoll, Regional

- Marketing Manager,

- paul.ingersoll@xilinx.com

board and a blow-dryer test would be used to judge the successful completion of the design. **Figure 1** illustrates the design flow.

The two Xilinx-based teams were able to complete the design in record time - approximately two hours. The first Altera team required an additional hour and used twice as much device resources. The second Altera team could not complete the design because Altera's MAX PLUS II software kept issuing a "Device Does Not Fit" error.

## Summary of the teams' results:

| Rank | Team | Device       | Utiliz-<br>ation          | Design<br>Cycle* |

|------|------|--------------|---------------------------|------------------|

| 1st  | 1    | Xilinx 4005E | 35%                       | 120<br>mins      |

| 2nd  | 2    | Xilinx 4005E | 35%                       | 120<br>mins      |

| 3rd  | 3    | Altera 8282  | 70%                       | 130<br>mins      |

| 4th  | 4    | Altera 8282  | Device<br>Does<br>Not Fit | Incom-<br>plete  |

\* Design Cycle – Includes writing the HDL, simulation, synthesis, and device programming.

## Conclusion

So, as you can see, Xilinx has the easiest-to-use, the simplest, the most tightly-integrated HDL design flow, with faster runtimes. Of course, tests of this type are very subjective. However, based on these tests and other benchmarks, we are confident you will see similar results. Judge for yourself. ◆