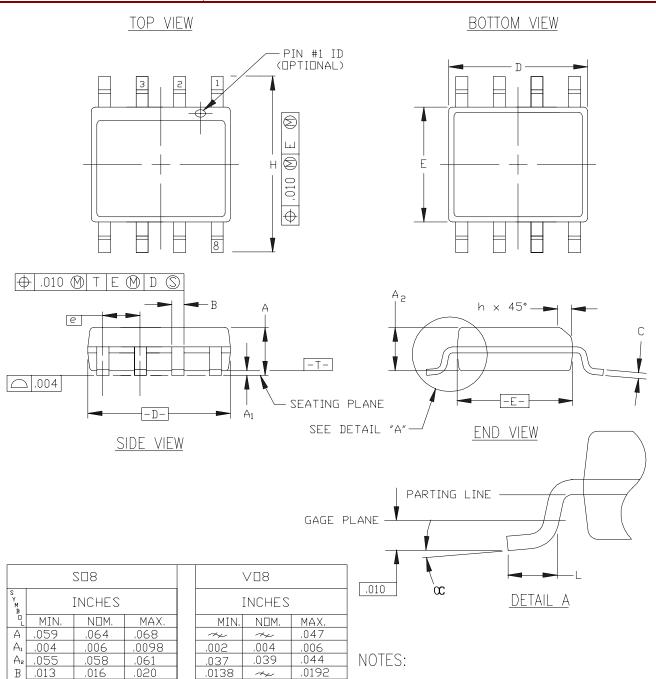

## SOIC (SO8) and TSOP (VO8) Packages

PK002 (v1.0) June 1, 2000

NOTES:

- 1. ALL DIMENSIONS AND TOLERANCES CONFORM TO ANSI Y14.5M-1982.

- 2. DIMENSION 'D' DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION SHALL NOT EXCEED .006" PER SIDE.

- 3. DIMENSION 'E' DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION SHALL NOT EXCEED .010 INCH PER SIDE.

- 4. LEAD FINISH: SOLDER PLATE

## 8 LEAD SOIC/TSOP (SO8, VO8)

.039

.194

.155

.050 BSC .236

.013

.025

$\prec_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!}$

4

.0075

.189

.150

230

.010

.016

0°

.0192

.0089

.196

.157

244

.019

.035

8°

© 2000 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Az .055

В

С

$\mathbb{D}$

Е .150

е

Н

h

œ

REF

.013

.0075

229

.010

016

0°

.189

.058

.016

.008

.194

.155

.236

.013

.025

5°

JEDEC MS-012

050 BSC

.061

.020

.196

.157

244

.019

.035

8°

<u>.009</u>8