# FPGA Editor Guide

**Introduction**

**Getting Started**

**Using the FPGA Editor**

*Working with Physical Macros*

**Customizing the FPGA Editor**

**FPGA Editor Files**

**Glossary**

FPGA Editor Guide

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI, 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, AACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235;

5.737.631: 5.742.178: 5.742.531: 5.744.974: 5.744.979: 5.744.995: 5.748.942: 5.748.979: 5.752.006: 5.752.035: 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This manual describes the Xilinx FPGA Editor, a graphical application used for displaying and configuring Field Programmable Gate Arrays (FPGAs).

Before using this manual, you should be familiar with the Xilinx design flow, including design entry and implementation. For more information on the Xilinx tools, refer to the *Development System Reference Guide, Design Manager/Flow Engine Guide,* and the *Alliance Series 3.1i Quick Start Guide.*

Note This Xilinx software release is certified as Year 2000 compliant.

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," provides an overview of the FPGA Editor.

- Chapter 2, "Getting Started," includes information on how to start and exit the FPGA Editor, and describes the user interface.

- Chapter 3, "Using the FPGA Editor," describes how to perform various operations on your design files.

- Chapter 4, "Working with Physical Macros," explains how to create and work with macros.

- Chapter 5, "Customizing the FPGA Editor," describes how to customize the FPGA Editor to suit your needs.

- Appendix A, "FPGA Editor Files," provides a listing of the files used by the FPGA Editor.

• "Glossary" describes the basic terminology used in the FPGA Editor manual.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/<br>index.htm                                                                                                          |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                 |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                           |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-<br>specific information on Xilinx device characteristics, including readback,<br>boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                      |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/<br>index.htm                                                                                                                 |

# Conventions

This manual uses the following conventions. An example illustrates each convention.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

${\tt File} \ \rightarrow \ {\tt Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2locn;

### **Online Document**

The following conventions are used for online documents.

• Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference. • Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# Contents

#### **About This Manual**

| Manual Contents      | . i  |

|----------------------|------|

| Additional Resources | . ii |

### Conventions

| Typographical   | iii |

|-----------------|-----|

| Online Document | iv  |

### Chapter 1 Introduction

| Dverview             | 1-1 |

|----------------------|-----|

| Design Flow          | 1-2 |

| FPGA Editor Files    | 1-3 |

| NCD File             | 1-3 |

| PCF File             |     |

| NMC File             |     |

| Architecture Support | 1-4 |

### Chapter 2 Getting Started

| Starting the FPGA Editor                     | 2-1 |

|----------------------------------------------|-----|

| From the Design Manager (Alliance Series)    | 2-1 |

| From the Project Manager (Foundation Series) | 2-2 |

| Stand-Alone Tool (PC Only)                   | 2-2 |

| From the Command Line                        | 2-2 |

| Syntax                                       | 2-2 |

| Variables                                    | 2-3 |

| Options                                      | 2-4 |

| Exiting the FPGA Editor                      | 2-5 |

| Configuring Xprinter                         | 2-6 |

| Using the Interface                          | 2-6 |

| Main Window                                  | 2-6 |

|                                              |     |

| Tit   | tle Bar                       | 2-8  |

|-------|-------------------------------|------|

| Me    | enu Bar                       | 2-8  |

| St    | andard Toolbar                | 2-9  |

| La    | yer Visibility Toolbar        | 2-9  |

| Ar    | ray Window                    | 2-10 |

| Lis   | st Window                     | 2-13 |

| Us    | ser Toolbar                   | 2-14 |

| W     | orld Window                   | 2-17 |

| W     | indow Tabs                    | 2-17 |

| Hi    | story Toolbar                 | 2-18 |

| Co    | ommand Line Toolbar           | 2-19 |

| St    | atus Bar                      | 2-20 |

| Bl    | ock Window                    | 2-20 |

| Using | Dialog Boxes                  | 2-21 |

| Us    | sing Common Fields            | 2-22 |

| Br    | owse Buttons                  | 2-22 |

| M     | oving Items within List Boxes | 2-22 |

| Us    | sing Filters with Commands    | 2-23 |

| Using | I Help                        | 2-24 |

| He    | elp Menu                      | 2-24 |

| To    | olbar Help Button             | 2-25 |

| F1    | Key                           | 2-25 |

| He    | elp Button in Dialog Boxes    | 2-25 |

| Using | the Mouse and Keyboard        | 2-26 |

|       | poming with the Mouse         |      |

| Zc    | oom Toggle                    | 2-27 |

| Pa    | anning                        | 2-27 |

|       |                               |      |

# Chapter 3 Using the FPGA Editor

| Creating a New Design File                    | 3-2  |

|-----------------------------------------------|------|

| Opening an Existing Design File               | 3-4  |

| Saving a Design File                          | 3-5  |

| With the Same Name                            | 3-5  |

| With a Different Name                         | 3-5  |

| Recovering a Terminated Session               | 3-7  |

| Selecting Objects                             | 3-8  |

| Notes On Selecting Objects                    | 3-9  |

| Selecting Objects with the Mouse and Keyboard | 3-11 |

| Selecting Objects with the List Window        | 3-11 |

| Customizing the List Window                   | 3-12 |

| Selecting Objects with the Find Command       | 3-13 |

| Selecting Objects with the Select Command     | 3-14 |

|                                               |      |

| Deselecting Objects                       | 3-14 |

|-------------------------------------------|------|

| Adding Objects                            |      |

| Adding Components                         |      |

| Notes on Adding Components                |      |

| Adding a Net                              |      |

| Notes on Adding Nets                      |      |

| Adding Component Pins to an Existing Net  |      |

| Adding a Macro                            |      |

| Deleting Objects                          |      |

| Deleting Components                       |      |

| Deleting Nets                             |      |

| Deleting Net Pins                         |      |

| Deleting Macros                           | 3-20 |

| Deleting Paths                            |      |

| Deleting Path Elements                    | 3-21 |

| Highlighting Objects                      |      |

| Viewing and Changing Properties           | 3-23 |

| Getattr and Setattr Commands              | 3-24 |

| Main Properties                           | 3-24 |

| Component Properties                      |      |

| General Page                              | 3-26 |

| Configuration Page                        | 3-26 |

| Physical Constraints Page                 | 3-27 |

| Pin Properties                            | 3-28 |

| Net Properties                            |      |

| General Page                              | 3-30 |

| Physical Constraints Page                 | 3-31 |

| Pins Page                                 | 3-33 |

| Site Properties                           | 3-33 |

| Wire Properties                           | 3-34 |

| Macro Properties                          | 3-35 |

| Path Properties                           | 3-35 |

| Layer Properties                          |      |

| Moving and Swapping Components and Macros |      |

| Moving Components with the Swap Command   |      |

| Moving Components using Drag and Drop     |      |

| Moving Macros                             |      |

| Swapping Components                       |      |

| Swapping Component Pins                   |      |

| Editing Component Logic                   |      |

| Notes on Editing a Component              |      |

| Placing and Unplacing Components          | 3-39 |

|           | Automatically Placing Selected Components        | 3-40 |

|-----------|--------------------------------------------------|------|

|           | Notes on Placing Selected Components             | 3-40 |

|           | Automatically Placing All Unplaced Components    | 3-41 |

|           | Manually Placing Selected Components             | 3-42 |

|           | Unplacing Components                             | 3-42 |

|           | Selected Components                              | 3-42 |

|           | All Components                                   | 3-42 |

|           | Routing and Unrouting                            | 3-43 |

|           | Automatic Routing                                | 3-43 |

|           | Notes on Automatically Routing Selected Objects  | 3-44 |

|           | Notes on Automatically Routing the Entire Design | 3-46 |

|           | Manual Routing                                   | 3-46 |

|           | Notes on Manual Routing                          | 3-47 |

|           | Switch Boxes in Manual Routing                   | 3-48 |

|           | Routing Through a Logic Block                    | 3-50 |

|           | Automatic Routing Option                         | 3-51 |

|           | Unrouting                                        | 3-52 |

|           | Unrouting Selected Objects                       | 3-52 |

|           | Unrouting Entire Design                          | 3-52 |

|           | Unrouting Notes                                  | 3-53 |

|           | Constraints                                      | 3-53 |

|           | Locked Nets and Components                       | 3-54 |

|           | Using the ILA Command                            | 3-55 |

|           | Using Probes                                     | 3-57 |

|           | Adding a Probe                                   | 3-57 |

|           | Saving Probe Definition                          |      |

|           | Opening a Probe Script File                      | 3-60 |

|           | Verifying Your Design                            |      |

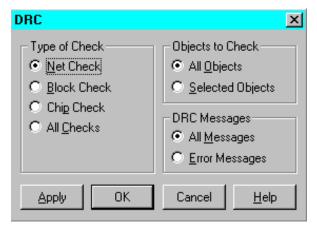

|           | Physical Design Rule Check (DRC)                 | 3-61 |

|           | Running a DRC                                    | 3-62 |

|           | Delay Calculator                                 | 3-63 |

|           | Calculating Net Delay                            |      |

|           | Calculating Path Delay                           |      |

|           | TRACE                                            |      |

|           | Running TRACE from the Tools Menu                | 3-64 |

| Chapter 4 | Working with Physical Macros                     |      |

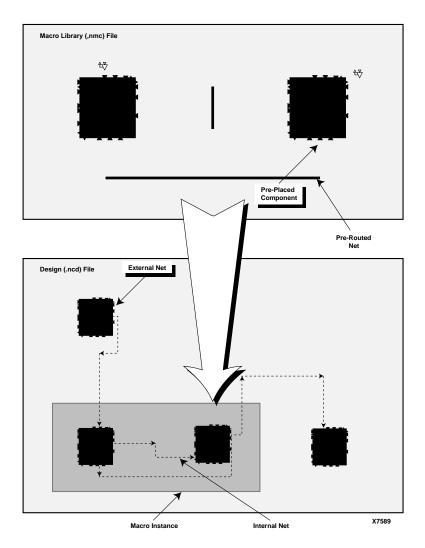

| Macro Terminology    | 4-3 |

|----------------------|-----|

| Macro Library File   | 4-4 |

| Macro Instance       | 4-5 |

| Pre-placed Component | 4-5 |

| Pre-routed Net       | 4-5 |

| Reference Component                                   |      |

|-------------------------------------------------------|------|

| External Pin                                          | 4-5  |

| Internal Net                                          | 4-5  |

| External Net                                          | 4-6  |

| Unbind                                                |      |

| Creating a New Macro File                             | 4-6  |

| Opening an Existing Macro                             | 4-7  |

| Saving your Design as a Macro File                    | 4-8  |

| Saving a Macro Library File                           | 4-8  |

| With the Same Name                                    | 4-9  |

| With a Different Name                                 | 4-9  |

| Saving a Macro Library File as a Design File          | 4-9  |

| Adding Macros to Your Design                          | 4-10 |

| Notes on Adding Macros                                | 4-11 |

| Operating on Macro Components and Nets in Your Design | 4-12 |

| Selecting Macros in Your Design                       | 4-13 |

| Deleting Macros from Your Design                      | 4-13 |

| Viewing and Changing Macro Properties in Your Design  | 4-14 |

| General Page                                          | 4-15 |

| Physical Constraints Page                             | 4-15 |

| Moving Macros in Your Design                          | 4-16 |

| Moving Macros with the Swap Command                   | 4-16 |

| Moving Macros using Drag and Drop                     |      |

| Unbinding Macros in Your Design                       | 4-17 |

| Placing and Unplacing Macros in Your Design           | 4-18 |

| AutoPlacing Macros                                    | 4-18 |

| Manually Placing Macros                               | 4-18 |

| Unplacing                                             | 4-19 |

| Routing and Unrouting Macros in Your Design           | 4-19 |

| External Macro Pins in Your Design                    | 4-20 |

| Editing Your Macro File                               | 4-20 |

| Adding External Pins                                  | 4-21 |

| Macro to External Net Recommendations                 | 4-22 |

| Viewing and Changing External Pin Properties          | 4-24 |

| Deleting External Pins                                | 4-26 |

| Listing External Pins                                 | 4-27 |

| Designating a Reference Component                     | 4-27 |

| Adding a Macro to a Macro File                        | 4-28 |

| Macro File Placement and Routing                      | 4-28 |

| DRC Checks in Your Macro File                         | 4-28 |

### Chapter 5 Customizing the FPGA Editor

| Initializing the FPGA Editor<br>Customizing the User Toolbar<br>Before Starting the FPGA Editor<br>During an Editing Session<br>Customizing Mouse Buttons<br>Customizing Colors<br>Changing Window Colors on the PC<br>Changing Object Colors on Workstation and PC<br>Editing the FGPA_editor.ini File<br>Using the Command Line Toolbar<br>Using the Devcolor Command | 5-2<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-4<br>5-5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                         | 5-5                                                                       |

| Customizing Fonts (PC only)                                                                                                                                                                                                                                                                                                                                             | 5-6                                                                       |

| Customizing with Command Aliases                                                                                                                                                                                                                                                                                                                                        | 5-6                                                                       |

| Customizing with Command Scripts<br>Recording a Script<br>Playing Back a Script                                                                                                                                                                                                                                                                                         | 5-9                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

### Appendix A FPGA Editor Files

| Window Manager Resources A-2 | 2 |

|------------------------------|---|

|------------------------------|---|

# **Chapter 1**

# Introduction

This chapter provides an overview of the FPGA Editor and includes the following sections.

- "Overview"

- "Design Flow"

- "FPGA Editor Files"

- "Architecture Support"

### Overview

The FPGA Editor is a graphical application for displaying and configuring Field Programmable Gate Arrays (FPGAs). The FPGA Editor reads from and writes to Native Circuit Description (NCD) files, macro files (NMC), and Physical Constraints Files (PCF).

The following is a list of a few of the functions you can perform on your designs in the FPGA Editor.

- Place and route critical components before running the automatic place and route tools.

- Finish placement and routing if the routing program does not completely route your design.

- Add probes to your design to examine the signal states of the targeted device. Probes are used to route the value of internal nets to an IOB (Input/Output Block) for analysis during the debugging of a device.

- Run the BitGen program and download the resulting bitstream file to the targeted device.

- View and change the nets connected to the capture units of an Integrated Logic Analyzer (ILA) core in your design.

- Create an entire design by hand (advanced users).

### **Design Flow**

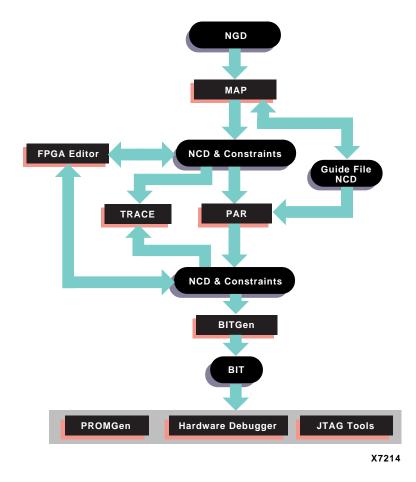

The following steps are an overview of the FPGA Editor design flow.

- 1. Save your design in EDIF (Electronic Data Interchange Format).

- 2. Run NGDBuild, which creates an NGD (Native Generic Database) file.

- 3. Run the MAP program, which creates an NCD (Native Circuit Description) file.

- 4. Load your design into the FPGA Editor, make necessary changes, and save the modified design as an NCD file.

- 5. Run the PAR (Place and Route) program on the modified NCD file.

The following figure shows the complete Xilinx design flow.

Figure 1-1 Design Flow

# **FPGA Editor Files**

The following files are used with the FPGA Editor. See the "FPGA Editor Files" appendix for more information on these files.

### **NCD File**

The NCD file is the output file from the MAP program and represents the physical design. This file describes a design in terms of CLBs (Configurable Logic Blocks) and IOBs (Input/Output Blocks). You can edit a design in the FPGA Editor, save it, and then route it with PAR (Place and Route).

### **PCF File**

The PCF file is an ASCII file containing physical constraints created by the MAP program, as well as physical constraints entered by you in your design and in the UCF (User Constraints File). You can edit the PCF file in the FPGA Editor.

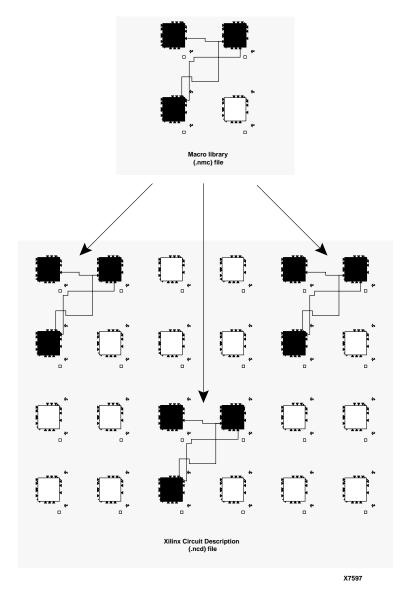

### **NMC File**

The NMC file is a physical macro library file. This file contains a physical macro definition that can be instantiated into an FPGA Editor design.

### **Architecture Support**

The software supports the following architecture families in this release.

- Spartan<sup>™</sup>/XL/-II

- Virtex<sup>TM</sup>/-E/-II

- XC4000<sup>TM</sup>E/L/EX/XL/XV/XLA

- XC3000<sup>TM</sup>A/L

- XC3100<sup>™</sup>A/L

- XC5200<sup>TM</sup>

# **Chapter 2**

# **Getting Started**

This chapter describes how to start and exit the FPGA Editor. It also explains the basic elements and operations of the FPGA Editor interface. This chapter includes the following sections.

- "Starting the FPGA Editor"

- "Exiting the FPGA Editor"

- "Configuring Xprinter"

- "Using the Interface"

### Starting the FPGA Editor

The FPGA Editor runs on PCs and workstations. You can start the FPGA Editor from the Windows Program Manager, the Xilinx Alliance Design Manager, the Xilinx Foundation Project Manager, or the command line.

This section contains the following topics.

- "From the Design Manager (Alliance Series)"

- "From the Project Manager (Foundation Series)"

- "Stand-Alone Tool (PC Only)"

- "From the Command Line"

### From the Design Manager (Alliance Series)

To start the FPGA Editor from the Design Manager window (PC or workstation), select **Tools**  $\rightarrow$  **FPGA Editor** or click on the FPGA Editor icon as shown in the following figure.

### From the Project Manager (Foundation Series)

To start the FPGA Editor from the Project Manager window, select  $\texttt{Tools} \rightarrow \texttt{Implementation} \rightarrow \texttt{FPGA Editor}$ .

### Stand-Alone Tool (PC Only)

**Note** To run the FPGA Editor as a stand-alone tool on a PC, you must have the XILINX environment variable defined and the path must include \$XILINX/bin/nt.

If you installed the FPGA Editor as a stand-alone tool on a PC, click on the FPGA Editor icon (shown in the previous figure) on the Windows desktop. Optionally, you can select the Run command from the Windows Start button menu, and specify fpga\_editor.exe in the Run dialog box. See the following section for information on the various options you can specify in the Run dialog box.

### From the Command Line

Enter the following command to start the FPGA Editor from the command line.

fpga\_editor

#### **Syntax**

This section provides examples for starting the FPGA Editor from the command line. The "Variables" and "Options" sections that follow provide definitions of the command line variables and options.

To run the FPGA Editor on an existing design, use the following command.

```

fpga_editor [-r | -e | -n] design_name.ncd

[pcf_file_name.pcf]

```

To run the FPGA Editor and create a new design, use the following command.

```

fpga_editor -e design_name.ncd [pcf_file_name.pcf]

[arch device package speed]

```

To run the FPGA Editor on an existing physical macro, use the following command.

fpga\_editor [-e|-r] -m macro\_file\_name

To run the FPGA Editor to create a new physical macro, use the following command.

```

fpga_editor -e -m macro_file_name [arch device package

speed]

```

#### Variables

This section describes the command line variables.

• Design\_name.ncd

The name of your new or existing design file. The .ncd extension is optional.

• Macro\_file\_name

The name of your new or existing macro file.

• Pcf\_file\_name.pcf

The name of the new or existing constraints file that you want applied to your design file. The .pcf extension is optional.

• Script\_file\_name.scr

Specifies the name of a command file that includes command line arguments. The .scr extension is optional.

• Arch

Specifies the architecture (product family) of your design (for example, Virtex).

**Note** To see what devices, packages, and speeds are available, select File  $\rightarrow$  New from within the FPGA Editor. Click Select Part to display the Part Selector dialog box. See Figure 3-2 of the "Using the FPGA Editor" chapter.

• Device

Specifies a device within the selected architecture (for example, 4036 or 4028).

• Package

Specifies a package within the selected architecture and device (for example, PC84 or PQ100).

**Note** You can only enter a device and package from a part library that is installed on your system. For example, if you have not installed the Xilinx 4036EX series part library, you cannot create a design using the 4036EX device and the package.

• Speed

Specifies the speed grade of the selected part. Allowable speeds are listed in the online Data Book at http://support.xilinx.com/partinfo/databook.htm.

#### Options

**Note** See the "Opening an Existing Design File" section of the "Using the FPGA Editor" chapter for more information on command options.

| Option | Definition                                                                                                                                                                                                                                                                                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -r     | Read Only Mode—prevents overwriting<br>your design. You can open and edit your<br>design, but you cannot save changes to your<br>original file. However, you can save your<br>changes to a file with a different name.                                                                                                                    |

| -e     | Read-Write Mode—allows changes to your design, including changes to the logical configurations.                                                                                                                                                                                                                                           |

| -n     | No Logic Changes Mode—allows placement<br>and routing changes, but not changes to the<br>logical configurations. For example, you<br>cannot add or delete nets and components or<br>reprogram programmable components. This<br>mode ensures that the design database is<br>consistent with the schematic or netlist used<br>to create it. |

**Table 2-1 Command Line Options**

Option

Definition

-p script\_file\_name

Use this option to execute the command line arguments in the specified file after your design or macro is opened or created.

Use this option to edit or create a macro.

Table 2-1

Command Line Options

# **Exiting the FPGA Editor**

This section describes how to exit the FPGA Editor.

- 1. To exit the FPGA Editor, perform one of the following.

- $\bullet \quad Select \, \texttt{File} \to \texttt{Exit}.$

- Select Exit from the User toolbar.

- Enter the following in the Command Line toolbar.

exit

-m macro\_file\_name

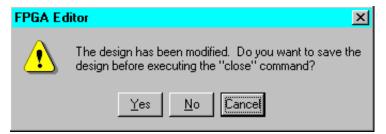

The following dialog box appears.

**Note** If you have not made any changes since you last saved the design, the FPGA Editor window closes without displaying this dialog box.

#### Figure 2-1 Exit Dialog Box

2. Click **Yes** to save changes and exit, **No** to discard changes and exit, or **Cancel** to return to your design without exiting.

# **Configuring Xprinter**

Note This section applies only to workstation applications.

For detailed instructions on configuring a printer so you can print from the FPGA Editor, see the *Alliance Series 3.1i Quick Start Guide*.

### Using the Interface

This section describes the FPGA Editor interface and how to use it.

**Note** Menus, dialog boxes, and parts of the application window are documented as they appear on a PC. Differences between the PC and the workstation applications are documented if there is a difference in operation between the two platforms.

This section contains the following topics.

- "Main Window"

- "Using Dialog Boxes"

- "Using Help"

- "Using the Mouse and Keyboard"

#### **Main Window**

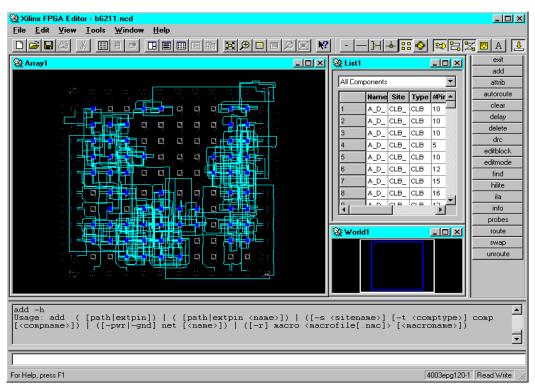

This section describes the FPGA Editor main window. To work in a section of the interface, click the left mouse button in that section. The default layout of the main window is shown in the following figure. You can execute commands from the menus, toolbars, and command line. The client or work space area includes the Array window, List window, and World window.

**Note** If you do not have a design open in the Array window, an abbreviated menu bar is displayed.

#### Figure 2-2 FPGA Editor Main Window

The main window includes the following areas.

Note Each window area is described in more detail in this section.

- Title Bar

- Menu Bar

- Standard Toolbar

- Layer Visibility Toolbar

- Array Window

- List Window

- User Toolbar

- World Window

- Window Tabs

**Note** The Window Tabs are displayed at the bottom of the client area when you select  $View \rightarrow Window Tabs$ .

- History Toolbar

- Command Line Toolbar

- Status Bar

- Block Window

**Note** The Block Window and its command toolbar are displayed when you double click the left mouse button on a logic block.

Block Window Toolbar

#### Title Bar

The title bar at the top of the main window displays the program name (Xilinx FPGA Editor) and the name of the currently loaded design.

#### Menu Bar

The menu bar is located above the Array window. Most of the FPGA Editor commands are available in the pull-down menus of the FPGA Editor window after a design is loaded.

You can select menu commands with the mouse or the keyboard. With the mouse, click the left mouse button on the command. With the keyboard, press the Alt key and type in the letter underlined in the menu for that command. When you select a menu command with either method, a brief description of the command appears in the Status Bar at the bottom of the FPGA Editor window.

Some menu commands include an ellipsis (...). When you select one of these commands, a dialog box appears. You can enter additional information for that command in the dialog box. Refer to the FPGA Editor online help for detailed information on the commands in each menu. To access the online help within the FPGA Editor, select Help  $\rightarrow$  Help Topics.

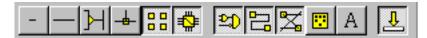

#### **Standard Toolbar**

The Standard toolbar contains commands for performing common operations on your designs, such as opening a design file, deleting objects from a design, and displaying a more detailed view of a design. Click once on a button in the toolbar to access a command. When you position the mouse pointer over a toolbar button, a short description (a tool tip) appears next to the button and a longer description appears in the status bar at the bottom of the main window. See the FPGA Editor online help for more information on the Standard toolbar.

#### Layer Visibility Toolbar

The Layer Visibility toolbar allows you to specify which objects are displayed in the Array window. When you position the mouse pointer over a toolbar button, a short description (a tool tip) appears next to the button and a longer description appears in the status bar at the bottom of the main window. See the FPGA Editor online help for more information on the Layer Visibility toolbar.

Use the left mouse button to select or deselect the layers you want displayed or hidden. You can control the display of the following objects.

Note See the "Glossary" for definitions of these objects.

- Local lines

- Long lines

- Pin wires

- Pips

- Sites

- Switch boxes

- Components

- Routes

- Ratsnests

- Macros

- Text (reference designators)

- For Virtex and Virtex2 designs, double and hex lines can be displayed

#### **Array Window**

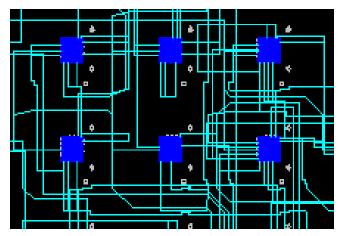

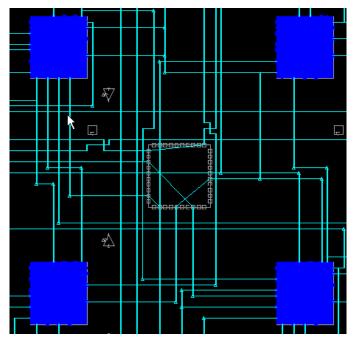

The Array window displays a graphical representation of the FPGA device. The following figure shows a section of the Array window.

Figure 2-3 Section of Array Window

When you position the mouse pointer over an object in the Array window, a description or data tip appears in a small floating window. This functionality is similar to using the pick –q command (see the FPGA Editor online help for more information on the Pick command). The following is an example of a data tip for a site.

site "CLB\_R9C12.S1", type = SLICE.

To turn off the data tips, enter the following in the Command Line toolbar.

```

setattr main array-datatips off

```

**Note** See the FPGA Editor online help for a complete description of the Setattr command.

The device components and the interconnections (both logical and routed) between these components are displayed in this window. When you edit the internal logic of a programmable component such as a logic block, a schematic of the interior of the component is displayed in the Block window (see the "Block Window" section for more information). You can control the display of objects in the Array window with the Layer Visibility toolbar. You can turn off the display of individual object layers, such as switches, wires, and routed connections, to make your design easier to view. Selectively viewing objects also reduces the duration of each screen redraw.

**Note** Symbols used in the FPGA Editor Array window for specific devices are described in *The Programmable Logic Data Book*.

A site is a programmable logic element (used or unused) located within the device. Sites are potential locations for components and are displayed in the Array window as outlines of components. Components are CLBs, IOBs, tristate buffers, pull-up resistors, oscillators, or clocks. When you place a component in a site, the outline is filled in as shown in the following figure.

X8971

Figure 2-4 Sites and Components

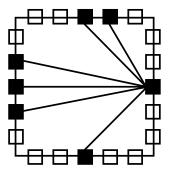

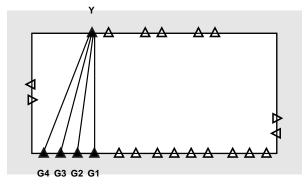

Components are connected by nets. A net is a set of component pins that are electrically connected in the finished design. When a component is placed, but not yet routed, the connection between its net pins (those pins on the net) and net pins from other components is logical, not physical. The pins are associated with each other, even though there is no electrical connection between them. In the Array window, the logical connections that make up a net are displayed as ratsnest lines or direct point-to-point connections between net pins, as shown in the following figure.

Figure 2-5 Ratsnest Display (Unrouted Net)

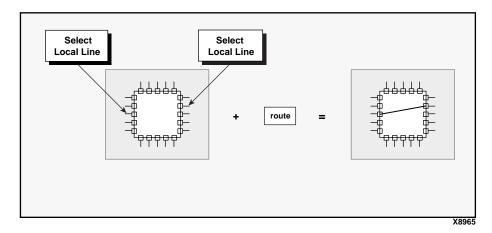

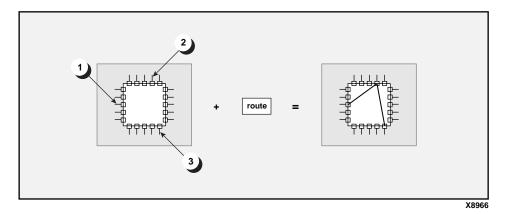

When the net is routed, electrical connections are made between the net pins. In the Array window, the routed connections appear as lines following the routing resources available on the device (long lines, pinwires, switch boxes, and so on). The following figure shows a routed net.

Figure 2-6 Display of Routed Net

#### **List Window**

The List window displays a list of the components, nets, layers, paths, macros, constraints, and bels in your design. Use the pull-down list box at the top of the window to specify the items you want displayed in the List window. You can use the Maximize List Window toolbar button to maximize this window. To print the List window, first select the window with the mouse and then use the Print command in the File menu. To save the List window data to a Comma Separated Value (.csv) file, use the Export command in the File menu (see the FPGA Editor online help for more information on the Export command).

| Place | d Compor | nents |      |       |         |

|-------|----------|-------|------|-------|---------|

|       | Name     | Site  | Туре | #Pins | Hilit _ |

| 1     | A_D_     | CLB_  | CLB  | 10    |         |

| 2     | A_D_     | CLB_  | CLB  | 10    |         |

| 3     | A_D_     | CLB_  | CLB  | 10    |         |

| 4     | A_D_     | CLB_  | CLB  | 5     |         |

| 5     | A_D_     | CLB_  | CLB  | 9     |         |

| 6     | A_D_     | CLB_  | CLB  | 12    |         |

| 7     | A_D_     | CLB_  | CLB  | 14    |         |

| 8     | A_D_     | CLB_  | CLB  | 15    |         |

| 9     | A_D_     | CLB_  | CLB  | 11    |         |

| 10    | A6       | CLB_  | CLB  | 7     |         |

| 11    | A7       | CLB_  | CLB  | 7     |         |

#### Figure 2-7 List Window

**Note** See the "Selecting Objects with the List Window" section of the "Using the FPGA Editor" chapter for more information on the List window.

#### **User Toolbar**

The User toolbar, shown in the following figure, provides a convenient way to perform frequently used commands. To use a command, select the appropriate command button with the left mouse button.

| exit      |

|-----------|

| add       |

| attrib    |

| autoroute |

| clear     |

| delay     |

| delete    |

| drc       |

| editblock |

| editmode  |

| find      |

| hilite    |

| ila       |

| info      |

| probes    |

| route     |

| swap      |

|           |

Figure 2-8 User Toolbar

You can customize the User toolbar with the Button and Unbutton commands described in the FPGA Editor online help. Alternatively, you can edit the fpga\_editor.ini or the fpga\_editor\_user.ini file (see "Customizing the FPGA Editor" chapter for more information on these files). These files define the default User toolbar buttons that appear when the FPGA Editor window opens. You can define up to fifty buttons; however, the height of the toolbar may limit the number of buttons that are visible.

#### Table 2-2 User Toolbar Command Summary

| Command | Description                                                                                      |

|---------|--------------------------------------------------------------------------------------------------|

| exit    | Exits FPGA Editor. If you edited your design, a dialog box appears to allow you to save changes. |

| add     | Adds selected sites as components to your design.                                                |

| Command   | Description                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| attrib    | Posts a dialog box containing property information<br>for all selected items or for the main window if no<br>item is selected.                                                            |

| autoroute | Automatically routes a selected component, macro,<br>net, ratsnest, or net pin between selected routing<br>resources.                                                                     |

| clear     | Deselects all selected objects.                                                                                                                                                           |

| delay     | Calculates and lists the path delay for a selected net or<br>selected pins on a net. This information appears in the<br>History toolbar and in the List window when nets are<br>selected. |

| delete    | Deletes selected objects from the design.                                                                                                                                                 |

| drc       | Performs a DRC (Design Rule Check), which checks<br>for logical and physical errors in the design. The<br>results appear in the History toolbar and also in the<br>log file.              |

| editblock | Opens the Block window, which allows you to view<br>or edit the internal logic of a selected logic block.                                                                                 |

| editmode  | Toggles between Read Only, No Logic Changes, or<br>Read Write edit modes.                                                                                                                 |

| find      | Posts a dialog box that allows you to find a specified component, macro, site, pin, or net.                                                                                               |

| hilite    | Highlights a selected object.                                                                                                                                                             |

| ila       | Posts a dialog box that allows you to view and change<br>the nets connected to the capture units of the ILA core<br>in your design.                                                       |

| info      | Lists the properties for a selected object in the History toolbar.                                                                                                                        |

| probes    | Posts a dialog box that allows you to add probes to your design.                                                                                                                          |

| route     | Routes selected objects (manual route).                                                                                                                                                   |

Table 2-2

User Toolbar Command Summary

Table 2-2 User Toolbar Command Summary

| Command | Description                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| swap    | Moves a component to another site or swaps locations<br>between two components or two logic block pins. |

| unroute | Unroutes selected objects.                                                                              |

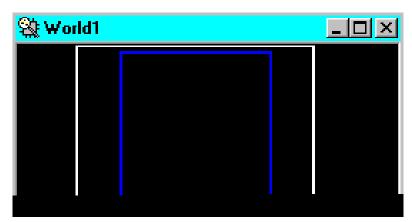

### **World Window**

The World window, as shown in the following figure, shows the area of the device that is currently displayed in the Array window.

Figure 2-9 World Window

As you pan and zoom the Array window, notice the corresponding changes in the size and position of the white rectangle within the World window. Also, any objects selected in the Array window appear in the World window. You can drag the white rectangle with the mouse button to pan the display to the desired position. If you have multiple Array windows, the World window displays a rectangle for each Array window.

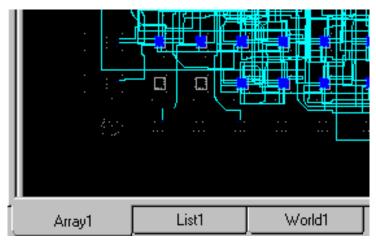

### Window Tabs

The Window Tabs, as shown in the following figure, are displayed at the bottom of the client area when you select  $View \rightarrow Window$  Tabs. These tabs display the windows that are open even if they are minimized.

Figure 2-10 Window Tabs

#### **History Toolbar**

The History toolbar, shown in the following figure, is located below the Array window and displays commands and responses. All error messages, warnings, and command responses are written to the History toolbar. Information in the History toolbar is especially useful for deciphering unexpected command results.

```

net "GT_7F".

net "XSIG271".

net "XSIG260", node = /X:2096/Y:592.

```

Use the scroll bar located to the right of the History toolbar to view all the commands and responses recorded during an editing session. You can resize this area by selecting the top of the toolbar, and using the left mouse button to move the double-headed arrow that appears up or down.

The History toolbar accommodates 32,000 characters of output on Windows 98<sup>®</sup> platforms, and a much larger number of characters on Windows NT<sup>®</sup> and UNIX<sup>®</sup> platforms. To examine text beyond this limit, use any text editor to view the contents of the FPGA Editor log file while you are editing your design. The log file is named *design\_name\_fpga\_editor.out* and is described in the "Recovering a Terminated Session" section of the "Using the FPGA Editor" chapter. You must remain in the FPGA Editor while you view this file because the file is renamed when you exit the program. The .out file is

renamed *design\_name\_fpga\_editor\_YYMMDD\_HHMMSS.log*, where Y is year, M is month, D is day, H is hour, M is minute, and S is second.

#### **Command Line Toolbar**

Use the Command Line toolbar (located directly below the History toolbar) to enter commands from the keyboard.

The following is a list of tips for using the Command Line toolbar.

- To enter multiple commands on the same line, use semicolons to separate each command.

- Use a backslash at the end of the line to continue a command on the next line.

- Commands are case-sensitive.

- For command arguments that contain special characters ("'\*? \; #), embedded spaces, or leading dashes, you must place the argument in quotation marks (for example, button "zoom in twice" "zoom in; zoom in"). Alternatively, you can precede the reserved character with a back slash (for example, select net \;\\* selects a net with the name ;\*).

On PC's, since the back slash serves as the FPGA Editor escape character, it affects  $DOS^{TM}$ -style path names. For example, the following command will not produce the desired effect.

load design \data\mydesign.ncd

The system responds with the following.

ERROR - load: file "datamydesign.ncd" not found

Use one of these solutions to solve this problem.

• Use forward slashes (UNIX style) in the path name as in the following example.

load design /data/mydesign.ncd

• Escape the escape characters as in the following example.

load design \\data\\mydesign.ncd

• If you have trouble entering text, make sure the keyboard focus is in the Command Line toolbar. Press the F2 key to move the keyboard focus to the Command Line toolbar.

- Use the up and down arrow keys to display the values of previous and next commands.

- Use the following keystrokes to move the cursor in the Command Line toolbar.

| Keystroke                                  | Description                                                                                     |

|--------------------------------------------|-------------------------------------------------------------------------------------------------|

| Left arrow ( $\leftarrow$ ) or Control–b   | Move back one character                                                                         |

| Right arrow ( $\rightarrow$ ) or Control–f | Move forward one character                                                                      |

| Home or Control–a                          | Move to the beginning of the line                                                               |

| End or Control-e                           | Move to the end of the line                                                                     |

| Backspace                                  | Delete the character to the left of the cursor                                                  |

| Control-x                                  | Cut the selected characters to the clipboard                                                    |

| Control-v                                  | Paste the clipboard contents to<br>the right of the cursor or to<br>replace selected characters |

| Control-c                                  | Copy selected characters to the clipboard                                                       |

Table 2-3 Command Line Toolbar Keystrokes

#### **Status Bar**

The status bar appears at the bottom of the main window (below the Command Line toolbar). When you select a menu command, a brief description of its function appears in the status bar.

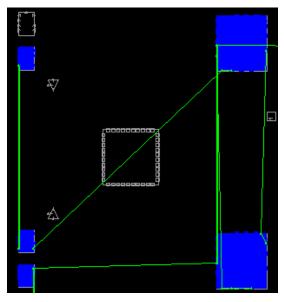

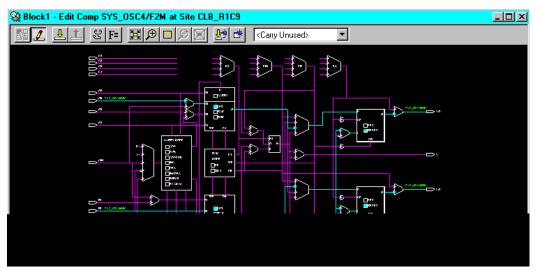

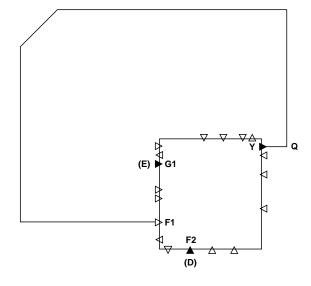

#### **Block Window**

The Block window is used to edit logic blocks. This window is displayed when you double click the left mouse button on a logic block. You can use only one Block window at a time for editing; however, you can have additional Block windows open for viewing. See the "Editing Component Logic" section of the "Using the FPGA Editor" chapter for more information. The Block window is shown in the following figure.

#### Figure 2-11 Block Window

When you position the mouse pointer over an object in the Block window, a description or data tip appears in a small floating window. To turn off the data tips, enter the following in the Command Line toolbar:

```

setattr main block-datatips off

```

**Note** See the FPGA Editor online help for a complete description of the Setattr command.

### **Using Dialog Boxes**

Many menu commands display dialog boxes in which you can enter information and set options.

#### **Using Common Fields**

The fields shown in the following table are common to most dialog boxes.

Dialog Box FieldFunctionOKCloses the dialog box and implements the<br/>intended action according to the settings in the<br/>dialog boxApplyImplements the intended action without closing<br/>the dialog boxCancelCloses the dialog box without effecting any<br/>actionHelpDisplays information on the dialog box

Table 2-4 Common Dialog Box Fields

#### **Browse Buttons**

Many dialog boxes contain browse buttons to allow you to navigate through your directory structure to find a particular file or to save a file to a specific location.

#### **Moving Items within List Boxes**

Many of the dialog boxes feature list boxes. You can select and move items from one list box to another using either the mouse or the keyboard, or a combination of these methods.

Use the mouse to select items in list boxes as follows.

- To move an item to a list box on the right, select it with the left mouse button. Click the > button. To move an item to a list box on the left, select it, then click the < button.

- To move all items to a list box on the right, click the >> button. To move all items to a list box on the left, click the << button.

- To move sequential items, select the first one with the left mouse button. Hold down the **Shift** key. Select the last item and release the **Shift** key. Click the > or < button to move the selected items to the right or left list box, respectively.

You can also select the first item; drag the mouse up or down until all the desired items are highlighted; and then click the > or < button.

• To move multiple items in any order, hold down the Ctrl key while clicking individual items. When you finish selecting, release the Ctrl key and click the > or < button.

Use the keyboard to select items in list boxes as follows.

- To move an item in a list box, press the **Tab** key until the first item in the list box is highlighted. Press the down arrow key to select the desired item. Tab to the > or < button to move it to the right or left list box, respectively. Press Enter.

- To move all items to a list box on the right, tab to the >> button and press Enter. To move all items to a list box on the left, tab to the << button and press Enter.

- To move consecutive items, tab to the first item in the list box. Use the down arrow key to highlight the first desired item. Press and hold the Shift key while using the down arrow key to select the other items in the sequence. Tab to the > button. Press Enter.

- On workstations only: To move multiple items in any order, tab to the list box and press **Shift F8**. Use the up and down arrow keys to navigate within the list box. Press the space bar to select each item. Tab to the > button. Press the **Enter** key.

### **Using Filters with Commands**

Many menu commands have dialog boxes that allow you to filter a list of choices, that is, display a subset of the listed items. These dialog boxes contain a filter field, Apply buttons, and Clear or Reset buttons.

In filter fields, you can enter a text string consisting of characters and wildcards. You cannot enter a range of items in filter fields.

- Characters can be any alphanumeric characters, text spaces, and the characters that appear on the top of the number keys on a keyboard. Alphabetic characters are case-sensitive. Control characters are not permitted.

- A wildcard can be an asterisk (\*), which can represent any number of characters, or a question mark (?), which represents a single character.

The software does not strictly match patterns; it matches entire text strings. It does not find a string if it is embedded in a larger string unless you use wildcards. For example, it does not find \$1N36 if it is embedded in ABC\$1N36XYZ. However, if you searched for \*\$1N36\*, it would find that string in ABC\$1N36XYZ.

To use the Filter dialog boxes, follow these steps.

- 1. Specify the pattern to include in your list by typing the characters.

- 2. Include one or more wildcards (\*) to do a global search on the specified string.

Precede the character string with a wildcard to retrieve all signal names that end with the string of specified characters.

Append the wildcard to the character string to retrieve all signal names that start with the specified character string.

3. Click Apply.

The list displays only the choices that match the selection criteria.

4. To clear the filter, click Clear or Reset or backspace over the information specified in the filter text box.

### **Using Help**

You can obtain help on commands and procedures with the Help menu or by selecting the Help toolbar button. In addition, the dialog boxes associated with many commands have a Help button that you can click to obtain context-sensitive help.

**Note** The online help provides detailed information on menu commands, dialog boxes, and command line commands.

#### **Help Menu**

Use the following Help menu commands to obtain help.

• The Help Topics command opens Help and lists the online help topics available. From the Contents page, you can jump to command information or step-by-step instructions. After you open help, you can click the Help Topics button in the Help window whenever you want to return to the help topic list.

- The Online Documentation command opens the software manuals in the default Web browser.

- The About FPGA Editor command opens a popup window that displays the version number of the tool and a copyright notice.

#### **Toolbar Help Button**

You can obtain context-sensitive help from the toolbar as follows.

1. Click the Help button in the toolbar.

The cursor changes to a question mark.

2. With the left mouse button, click the menu item or toolbar button for which you want help.

Help appears for the selected command or option.

Note You can also press Shift F1 to obtain context-sensitive help.

### F1 Key

Pressing the F1 key on a dialog box displays help on that dialog box. Pressing the F1 key is the same as selecting Help Topics from the Help menu, if no dialog boxes are displayed.

### Help Button in Dialog Boxes

Many of the dialog boxes have a Help button that you can click to obtain help for the dialog box with which you are working. You can also press **Alt H** on your keyboard while positioned over the dialog box to obtain help.

### Using the Mouse and Keyboard

Use the mouse and keyboard to perform the following operations in the FPGA Editor.

| Mouse Action                  | Function                                                                                     |

|-------------------------------|----------------------------------------------------------------------------------------------|

| Left Click                    | To select toolbar buttons, menus, menu commands, dialog box options, design objects          |

| Right Click                   | Display a popup menu at the top of the columns in the List window                            |

| Control + Right Click         | To zoom in                                                                                   |

| Shift + Control + Right Click | To zoom out                                                                                  |

| Control + Right Drag          | To pan                                                                                       |

| Right Drag                    | To move a placed component to an unused site                                                 |

| Left Drag                     | To move an unplaced component from the List window to an unused site                         |

| Middle Drag                   | To draw a rectangle around an area to zoom in on (avail-<br>able in Array and Block windows) |

Table 2-5

Using the Mouse and Keyboard

You can edit the fpga\_editor.ini file to change the mouse button settings and customize them to perform operations other than those shown. For example, if you do not have a middle button on your mouse, you can change the settings in this file. The procedure for customizing mouse buttons is described in the "Customizing the FPGA Editor" chapter.

### Zooming with the Mouse

To zoom in or out, click the appropriate button on your mouse; see Table 2-5. The Array window zooms by a preset factor; the number of available zoom levels is five by default.

**Note** See the fpga\_editor.ini file for information on using the Setattr command to change the zoom settings for viewing dense designs. This file is described in the "Customizing the FPGA Editor" chapter.

### Zoom Toggle

The zoom toggle feature allows you to toggle from an inner zoom level to the outermost zoom level and back. This feature is useful when you want to remain at a zoom level that provides good visibility for editing. For example, to move to a location outside your current editing area, but maintain the selected zoom level, use the zoom toggle to go to the outer zoom level, move the cursor to the desired location, and zoom back in.

To perform a zoom toggle, place the cursor in the Array window and type the letter "z" or "Z." If you begin at a zoomed-in level, you zoom out to the maximum zoom level. When you toggle again, you return to the previous zoom level.

**Note** The default letter "z" is defined in the fpga\_initialization.ini file. You can edit this file and customize it for your use.

#### Panning

Panning keystrokes are defined in the FPGA Editor initialization (fpga\_editor.ini) file and are summarized in Table 2-6. You can also use the World window to pan to a selected area. This panning method is described in the "World Window" section.

To pan, you must zoom in at least one level and position the mouse cursor in the Array window. You can perform the following pan operations.

- For smooth panning, hold down the right mouse button and drag the mouse. The window pans in the direction of the mouse movement. Panning continues until you reach the edge of the window or until you release the mouse button.

- When you reach the edge of the window with the cursor, the FPGA Editor will autopan the window until the edge of the FPGA device is reached. If you are near the edge of the window, the autopanning is slower than when you are far from the edge of the window.

- Use the keyboard arrow keys to pan left, right, up, or down.

- Use the Shift key with one of the arrow keys to pan the window to its furthest boundary in the direction of the arrow key.

• Press the space bar to center the display around the cursor position.

| Keystrokes                    | Result                                         |

|-------------------------------|------------------------------------------------|

| Up arrow (↑)                  | Pan up 75% of one window height.               |

| Shift + ↑                     | Pan to upper edge of device.                   |

| Down arrow ( $\downarrow$ )   | Pan down 75% of one window height.             |

| Shift + $\downarrow$          | Pan to lower edge of device.                   |

| Left arrow ( $\leftarrow$ )   | Pan left 75% of one window height.             |

| Shift + $\leftarrow$          | Pan to left edge of device.                    |

| Right arrow ( $\rightarrow$ ) | Pan right 75% of one window height.            |

| Shift + $\rightarrow$         | Pan to right edge of device.                   |

| Space bar                     | Center display around current cursor position. |

#### Table 2-6 Panning Keystrokes

# **Chapter 3**

# Using the FPGA Editor

This chapter includes information on performing various operations on your designs within the FPGA Editor. It includes the following sections.

**Note** You can select commands from the pull-down menus or the User toolbar, or you can enter commands in the Command Line toolbar. For more detailed information on Menu and Command Line commands, see the FGPA Editor online help.

- "Creating a New Design File"

- "Opening an Existing Design File"

- "Saving a Design File"

- "Recovering a Terminated Session"

- "Selecting Objects"

- "Adding Objects"

- "Deleting Objects"

- "Highlighting Objects"

- "Viewing and Changing Properties"

- "Moving and Swapping Components and Macros"

- "Editing Component Logic"

- "Placing and Unplacing Components"

- "Routing and Unrouting"

- "Constraints"

- "Using the ILA Command"

- "Using Probes"

- "Verifying Your Design"

# **Creating a New Design File**

**Note** You must close your current design or macro before using the New command to create a new design.

To create a new design in the FPGA Editor, follow these steps.

1. Select  $File \rightarrow New$  or click on the New toolbar button.

The New dialog box appears as shown in the following figure.

| New                                  |         | X           |

|--------------------------------------|---------|-------------|

| Design <u>o</u> r Macro?<br>© Design | O Macro |             |

| <u>D</u> esign File                  |         |             |

|                                      |         | Browse      |

| Physical Constraints File            |         |             |

|                                      |         | Browse      |

| Part                                 |         |             |

| XCV50-4-BG256                        |         | Select Part |

|                                      |         |             |

|                                      |         |             |

|                                      |         |             |

#### Figure 3-1 New Dialog Box

2. Select the Design option.

3. Enter the design name in the Design File field. If you do not enter the .ncd extension, it is automatically added when the file is created.

You can open a new design under a directory other than the current working directory. Type in the path name of the target directory in the Design File field, or click **Browse** to select your target directory and specify your design file name.

- 4. In the New dialog box, enter the constraints file name in the Physical Constraints File field, or click **Browse** to specify the directory and file name. If you do not enter the .pcf extension, it is automatically added to your file name. If you do not enter a file name, a constraints file is created with the same name as the .ncd file but with a.pcf extension.

- 5. Click **Select Part** to display the Part Selector dialog box.

| Part Selector        |         | ×            |

|----------------------|---------|--------------|

| <u>F</u> amily:      | VIRTEX  | ОК           |

| <u>D</u> evice:      | XCV50   | Cancel       |

| <u>P</u> ackage:     | BG256 💌 | <u>H</u> elp |

| <u>S</u> peed Grade: | -4 💌    | ]            |

|                      |         |              |

Figure 3-2 Part Selector Dialog Box

6. Select a Family, Device, Package, and Speed Grade for your design.

**Note** You can only select a part number from a part library you have installed on your system.

- 7. Click **OK**. The Part field in the New dialog box is filled in with your selections.

- 8. Click **OK** to close the New dialog box.

An empty (unprogrammed) design is loaded into the FPGA Editor window with the part number and speed as specified.

## **Opening an Existing Design File**

**Note** You must close your current design or macro before using the Open command to open another design.

To open an existing design file from within the FPGA Editor, follow these steps.

1. Select  $\mathtt{File} \rightarrow \mathtt{Open}$  or click on the Open toolbar button.

The Open dialog box is displayed.

| Design or Macro?         O Design       O Macro         Design File         Browse         Physical Constraints File | Open                              |          | ×              |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|----------------|

| Design File Browse Physical Constraints File                                                                         | – Design <u>o</u> r Macro? – – –  |          |                |

| Physical Constraints File                                                                                            | Design                            | O Macro  |                |

| Physical <u>C</u> onstraints File                                                                                    | <u>D</u> esign File               |          |                |

|                                                                                                                      |                                   |          | <u>B</u> rowse |

|                                                                                                                      | Physical <u>C</u> onstraints File |          |                |

| Biowse                                                                                                               |                                   |          | <u>Br</u> owse |

| <u>E</u> dit Mode                                                                                                    | <u>E</u> dit Mode                 |          |                |

| No Logic Changes 💌                                                                                                   | No Logic Changes                  | <b>v</b> |                |