# Xilinx/ Synopsys Interface Guide

Introduction to the Xilinx/ Synopsys Interface

**Getting Started**

Synthesizing Your Design with FPGA Compiler II

Synthesizing Your Design with FPGA Compiler and Design Compiler

Using Core Generator and LogiBLOX

Simulating Your Design

Using Files, Programs, and Libraries

**XSI Library Primitives**

**Targeting Virtex Devices**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

## **About This Manual**

This manual describes the Xilinx/Synopsys Interface (XSI) program, a tool used for implementing Field Programmable Gate Array (FPGA) designs using either Synopsys FPGA Compiler, FPGA Compiler II, or the Design Compiler synthesis tools.

This manual does not cover the use of Synopsys FPGA Express with the XSI program.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*. Other publications you can consult for related information are the *LogiBLOX Guide*, and *Libraries Guide*.

#### **Manual Contents**

This manual covers the following topics.

- "Introduction to the Xilinx/Synopsys Interface" chapter provides information on the XSI Design Flow, FPGA Compiler, FPGA Compiler II, and Design Compiler. This chapter also includes a list of additional documentation.

- "Getting Started" chapter shows you how to verify your software installation, modify your Synopsys startup file, and run Synlibs to set the link and target libraries.

- "Synthesizing Your Design with FPGA Compiler II" chapter shows how to port code from FPGA Compiler to FPGA Compiler II, convert script files from FPGA Compiler and Design Compiler

and includes design information on attribute passing, IOB configuration, clock buffers, memory, boundary scan, the Global Set/Reset net, and timing specifications.

- The "Synthesizing Your Design with FPGA Compiler and Design Compiler" chapter includes design information on wire-load models, IOB configuration, clock buffers, memory, boundary scan, the Global Set/Reset net, timing specifications, compiling, area reports, debugging, implementing, and saving your designs.

- The "Using Core Generator and LogiBLOX" chapter provides information about using Core Generator and LogiBLOX to create high-level modules for your designs.

- "Simulating Your Design" chapter describes how to perform RTL and timing simulation.

- "Using Files, Programs, and Libraries" chapter describes the files, programs, and Xilinx-supplied libraries you need to translate your HDL design using FPGA Compiler or Design Compiler.

- The "XSI Library Primitives" appendix lists the primitives you can synthesize or instantiate in a VHDL or Verilog HDL file.

- The "Targeting Virtex Devices" appendix describes how to apply the XSI design flow to Virtex devices.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm              |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools Search this database using the search function at http://support.xilinx.com/support/searchtd.htm |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                        |

| Resource       | Description/URL                                                                                                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Book      | Pages from <i>The Programmable Logic Data Book</i> , which contain device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                               |

| Technical Tips | Latest news, design tips, and patch information for the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                 |

### Conventions

This manual uses the following conventions. An example illustrates each convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: - 100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

File \rightarrow Open

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on|off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

```

allow block block_name loc1 loc2locn;

```

### **Online Document**

The following conventions are used for online documents.

Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.  Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Contents**

| About This | Manual                                                                                                                                                                                                                                                                                                                                                      |                                                      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|            | Manual Contents                                                                                                                                                                                                                                                                                                                                             | i                                                    |

| Conventior | ns                                                                                                                                                                                                                                                                                                                                                          |                                                      |

|            | TypographicalOnline Document                                                                                                                                                                                                                                                                                                                                |                                                      |

| Chapter 1  | Introduction to the Xilinx/Synopsys Interface                                                                                                                                                                                                                                                                                                               |                                                      |

|            | What Is XSI? XSI Design Flow Using FPGA Compiler II XSI Design Flow Using FPGA Compiler Comparing Design Compiler to FPGA Compiler and FPGA Compiler II Using FPGA Compiler II Xilinx Documentation Set                                                                                                                                                     | 1-2<br>1-3<br>1-5<br>1-6                             |

| Chapter 2  | Getting Started                                                                                                                                                                                                                                                                                                                                             |                                                      |

|            | Setting Up the Synopsys Interface  Setting up the XDW and Simulation Libraries  Compiling XDW Libraries  Compiling the Simulation Libraries  Modifying the Default Synopsys Startup File  Checking the FPGA Compiler Setup File  Checking the Design Compiler Setup File  Examples of Synopsys Setup Files  XC4000 Devices  Example .synopsys_dc.setup File | 2-3<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-9<br>2-9 |

|            | Example Script File for XC4000E/EX/XL/XV Designs  Virtex Devices  Example .synopsys_dc.setup File                                                                                                                                                                                                                                                           | 2-10<br>2-12                                         |

|            |                                                                                                                                                                                                                                                                                                                                                             |                                                      |

|           | Example Script File for Virtex DevicesVerifying Software Installation |          |

|-----------|-----------------------------------------------------------------------|----------|

| Chapter 3 | Synthesizing Your Design with FPGA Compiler II                        |          |

|           | Before You Begin                                                      | 3-2      |

|           | Naming Conventions                                                    | 3-2      |

|           | Porting Code from FPGA Compiler to FPGA Compiler II                   | 3-2      |

|           | Converting Script Files from FPGA Compiler and Design Comp            | iler 3-4 |

|           | Synthesizing the Design                                               | 3-4      |

|           | Entering Design Constraints and Controls                              | 3-9      |

|           | Specifying Timing Constraints                                         | 3-10     |

|           | Specifying Clock Constraints                                          | 3-12     |

|           | Specifying Path Group Constraints                                     |          |

|           | Specifying I/O Constraints                                            | 3-15     |

|           | Timing Subpaths                                                       | 3-15     |

|           | Defining Multicycle Timing Constraints                                | 3-17     |

|           | Adding Pull-Up and Pull-Down Resistors                                | 3-20     |

|           | Optimizing a Design Implementation                                    | 3-21     |

|           | Optimizing Logic Across Hierarchical Boundaries                       | 3-21     |

|           | Using a Flattening Optimization Strategy                              | 3-23     |

|           | Setting Port Attributes and Constraints                               | 3-23     |

|           | Evaluating Timing Delays                                              | 3-24     |

|           | Using the FPGA Compiler II Time Tracker                               | 3-25     |

|           | Viewing the Results of Optimization                                   | 3-25     |

|           | Generating Reports for Debugging                                      | 3-29     |

|           | Viewing the Schematics                                                | 3-30     |

|           | Exporting the Netlist                                                 | 3-30     |

|           | Using the Xilinx Development System                                   | 3-31     |

|           | HDL Coding Techniques                                                 | 3-31     |

|           | Configuring IOBs                                                      | 3-31     |

|           | All Architectures                                                     | 3-32     |

|           | Optimizing Inputs                                                     | 3-32     |

|           | Understanding and Using Slew Rate                                     | 3-32     |

|           | Using IOBs                                                            | 3-32     |

|           | Using Input Blocks                                                    | 3-32     |

|           | Using Output Blocks                                                   | 3-33     |

|           | Using Bidirectional Mode                                              | 3-34     |

|           | Inserting Bidirectional I/Os                                          |          |

|           | Assigning Pad Locations                                               |          |

|           | Instantiating a Registered Bidirectional I/O                          |          |

|           | Implementing 3-State Registered Output                                |          |

|           | Example of Not Directly Driving the 3-State Signal                    |          |

|                         | Example of Directly Driving the 3-State Signal              |      |

|-------------------------|-------------------------------------------------------------|------|

|                         | Attribute Passing                                           |      |

|                         | Implementing Clock Buffers                                  |      |

|                         | Using Memory                                                |      |

|                         | Implementing Virtex/E/2 RAM                                 |      |

|                         | Implementing XC4000 RAM                                     |      |

|                         | Implementing XC4000 ROM                                     |      |

|                         | Performing Boundary Scan                                    |      |

|                         | Using the Global Set/Reset Net                              |      |

|                         | Implementing GSR Buffers                                    |      |

|                         | Accessing Global Set/Reset Using STARTBUF                   |      |

|                         | Synthesizing/Simulating for VHDL Global Set/Reset Emulation |      |

|                         | Using STARTBUF in VHDL                                      |      |

|                         | Instantiating a STARTUP Block in VHDL                       |      |

|                         | Setting Direct Preset or Direct Clear                       |      |

|                         | Increasing Performance with the GSR Net                     | 3-59 |

| Chapter 4<br>Design Con | Synthesizing Your Design with FPGA Compiler and npiler      | k    |

|                         | Before You Begin                                            | 4-2  |

|                         | Naming Conventions                                          |      |

|                         | Setting the Wire-Load Model                                 |      |

|                         | Setting the Operating Condition Parameters                  |      |

|                         | Configuring IOBs                                            |      |

|                         | All Architectures                                           |      |

|                         | Optimizing Inputs                                           |      |

|                         | Understanding and Using Slew Rate                           |      |

|                         | XC3000A/L and XC3100A/L IOBs                                |      |

|                         | Using Input Blocks                                          |      |

|                         | Using Output Blocks                                         |      |

|                         | Using Bidirectional Mode                                    |      |

|                         | XC4000 IOBs                                                 | 4-7  |

|                         | Using Input Blocks                                          | 4-7  |

|                         | Using Output Blocks                                         | 4-7  |

|                         | Using Bidirectional Mode                                    | 4-8  |

|                         | Using XC5200 IOBs                                           | 4-9  |

|                         | Using Input Blocks                                          | 4-9  |

|                         | Using Output Blocks                                         |      |

|                         | Using Bidirectional Mode                                    |      |

|                         | Assigning Pad Locations                                     | 4-10 |

|                         | Implementing 3-State Registered Output                      | 4-11 |

| Example of Not Directly Driving the 3-State Signal          | 4-11 |

|-------------------------------------------------------------|------|

| Example of Directly Driving the 3-State Signal              |      |

| Inserting Bidirectional I/Os                                |      |

| Instantiating a Registered Bidirectional I/O                | 4-15 |

| Compiling Bidirectional I/O                                 |      |

| Using Unbonded IOBs                                         |      |

| Adding Pull-Up and Pull-Down Resistors                      | 4-22 |

| Removing the Default Input Delay                            | 4-23 |

| Initializing the IOB Flip-Flop to Preset                    | 4-23 |

| Inserting Clock Buffers                                     | 4-23 |

| Controlling Clock Buffer Insertion                          |      |

| Determining the Number of Clock Buffers                     | 4-26 |

| Preventing the Insertion of Clock Buffers                   | 4-27 |

| Using Memory                                                |      |

| Implementing XC4000 RAMs                                    | 4-28 |

| Implementing XC4000 ROMs                                    |      |

| Implementing RAM In Virtex Devices                          | 4-31 |

| Performing Boundary Scan                                    | 4-32 |

| Using the Global Set/Reset Net                              |      |

| Accessing Global Set/Reset Using STARTBUF                   |      |

| Synthesizing/Simulating for VHDL Global Set/Reset Emulation |      |

| Using STARTBUF in VHDL                                      | 4-39 |

| Instantiating a STARTUP Block in VHDL                       | 4-40 |

| Setting Direct Preset or Direct Clear                       |      |

| Increasing Performance with the GSR Net                     | 4-40 |

| Using the Xilinx DesignWare Library                         | 4-44 |

| Improving Design Area and Speed                             | 4-44 |

| Creating Timing Specifications                              | 4-46 |

| Following the DC2NCF Design Flow                            |      |

| Creating the Netlist and Script File (Design Compiler)      |      |

| Creating the Netlist and Script File (FPGA Compiler)        |      |

| Understanding DC2NCF Translation Limitations                |      |

| Limitations of Create Clock                                 |      |

| Limitations of Set Input Delay and Set Output Delay         |      |

| Limitations of Set Max Delay and Set False Path             | 4-52 |

| Set Multicycle Path                                         | 4-55 |

| Compiling Your Design                                       |      |

| Optimizing Logic Across Hierarchical Boundaries             |      |

| Using a Flattening Optimization Strategy                    |      |

| Compiling the Design with Hierarchy                         |      |

| Compiling the Design without Hierarchy                      |      |

| Compiling a Design with Instantiated I/O Cells              | 4-59 |

|           | Compiling XC4000, Spartan, and Virtex Designs        |      |

|-----------|------------------------------------------------------|------|

|           | Creating the Area Report                             |      |

|           | Evaluating Timing Delays                             |      |

|           | Generating Reports for Debugging                     |      |

|           | Generating a Configuration Report                    |      |

|           | Generating a Hierarchical Schematic                  |      |

|           | Creating a Level for Each CLB and IOB                |      |

|           | Generating a Level for Each Function Generator       |      |

|           | Writing and Saving Your Design                       | 4-71 |

|           | Saving the DB File                                   |      |

|           | Replacing CLBs and IOBs with Gates                   | 4-72 |

|           | Invoking the Replace FPGA Command                    | 4-72 |

|           | Replacing CLBs and IOBs in Designs with Hierarchy    | 4-73 |

|           | Controlling the Synopsys Mapping                     | 4-73 |

|           | Removing FMAP and HMAP Symbols                       | 4-74 |

|           | Restoring BLKNM Attributes                           | 4-74 |

|           | Setting the Design Part Type                         | 4-74 |

|           | Saving the Design Netlist File                       | 4-74 |

|           | Saving your Netlist in EDIF Format (Design Compiler) | 4-74 |

|           | Saving your Netlist in XNF Format (FPGA Compiler)    | 4-75 |

|           | Using the Xilinx Development System                  | 4-76 |

| Chapter 5 | Using Core Generator and LogiBLOX                    |      |

|           | Using Core Generator                                 | 5-1  |

|           | Specifying Inputs and Outputs in LogiBLOX            |      |

|           | Using LogiBLOX in the HDL Design Flow                |      |

|           | Instantiating RAM                                    |      |

|           | Instantiating RAM or ROM with FPGA Compiler          |      |

|           | Instantiating RAM or ROM with FPGA Compiler II       |      |

| 01 1 0    |                                                      |      |

| Chapter 6 | Simulating Your Design                               |      |

|           | Simulation Design Flow Overview                      | 6-2  |

|           | Using Simulation Libraries                           |      |

|           | UniSim Library                                       | 6-4  |

|           | UniSim Library Structure                             |      |

|           | UniSim Library Files                                 |      |

|           | UniSim Library Component Instantiation               |      |

|           | SimPrim Library                                      |      |

|           | LogiBLOX Library                                     |      |

|           | LogiBLOX Library Compilation                         |      |

|           | LogiBLOX Library Component Instantiation             |      |

|           |                                                      |      |

|           | Working with the VITAL Standard                             | 6-7  |

|-----------|-------------------------------------------------------------|------|

|           | VHDL and Verilog Simulation Flow                            |      |

|           | Simulating at Register Transfer Level (RTL)                 | 6-8  |

|           | Conducting a Post-Synthesis (pre-NGDBuild) Gate-Level       |      |

|           | Functional Simulation                                       | 6-9  |

|           | Conducting a Post-NGDBuild (Pre-Map) Gate-Level Functiona   |      |

|           | Simulation                                                  | 6-9  |

|           | Conducting a Post-Route Full Timing (Block and Net Delays)  |      |

|           | Simulation                                                  |      |

|           | Synthesizing/Simulating for VHDL Global Set/Reset Emulation |      |

|           | Using STARTBUF in VHDL                                      |      |

|           | Instantiating a STARTUP Block in VHDL                       |      |

|           | Generating a Reset-On-Configuration in VHDL                 | 6-12 |

|           | Using ROCBUF in VHDL                                        |      |

|           | Generating a 3-State-On-Configuration in VHDL               |      |

|           | Using TOCBUF in VHDL                                        |      |

|           | Using Oscillators in VHDL                                   |      |

|           | Using Global Set/Reset Emulation in Verilog                 |      |

|           | Using Global 3-State Emulation in Verilog                   |      |

|           | Using Oscillators in Verilog                                |      |

|           | NGDBuild Support of Multiple Device Architectures           |      |

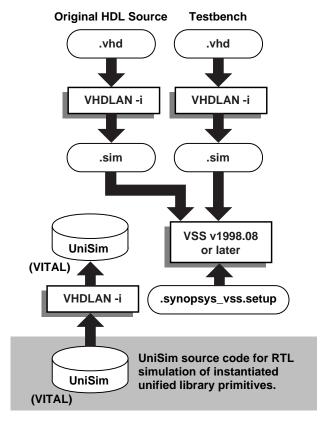

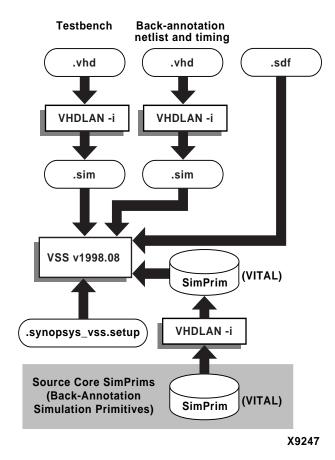

|           | Recommended VSS Simulation Strategy                         |      |

|           | VSS Simulation Flow                                         |      |

|           | Editing the VSS Setup File                                  |      |

|           | Creating a Testbench File                                   |      |

|           | Using RTL Simulation                                        |      |

|           | Implementing Your Design                                    | 6-22 |

| Chapter 7 | Using Files, Programs, and Libraries                        |      |

|           | Understanding the XSI Directory Structure                   | 7-1  |

|           | Using File Descriptions                                     |      |

|           | Using Program Descriptions                                  |      |

|           | Using Supplied Libraries Descriptions                       |      |

|           | Finding Supported Part Types and Speed Grades               |      |

|           | Finding Unsupported Part Types and Speed Grades             |      |

|           |                                                             |      |

| Appendix A | XSI Library Primitives                                                                                                                                                                                                                                                                                     |                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|            | Generating a List of XSI Library Primitives  Obtaining XSI Library Primitive Pin Order  Alphabetical List of Primitives for All Architectures  Using the Dont Touch Attribute                                                                                                                              | A-3<br>A-4                 |

|            | Setting the INIT Attribute Primitive Name Suffixes Virtex-Specific Primitive Name Suffixes                                                                                                                                                                                                                 | . A-4<br>. A-5             |

|            | Architecture AbbreviationsPrimitive Tables                                                                                                                                                                                                                                                                 | . A-7<br>. A-7             |

|            | Understanding Virtex-Specific Cell Names Virtex-Specific Primitives Table Virtex RAM Primitive Name Suffixes Xilinx DesignWare Modules Post-Configuration Initialization States                                                                                                                            | . A-34<br>. A-37<br>. A-41 |

| Appendix B | Targeting Virtex Devices                                                                                                                                                                                                                                                                                   |                            |

|            | Following General Guidelines  Setting FPGA Compiler to Synthesize a Virtex Design  Synthesizing a Virtex Design into FPGA Compiler  Setting VSS Simulation for Virtex  Setting FPGA Compiler II for Virtex  Synthesizing a Virtex Design in FPGA Compiler II  Using Clock Delay Locked Loops with Synopsys | B-3<br>B-4<br>B-5<br>B-6   |

# Chapter 1

# Introduction to the Xilinx/Synopsys Interface

This chapter describes the Xilinx/Synopsys Interface (XSI), compares FPGA Compiler, FPGA Compiler II, and Design Compiler, and lists additional Xilinx and Synopsys documentation you can use in conjunction with this manual. This chapter includes the following sections.

- "What Is XSI?"

- "XSI Design Flow Using FPGA Compiler II"

- "XSI Design Flow Using FPGA Compiler"

- "Comparing Design Compiler to FPGA Compiler and FPGA Compiler II"

- "Using FPGA Compiler II"

- "Xilinx Documentation Set"

#### What Is XSI?

XSI supports Synopsys FPGA Compiler Version 1999.05 or later, FPGA Compiler II Version 3.3 or later, and Synopsys Design Compiler Version 1999.05 or later.

This manual does not cover the use of Synopsys FPGA Express.

Use the XSI design tool kit to implement Xilinx Field Programmable Gate Array (FPGA) designs using either Synopsys FPGA Compiler, FPGA Compiler II, or Design Compiler. These Synopsys High-Level Design Automation (HLDA) tools allow you to create and optimize circuit designs from hardware descriptions written in VHSIC Hardware Description Language (VHDL) or Verilog HDL. Library support for XC4000E/L/EX/XL/XLA/XV, XC5200, XC9000, Spartan/XL/2, and Virtex/E/2 devices includes a Xilinx DesignWare (XDW) library.

Before you start creating your FPGA designs, refer to the most current version of the Alliance Series 3.1i Quick Start Guide for information about the following topics.

- XSI installation instructions

- Tutorial on the tools

- Reference information on common instantiated components

- Constraints guide

For the latest information on Xilinx parts and software, visit the Xilinx Web site at http://www.xilinx.com.

# **XSI Design Flow Using FPGA Compiler II**

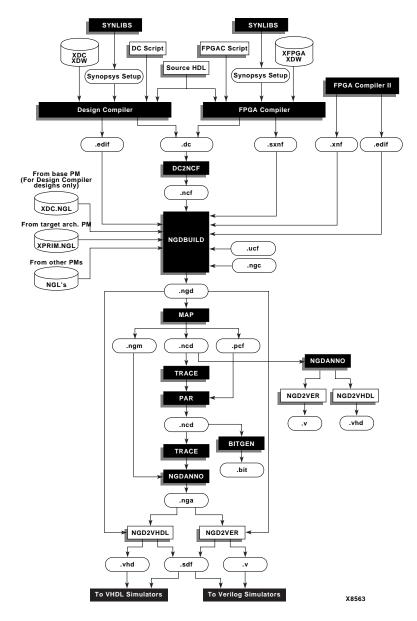

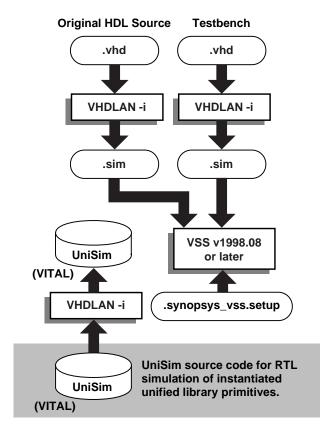

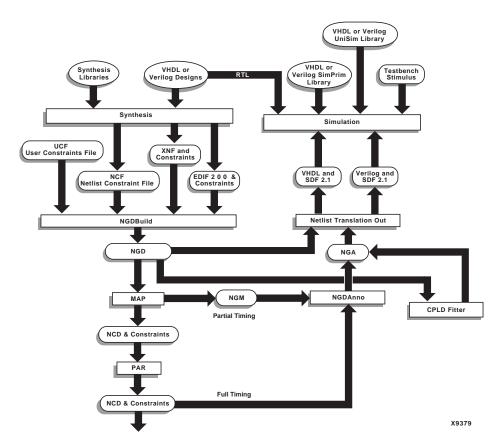

Figure 1-1 illustrates the following required steps you follow to implement and simulate your HDL designs using FPGA Compiler II.

Refer to the XSI Synopsys tutorials at http://support.xilinx.com/support/techsup/tutorials/index.htm for step-by-step instructions on converting your HDL designs.

- Synthesize your design with FPGA Compiler II.

- 2. Save your design as an EDIF file.

- 3. Run NGDBuild on the EDIF file to create an NGD file.

- Run the MAP program on the NGD file to create a mapped NCD file.

- 5. Run the TRACE program to determine if PAR meets your timing goals.

- 6. Run PAR on the NCD file to place and route your design.

- 7. Run TRACE again on your placed and routed design.

- 8. Run NGDAnno on your routed NCD and NGM files to create an NGA file.

- Run either NGD2VHDL or NGD2VER on the NGA file to create a VHDL (VHD) or Verilog (V) file for simulation with the appropriate simulators for back annotation. These two programs also create a Standard Delay Format (SDF) file containing timing information.

10. Run the BitGen program to create a bitstream for programming the FPGA.

# XSI Design Flow Using FPGA Compiler

Figure 1-1 illustrates the following required steps you follow to implement and simulate your HDL designs using FPGA Compiler.

Refer to the XSI Synopsys tutorials at http://support.xilinx.com/support/techsup/tutorials/index.htm for step-by-step instructions on converting your HDL designs.

- 1. Use the Synlibs program to determine the appropriate libraries for your design.

- 2. Synthesize your design with either FPGA Compiler or Design Compiler.

- 3. Save your design as an SXNF file or an SEDIF file, along with a DC file that contains Synopsys constraints. Make sure you use the .sxnf or .sedif file extension as NGDBuild will recognize that the netlists are coming from FPGA Compiler or Design Compiler.

- 4. Use the DC2NCF program to translate the Synopsys constraints DC file to a Netlist Constraints File (NCF).

- 5. Run NGDBuild on the SXNF or SEDIF file to create an NGD file.

- 6. Run the MAP program on the NGD file to create a mapped NCD file.

- 7. Run the TRACE program to determine if PAR meets your timing goals.

- 8. Run PAR on the NCD file to place and route your design.

- 9. Run TRACE again on your placed and routed design.

- 10. Run NGDAnno on your routed NCD and NGM files to create an NGA file.

- 11. Run either NGD2VHDL or NGD2VER on the NGA file to create a VHDL (VHD) or Verilog (V) file for simulation with the appropriate simulators for back annotation. These two programs also create a Standard Delay Format (SDF) file containing timing information.

12. Run the BitGen program to create a bitstream for programming the FPGA.

Figure 1-1 XSI Design Flow

# Comparing Design Compiler to FPGA Compiler and FPGA Compiler II

XSI contains libraries for the following device families:

- XC3000A/L

- XC3100A/L

- XC4000

- XC5200

- XC9000

- Spartan

- Virtex

You can use either FPGA Compiler, FPGA Compiler II, or Design Compiler to synthesize a design for these devices. Generally, for XC4000L and XC4000XL devices, you can use the XC4000E and the XC4000EX synthesis libraries, respectively.

This manual assumes that you use FPGA Compiler or FPGA Compiler II synthesis tools for XC4000, XC5200, XC9000, Spartan, and Virtex devices. If you do not have FPGA Compiler or FPGA Compiler II, XSI provides XC4000, XC5200, XC9000, Spartan, and Virtex libraries to use with Design Compiler. You can use FPGA Compiler or FPGA Compiler II for XC3000 and XC3100 devices, but the libraries for these devices use the Design Compiler synthesis features.

Design Compiler offers the following features.

- Optimizes flip-flops without clock enables, and latches in the input/output block (IOB)

- Optimizes 3-state buffers in the IOB

- Encodes one-hot state machines

- Automatically uses the configurable logic block (CLB) Clock Enable pin

FPGA Compiler and FPGA Compiler II offers the previously described Design Compiler features, as well as the following.

- Optimizes logic to the XC4000 and Spartan/XL CLB and IOB architectures

- Reports area and timing by device architecture, for example, CLB, IOB, and 3-state buffer

- Passes timing constraints to the core tools

- Uses lookup table (LUT) optimization for XC3000A/L, XC3100A/L, XC5200, Spartan2, and Virtex devices. These new libraries that use the LUT optimization allow FPGA Compiler and FPGA Compiler II to synthesize your design to a collection of lookup tables, registers, and I/O pads.

# **Using FPGA Compiler II**

FPGA Compiler II, a logic-synthesis and optimization tool, allows you to create optimized netlists from VHDL, Verilog, and existing unoptimized FPGA netlists. FPGA Compiler II (Version 3.2 or better) offers the following features.

- Provides an integrated text editor for entering VHDL and Verilog source code for your design

- Analyzes HDL source files for correct syntax, accepting any combination of VHDL, Verilog, and FPGA netlist files as sources

- Synthesizes logic from VHDL, Verilog, and FPGA netlist sources

- Optimizes logic for speed and area according to design constraints

- Contains integrated schematic viewing and static timing analysis

- Extracts and displays accurate post-synthesis delay information

Synopsys provides FPGA Compiler II libraries used for Xilinx products.

#### **Xilinx Documentation Set**

The following documents provide additional design information.

- CPLD Synthesis Design Guide contains information on how to use your Synopsys tools with the Xilinx Development System to create CPLD designs.

- *Development System Reference Guide* provides detailed information on the programs found in Xilinx software.

- LogiBLOX Guide describes the LogiBLOX program, a tool used to create high-level modules for insertion into your HDL design.

- *Libraries Guide* presents information about the various Xilinx-provided primitives and macros.

- Alliance 3.1i *Release Documentation* describes installation setup and current issues regarding the use of the Synopsys interface.

- For converting an XACT 5.xx Synopsys design to M1, refer to the Xilinx Software Conversion Guide from XACTstep v.5.X.X to XACTstep vM1.X.X.

# **Chapter 2**

# **Getting Started**

This chapter provides information on setting up the Xilinx Synopsys Interface (XSI) and associated libraries. Example files are included to help you set up the FPGA Compiler with the Xilinx software. This chapter also describes how to verify your software installation, modify the .synopsys\_dc.setup file, and use the Synlibs program to determine the correct XSI libraries for FPGA Compiler or Design Compiler. You will also find general information about using the interface.

Read this chapter before you begin either the FPGA Compiler or Design Compiler tutorials located at http://

www.support.xilinx.com/support/techsup/tutorials/

index.htm.

This chapter includes the following sections.

- "Setting Up the Synopsys Interface"

- "Setting up the XDW and Simulation Libraries"

- "Modifying the Default Synopsys Startup File"

- "Examples of Synopsys Setup Files"

- "Verifying Software Installation"

# **Setting Up the Synopsys Interface**

The following environment variables must be modified or added to run the Synopsys interface tools.

- SYNOPSYS (add)

- PATH (modify)

- LD\_LIBRARY\_PATH (modify)

- SHLIB\_PATH (modify)

#### Set these variables as follows.

```

setenv SYNOPSYS installation_path_to_synopsys

set path = ($XILINX/bin/platform_name \

$SYNOPSYS/platform_name/syn/bin \

$SYNOPSYS/platform_name/sim/bin \

$path)

```

#### For Solaris only.

```

setenv LD_LIBRARY_PATH $SYNOPSYS/platform_name/sim/

lib:$LD_LIBRARY_PATH

```

#### For HP/UX only.

```

setenv SHLIB_PATH $SYNOPSYS/platform_name/sim/

lib:$SHLIB_PATH

```

#### The following is an example.

```

setenv SYNOPSYS /usr/synopsys

set path = ($XILINX/bin/sol \

$SYNOPSYS/sol/syn/bin \

$SYNOPSYS/sol/sim/bin \

$path)

setenv LD_LIBRARY_PATH $SYNOPSYS/sol/sim/

lib:$LD_LIBRARY_PATH

```

# **Setting up the XDW and Simulation Libraries**

**Note** If you are not using FPGA Compiler II v3.2 or a later, you must re-compile the Xilinx DesignWare (XDW) libraries.

The XSI (Xilinx Synopsys Interface) simulation and XDW (Xilinx DesignWare) libraries are compiled for Synopsys v1999.05. If you are using the latest version of XSI with a version of Synopsys newer than v1999.05, you must re-compile the XDW libraries with the version of Synopsys you are using. If you are going to simulate with VSS, you must re-compile the simulation libraries.

Compiling the libraries in the \$XILINX area requires write permissions to this area. If you copy the \$XILINX/synopsys directory to a local area, you do not need rewrite permissions for the \$XILINX area to re-compile the libraries. However, verify that the .synopsys\_dc.setup and .synopsys\_vss.setup files use the local copy.

### **Compiling XDW Libraries**

Follow these steps to compile the XDW libraries.

- 1. Set up your Xilinx and Synopsys software environments.

- 2. Go to the \$XILINX/synopsys/libraries/dw/src directory.

- 3. In this directory, there are subdirectories that represent the Xilinx device families that have XDW libraries. If you are going to use any of the device families listed, you must go to the corresponding subdirectory and run the .dc compile script in that directory. For example, for a Spartan device, enter the following commands.

cd spartan

Run the install\_dw.dc script by entering the following.

```

dc_shell -f install_dw.dc

```

4. When the script is finished, go back to \$XILINX/synopsys/libraries/dw/src. Repeat these steps for each device you plan on using.

### **Compiling the Simulation Libraries**

**Note** The following procedure is for compiling the XSI simulation libraries with VSS. If you are using a different HDL simulator, refer to your simulator's documentation for instructions on compiling HDL simulation libraries.

- 1. Setup your XSI and Synopsys software environments.

- 2. Go to the \$XILINX/synopsys/libraries/sim/src directory.

- 3. In this directory, there are subdirectories that represent the five simulation libraries, described as follows.

- ◆ LogiBLOX for functional simulation of VHDL designs with instantiated LogiBLOX components

- ♦ SimPrims timing simulation library

- UNISIMS functional simulation library

- ★ XC9000 XC9500 functional simulation library

- ◆ XDW Functional simulation library for post-synthesis (FPGA compiler) pre-NGDBuild simulation

Some or all of these libraries need to be re-compiled depending on the device and type of simulation you plan on using. Xilinx recommends compiling the logiblox, simprims, and unisims libraries. Use the following steps to compile these libraries.

4. Go to the logiblox directory and enter the following command.

./analyze.csh

Go back to the \$XILINX/synopsys/libraries/sim/src directory.

5. Go to the simprims directory and enter the following command.

./analyze.csh

Go back to the \$XILINX/synopsys/libraries/sim/src directory.

6. Go to the unisims directory and enter the following command.

./analyze.csh

The unisims directory also contains the analyze\_52k.csh script. If you plan on simulating XC5200 devices, you must run this script as well. You must also edit the .synopsys\_dc.setup file in the unisims directory to point to a location for the compiled XC5200 libraries.

Go back to the \$XILINX/synopsys/libraries/sim/src directory.

7. Go to the xdw directory and enter the following command.

./analyze.csh

Go back to the \$XILINX/synopsys/libraries/sim/src directory.

Go to the xc9000/ftgs directory and enter the following command.

dc shell -f install xc9000.dc

# Modifying the Default Synopsys Startup File

The startup file for the Synopsys synthesis tools is .synopsys\_dc.setup. This file contains the search path for the XSI libraries, Synopsys libraries, and user libraries. XSI provides a template Synopsys startup file.

XSI provides the template.synopsys\_dc.setup\_dc and template.synopsys\_dc.setup\_fc template files. You can find the template files in the \$XILINX/synopsys/examples directory. Use template.synopsys\_dc.setup\_dc if you use Design Compiler; use template.synopsys\_dc.setup\_fc if you use FPGA Compiler.

\$SYNOPSYS is the directory where the Synopsys software resides. If you do not know the location of this directory, enter the following at the system prompt.

#### echo \$SYNOPSYS

If you already have a .synopsys\_dc.setup file, you must modify your file to include the commands found in the Xilinx-supplied template startup files.

If you do not already have a Synopsys startup file, copy the appropriate Xilinx-supplied startup file to your home or working directory and rename it as follows.

```

cp $XILINX/synopsys/examples/

template.synopsys_dc.setup_compiler

.synopsys_dc.setup

```

Substitute "dc" or "fc" for compiler.

### **Checking the FPGA Compiler Setup File**

This section contains a reproduction of the template setup file for FPGA Compiler.

```

______

Template .synopsys_dc.setup file for Xilinx

designs

* /

/*

For use with Synopsys FPGA Compiler.

* /

/*

______

/* The Synopsys search path should be set to point

* /

/* to the directories that contain the various

* /

/* synthesis libraries used by FPGA Compiler during synthesis.*/

XilinxInstall = get_unix_variable(XILINX);

SynopsysInstall = get unix variable(SYNOPSYS);

search_path = { . \

XilinxInstall + /synopsys/libraries/syn \

SynopsysInstall + /libraries/syn }

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!!!

/* Ensure that your UNIX environment */

/* includes the two environment var- */

/* iables: $XILINX (points to the

/* Xilinx installation directory) and*/

/* $SYNOPSYS (points to the Synopsys */

/* installation directory.)

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

/* =========== */

/* Define a work library in the current project dir

/* to hold temporary files and keep the project area */

/* uncluttered. Note: You must create a subdirectory */

/* in your project directory called WORK.

* /

```

```

/* ============ */

define_design_lib WORK -path ./WORK

/* ============ */

/* General configuration settings.

* /

/* =========== */

compile_fix_multiple_port_nets = true

xnfout_constraints_per_endpoint = 0

xnfout_library_version = "2.0.0"

bus naming style = "%s<%d>"

bus dimension separator style = "><"

bus inference style = "%s<%d>"

/* ========== */

/* Set the link, target and synthetic library

* /

/* variables. Use synlibs (with the -fc switch) to

* /

/* determine the link and target library settings.

* /

/* You may like to copy this file to your project

* /

/* directory, rename it ".synopsys dc.setup" and

* /

/* append the output of synlibs. For example:

* /

synlibs -fc 4028ex-3 >> .synopsys_dc.setup

/* ============ */

```

## **Checking the Design Compiler Setup File**

This section shows the template setup file for Design Compiler.

```

file

for

Xilinx

Template

.synopsys_dc.setup

designs

* /

/*

For use with Synopsys Design Compiler.

/* ============== */

/* ================== */

/* The Synopsys search path should be set to point

* /

/* to the directories that contain the various

* /

/*synthesis libraries used by Design Compiler during

* /

/* synthesis.

/* ============= */

XilinxInstall = get_unix_variable(XILINX);

SynopsysInstall = get_unix_variable(SYNOPSYS);

```

```

search_path = { . \

XilinxInstall + /synopsys/libraries/syn \

SynopsysInstall + /libraries/syn }

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!*/

/* Ensure that your UNIX environment */

/* includes the two environment var- */

/* iables: $XILINX (points to the

/* Xilinx installation directory) and*/

/* $SYNOPSYS (points to the Synopsys */

/* installation directory.)

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

/* =========== */

/* Define a work library in the current project dir */

/* to hold temporary files and keep the project area */

/* uncluttered. Note: You must create a subdirectory */

/* in your project directory called WORK.

/* =========== */

define_design_lib WORK -path ./WORK

/* =========== */

/* General configuration settings.

/* =========== */

compile fix multiple port nets = true

bus_naming_style = "%s<%d>"

bus_dimension_separator_style = "><"</pre>

bus_inference_style = "%s<%d>"

edifout netlist only = true

edifout_power_and_ground_representation = cell

edifout_write_properties_list = "instance_number pad_location part"

edifout no array = true

/* =========== */

/* Set the link, target and synthetic library

* /

/* variables. Use synlibs (with the -dc switch) to

* /

/* determine the link and target library settings.

* /

/* You may like to copy this file to your project

* /

/* directory, rename it ".synopsys dc.setup" and

* /

/* append the output of synlibs. For example:

* /

synlibs -dc 4028ex-3 >> .synopsys_dc.setup

* /

/* ============= */

```

# **Examples of Synopsys Setup Files**

This section includes examples of the Synopsys setup files needed to run the FPGA Compiler with the Xilinx tools. These examples are for XC4000XL and Virtex devices. Other FPGA and CPLD templates are in the Xilinx installation path, \$XILINX/synopsys/examples.

#### XC4000 Devices

Although the following .synopsys\_dc.setup file example is for an XC4000XL device, it is similar to the setup file required for XC4000E/EX/XLA/XV devices.

## Example .synopsys\_dc.setup File

Following is an example of a .synopsys\_dc.setup file.

```

/* Template .synopsys dc.setup file for Xilinx */

/* For targeting a XC4000XL

* /

XilinxInstall = get unix variable(XILINX);

SynopsysInstall = get_unix_variable(SYNOPSYS);search_path = { . \

XilinxInstall + /synopsys/libraries/syn \

SynopsysInstall + /libraries/syn }

/* Define a work library. You must create 'work'

define design lib WORK -path ./WORK

/* Declare the Xilinx DesignWare library

* /

define design lib xdw 4000xl -path \

XilinxInstall + /synopsys/libraries/dw/lib/xc4000xl

/* General configuration settings.

* /

compile_fix_multiple_port_nets = true

xnfout_constraints_per_endpoint = 0

xnfout_library_version = "2.0.0"

bus_naming_style = "%s<%d>"

bus dimension separator style = "><"

bus inference style = "%s<%d>"

synlibs -fc 4028ex-3 >> .synopsys dc.setup */

```

## Example Script File for XC4000E/EX/XL/XV Designs

This section describes the typical sequence of commands used to process designs with the Synopsys interface. You should run the commands at the dc\_shell command line, either individually or in batch mode. While every design may not require all the commands used in this section, the following example represents a good starting point for most designs. This script file includes information on I/O pin location constraints, timing constraints, setting the part-type, controlling I/O characteristics, and controlling Synopsys mapping and packing functions.

\*\*add tabs to the following for correct spacing\*\*

```

/* Sample Script for Synopsys to Xilinx Using */

/* FPGA Compiler targeting a XC4000EX device*/

/* Set the name of the design's top-level */

TOP = <design_name>

designer = "XSI Team"

company = "Xilinx, Inc"

= "4028 \exp 299 - 3"

/* Analyze and Elaborate the design file. */

analyze -format vhdl TOP + ".vhd"

elaborate TOP

/* Set the current design to the top level. */

current_design TOP

/* Set the synthesis design constraints. */

remove constraint -all

/* Some example constraints */

create_clock <clock_port_name> -period 50

set_input_delay 5 -clock <clock_port_name> \

{ <a_list_of_input_ports> }

set_output_delay 5 -clock <clock_port_name> \

{ <a_list_of_output_ports> }

set max delay 100 -from <source> -to <destination>

set false path -from <source> -to <destination>

/* Indicate which ports are pads. */

set_port_is_pad "*"

/* Some example I/O parameters */

set_pad_type -pullup <port_name>

set pad type -no clock all inputs()

```

```

set_pad_type -clock <clock_port_name>

set_pad_type -exact BUFGS_F <hi_fanout_port_name>

set_pad_type -slewrate HIGH all_outputs()

insert_pads

/* Synthesize the design.*/

compile -boundary_optimization -map_effort med

/* Write the design report files. */

report_fpga > TOP + ".fpga"

report_timing > TOP + ".timing"

/* Write out an intermediate DB file to save state*/

write -format db -hierarchy -output TOP + "_compiled .db"

/* Replace CLBs and IOBs primitives (XC4000E/EX/XL only)*/

replace fpga

/* reapply set_max_delay/set_false_path if using FPGA compiler */

/* Set the part type for the output netlist.

set_attribute TOP "part" -type string part

/* Optional attribute to remove the mapping symbols*/set attribute

find(design, "*")\

"xnfout_write_map_ symbols" -type boolean FALSE

/* Add any I/O constraints to the design. */

set attribute <port name> "pad location" \

-type string "<pad location>"

/* Write out the intermediate DB file to save state*/

write -format db -hierarchy -output TOP + ".db"

/* Write out the timing constraints*/

ungroup -all -flatten

write script > TOP + ".dc"

/* Save design in XNF format as <design>.sxnf */

write -format xnf -hierarchy -output TOP + ".sxnf"

/* Convert constraints to Xilinx syntax */

sh dc2ncf TOP + ".dc"

/* Exit the Compiler. */

exit

```

#### **Virtex Devices**

The following setup file examples are for Virtex devices.

### Example .synopsys\_dc.setup File

```

/* ============ */

/* Template .synopsys_dc.setup file for Xilinx designs */

/* For use with Synopsys FPGA Compiler.

/* =========== */

/* =========== */

/* The Synopsys search path should be set to point

/* to the directories that contain the various

/* synthesis libraries used by FPGA Compiler during */

/* synthesis.

/* ============ */

XilinxInstall = get unix variable(XILINX);

SynopsysInstall = get unix variable(SYNOPSYS);

search path = { .

XilinxInstall + /synopsys/libraries/syn \

SynopsysInstall + /libraries/syn }

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!*/

/* Ensure that your UNIX environment */

/* includes the two environment var- */

/* iables: $XILINX (points to the

/* Xilinx installation directory) and*/

/* $SYNOPSYS (points to the Synopsys */

/* installation directory.)

/* !!!!!!!!!!!!!!!!!!!!!!!!!!!!!

/* ============ */

```

```

/* Define a work library in the current project dir */

/* to hold temporary files and keep the project area */

/* uncluttered. Note: You must create a subdirectory */

/* in your project directory called WORK.

/* =========== */

define_design_lib WORK -path ./WORK

bus extraction style = "%s<%d:%d>"

bus naming style = "%s<%d>"

bus dimension separator style = "><"

edifin lib logic 1 symbol = "VCC"

edifin lib logic 0 symbol = "GND"

edifout_ground_name = "GND"

edifout ground pin name = "G"

edifout power name = "VCC"

edifout power pin name = "P"

edifout netlist only = "true"

edifout_no_array = "false"

edifout power and ground representation = "cell"

edifout_write_properties_list = { "CLK1X_DUTY" "INIT_00"

"INIT 01" "INIT 02" "INIT 03" \

"INIT 04"

"INIT_05" "INIT_06" "INIT_07" "INIT_08" "INIT_09"

"INIT_0A" "INIT_0B" "INIT_0C" \

"INIT OD" "INIT OE" "INIT OF" "INIT" "CLKDV DIVIDE" "IOB" "EON"

"lut function" }

/* ============= */

/* Set the link, target and synthetic library

* /

/* variables. Use synlibs to

* /

/* determine the link and target library settings.

* /

/* You may like to copy this file to your project

* /

/* directory, rename it ".synopsys dc.setup" and

* /

/* append the output of synlibs. For example:

* /

/* synlibs xfpga_virtex-3 >> .synopsys_dc.setup

* /

/* ========== */

link_library = {xfpga_virtex-5.db }

symbol_library = {virtex.sdb}

```

```

define_design_lib xdw_virtex -path XilinxInstall + /synopsys/

libraries/dw/lib/virtex

synthetic_library = {xdw_virtex.sldb standard.sldb}

```

## **Example Script File for Virtex Devices**

```

/* =========== */

/*

Sample Script for Synopsys to Xilinx Using

/*

FPGA Compiler

* /

/*

Targets the Xilinx XCV150PQ240-3 and assumes a

/*

* /

VHDL source file by way of an example.

/*

* /

For general use with VIRTEX architectures.

/* =========== */

/* ========== */

/* Set the name of the design's top-level module.

* /

/* (Makes the script more readable and portable.)

* /

/* Also set some useful variables to record the

* /

* /

/* designer and company name.

/* ============ */

```

```

TOP = <design_name>

/* ======== */

/* Note: Assumes design file- */

/* name and entity name are */

/* the same (minus extension) */

/* ======= */

designer = "XSI Team"

company = "Xilinx, Inc"

part = "XCV150PQ240-3"

/* ========== */

/* Analyze and Elaborate the design file and specify */

/* the design file format.

* /

/* ============ */

analyze -format vhdl TOP + ".vhd"

```

```

/* ======= */

/* You must analyze lower-level */

/* hierarchy modules here */

/* ======== */

elaborate TOP

/* =========== */

/* Set the current design to the top level.

/* =========== */

current_design TOP

/* ========== */

/* Set the synthesis design constraints.

* /

/* ========== */

remove constraint -all

/* If setting timing constraints, do it here.

For example:

* /

/*

create_clock <clock_pad_name> -period 50

```

```

/* ============ */

/* Indicate those ports on the top-level module that */

/* should become chip-level I/O pads. Assign any I/O */

/* attributes or parameters and perform the I/O

/* synthesis.

* /

/* ============ */

set_port_is_pad "*"

set_pad_type -slewrate HIGH all_outputs()

insert pads

/*

Compile the design

* /

compile -map_effort med

/* ============ */

/* Write the design report files.

* /

/* ============= */

report_fpga > TOP + ".fpga"

```

```

report_timing > TOP + ".timing"

/* ========== */

/* Set the part type for the output netlist.

/* =========== */

set_attribute TOP "part" -type string part

/* ============= */

/* Save design in EDIF format as <design>.sedif

/* =========== */

write -format xnf -hierarchy -output TOP + ".sedif"

/* =========== */

/* Write out the design to a DB.

* /

/* ============= */

write -format db -hierarchy -output TOP + ".db"

/* =========== */

/* Write-out the timing constraints that were

/* applied earlier. (Note that any design hierarchy */

/* needs to be flattened before the constraints are */

```

```

* /

/* written-out.)

/* =========== */

write_script > TOP + ".dc"

/* ========== */

/* Call the Synopsys-to-Xilinx constraints translator*/

/* utility DC2NCF to convert the Synopsys constraints*/

/* to a Xilinx NCF file. You may like to view

* /

/* dc2ncf.log to review the translation process.

/* =========== */

sh dc2ncf -w TOP + ".dc"

/* =========== */

/* Exit the Compiler.

/* =========== */

exit

/* ========== */

/* Now run the Xilinx design implementation tools. */

/* ============= */

```

# **Verifying Software Installation**

Use the following steps to verify installation of Xilinx, XSI, and DesignWare software on your system, and to ensure your .cshrc or .login files include the required environmental variables and search paths.

Xilinx supports Synopsys v1998.08 and later, and Synopsys FPGA Compiler II version 3.2 or later. These instructions verify the installation of Synopsys v 1998.08 or later.

- 1. Go to the platform where the Xilinx software is installed.

- 2. To verify that your system has the Xilinx software, enter the following.

```

which par

```

The full path for PAR appears. If the system cannot find PAR, refer to the installation instructions in the release notes or contact your system administrator.

3. To verify XSI installation, enter the following.

```

which synlibs

```

The full path for XSI appears. If the system cannot find Synlibs, refer to the installation instructions in the release notes or contact your system administrator.

4. Enter the following to change to the correct directory.

```

cd $XILINX/synopsys/libraries/dw/lib/architecture

```

5. List the contents of this directory to verify that installation placed the source Xilinx DesignWare files in this directory.

This directory contains the object file for the Xilinx DesignWare symbol modules (*xdw\_module*.syn) and the simulation modules (*xdw\_module*.sim). The variable xdw\_module refers to the Xilinx DesignWare primitive name.

If you do not find the SYN and SIM files in this directory, refer to the release notes or contact your system administrator. The README file contains installation instructions, and resides in the \$XILINX/synopsys/libraries/dw/src/architecture directory.

6. To verify that you are using Synopsys v1998.08 or later, enter the following.

### design\_analyzer

This command starts Design Analyzer and displays the version number on your screen.

# **Chapter 3**

# Synthesizing Your Design with FPGA Compiler II

Synthesize and implement your HDL designs for Xilinx FPGA devices with FPGA Compiler II by using the information in the following sections.

- "Before You Begin"

- "Naming Conventions"

- "Porting Code from FPGA Compiler to FPGA Compiler II"

- "Converting Script Files from FPGA Compiler and Design Compiler"

- "Synthesizing the Design"

- "Entering Design Constraints and Controls"

- "Specifying Timing Constraints"

- "Optimizing a Design Implementation"

- "Evaluating Timing Delays"

- "Exporting the Netlist"

- "Using the Xilinx Development System"

- "HDL Coding Techniques"

- "Inserting Bidirectional I/Os"

- "Implementing 3-State Registered Output"

- "Attribute Passing"

- "Implementing Clock Buffers"

- "Using Memory"

- "Performing Boundary Scan"

• "Using the Global Set/Reset Net"

# **Before You Begin**

Before beginning a Xilinx design using the Synopsys tools, read the "Getting Started" chapter and ensure the following.

- Verify the installation of Xilinx software on your system.

- Verify that you use Synopsys version 3.3.1 or later for FPGA Compiler II.

# **Naming Conventions**

Unless otherwise noted, the following naming conventions are used to group Xilinx device families:

- Virtex represents Virtex, Virtex-E, Virtex-II and Spartan-II devices.

- Spartan represents Spartan and SpartanXL devices.

- XC4000 represents XC4000E, XC4000L, XC4000EX, XC4000XL, XC4000XLA and XC4000XV devices.

- XC9500 represents XC9500, XC9500XL, XC9500XV and XC9500XVA devices.

- XC3000 represents XC3100 and XC3100A devices.

- XC5200 represents XC5200 devices.

# Porting Code from FPGA Compiler to FPGA Compiler II

You can port a design from FPGA Compiler or Design Compiler to FPGA Compiler II. You do not have to modify the code if you are compiling a 100 percent behavioral design originally compiled with FPGA Compiler or Design Compiler. However, if you instantiated components from the XSI libraries, understand that some of these components do not exist in the FPGA Compiler II libraries.

Some of the components you can instantiate in the Xilinx design flow you cannot instantiate in the FPGA Compiler II tool because of slight differences in names. For example, the BUFGP\_F in the XSI component library does not exist in the FPGA Compiler II component library. In FPGA Compiler II, the equivalent name of the BUFGP\_F is BUFGP. For a complete listing of the library cells that can be instantiated in FPGA Compiler II, refer to the contents of the following.

fpgacompilerII/lib/virtex

fpgacompilerII/lib/spartan

fpgacompilerII/lib/spartanxl

fpgacompilerII/lib/xc4000e

fpgacompilerII/lib/xc4000ex

fpgacompilerII/lib/xc9500

fpgacompilerII/lib/xc3000

fpgacompilerII/lib/xc5200

The *fpgacompilerII* directory is where FPGA Compiler II resides on your system. These directories contain files with a .dsn extension. The string in front of .dsn is the name of the CELL that you can instantiate in FPGA Compiler. Refer to the *Xilinx Libraries Guide* for pin names.

In general, instantiation is not necessary. For the XC4000 and Virtex FPGA Compiler II flow, you must instantiate the following components.

- I/O multiplexers

- Fast capture latches

- RAM

- BSCAN, READBACK

- LogiBLOX, CoreGen modules

# **Converting Script Files from FPGA Compiler and Design Compiler**

This chapter will not document the TCL-based scripting capabilities of FPGA Compiler II. Please consult the FPGA Compiler II documentation for details on the fc2\_shell program. However, a few things are noted here:

- fc2\_shell is the command line name of the FPGA Compiler II shell tool.

- A script converter, dc-transcript, is available on Unix to convert DC shell scripts to TCL shell. This program is not available within FPGA Compiler II itself.

- TCL script can be created after synthesizing in the FPGA Compiler II

GUI. Select the optimized chip and then select Script → Export

FPGA Script to create a script of all the commands run up to that

point.

# Synthesizing the Design

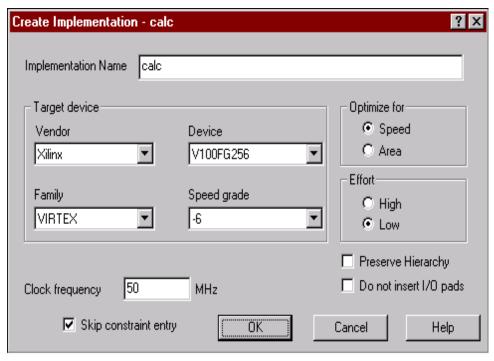

This section describes the synthesis flow through the FPGA Compiler II product, using the Graphical User Interface (GUI), from creating the project through the netlist generation.

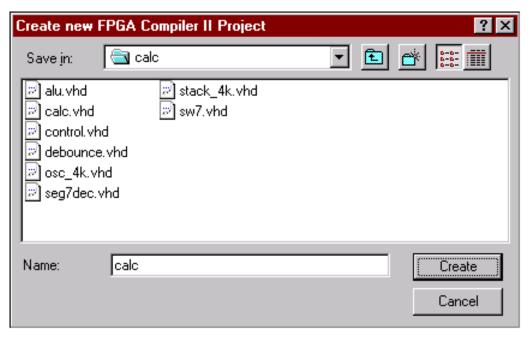

After opening the FPGA Compiler II GUI, select  $\mathtt{File} \to \mathtt{New}$  Project. Select the name and location for this project before clicking Create. HDL source files may also be added at this time.

Figure 3-1 Create a New FPGA Compiler II Project

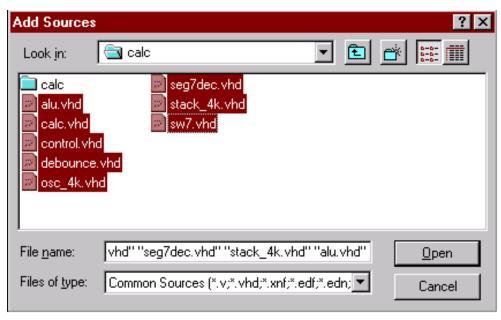

Add all the source files by selecting **Synthesis**  $\rightarrow$  **Add Source Files** (if they have not yet been added to the project). FPGA Compiler II analyzes the source files and reports syntax errors. Be sure to add any package files first, as these files must be analyzed before the HDL files that access them.

Figure 3-2 Add HDL Source Files

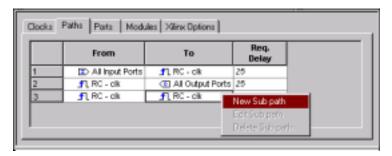

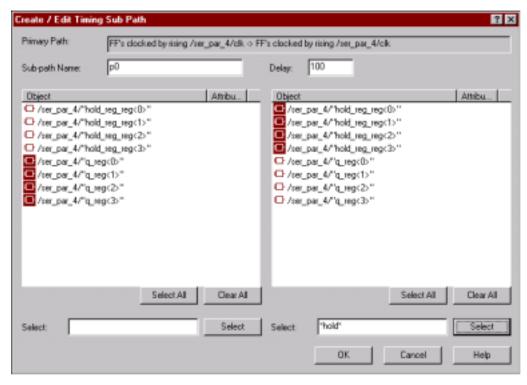

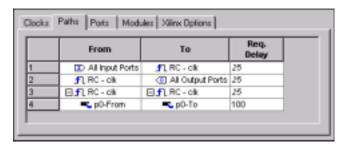

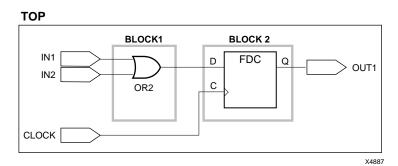

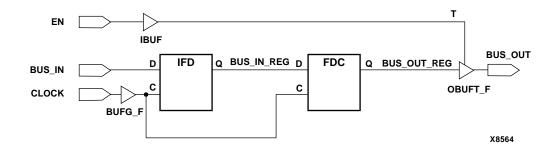

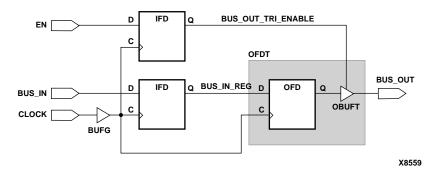

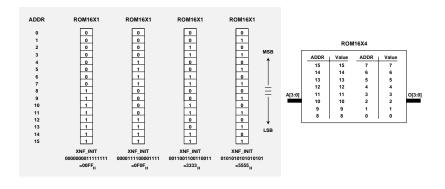

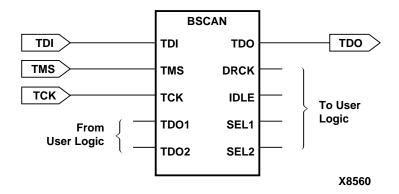

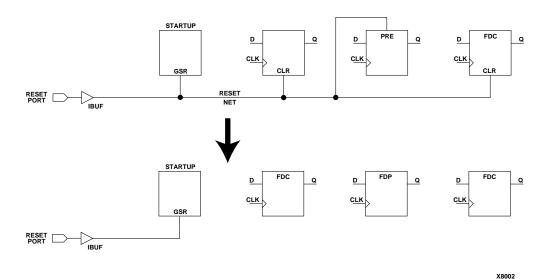

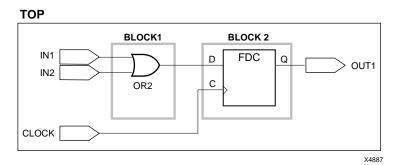

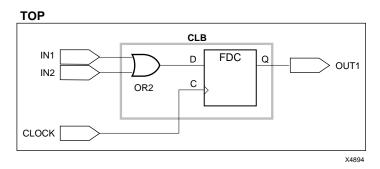

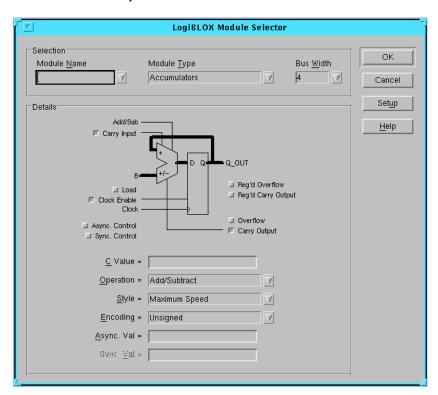

New libraries may be created by selecting **Synthesis**  $\rightarrow$  **New Library**. Give this new library a name and click **OK**. Add any VHDL library files to it by right clicking the library name and selecting **Add sources in library**>.