# **Using the Virtex Delay-Locked Loop**

## **Summary**

The Virtex<sup>™</sup> FPGA series offers up to eight fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits providing zero propagation delay, low clock skew between output clock signals distributed throughout the device, and advanced clock domain control. These dedicated DLLs can be used to implement several circuits which improve and simplify system level design.

## Introduction

As FPGAs grow in size, quality on-chip clock distribution becomes increasingly important. Clock skew and clock delay impact device performance and the task of managing clock skew and clock delay with conventional clock trees becomes more difficult in large devices. The Virtex series of devices resolve this potential problem by providing up to eight fully digital dedicated on-chip Delay-Locked Loop (DLL) circuits which provide zero propagation delay and low clock skew between output clock signals distributed throughout the device.

Each DLL can drive up to two global clock routing networks within the device. The global clock distribution network minimizes clock skews due to loading differences. By monitoring a sample of the DLL output clock, the DLL can compensate for the delay on the routing network, effectively eliminating the delay from the external input port to the individual clock loads within the device.

In addition to providing zero delay with respect to a user source clock, the DLL can provide multiple phases of the source clock. The DLL can also act as a clock doubler or it can divide the user source clock by up to 16.

Clock multiplication gives the designer a number of design alternatives. For instance, a 50 MHz source clock doubled by the DLL can drive an FPGA design operating at 100 MHz. This technique can simplify board design because the clock path on the board no longer distributes such a high-speed signal. A multiplied clock also provides designers the option of time-domain-multiplexing, using one circuit twice per clock cycle, consuming less area than two copies of the same circuit. Two DLLs can be connected in series to increase the effective clock multiplication factor to four.

The DLL can also act as a clock mirror. By driving the DLL output off-chip and then back in again, the DLL can be used to de-skew a board level clock between multiple devices.

The DLL can delay the completion of configuration until after DLL locks to guarantee the system clock is established prior to initiating the device.

By taking advantage of the DLL to remove on-chip clock delay, the designer can greatly simplify and improve system level design involving high-fanout, high-performance clocks.

## **Fundamentals**

Two basic types of circuits remove clock delay: Phased-Locked Loops (PLLs), and DLLs. In addition to the primary function of removing clock distribution delay, DLLs and PLLs typically provide some additional functionality such as frequency synthesis (clock multiplication and clock division) and clock conditioning (duty cycle correction and phase shifting). Multiple clock outputs can also be de-skewed with respect to one another, to take advantage of multiple clock domains.

© 2000 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

#### **Delay-Locked Loop**

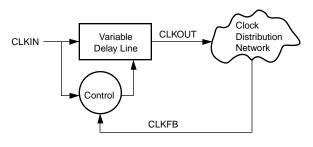

As shown in Figure 1, a DLL in its simplest form consists of a variable delay line and control logic. The delay line produces a delayed version of the input clock CLKIN. The clock distribution network routes the clock to all internal registers and to the clock feedback CLKFB pin. The control logic must sample the input clock as well as the feedback clock in order to adjust the delay line.

Delay lines can be built using a voltage controlled delay or as a series of discrete delay elements. For optimum performance the Virtex DLL uses a discrete digital delay line.

A DLL works by inserting delay between the input clock and the feedback clock until the two rising edges align, putting the two clocks 360 degrees out of phase (meaning they are in phase). After the edges from the input clock line up with the edges from the feedback clock, the DLL "locks." As long as the circuit is not evaluated until after the DLL locks, the two clocks have no discernible difference. Thus, the DLL output clock compensates for the delay in the clock distribution network, effectively removing the delay between the source clock and its loads.

x132\_01\_091799

Figure 1: Delay-Locked Loop Block Diagram

#### Phase-Locked Loop

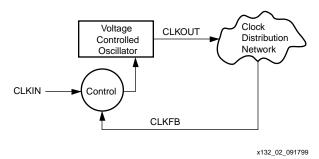

While designed for the same basic function, the PLL uses a different architecture to accomplish the task. As shown in Figure 2, the fundamental difference between the PLL and DLL is that instead of a delay line, the PLL uses a voltage controlled oscillator which generates a clock signal that approximates the input clock CLKIN. The control logic, consisting of a phase detector and filter, adjusts the oscillator frequency and phase to compensate for the clock distribution delay.

The PLL control logic compares the input clock to the feedback clock CLKFB and adjusts the oscillator clock until the rising edge of the input clock aligns with the feedback clock. The PLL then "locks."

Figure 2: Phase-Locked Loop Block Diagram

#### Implementation

Implementation of the DLL or PLL can be accomplished using either analog or digital circuitry; each holds its own advantages. An analog implementation with careful design can produce a

DLL or PLL with a finer timing resolution. Analog implementations can additionally take less silicon area.

Conversely, digital implementations offer advantages in noise sensitivity, lower power consumption and jitter performance. Digital implementations also provide the ability to stop the clock, facilitating power management. Analog implementations can require additional power supplies, require close control of the power supply, and pose problems in migration to new process technologies.

#### DLL vs. PLL

When it comes to choosing between a PLL or a DLL for a particular application, understand the differences in the architectures. The oscillator used in the PLL inherently introduces instability and an accumulation of phase error. This in turn degrades the performance of the PLL when attempting to compensate for the delay of the clock distribution network. Conversely, the unconditionally stable DLL architecture does not accumulate phase error.

For this reason, for delay compensation and clock conditioning, choose the DLL as the architecture. On the other hand, the PLL typically has an advantage when it comes to frequency synthesis.

#### Library DLL Symbols

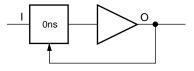

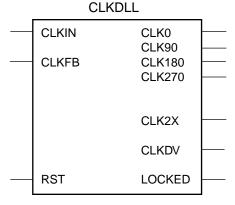

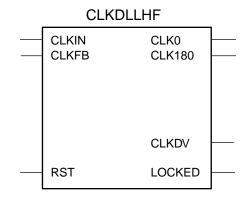

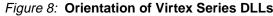

Figure 3 shows the simplified Xilinx library DLL macro symbol, BUFGDLL. This macro delivers a quick and efficient way to provide a system clock with zero propagation delay throughout the device. Figure 4 and Figure 5 show the two library DLL primitives. These symbols provide access to the complete set of DLL features when implementing more complex applications.

x132\_03\_092499

Figure 3: Simplified DLL Macro Symbol BUFGDLL

x132\_04\_012400

Figure 4: Standard DLL Symbol CLKDLL

x132\_05\_012400

## BUFGDLL Pin Descriptions

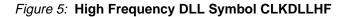

Use the BUFGDLL macro as the simplest way to provide zero propagation delay for a highfanout on-chip clock from an external input. This macro uses the IBUFG, CLKDLL and BUFG primitives to implement the most basic DLL application as shown in Figure 6.

This symbol does not provide access to the advanced clock domain controls or to the clock multiplication or clock division features of the DLL. This symbol also does not provide access to the RST, or LOCKED pins of the DLL. For access to these features, a designer must use the library DLL primitives described in the following sections.

xapp132\_06\_092099

Figure 6: BUFGDLL Schematic

#### Source Clock Input — I

The I pin provides the user source clock, the clock signal on which the DLL operates, to the BUFGDLL. For the BUFGDLL macro the source clock frequency must fall in the low frequency range as specified in the datasheet. The BUFGDLL requires an external signal source clock. Therefore, only an external input port can source the signal that drives the BUFGDLL I pin.

## Clock Output — O

The clock output pin O represents a delay-compensated version of the source clock (I) signal. This signal, sourced by a global clock buffer BUFG symbol, takes advantage of the dedicated global clock routing resources of the device.

The output clock has a 50-50 duty cycle unless you deactivate the duty cycle correction property.

## CLKDLL Primitive Pin Descriptions

The library CLKDLL primitives provide access to the complete set of DLL features needed when implementing more complex applications with the DLL.

## Source Clock Input — CLKIN

The CLKIN pin provides the user source clock (the clock signal on which the DLL operates) to the DLL. The CLKIN frequency must fall in the ranges specified in the datasheet. The clock input signal can be provided by one of the following:

- BUFG Internal global clock buffer

- IBUFG Global clock input buffer on the same edge of the device (top or bottom)

- IO\_LVDS\_DLL the pin adjacent to a global clock pin.

## Feedback Clock Input — CLKFB

The DLL requires a reference or feedback signal to provide the delay-compensated output. Connect only the CLK0 or CLK2X DLL outputs to the feedback clock input (CLKFB) pin to provide the necessary feedback to the DLL. The feedback clock input signal can be driven by an internal global clock buffer (BUFG), one of the global clock input buffers (IBUFG) on the same edge of the device (top or bottom), or IO\_LVDS\_DLL (the pin adjacent to a global clock pin.)

If an IBUFG sources the CLKFB pin, the following special rules apply.

- 1. An external input port must source the signal that drives the IBUFG input pin.

- The CLK2X output must feedback to the device if both the CLK0 and CLK2X outputs are driving off chip devices.

- 3. That signal must directly drive only OBUFs and nothing else.

- 4. These rules enable the software determine which DLL clock output sources the CLKFB pin.

## Reset Input - RST

When the reset pin RST activates, the LOCKED signal deactivates within four source clock cycles. The RST pin, active High, must either connect to a dynamic signal or tied to ground. As the DLL delay taps reset to zero, glitches can occur on the DLL clock output pins. Activation of the RST pin can also severely affect the duty cycle of the clock output pins. Furthermore, the DLL output clocks no longer de-skew with respect to one another. For these reasons, rarely use the reset pin unless reconfiguring the device or changing the input frequency.

## 2x Clock Output — CLK2X

The output pin CLK2X provides a frequency-doubled clock with an automatic 50/50 duty-cycle correction. Until the CLKDLL has achieved lock, the CLK2X output appears as a 1x version of the input clock with a 25/75 duty cycle. This behavior allows the DLL to lock on the correct edge with respect to source clock. This pin is not available on the CLKDLLHF primitive.

## Clock Divide Output — CLKDV

The clock divide output pin CLKDV provides a lower frequency version of the source clock. The CLKDV\_DIVIDE property controls CLKDV such that the source clock is divided by N where N is either 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

This feature provides automatic duty cycle correction such that the CLKDV output pin has a 50/50 duty cycle only for integer values of the division factor N.

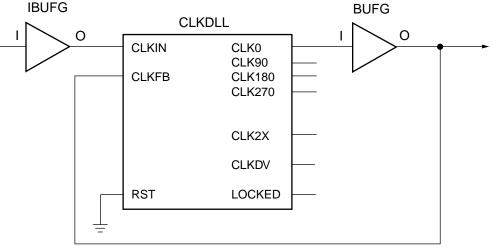

## 1x Clock Outputs — CLK[0|90|180|270]

The 1x clock output pin CLK0 represents a delay-compensated version of the source clock (CLKIN) signal. The CLKDLL primitive provides three phase-shifted versions of the CLK0 signal while CLKDLLHF provides only the 180 phase-shifted version. The relationship between phase shift and the corresponding period shift appears in Table 1.

The timing diagrams in Figure 7 illustrate the DLL clock output characteristics.

#### Table 1: Relationship of Phase-Shifted Output Clock to Period Shift

| Phase (degrees) | % Period Shift |  |

|-----------------|----------------|--|

| 0               | 0%             |  |

| 90              | 25%            |  |

| 180             | 50%            |  |

| 270             | 75%            |  |

Figure 7: DLL Output Characteristics

The DLL provides duty cycle correction on all 1x clock outputs such that all 1x clock outputs by default have a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (TRUE by default), controls this feature. In order to deactivate the DLL duty cycle correction, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL symbol. When duty cycle correction deactivates, the output clock has the same duty cycle as the source clock.

The DLL clock outputs can drive an OBUF, a BUFG, or they can route directly to destination clock pins. The DLL clock outputs can only drive the BUFGs that reside on the same edge (top or bottom).

## Locked Output — LOCKED

In order to achieve lock, the DLL may need to sample several thousand clock cycles. After the DLL achieves lock the LOCKED signal activates. The DLL timing parameter section of the datasheet provides estimates for locking times.

To guarantee that the system clock is established prior to the device "waking up," the DLL can delay the completion of the device configuration process until after the DLL locks. The STARTUP\_WAIT property activates this feature.

Until the LOCKED signal activates, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement. In particular the CLK2X output will appear as a 1x clock with a 25/75 duty cycle.

## **DLL Properties**

Properties provide access to some of the Virtex series DLL features, (for example, clock division and duty cycle correction).

## **Duty Cycle Correction Property**

The 1x clock outputs, CLK0, CLK90, CLK180, and CLK270, use the duty cycle corrected default such that they exhibit a 50/50 duty cycle. The DUTY\_CYCLE\_CORRECTION property (by default TRUE) controls this feature. In order to deactivate the DLL duty cycle correction for the 1x clock outputs, attach the DUTY\_CYCLE\_CORRECTION=FALSE property to the DLL symbol. When duty cycle correction deactivates, the output clock has the same duty cycle as the source clock.

## **Clock Divide Property**

The CLKDV\_DIVIDE property specifies how the signal on the CLKDV pin is frequency divided with respect to the CLK0 pin. The values allowed for this property are 1.5, 2, 2.5, 3, 4, 5, 8, or 16; the default value is 2.

## **Startup Delay Property**

This property, STARTUP\_WAIT, takes on a value of TRUE or FALSE (the default value). When TRUE the device configuration DONE signal waits until the DLL locks before going to High.

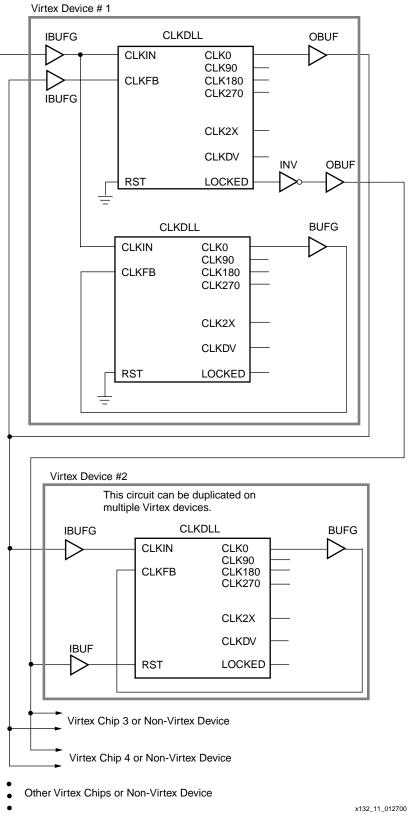

## **Virtex Series DLL Location Constraints**

The DLLs are distributed such that there is one DLL in each corner of the device. The location constraint LOC, attached to the DLL symbol with the numeric identifier 0, 1, 2, or 3, controls DLL location. The orientation of the four DLLs and their corresponding clock resources appears in Figure 8.

The LOC property uses the following form.

LOC = DLL2

For the Virtex-E and the Virtex-E Extended Memory (Virtex-EM) DLL locations see "DLL Location Constraints" on page 14.

| GCLKPAD3   |                   |

|------------|-------------------|

| DLL3       | DLL2              |

| GCLKBUF3 ∇ | $\nabla$ GCLKBUF2 |

|            |                   |

| GCLKBUF1 △ |                   |

| DLL1       | DLL0              |

| GCLKPAD1   | GCLKPAD0          |

|            | x132_08_031400    |

## Design Considerations

Use the following design considerations to avoid pitfalls and improve success designing with Xilinx devices.

## Input Clock

The output clock signal of a DLL, essentially a delayed version of the input clock signal, reflects any instability on the input clock in the output waveform. For this reason the quality of the DLL input clock relates directly to the quality of the output clock waveforms generated by the DLL. The DLL input clock requirements are specified in the datasheet.

In most systems a crystal oscillator generates the system clock. The DLL can be used with any commercially available quartz crystal oscillator. For example, most crystal oscillators produce an output waveform with a frequency tolerance of 100 PPM, meaning 0.01 percent change in the clock period. The DLL operates reliably on an input waveform with a frequency drift of up to 1 ns — orders of magnitude in excess of that needed to support any crystal oscillator in the industry. However, the cycle-to-cycle jitter must be kept to less than 300 ps in the low frequencies and 150 ps for the high frequencies.

## **Input Clock Changes**

Changing the period of the input clock beyond the maximum drift amount requires a manual reset of the CLKDLL. Failure to reset the DLL will produce an unreliable lock signal and output clock.

It is possible to stop the input clock with little impact to the DLL. Stopping the clock should be limited to less than 100 ms to keep device cooling to a minimum. The clock should be stopped during a Low phase, and when restored the full High period should be seen. During this time LOCKED will stay High and remain High when the clock is restored.

When the clock is stopped, one to four more clocks will still be observed as the delay line is flushed. When the clock is restarted, the output clocks will not be observed for one to four clocks as the delay line is filled. The most common case will be two or three clocks.

In a similar manner, a phase shift of the input clock is also possible. The phase shift will propagate to the output one to four clocks after the original shift, with no disruption to the CLKDLL control.

## **Output Clocks**

As mentioned earlier in the DLL pin descriptions, some restrictions apply regarding the connectivity of the output pins. The DLL clock outputs can drive an OBUF, a global clock buffer BUFG, or they can route directly to destination clock pins. The only BUFGs that the DLL clock outputs can drive are the two on the same edge of the device (top or bottom).

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

## Useful Application Examples

The Virtex DLL can be used in a variety of creative and useful applications. The following examples show some of the more common applications. The Verilog and VHDL example files are available at:

ftp://ftp.xilinx.com/pub/applications/xapp/xapp132.zip

## Standard Usage

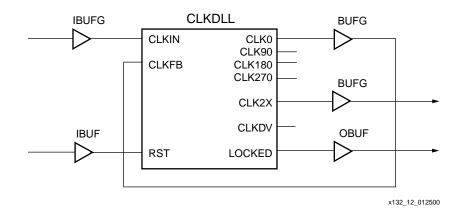

The circuit shown in Figure 9 resembles the BUFGDLL macro implemented in such a way as to provide access to the RST and LOCKED pins of the CLKDLL.

The dll\_standard files in the xapp132.zip file show the VHDL and Verilog implementation of this circuit.

x132\_09\_012500

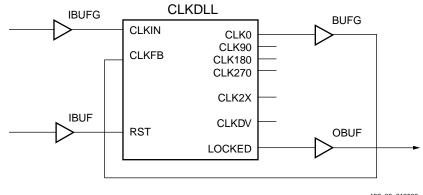

## **Board Level De-skew of Multiple Non-Virtex Devices**

The circuit shown in Figure 10 can be used to de-skew a system clock between a Virtex chip and other non-Virtex chips on the same board. This application is commonly used when the Virtex device is used in conjunction with other standard products such as SRAM or DRAM devices. While designing the board level route, ensure that the return net delay to the source equals the delay to the other chips involved.

Figure 10: DLL De-skew of Board Level Clock

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

The dll\_mirror\_1 files in the xapp132.zip file show the VHDL and Verilog implementation of this circuit.

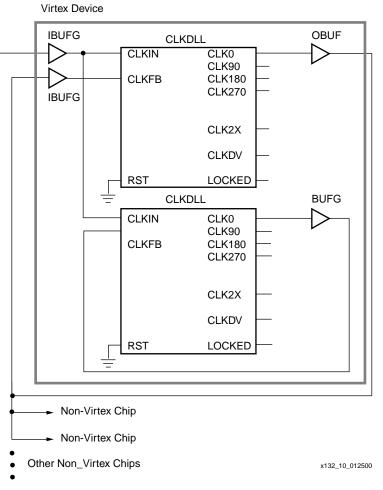

#### **Board Level De-skew of Multiple Virtex Devices**

The circuit shown in Figure 11 can be used to de-skew a system clock between multiple Virtex chips on the same board. While designing the board level route, ensure that the return net delay to the source equals the delay to the other chips involved.

Do not use the DLL output clock signals until after activation of the LOCKED signal. Prior to the activation of the LOCKED signal, the DLL output clocks are not valid and can exhibit glitches, spikes, or other spurious movement.

The clock mirroring scheme should be used for systems (such as PCI) that specify a loading/ fanout limit on the system clock. This scheme can also be used when the clock source in a single board system is not capable of driving all the loads on the board.

The dll\_mirror\_2 files in the xapp132.zip file show the VHDL and Verilog implementation of this circuit.

Figure 11: DLL De-skew of Board Level Clock

#### **De-skew of Clock and Its 2x Multiple**

The circuit shown in Figure 12 implements a 2x clock multiplier and also uses the CLK0 clock output with zero ns skew between registers on the same chip. A clock divider circuit could alternatively be implemented using similar connections.

Because any single DLL can only access at most two BUFGs, any additional output clock signals must be routed from the DLL in this example on the high speed backbone routing.

The dll\_2x files in the xapp132.zip file show the VHDL and Verilog implementation of this circuit.

Figure 12: DLL De-skew of Clock and 2x Multiple

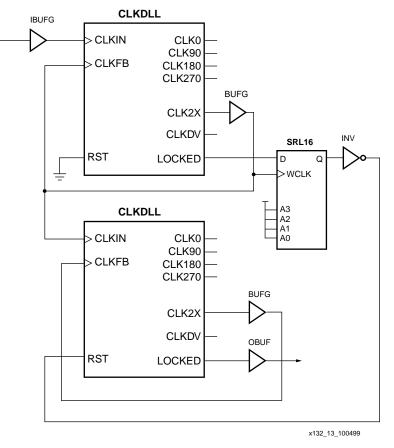

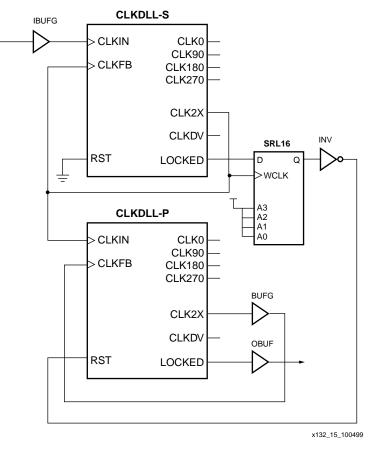

## **Generating a 4x Clock**

By connecting two DLL circuits each implementing a 2x clock multiplier in series as shown in Figure 13, a 4x clock multiply can be implemented with zero ns skew between registers in the same device.

If other clock output is needed, the clock could access a BUFG only if the DLLs are constrained to exist on opposite edges (Top or Bottom) of the device.

When using this circuit it is vital to use the SRL16 cell to reset the second DLL after the initial chip reset. If this is not done, the second DLL may not recognize the change of frequencies from when the input changes from a 1x (25/75) waveform to a 2x (50/50) waveform.

The dll\_4x files in the xapp132.zip file show the VHDL and Verilog implementation of this circuit.

Figure 13: DLL Generation of 4x Clock

## Appendix A DLLs in Virtex-E and Virtex-E Extended Memory (Virtex-EM) devices

Differences between the Virtex family and the Virtex-E and Virtex-EM DLLs are described in this appendix. The basic operations of the DLLs are the same in all the families. For example, the schemes for board level de-skew of multiple non-Virtex devices, board level de-skew of multiple Virtex devices, de-skew of clock and its 2x multiple, or generating a 4x clock remains the same. Only the number of DLLs and their connectivity has changed in the Virtex-E and Virtex-EM devices.

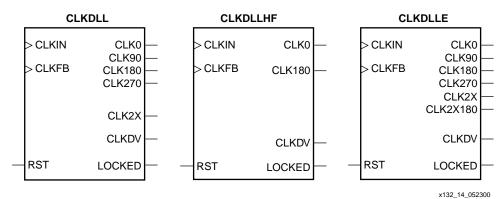

#### **DLL Macros**

In the Virtex series there are two DLL macros (CLKDLL, CLKDLLHF) common to Virtex, Virtex-E and Virtex-EM devices. The Virtex-E and Virtex-EM device families have an additional CLKDLLE macro with an additional CLK2X180 output (Figure 14).

Figure 14: DLL Macros

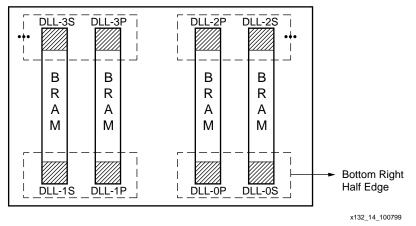

## **DLL Location Constraints**

Figure 15 shows the four additional DLLs in the Virtex-E and Virtex-EM devices. A total of eight DLLs are available per Virtex-E or Virtex-EM device. These DLLs are located in silicon, at the top and bottom of the two innermost block SelectRAM+ columns.

The location constraint LOC, attached to the DLL symbol with the identifier DLL0S, DLL0P, DLL1S, DLL1P, DLL2S, DLL2P, DLL3S, or DLL3P controls the DLL location.

The LOC property uses the following form:

LOC = DLL0P

Figure 15: DLLs in Virtex-E and Virtex-EM Devices

#### 4x Clock

To generate the 4x clock shown in Figure 16, two DLLs located in the same half-edge (top-left, top-right, bottom-right, bottom-left) can be connected together, without using a BUFG between the CLKDLLs. The entire Virtex series (Virtex, Virtex-E, and Virtex-EM) has four clock networks available for internal de-skewing of the clock. Each of the eight Virtex-E or Virtex-EM DLLs have access to two of the four clock networks. Although all the DLLs can be used for internal de-skewing, the presence of two BUFGs on the top and two on the bottom indicate that only two of the four DLLs on the top (and two of the four DLLs on the bottom) can be used for this purpose.

Figure 16: DLL Generation of 4x Clock in Virtex-E and Virtex-EM Devices

## **DLL Input Pins**

There are four additional input pins (IO\_LVDS\_DLL) that can be used as inputs to the DLLs. This makes a total of eight usable inputs for DLLs in the Virtex-E and Virtex-EM families.

The dll\_4x files in the XAPP132.zip file show the DLL implementation in Verilog for Virtex-E devices. These files can be found at:

ftp://ftp.xilinx.com/pub/applications/xapp/xapp132.zip

## Revision History

The following table shows the revision history for this document.

| Date     | Version | Revision                                                          |

|----------|---------|-------------------------------------------------------------------|

| 10/21/98 | 1.31    | Initial Release                                                   |

| 10/11/99 | 1.4     | Included Virtex-E devices in a new Appendix A.                    |

| 1/27/00  | 2.0     | Reformatted application note to a new template.                   |

| 3/20/00  | 2.1     | Corrected Figure 8. Added Virtex-E Extended Memory to Appendix A. |

| 5/23/00  | 2.2     | Updated pages 5 and 14. Added Figure 14.                          |

| 9/20/00  | 2.3     | Minor update to text on page 5.                                   |