# Use Multiple Configuration Bitstreams to Enhance Your Next FPGA-Based Design

Silver Engineering Inc. used multiple bitstreams to reduce test time and to provide versatility in their new VME Command Encoder Unit.

by Dennis Silver President of Silver Engineering Inc, VP of Configurator Inc. Silver Engineering Inc, and Configurator Inc. silver@fpgaconfigurator.com Figure 1 - VCEU card with XCV400 FPGA and Configurator

44

Most of us who have used fuse-based FPGAs really appreciate the forgiveness of reprogrammable RAM-based FPGA designs. But are you actually taking full advantage of the possibilities?

At Silver Engineering Inc., we recently devel-

oped a VME (VersaModule Eurocard) bus card specifically created for future field upgrades and design reuse. The VCEU (VME Command Encoder Unit) card (Figure 1) is primarily used as a ground-support satellite uplink/downlink (command/telemetry) processing card.

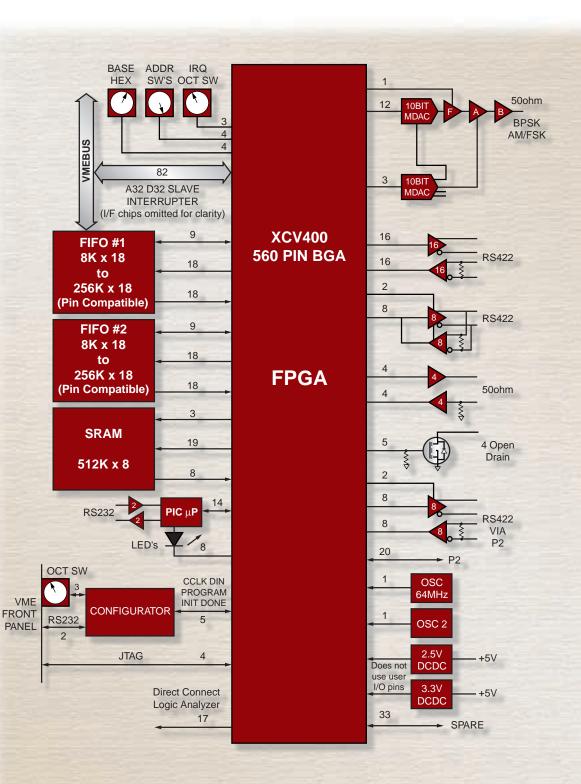

The VCEU is capable of generating both analog BPSK (Bi-Phase Shift Keyed) and AM/FSK (Amplitude Modulated/Frequency Shift Keyed) command formats. It incorporates a variety of digital I/O and on-card resources, allowing the card to emulate/test various spacecraft components during integration and test phases. Figure 2 illustrates the interface to the XCV400 on the VCEU card.

In this article, I will show how you can use multiple bitstreams to add extra value to your designs with minimal additional cost. To take full advantage of RAM-based FPGAs, consider the following three opportunities:

- Diagnostic/test bitfiles To simplify board bring-up and test, you can implement multiple simple test designs. This accelerates hardware debugging, because the test hardware does not interfere with the system application hardware.

- Multiple bitfiles for different functionality or for reuse – You can use multiple bitstreams to perform com-

pletely different functions within a single card design. Moreover, these designs will not interfere with each other, and you can utilize the entire FPGA for each design.

• Easy field upgrades — Most engineers have had the experience of having to fix bugs or

add features when a design is in the field. RAM-based FPGAs give you the flexibility of re-programmability so, with some planning, you may not have to make board modifications. Updating your design can be as easy as e-mailing a new bitfile.

### Figure 2 - VCEU FPGA interfaces

## Multiple Bitstreams Using the Configurator Module

The VCEU card incorporates a device called the Configurator. (See www.fpgacon-figurator.com for details.) We chose to use

the Configurator module because it provides a prepackaged solution to storing multiple bitstreams. The Configurator programs up to eight FPGAs in parallel and can supply up to eight configuration bitfiles for each FPGA. The bitfiles are stored in reprogrammable flash memory. The size of the FPGAs and the number of different bitstreams for each are limited by the flash size.

The Configurator has an embedded serial port that can be utilized for field upgrades.

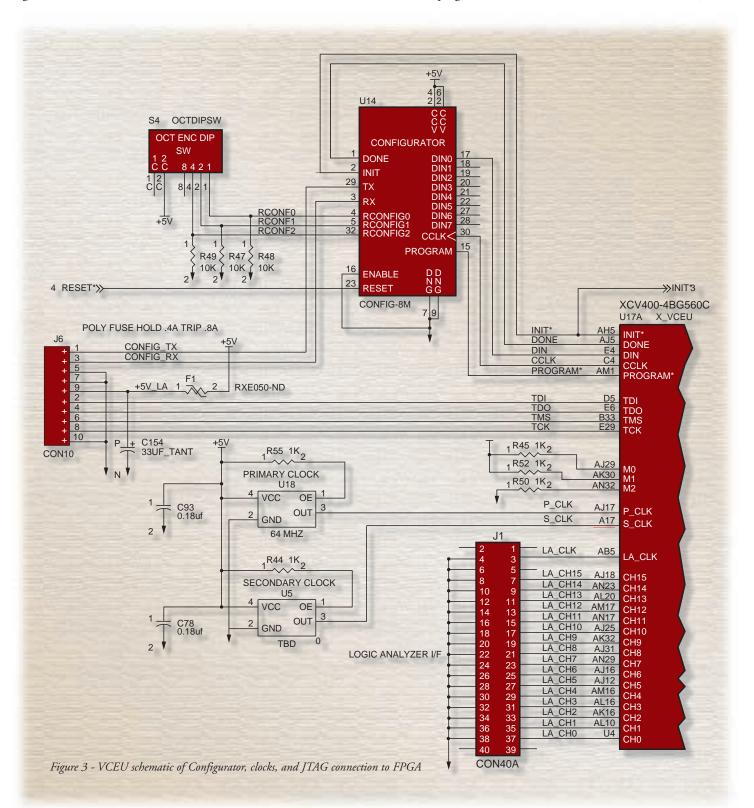

The front panel of the VCEU card has an octal encoded rotary switch that connects to the Configurator and selects one of eight possible bitstreams to be loaded into the XCV400. In addition, the Configurator module's RS232 signals are connected to the VME front panel for easy downloading of new bitstreams from a field service laptop or any other device with a serial port. The VCEU card schematic of the Configurator interface is shown in Figure 3.

### Using Diagnostic/Test Bitfiles

Traditionally, we have tested circuit cards with only the card's main purpose in mind. In developing the VCEU, we took full advantage of multiple bitstream functionality for board bring-up and test.

A card that generates satellite uplink commands and receives downlink telemetry requires a lot of custom test equipment. To simplify basic testing of the VCEU card, we downloaded a series of diagnostic FPGA bitfiles into the Configurator module. The first set of diagnostic hardware files verified basic functions such as the front panel LEDs, hex rotary switches, and clocks feeding the FPGA. Once we had the basic functions confirmed, we used the LEDs switches as control and pass/fail indicators in complex diagnostic hardware tests. For example, we tested the SRAM, two large FIFOs, and drove test patterns for the D/A converters and other components. After all the diagnostic tests were completed, we then downloaded the "real" bitfile.

We retained all the previously used diagnostic bitfiles within the Configurator module on the VCEU card. To gain the maximum test coverage using diagnostic bitfiles, we connected most of the board's hardware to the FPGA. Additionally, we took some care to create complete signal paths so that signals driven out of the FPGA though the board hardware would be looped back into the FPGA for verification of signal integrity. By installing external loopback cables, we were able to check digital I/Os with a simple walking pulse test.

Along with diagnostic configuration files, we developed a configuration file for a built-in self-test. In the case of the selftest, which can happen at system powerup or on command, care must be taken so that the self-test does not interfere or conflict with external hardware from the board under test. This limits the self-test to testing only a portion of the board, but if you are creative with your board design (as we were), the only untested logic will be the input and output drivers.

### **Multiple Functions for the Same Board**

We specifically designed the VCEU board to allow different functions to be implemented in the future using the same physical hardware. For example, a future requirement might include the capability of driving signals out differentially. Because we incorporated differential drivers on the board along with the Xilinx FPGA, we will be able to support this new requirement without a costly board re-layout. The new design will just become another configuration bitstream selected by the front panel rotary switch.

To avoid the risk of premature obsolescence, when you are designing a new circuit board, ask yourself: "What other application might this board be required to do?" Then do a cost/benefit analysis of how much additional hardware would be needed on board to support the future scenarios. Remember, you don't necessarily have to have this additional hardware populated on the board. It might only be a matter of having enough board space and paying for a few extra board vias (plated through-holes in a printed circuit board).

### **Easy Field Upgrades**

Due to the often remote geographical locations of satellite ground stations, it is imperative that the FPGA can be easily updated to support feature additions or bug fixes. Therefore, the front panel of the VME card has a small connector that links to the Configurator module's serial port. When a new FPGA design is produced, the \*.bit file is emailed to the designated field support personnel. Any on-site personnel can then simply connect the COM port of a laptop PC to the VME card front panel connector and download the new configuration file. The only disruption in service is the period of time that the FPGA is being reconfigured.

### Conclusion

With some careful planning, you can optimize your designs for now — and for the future — by using devices like the Configurator and reprogrammable Xilinx FPGAs. Multiple configuration files offer on-board support for diagnostic/testing, multiple functions utilizing the same card, and easy field upgrades. Make yourself a hero in your next design and do some "reconfigurable computing."

# About Silver Engineering, Inc.

Silver Engineering Inc. (SEI) specializes in the design of hardware for spacecraft flight and ground-support systems utilizing Xilinx FPGAs.

Dennis Silver is president of Silver Engineering Inc. and vice president of Configurator Inc. For more information, visit

www.silvereng.com and www.fpgaconfigurator.com.