# Chapter 1

# **Timing Models**

# Summary

The following topics are covered in this chapter:

- CLB / Slice Timing Model

- Block SelectRAM Timing Model

- Embedded Multiplier Timing Model

- IOB Timing Model

- Pin-to-Pin Timing Model

- Digital Clock Manager Timing Model

### Introduction

Due to the large size and complexity of Virtex-II FPGAs, understanding the timing associated with the various paths and functional elements has become a difficult and important problem. Although it is not necessary to understand the various timing parameters in order to implement most designs using Xilinx, Inc. software, a thorough timing model can assist advanced users in analyzing critical paths, or planning speed-sensitive designs.

The Timing Model chapter is broken up into five sections consisting of three basic components:

- Functional Element Diagram basic architectural schematic illustrating pins and connections.

- Timing Parameters <u>Virtex-II Data Sheet</u> timing parameter definitions.

- Timing Diagram illustrates functional element timing parameters relative to each other.

This chapter was written with the Xilinx Timing Analyzer software (TRCE) in mind. All pin names, parameter names, and paths are consistent with Post Route Timing and Pre-Route Static Timing reports. Use the models in this chapter in conjunction with both the Timing Analyzer software and the section on switching characteristics in the <u>Virtex-II Data</u> <u>Sheet</u>. Most of the timing parameters found in the section on switching characteristics are described in this chapter.

# **CLB / Slice Timing Model**

### Introduction

This section describes all timing parameters reported in the Virtex-II Data Sheet that are associated with slices and Configurable Logic Blocks (CLBs). It consists of three parts corresponding to their respective (switching characteristics) sections in the data sheet:

- General Slice Timing Model and Parameters (CLB Switching Characteristics)

- Slice Distributed RAM Timing Model and Parameters (CLB Distributed RAM Switching Characteristics)

- Slice SRL Timing Model and Parameters (CLB SRL Switching Characteristics)

### General Slice Timing Model and Parameters

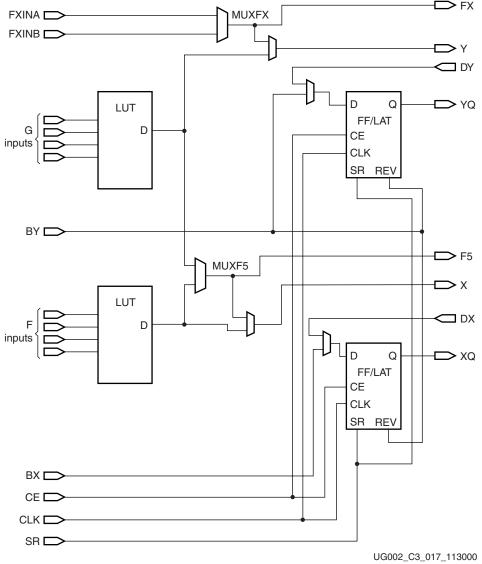

Figure 1-1 illustrates the details of a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

# **Timing Parameters**

| Parameter                                                                                              | Function                                       | Control<br>Signal | Description                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Combinatorial                                                                                          | Delays                                         |                   |                                                                                                                                                                               |

| T <sub>ILO</sub>                                                                                       | F/G inputs to X/Y outputs                      |                   | Propagation delay from the F/G inputs of<br>the slice, through the look-up tables<br>(LUTs), to the X/Y outputs of the slice.                                                 |

| T <sub>IF5</sub>                                                                                       | F/G inputs to F5<br>output                     |                   | Propagation delay from the F/G inputs of the slice, through the LUTs and MUXF5 to the F5 output of the slice.                                                                 |

| T <sub>IF5X</sub>                                                                                      | F/G inputs to X<br>output                      |                   | Propagation delay from the F/G inputs of the slice, through the LUTs and MUXF5 to the X output of the slice.                                                                  |

| T <sub>IFXY</sub>                                                                                      | FXINA/FXINB<br>inputs to Y<br>output           |                   | Propagation delay from the<br>FXINA/FXINB inputs, through MUXFX<br>to the Y output of the slice.                                                                              |

| T <sub>IFNCTL</sub>                                                                                    | Transparent<br>Latch input to<br>XQ/YQ outputs |                   | Incremental delay through a transparent latch to XQ/YQ outputs.                                                                                                               |

| Sequential Del                                                                                         | ays                                            |                   | ·                                                                                                                                                                             |

| T <sub>CKO</sub>                                                                                       | FF Clock (CLK)<br>to XQ/YQ<br>outputs          |                   | Time after the clock that data is stable at the XQ/YQ outputs of the slice sequential elements (configured as a flip-flop).                                                   |

| T <sub>CKLO</sub>                                                                                      | Latch Clock<br>(CLK) to<br>XQ/YQ outputs       |                   | Time after the clock that data is stable at the XQ/YQ outputs of the slice sequential elements (configured as a latch).                                                       |

| Setup and Hole                                                                                         | d for Slice Sequent                            | tial Elements     | S                                                                                                                                                                             |

| T <sub>xxCK</sub> = Setup time (before clock edge)<br>T <sub>CKxx</sub> = Hold time (after clock edge) |                                                |                   | The following descriptions are for setup times only.                                                                                                                          |

| T <sub>DICK</sub> /T <sub>CKDI</sub>                                                                   | BX/BY inputs                                   |                   | Time before Clock (CLK) that data from<br>the BX or BY inputs of the slice must be<br>stable at the D-input of the slice sequential<br>elements (configured as a flip-flop).  |

| T <sub>DYCK</sub> /T <sub>CKDY</sub>                                                                   | DY input                                       |                   | Time before Clock (CLK) that data from<br>the DY input of the slice must be stable at<br>the D-input of the slice sequential<br>elements (configured as a flip-flop).         |

| T <sub>DXCK</sub> /T <sub>CKDX</sub>                                                                   | DX input                                       |                   | Time before Clock (CLK) that data from<br>the DX input of the slice must be stable at<br>the D-input of the slice sequential<br>elements (configured as a flip-flop).         |

| T <sub>CECK</sub> /T <sub>CKCE</sub>                                                                   | CE input                                       |                   | Time before Clock (CLK) that the CE<br>(Clock Enable) input of the slice must be<br>stable at the CE-input of the slice sequen-<br>tial elements (configured as a flip-flop). |

| Parameter                          | Function     | Control<br>Signal | Description                                                                                                                                                                                                             |

|------------------------------------|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RCK</sub> /T <sub>CKR</sub> | SR/BY inputs |                   | Time before CLK that the SR (Set/Reset)<br>and the BY (Rev) inputs of the slice must<br>be stable at the SR/Rev-inputs of the slice<br>sequential elements (configured as a flip-<br>flop). Synchronous set/reset only. |

| Clock CLK                          |              |                   |                                                                                                                                                                                                                         |

| T <sub>CH</sub>                    |              |                   | Minimum Pulse Width, High.                                                                                                                                                                                              |

| T <sub>CL</sub>                    |              |                   | Minimum Pulse Width, Low.                                                                                                                                                                                               |

| Set/Reset                          |              |                   |                                                                                                                                                                                                                         |

| T <sub>RPW</sub>                   |              |                   | Minimum Pulse Width for the SR<br>(Set/Reset) and BY (Rev) pins.                                                                                                                                                        |

| T <sub>RQ</sub>                    |              |                   | Propagation delay for an asynchronous<br>Set/Reset of the slice sequential elements.<br>From SR/BY inputs to XQ/YQ outputs.                                                                                             |

| F <sub>TOG</sub>                   |              |                   | Toggle Frequency - Maximum Frequency that a CLB flip-flop can be clocked: $1/(T_{CH}+T_{CL})$                                                                                                                           |

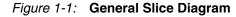

Figure 1-2 illustrates general timing characteristics of a Virtex-II slice.

Figure 1-2: General Slice Timing Diagram

- At time T<sub>CECK</sub> before Clock Event 1, the Clock-Enable signal becomes valid-high at the CE input of the slice register.

- At time T<sub>DYCK</sub> before Clock Event 1, data from the DY input becomes valid-high at the D input of the slice register and is reflected on the YQ pin at time T<sub>CKO</sub> after Clock Event 1\*.

- At time T<sub>RCK</sub> before Clock Event 3, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting the slice register, and this is reflected on the YQ pin at time T<sub>CKO</sub> after Clock Event 3.

\* NOTE: In most cases software uses the DX/DY inputs to route data to the slice registers when at all possible. This is the fastest path to the slice registers and saves other slice routing resources.

1

## Slice Distributed RAM Timing Model and Parameters

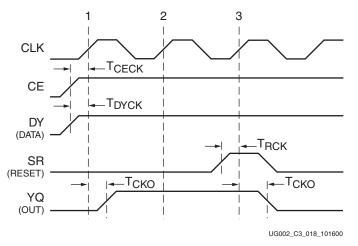

Figure 1-3 illustrates the details of distributed RAM implemented in a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

Figure 1-3: Slice Distributed RAM Diagram

## **Timing Parameters**

| Parameter                          | Function                                             | Control<br>Signal | Description                                                                                                                                            |  |  |  |

|------------------------------------|------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sequential D                       | <b>Delays for Slice LUT C</b>                        | Configured a      | s RAM (Distributed RAM)                                                                                                                                |  |  |  |

| T <sub>SHCKO16</sub>               | CLK to X/Y outputs<br>(WE active) in 16x1<br>mode    |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM (in 16x1 mode) is stable on the X/Y outputs of the slice. |  |  |  |

| T <sub>SHCKO32</sub>               | CLK to X/Y outputs<br>(WE active) in 32x1<br>mode    |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM (in 32x1 mode) is stable on the X/Y outputs of the slice. |  |  |  |

| T <sub>SHCKOF5</sub>               | CLK to F5 output<br>(WE active)                      |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the distributed RAM is stable on the F5 output of the slice.                  |  |  |  |

| Setup and H                        | old for Slice LUT Con                                | figured as R      | AM (Distributed RAM)                                                                                                                                   |  |  |  |

|                                    | p time (before clock edg<br>d time (after clock edge |                   | The following descriptions are for setup times only.                                                                                                   |  |  |  |

| T <sub>DS</sub> /T <sub>DH</sub>   | BX/BY Data inputs<br>(DI)                            |                   | Time before the clock that data must be<br>stable at the DI input of the slice LUT<br>(configured as RAM), via the slice<br>BX/BY inputs.              |  |  |  |

| $T_{AS}/T_{AH}$                    | F/G Address inputs                                   |                   | Time before the clock that address signals must be stable at the F/G inputs of the slice LUT (configured as RAM).                                      |  |  |  |

| T <sub>WES</sub> /T <sub>WEH</sub> | WE input (SR)                                        |                   | Time before the clock that the Write<br>Enable signal must be stable at the WE<br>input of the slice LUT (configured as<br>RAM).                       |  |  |  |

| Clock CLK                          | Clock CLK                                            |                   |                                                                                                                                                        |  |  |  |

| T <sub>WPH</sub>                   |                                                      |                   | Minimum Pulse Width, High (for a Distributed RAM clock).                                                                                               |  |  |  |

| T <sub>WPL</sub>                   |                                                      |                   | Minimum Pulse Width, Low (for a Distributed RAM clock).                                                                                                |  |  |  |

| T <sub>WC</sub>                    |                                                      |                   | Minimum clock period to meet address write cycle time.                                                                                                 |  |  |  |

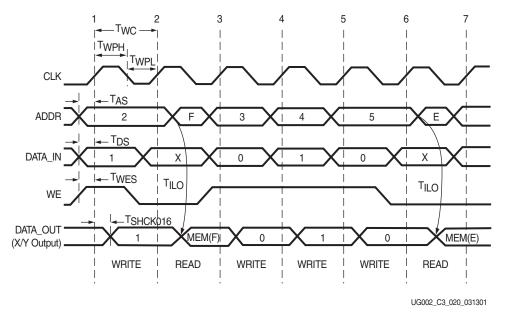

Figure 1-4 illustrates the timing characteristics of a 16-bit distributed RAM implemented in a Virtex-II slice (LUT configured as RAM).

Figure 1-4: Slice Distributed RAM Timing Diagram

### Clock Event 1: WRITE Operation

During a WRITE operation, the contents of the memory at the address on the ADDR inputs is changed. The data written to this memory location is reflected on the X/Y outputs synchronously.

- At time T<sub>WES</sub> before Clock Event 1, the Write Enable signal (WE) becomes valid-high, enabling the RAM for the following WRITE operation.

- At time T<sub>AS</sub> before Clock Event 1, the address (2) becomes valid at the F/G inputs of the RAM.

- At time T<sub>DS</sub> before Clock Event 1, the DATA becomes valid (1) at the DI input of the RAM and is reflected on the X/Y output at time T<sub>SHCKO16</sub> after Clock Event 1.

### **Clock Event 2: READ Operation**

All READ operations are asynchronous in distributed RAM. As long as write-enable (WE) is Low, the address bus can be asserted at any time, and the contents of the RAM at that address are reflected on the X/Y outputs after a delay of length  $T_{ILO}$  (propagation delay through a LUT). Note that the Address (F) is asserted *after* Clock Event 2, and that the contents of the RAM at that location are reflected on the output after a delay of length  $T_{ILO}$ .

# Slice SRL Timing Model and Parameters

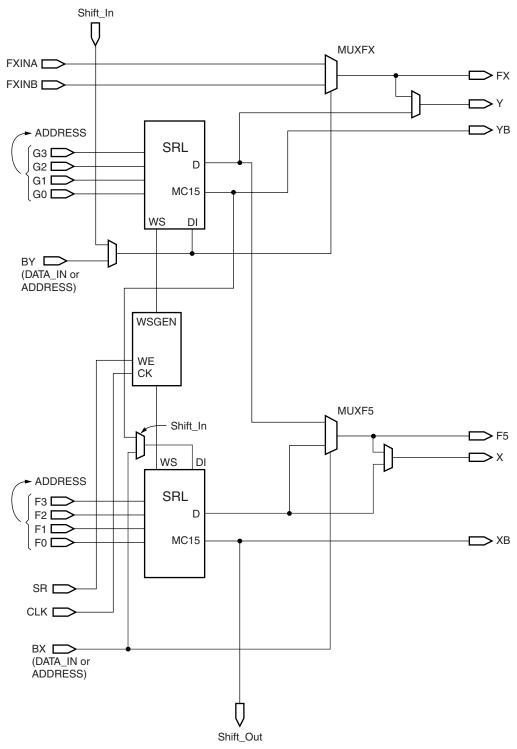

Figure 1-5 illustrates shift register implementation in a Virtex-II slice.

Note: Some elements of the Virtex-II slice have been omitted for clarity. Only the elements relevant to the timing paths described in this section are shown.

UG002\_C3\_021\_113000

### **Timing Parameters**

| Parameter                                  | Function                                         | Control<br>Signal | Description                                                                                                                               |  |  |

|--------------------------------------------|--------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sequential I                               | Delays for Slice LUT                             | [ Configur        | ed as SRL (Select Shift Register)                                                                                                         |  |  |

| T <sub>REG</sub>                           | CLK to<br>X/Y outputs                            |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the X/Y outputs of the slice.               |  |  |

| T <sub>CKSH</sub>                          | CLK to Shiftout                                  |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the Shiftout or XB/YB outputs of the slice. |  |  |

| T <sub>REGF5</sub>                         | CLK to F5 output                                 |                   | Time after the Clock (CLK) of a WRITE operation that the data written to the SRL is stable on the F5 output of the slice.                 |  |  |

| Setup/Hold                                 | for Slice LUT Confi                              | gured as S        | RL (Select Shift Register)                                                                                                                |  |  |

|                                            | up time (before clock<br>ld time (after clock eo |                   | The following descriptions are for setup times only.                                                                                      |  |  |

| T <sub>SRLDS</sub> /<br>T <sub>SRLDH</sub> | BX/BY Data<br>inputs (DI)                        |                   | Time before the clock that data must be stable<br>at the DI input of the slice LUT (configured as<br>SRL), via the slice BX/BY inputs.    |  |  |

| T <sub>WSS</sub> /T <sub>WSH</sub>         | CE input (WE)                                    |                   | Time before the clock that the Write Enable<br>signal must be stable at the WE input of the<br>slice LUT (configured as SRL).             |  |  |

| Clock CLK                                  | Clock CLK                                        |                   |                                                                                                                                           |  |  |

| T <sub>SRPH</sub>                          |                                                  |                   | Minimum Pulse Width, High (for an SRL clock).                                                                                             |  |  |

| T <sub>SRPL</sub>                          |                                                  |                   | Minimum Pulse Width, Low (for an SRL clock).                                                                                              |  |  |

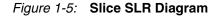

Figure 1-6 illustrates the timing characteristics of a 16-bit shift register implemented in a Virtex-II slice (LUT configured as SRL).

Figure 1-6: Slice SLR Timing Diagram

### Clock Event 1: Shift\_In

During a WRITE (Shift\_In) operation, the single-bit content of the register at the address on the ADDR inputs is changed, as data is shifted through the SRL. The data written to this register is reflected on the X/Y outputs synchronously, if the address is unchanged during the clock event. If the ADDR inputs are changed during a clock event, the value of the data at the addressable output (D) is invalid.

- At time T<sub>WSS</sub> before Clock Event 1, the Write Enable signal (SR) becomes valid-high, enabling the SRL for the WRITE operation that follows.

- At time T<sub>SRLDS</sub> before Clock Event 1 the data becomes valid (0) at the DI input of the SRL and is reflected on the X/Y output after a delay of length T<sub>REG</sub> after Clock Event 1\*.

\* Note: Since the address 0 is specified at Clock Event 1, the data on the DI input is reflected at the D output, because it is written to Register 0.

#### Clock Event 2: Shift\_In

At time T<sub>SRLDS</sub> before Clock Event 2, the data becomes valid (1) at the DI input of the SRL and is reflected on the X/Y output after a delay of length T<sub>REG</sub> after Clock Event 2\*.

\* Note: Since the address 0 is still specified at Clock Event 2, the data on the DI input is reflected at the D output, because it is written to Register 0.

### Clock Event 3: Shift\_In / Addressable (Asynchronous) READ

All READ operations are asynchronous. If the address is changed (between clock events), the contents of the register at that address are reflected at the addressable output (X/Y outputs) after a delay of length  $T_{ILO}$  (propagation delay through a LUT).

- At time T<sub>SRLDS</sub> before Clock Event 3 the Data becomes valid (1) at the DI input of the SRL, and is reflected on the X/Y output T<sub>REG</sub> time after Clock Event 3.

- Notice that the address is changed (from 0 to 2) some time after Clock Event 3. The value stored in Register 2 at this time is a 0 (in this example, this was the first data shifted in), and it is reflected on the X/Y output after a delay of length T<sub>ILO</sub>.

### Clock Event 16: MSB (Most Significant Bit) Changes

• At time T<sub>REGXB</sub> after Clock Event 16, the first bit shifted into the SRL becomes valid (logical 0 in this case) on the XB output of the slice via the MC15 output of the LUT (SRL).

# **Block SelectRAM Timing Model**

### Introduction

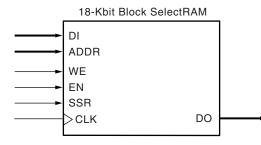

This section describes the timing parameters associated with the block SelectRAM (illustrated in Figure 1-7) in Virtex-II FPGA devices. This section is intended to be used with the section on switching characteristics in the <u>Virtex-II Data Sheet</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the switching characteristics section in the <u>Virtex-II Data Sheet</u>.

DS031\_10\_100300

Figure 1-7: Block SelectRAM Block Diagram

## **Timing Parameters**

| Parameter                                   | Function Control Signal                     |              | Description                                                                                                   |  |  |  |  |

|---------------------------------------------|---------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Setup and Hold F                            | Setup and Hold Relative to Clock (CLK)      |              |                                                                                                               |  |  |  |  |

| $T_{BxCK}$ = Setup t<br>$T_{BCKx}$ = Hold t | time (before clock o<br>ime (after clock ed | edge)<br>ge) | The following descriptions are for setup times only.                                                          |  |  |  |  |

| T <sub>BACK</sub> /T <sub>BCKA</sub>        | Address inputs                              | ADDR         | Time before the clock that address signals<br>must be stable at the ADDR inputs of the<br>block RAM.          |  |  |  |  |

| T <sub>BDCK</sub> /T <sub>BCKD</sub>        | Data inputs                                 | DI           | Time before the clock that data must be stable at the DI inputs of the block RAM.                             |  |  |  |  |

| T <sub>BECK</sub> /T <sub>BCKE</sub>        | Enable                                      | EN           | Time before the clock that the enable signal<br>must be stable at the EN input of the block<br>RAM.           |  |  |  |  |

| T <sub>BRCK</sub> /T <sub>BCKR</sub>        | Synchronous<br>Set/Reset                    | SSR          | Time before the clock that the synchronous set/reset signal must be stable at the SSR input of the block RAM. |  |  |  |  |

| T <sub>BWCK</sub> /T <sub>BCKW</sub>        | Write Enable                                | WE           | Time before the clock that the write enable signal must be stable at the WE input of the block RAM.           |  |  |  |  |

| Clock to Out                                |                                             |              |                                                                                                               |  |  |  |  |

| T <sub>BCKO</sub>                           | Clock to<br>Output                          | CLK to<br>DO | Time after the clock that the output data is stable at the DO outputs of the block RAM.                       |  |  |  |  |

| Clock                                       | -                                           |              |                                                                                                               |  |  |  |  |

| T <sub>BPWH</sub>                           | Clock                                       | CLK          | Minimum pulse width, high.                                                                                    |  |  |  |  |

| T <sub>BPWL</sub>                           | Clock                                       | CLK          | Minimum pulse width, low.                                                                                     |  |  |  |  |

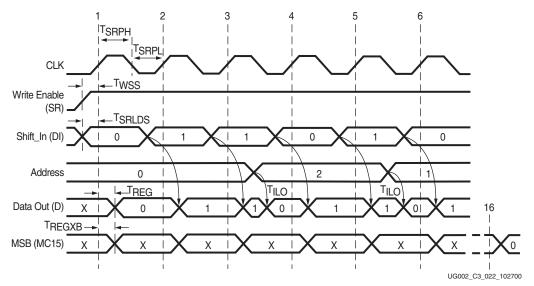

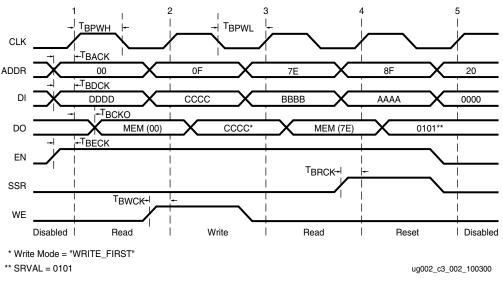

The timing diagram in Figure 1-8 describes a single-port block RAM in Write-First mode. The timing for Read-First and No-Change modes are similar (see chapter 2, block RAM section.)

Figure 1-8: Block SelectRAM Timing Diagram

At time 0, the block RAM is disabled; EN (enable) is low.

### Clock Event 1

#### **READ Operation:**

During a read operation, the contents of the memory at the address on the ADDR inputs are unchanged.

- T<sub>BACK</sub> before Clock Event 1, address 00 becomes valid at the ADDR inputs of the block RAM.

- At time T<sub>BECK</sub> before Clock Event 1, Enable goes High at the EN input of the block RAM, enabling the memory for the READ operation that follows.

- At time T<sub>BCKO</sub> after Clock Event 1, the contents of the memory at address 00 become stable at the DO pins of the block RAM.

### Clock Event 2

#### WRITE Operation:

During a write operation, the content of the memory at the location specified by the address on the ADDR inputs is replaced by the value on the DI pins and is immediately reflected on the output latches (in WRITE-FIRST mode); EN (enable) is high.

- At time T<sub>BACK</sub> before Clock Event 2, address 0F becomes valid at the ADDR inputs of the block RAM.

- At time T<sub>BDCK</sub> before Clock Event 2, data CCCC becomes valid at the DI inputs of the block RAM.

- At time T<sub>BWCK</sub> before Clock Event 2, Write Enable becomes valid at the WE following the block RAM.

- At time T<sub>BCKO</sub> after Clock Event 2, data CCCC becomes valid at the DO outputs of the block RAM.

### Clock Event 4

#### SSR (Synchronous Set/Reset) Operation

During an SSR operation, initialization parameter value SRVAL is loaded into the output latches of the block SelectRAM. The SSR operation does NOT change the contents of the memory and is independent of the ADDR and DI inputs.

- At time T<sub>BRCK</sub> before Clock Event 4, the synchronous set/reset signal becomes valid (High) at the SSR input of the block RAM.

- At time T<sub>BCKO</sub> after Clock Event 4, the SRVAL 0101 becomes valid at the DO outputs of the block RAM.

### **Clock Event 5**

#### **Disable Operation:**

De-asserting the enable signal EN disables any write, read or SSR operation. The disable operation does NOT change the contents of the memory or the values of the output latches.

- At time T<sub>BECK</sub> before Clock Event 5, the enable signal becomes valid (Low) at the EN input of the block RAM.

- After Clock Event 5, the data on the DO outputs of the block RAM is unchanged.

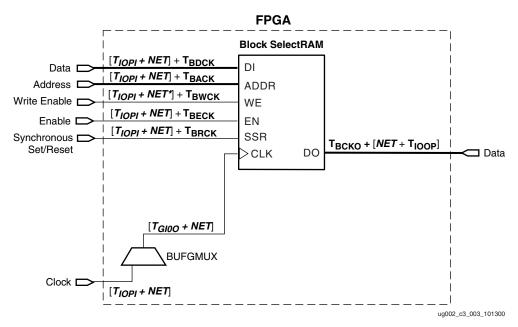

### **Timing Model**

**Figure 1-9** illustrates the delay paths associated with the implementation of block SelectRAM. This example takes the simplest paths on and off chip (these paths can vary greatly depending on the design). This timing model demonstrates how and where the block SelectRAM timing parameters are used.

**NET** = Varying interconnect delays  $T_{IOPI}$  = Pad to I-output of IOB delay  $T_{IOOP}$  = O-input of IOB to pad delay  $T_{GI0O}$  = BUFGMUX delay

# **Embedded Multiplier Timing Model**

### Introduction

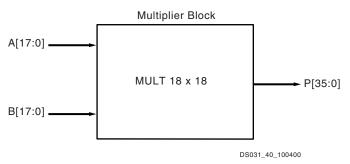

This section explains all timing parameters associated with the use of embedded 18-bit x 18-bit multipliers in Virtex-II FPGAs (see Figure 1-10). The propagation delays through the embedded multiplier differ based on the size of the multiplier function implemented. The longest delay through the multiplier is to the highest order bit output (P35). Therefore, if an 18-bit x 18-bit signed multiplier is implemented, the worst-case delay for this function is the longest delay associated with the embedded multiplier block. If smaller (LSB) multipliers are used, shorter delays can be realized.

This section is intended to be used in conjunction with the section on switching characteristics in the <u>Virtex-II Data Sheet</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the <u>Virtex-II Data Sheet</u>.

Figure 1-10: Embedded 18-bit x 18-bit Multiplier Block

## **Timing Parameters**

### Propagation Delays (All Worst-Case)

Table 1-1 lists the different values for the  $T_{MULT}$  timing parameter reported by the Timing Analyzer software. These values correspond to the propagation delay through the multiplier to a specific output pin of the multiplier block.

Table 1-1: Multiplier Switching Characteristics

| Description                     | Symbol            |

|---------------------------------|-------------------|

| Propagation Delay to Output Pin |                   |

| Input to Pin35                  | T <sub>MULT</sub> |

| Input to Pin34                  | T <sub>MULT</sub> |

| Input to Pin33                  | T <sub>MULT</sub> |

| Input to Pin32                  | T <sub>MULT</sub> |

| Input to Pin31                  | T <sub>MULT</sub> |

| Input to Pin30                  | T <sub>MULT</sub> |

| Input to Pin29                  | T <sub>MULT</sub> |

| Input to Pin28                  | T <sub>MULT</sub> |

| Input to Pin27                  | T <sub>MULT</sub> |

| Input to Pin26                  | T <sub>MULT</sub> |

| Input to Pin25                  | T <sub>MULT</sub> |

| Input to Pin24                  | T <sub>MULT</sub> |

| Input to Pin23                  | T <sub>MULT</sub> |

| Description    | Symbol            |

|----------------|-------------------|

| Input to Pin22 | T <sub>MULT</sub> |

| Input to Pin21 | T <sub>MULT</sub> |

| Input to Pin20 | T <sub>MULT</sub> |

| Input to Pin19 | T <sub>MULT</sub> |

| Input to Pin18 | T <sub>MULT</sub> |

| Input to Pin17 | T <sub>MULT</sub> |

| Input to Pin16 | T <sub>MULT</sub> |

| Input to Pin15 | T <sub>MULT</sub> |

| Input to Pin14 | T <sub>MULT</sub> |

| Input to Pin13 | T <sub>MULT</sub> |

| Input to Pin12 | T <sub>MULT</sub> |

| Input to Pin11 | T <sub>MULT</sub> |

| Input to Pin10 | T <sub>MULT</sub> |

| Input to Pin9  | T <sub>MULT</sub> |

| Input to Pin8  | T <sub>MULT</sub> |

| Input to Pin7  | T <sub>MULT</sub> |

| Input to Pin6  | T <sub>MULT</sub> |

| Input to Pin5  | T <sub>MULT</sub> |

| Input to Pin4  | T <sub>MULT</sub> |

| Input to Pin3  | T <sub>MULT</sub> |

| Input to Pin2  | T <sub>MULT</sub> |

| Input to Pin1  | T <sub>MULT</sub> |

| Input to Pin0  | T <sub>MULT</sub> |

Table 1-1: Multiplier Switching Characteristics (Continued)

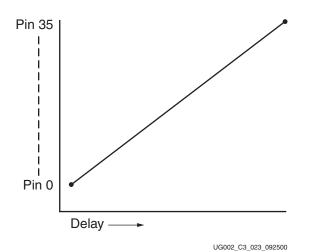

The shortest delay is to pin 0 and the longest delay to pin 35. Notice that the delay-to-pin ratio is essentially linear (see Figure 1-11). This implies that smaller multiply functions are faster than larger ones. This is true as long as the LSB inputs are used.

Figure 1-11: Pin-to-Delay Ratio Curve

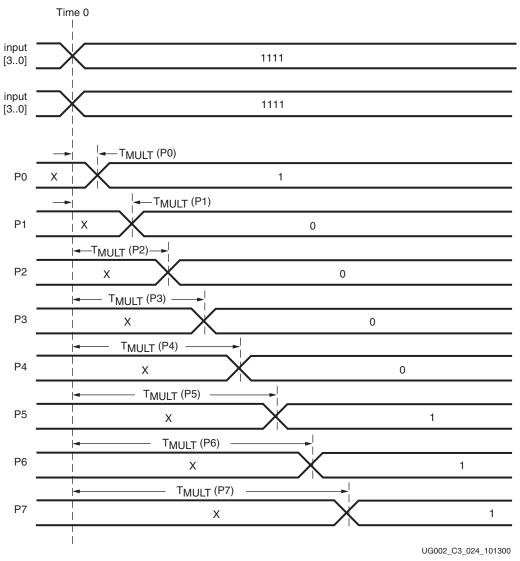

Figure 1-12 illustrates the result (outputs) of a 4-bit x 4-bit unsigned multiply implemented in an embedded multiplier block.

Figure 1-12: Embedded Multiplier Block Timing Diagram

At time 0 the two 4-bit numbers to be multiplied become valid at the A[0..3], B[0..3] inputs to the embedded multiplier. The result appears on the output pins P[0..7] in a staggered fashion. First, P0 becomes valid at time  $T_{MULT}$ (P0), followed by each subsequent output pin, until P7 becomes valid at time  $T_{MULT}$  (P7). In this case, the delay for this multiply function should correspond to that of Pin 7. In other words, the result is not valid until all output pins become valid.

# **IOB Timing Model**

### Introduction

This section describes all timing parameters associated with the Virtex-II IOB. The section consists of three parts:

- IOB Input Timing Model and Parameters

- IOB Output Timing Model and Parameters

- IOB 3-State Timing Model and Parameters

This section is intended to be used in conjunction with the section on switching characteristics in the <u>Virtex-II Data Sheet</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the <u>Virtex-II Data Sheet</u>.

#### A Note on I/O Standard Adjustments:

The "IOB Input and Output Switching Characteristics Standard Adjustments" tables in the switching characteristics section of the <u>Virtex-II Data Sheet</u> are delay adders (+/-) to be added to all timing parameter values associated with the IOB and the Global Clock (see "Pin-to-Pin Timing Model" on page 145), if an I/O standard other than LVTTL is used.

All values specified in the <u>Virtex-II Data Sheet</u> for the parameters covered in this section are specified for LVTTL. If another I/O standard is used, these delays change. However, there are several exceptions. The following parameters associated with the pad going to high-impedance (3-State buffer OFF) should NOT be adjusted:

- T<sub>IOTHZ</sub>

- T<sub>IOTLPHZ</sub>

- T<sub>GTS</sub>

- T<sub>IOCKHZ</sub>

- T<sub>IOSRHZ</sub>

1

# IOB Input Timing Model and Parameters

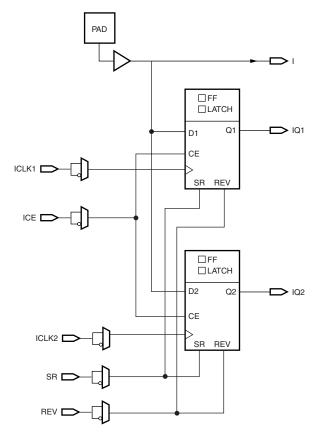

Figure 1-13 illustrates IOB inputs.

UG002\_C3\_004\_101300

Figure 1-13: Virtex-II IOB Input Diagram

# **Timing Parameters**

| Parameter                                           | Function                                    | Control<br>Signal | Description                                                                                                                       |  |  |  |  |

|-----------------------------------------------------|---------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>Propagation Delays</b>                           | Propagation Delays                          |                   |                                                                                                                                   |  |  |  |  |

| T <sub>IOPI</sub>                                   |                                             |                   | Propagation delay from the pad to I output of the IOB with no delay adder.                                                        |  |  |  |  |

| T <sub>IOPID</sub>                                  |                                             |                   | Propagation delay from the pad to I output of the IOB with the delay adder.                                                       |  |  |  |  |

| T <sub>IOPLI</sub>                                  |                                             |                   | Propagation delay from the pad to IQ output of the IOB via transparent latch with no delay adder.                                 |  |  |  |  |

| T <sub>IOPLID</sub>                                 |                                             |                   | Propagation delay from the pad to IQ output of the IOB via transparent latch with the delay adder.                                |  |  |  |  |

| Setup and Hold With                                 | Respect to Clock a                          | t IOB Inp         | ut Register                                                                                                                       |  |  |  |  |

| $T_{xxCK}$ = Setup time<br>$T_{xxCKxx}$ = Hold time | (before clock edge)<br>e (after clock edge) |                   | The following descriptions are for setup times only.                                                                              |  |  |  |  |

| T <sub>IOPICK</sub> /T <sub>IOICKP</sub>            | ID input with<br>NO delay                   |                   | Time before the clock that the input signal from the pad must be stable at the ID input of the IOB Input Register, with no delay. |  |  |  |  |

#

| Parameter                                  | Function                         | Control<br>Signal | Description                                                                                                                       |

|--------------------------------------------|----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| T <sub>IOPICKD</sub> /T <sub>IOICKPD</sub> | ID input with delay              |                   | Time before the clock that the input signal from the pad must<br>be stable at the ID input of the IOB Input Register, with delay. |

| T <sub>IOICECK</sub> /T <sub>IOCKICE</sub> | ICE input                        |                   | Time before the clock that the Clock Enable signal must be stable at the ICE input of the IOB Input Register.                     |

| T <sub>IOSRCKI</sub>                       | SR input (IFF,<br>synchronous)   |                   | Time before the clock that the Set/Reset signal must be stable<br>at the SR input of the IOB Input Register.                      |

| Clock to Out                               |                                  |                   |                                                                                                                                   |

| T <sub>IOCKIQ</sub>                        | Clock (CLK) to<br>(IQ) output    |                   | Time after the clock that the output data is stable at the IQ output of the IOB Input Register.                                   |

| Set/Reset Delays                           |                                  |                   |                                                                                                                                   |

| T <sub>IOSRIQ</sub>                        | SR Input to IQ<br>(asynchronous) |                   | Time after the Set/Reset signal of the IOB is toggled that the output of the IOB input register (IQ) reflects the signal.         |

| T <sub>GSRQ</sub>                          | GSR to output IQ                 |                   | Time after the Global Set/Reset is toggled that the output of the IOB input register (IQ) reflects the set or reset.              |

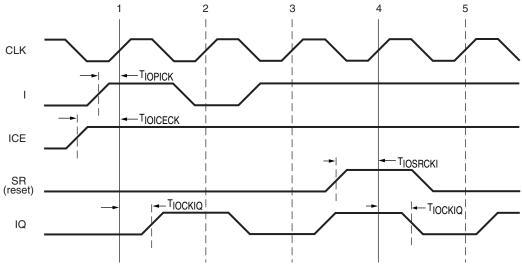

#### Figure 1-14 illustrates IOB input register timing.

UG002\_c3\_005\_112700

Figure 1-14: IOB Input Register Timing Diagram

### **Clock Events**

- At time T<sub>IOICECK</sub> before Clock Event 1, the input clock enable signal becomes valid-high at the ICE input of the input register, enabling the input register for incoming data.

- At time T<sub>IOPICK</sub> before Clock Event 1, the input signal becomes valid-high at the I input of the input register and is reflected on the IQ output of the input register at time T<sub>IOCKIQ</sub> after Clock Event 1.

- At time T<sub>IOSRCKI</sub> before Clock Event 4 the SR signal (configured as synchronous reset in this case) becomes valid-high resetting the input register and reflected at the IQ output of the IOB at time T<sub>IOCKIQ</sub> after Clock Event 4.

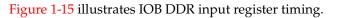

Figure 1-15: IOB DDR Input Register Timing Diagram

### **Clock Events**

- At time T<sub>IOICECK</sub> before Clock Event 1 the input clock enable signal becomes validhigh at the ICE input of both of the DDR input registers, enabling them for incoming data. Since the ICE and I signals are common to both DDR registers, care must be taken to toggle these signals between the rising edges of ICLK1 and ICLK2 as well as meeting the register setup-time relative to both clocks.

- At time T<sub>IOPICK</sub> before Clock Event 1 (rising edge of ICLK1) the input signal becomes valid-high at the I input of both registers and is reflected on the IQ1 output of input-register 1 at time T<sub>IOCKIQ</sub> after Clock Event 1.

- At time T<sub>IOPICK</sub> before Clock Event 2 (rising edge of ICLK2) the input signal becomes valid-low at the I input of both registers and is reflected on the IQ2 output of input-register 2 at time T<sub>IOCKIQ</sub> after Clock Event 2 (no change in this case).

- At time T<sub>IOSRCKI</sub> before Clock Event 9 the SR signal (configured as synchronous reset in this case) becomes valid-high resetting input-register 1 (IQ1) at time T<sub>IOCKIQ</sub> after Clock Event 9, and input-register 2 (IQ2) at time T<sub>IOCKIQ</sub> after Clock Event 10.

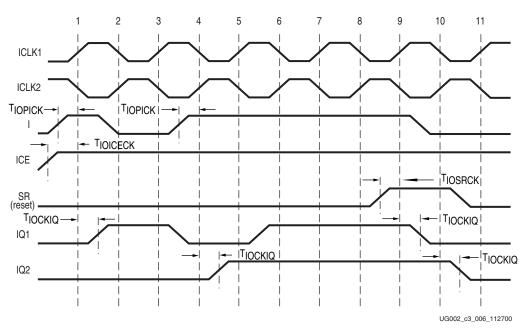

# **IOB** Output Timing Model and Parameters

Figure 1-16 illustrates IOB outputs.

Figure 1-16: Virtex-II IOB Output Diagram

### **Timing Parameters**

| Parameter                                              | Function                                 | Control<br>Signal | Description                                                                                                    |

|--------------------------------------------------------|------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|

| Propagation Delays                                     |                                          |                   |                                                                                                                |

| T <sub>IOOP</sub>                                      |                                          |                   | Propagation delay from the O input of the IOB to the pad.                                                      |

| T <sub>IOOLP</sub>                                     |                                          |                   | Propagation delay from the O input of the IOB to the pad via transparent latch.                                |

| Setup and Hold With F                                  | Respect to Clock at IOB                  | BOutput I         | Register                                                                                                       |

| $T_{xxCK}$ = Setup time (k<br>$T_{xxCKxx}$ = Hold time | pefore clock edge)<br>(after clock edge) |                   | The following descriptions are for setup times only.                                                           |

| T <sub>IOOCK</sub> /T <sub>IOCKO</sub>                 | O input                                  |                   | Time before the clock that data must be stable at the O input of the IOB Output Register.                      |

| T <sub>IOOCECK</sub> /T <sub>IOCKOCE</sub>             | OCE input                                |                   | Time before the clock that the Clock Enable signal must be stable at the OCE input of the IOB Output Register. |

| T <sub>IOSRCKO</sub> /T <sub>IOCKOSR</sub>             | SR input (OFF)                           |                   | Time before the clock that the Set/Reset signal must be stable at the SR input of the IOB Output Register.     |

| Clock to Out                                           |                                          |                   |                                                                                                                |

| T <sub>IOCKP</sub>                                     | Clock (CLK) to pad                       |                   | Time after the clock that the output data is stable at the pad.                                                |

| Set/Reset Delays                                       |                                          |                   |                                                                                                                |

| T <sub>IOSRP</sub>                                     | SR Input to pad (asynchronous)           |                   | Time after the Set/Reset input of the IOB is toggled that the pad reflects the set or reset.                   |

| T <sub>IOGSRQ</sub>                                    | GSR to pad                               |                   | Time after the Global Set/Reset is toggled that the pad reflects the set or reset.                             |

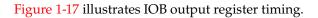

Figure 1-17: IOB Output Register Timing Diagram

### **Clock Events**

- At time T<sub>IOOCECK</sub> before Clock Event 1, the output clock enable signal becomes validhigh at the OCE input of the output register, enabling the output register for incoming data.

- At time T<sub>IOOCK</sub> before Clock Event 1, the output signal becomes valid-high at the O input of the output register and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 1.

- At time T<sub>IOSRCKO</sub> before Clock Event 4, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting the output register and reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 4.

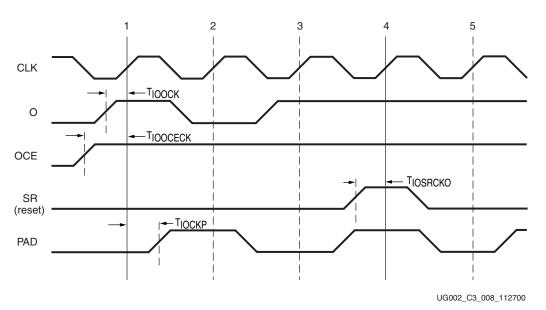

*Figure 1-18:* **IOB DDR Output Register Timing Diagram**

### **Clock Events**

- At time T<sub>IOOCECK</sub> before Clock Event 1, the output clock enable signal becomes validhigh at the OCE input of both of the DDR output registers, enabling them for incoming data. Since the OCE signal is common to both DDR registers, care must be taken to toggle this signal between the rising edges of OTCLK1 and OTCLK2 as well as meeting the register setup-time relative to both clocks.

- At time T<sub>IOOCK</sub> before Clock Event 1 (rising edge of OTCLK1), the output signal O1 becomes valid-high at the O1 input of output register 1 and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 1.

- At time T<sub>IOOCK</sub> before Clock Event 2 (rising edge of OTCLK2), the output signal O2 becomes valid-high at the O2 input of output register 2 and is reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 2 (no change on the pad in this case).

- At time T<sub>IOSRCKO</sub> before Clock Event 9, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting output-register 1 (reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 9) (no change in this case) and output-register 2 (reflected on the pad at time T<sub>IOCKP</sub> after Clock Event 10) (no change in this case).

# IOB 3-State Timing Model and Parameters

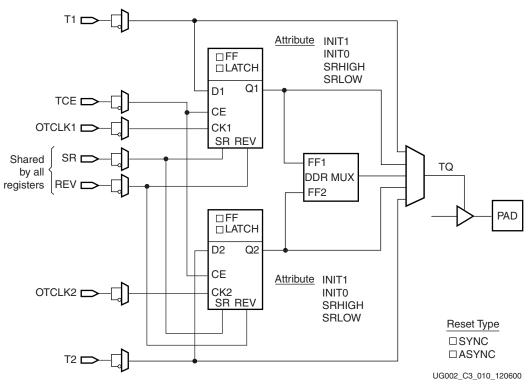

Figure 1-19 illustrates IOB 3-state timing

Figure 1-19: Virtex-II IOB 3-State Diagram

### **Timing Parameters**

| Parameter                                                                                  | Function | Control<br>Signal | Description                                                                                                                   |  |

|--------------------------------------------------------------------------------------------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Propagation Delays                                                                         |          |                   |                                                                                                                               |  |

| T <sub>IOTHZ</sub>                                                                         |          |                   | Time after T input of the IOB is toggled that the pad goes to high-impedance.                                                 |  |

| T <sub>IOTON</sub>                                                                         |          |                   | Time after the T input of the IOB is toggled that the pad goes from high-impedance to valid data.                             |  |

| T <sub>IOTLPHZ</sub>                                                                       |          |                   | Time after the T input of the IOB via transparent latch is toggled that the pad goes to high-impedance.                       |  |

| T <sub>IOTLPON</sub>                                                                       |          |                   | Time after the T input of the IOB via transparent latch<br>is toggled that the pad goes from high-impedance to<br>valid data. |  |

| T <sub>GTS</sub>                                                                           |          |                   | Time after the Global 3-state signal is asserted that the pad goes to high-impedance.                                         |  |

| Setup and Hold With Respect to Clock at IOB 3-State Register                               |          |                   |                                                                                                                               |  |

| $T_{xxCK}$ = Setup time (before clock edge)<br>$T_{xxCKxx}$ = Hold time (after clock edge) |          |                   | The following descriptions are for setup times only.                                                                          |  |

| T <sub>IOTCK</sub> /T <sub>IOCKT</sub>                                                     | T input  |                   | Time before the clock that the signal must be stable<br>at the T input of the IOB 3-state Register.                           |  |

#

| Parameter                                  | Function                                     | Control<br>Signal | Description                                                                                                           |  |

|--------------------------------------------|----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| T <sub>IOTCECK</sub> /T <sub>IOCKTCE</sub> | TCE input                                    |                   | Time before the clock that the clock enable signal<br>must be stable at the TCE input of the IOB 3-state<br>Register. |  |

| T <sub>IOSRCKT</sub> /T <sub>IOCKTSR</sub> | SR input (TFF)                               |                   | Time before the clock that the set/reset signal.                                                                      |  |

| Clock to Out                               | -                                            |                   |                                                                                                                       |  |

| T <sub>IOCKHZ</sub>                        | Clock (CLK) to pad High-Z                    |                   | Time after clock that the pad goes to high-<br>impedance.                                                             |  |

| T <sub>IOCKON</sub>                        | Clock (CLK) to valid data<br>on pad          |                   | Time after clock that the pad goes from high-<br>impedance to valid data.                                             |  |

| Set/Reset Delays                           |                                              |                   |                                                                                                                       |  |

| T <sub>IOSRHZ</sub>                        | SR Input to pad High-Z<br>(asynchronous)     |                   | Time after the SR signal is toggled that the pad goes to high-impedance.                                              |  |

| T <sub>IOSRON</sub>                        | SR Input to valid data on pad (asynchronous) |                   | Time after the SR signal is toggled that the pad goes from high-impedance to valid data.                              |  |

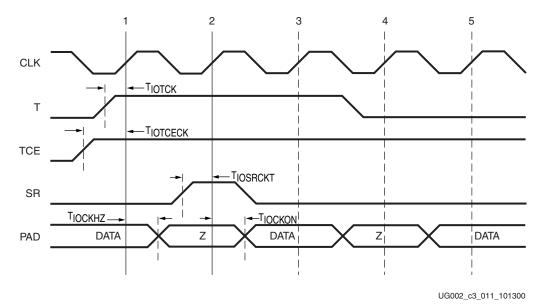

Figure 1-20 illustrates IOB 3-state register timing.

Figure 1-20: IOB 3-State Register Timing Diagram

### **Clock Events**

- At time T<sub>IOTCECK</sub> before Clock Event 1, the 3-state clock enable signal becomes validhigh at the TCE input of the 3-state register, enabling the 3-state register for incoming data.

- At time T<sub>IOTCK</sub> before Clock Event 1 the 3-state signal becomes valid-high at the T input of the 3-state register, returning the pad to high-impedance at time T<sub>IOCKHZ</sub> after Clock Event 1.

- At time T<sub>IOSRCKT</sub> before Clock Event 2, the SR signal (configured as synchronous reset in this case) becomes valid-high, resetting the 3-state register and returning the pad to valid data at time T<sub>IOSRON</sub> after Clock Event 2.

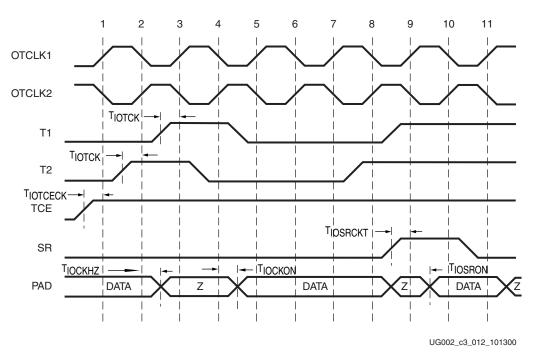

Figure 1-21: IOB DDR 3-State Register Timing Diagram

### **Clock Events**

- At time T<sub>IOTCECK</sub> before Clock Event 1, the 3-state clock enable signal becomes validhigh at the TCE input of both of the DDR 3-state registers, enabling them for incoming data. Since the TCE signal is common to both DDR registers, care must be taken to toggle this signal between the rising edges of OTCLK1 and OTCLK2 as well as meeting the register setup-time relative to both clocks.

- At time T<sub>IOTCK</sub> before Clock Event 2 (rising edge of OTCLK2), the 3-state signal T2 becomes valid-high at the T2 input of 3-state register 2, switching the pad to high-impedance at time T<sub>IOCKHZ</sub> after Clock Event 2.

- At time T<sub>IOTCK</sub> before Clock Event 3 (rising edge of OTCLK1), the 3-state signal T1 becomes valid-high at the T1 input of 3-state register 1, keeping the pad at high-impedance for another half clock cycle (half the period of OTCLK1 or 2).

- At time T<sub>IOTCK</sub> before Clock Event 4 (rising edge of OTCLK2), the 3-state signal T2 becomes valid-low at the T2 input of 3-state register 2, switching the pad to valid data at time T<sub>IOCKON</sub> after Clock Event 4. This is repeated for 3-state signal T1 at the following clock event (5) maintaining valid data on the pad until Clock Event 8.

- At time T<sub>IOTCK</sub> before Clock Event 8 (rising edge of OTCLK2), the 3-state signal T2 becomes valid-high at the T2 input of 3-state register 2, switching the pad to high-impedance at time T<sub>IOCKHZ</sub> after Clock Event 8.

- At time T<sub>IOSRCKT</sub> before Clock Event 9 (rising edge of OTCLK1), the SR signal (configured as synchronous reset in this case) becomes valid-high at the SR input of 3-state Register 1, returning the pad to valid data at time T<sub>IOSRON</sub> after Clock Event 9.

# **Pin-to-Pin Timing Model**

### Introduction

This section explains the delays and timing parameters associated with the use of the Global Clock network and the DCM. These delays are true pin-to-pin delays relative to the Global Clock pin and an output or input pin with or without the DCM.

This section consists of two parts:

- Global Clock Input to Output

- Global Clock Setup and Hold

The former describes the delay from the Global Clock pin (with and without the DCM) to an output pin via an Output flip-flop. The latter describes the set-up time for an Input flip-flop from an input pin relative to the Global Clock pin (with and without the DCM).

The values reported in the switching characteristics section of the <u>Virtex-II Data Sheet</u> are for LVTTL I/O standards. For different I/O standards, adjust these values with those shown in the "IOB Switching Characteristics Standard Adjustments" tables.

This section is intended to be used in conjunction with the section on switching characteristics in the <u>Virtex-II Data Sheet</u> and the Timing Analyzer (TRCE) report from Xilinx software. For specific timing parameter values, refer to the <u>Virtex-II Data Sheet</u>.

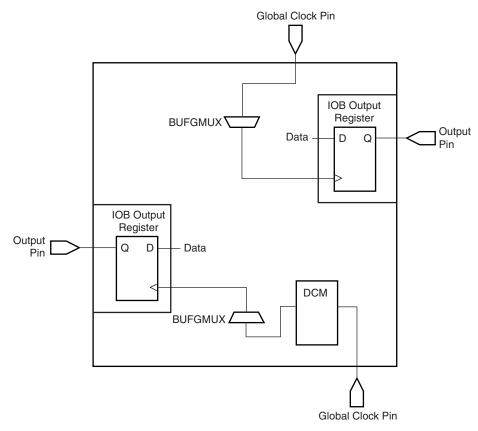

## Global Clock Input to Output

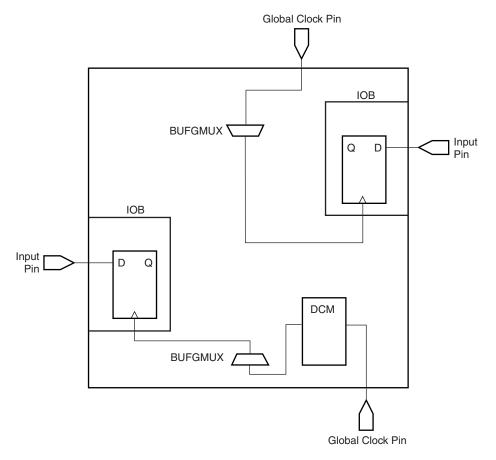

Figure 1-22 illustrates the paths associated with the timing parameters defined in this section. Note that they differ only in their use of the DCM.

UG002\_C3\_013\_101300

Figure 1-22: Global Clock Input to Output Model

### **Timing Parameters**

| Parameter             | Description                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>ICKOFDLL</sub> | Time after the Global Clock (pin), using the DCM, that the output data from an IOB Output flip-flop is stable at the output pin.   |

| T <sub>ICKOF</sub>    | Time after the Global Clock (pin), without the DCM, that the output data from an IOB Output flip-flop is stable at the output pin. |

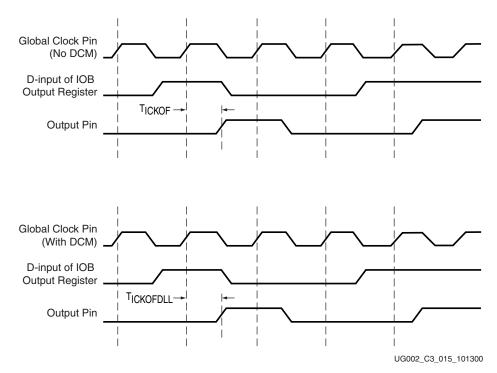

The waveforms depicted in Figure 1-23 demonstrate the relation of the Global Clock pin, the output data, and the use of the timing parameters.

Figure 1-23: Global Clock Input to Output Timing Diagram

### Global Clock Setup and Hold

Figure 1-24 illustrates the paths associated with the timing parameters defined in this section. Note, they differ only in their use of the DCM.

UG002\_C3\_014\_101300

Figure 1-24: Global Clock Setup and Hold Model

### **Timing Parameters**

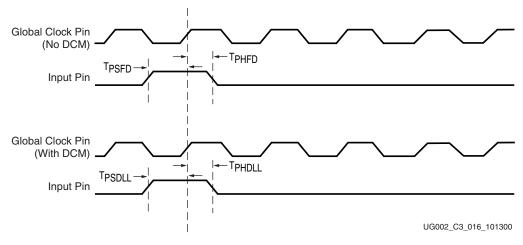

Setup and Hold for Input Registers Relative to the Global Clock (pin):

- T<sub>PSDLL</sub> / T<sub>PHDLL</sub> Time before the Global Clock (pin), with DCM, that the input signal must be stable at the D-input of the IOB input register.

- T<sub>PSFD</sub> / T<sub>PHFD</sub> Time before the Global Clock (pin), without DCM, that the input signal must be stable at the D-input of the IOB input register.

Note:  $T_{PSFD}$  = Setup time (before clock edge) and  $T_{PHFD}$  = Hold time (after clock edge). The previous descriptions are for setup times only.

The waveforms depicted in Figure 1-25 demonstrate the relation of the Global Clock pin, the input data, and the use of the timing parameters.

Figure 1-25: Global Clock Setup and Hold Timing Diagram

# **Digital Clock Manager Timing Model**

This section describes the timing parameters associated with the Digital Clock Manager (DCM), which are reported in the <u>Virtex-II Data Sheet</u>. Note that these parameters are not used by the Timing Analyzer software in the production of timing reports; they are all measured values and are fully characterized in silicon. For specific timing parameter values, refer to the <u>Virtex-II Data Sheet</u>. This section discusses the following:

- **Operating Frequency Ranges:** The minimum and maximum frequencies supported by the DCM for all clock inputs and outputs.

- **Input Clock Tolerances:** Input clock period (pulse widths), jitter, and drift requirements for proper function of the DCM for all clock inputs.

- **Output Clock Precision:** Output clock period jitter, phase offsets, and duty cycle for all clock outputs of the DCM (worst case).

- Miscellaneous Timing Parameters: DCM lock times, Tap delay and shifting range.

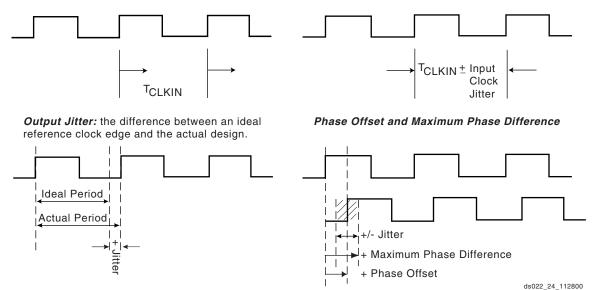

For a detailed description of input clock tolerance, jitter, and phase offset see the waveforms at the end of this section.

# **Operating Frequency Ranges**

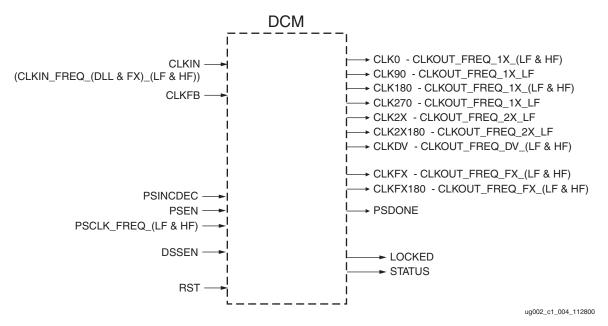

Figure 1-26 illustrates the DCM functional block and corresponding timing parameters for all clock inputs and outputs.

Figure 1-26: DCM Functional Block: Operating Frequency Ranges

### **Timing Parameters**

| Parameter                      | Description                                                                                                                            |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Low Frequency Mode             |                                                                                                                                        |  |

| CLKOUT_FREQ_1X_LF              | The minimum and maximum frequency for the CLK0, CLK90, CLK180, CLK270 outputs of the DCM in low-frequency mode.                        |  |

| CLKOUT_FREQ_2X_LF              | The minimum and maximum frequency for the CLK2X and CLK2X180 outputs of the DCM in low-frequency mode.                                 |  |

| CLKOUT_FREQ_DV_LF              | The minimum and maximum frequency for the CLKDV output of the DCM in low-frequency mode.                                               |  |

| CLKOUT_FREQ_FX_LF              | The minimum and maximum frequency for the CLKFX and CLKFX180 outputs of the DCM in low-frequency mode.                                 |  |

| CLKIN_FREQ_DLL_LF <sup>1</sup> | The minimum and maximum frequency for the CLKIN input to the DCM in low-frequency mode when using the delay-locked loop (DLL) outputs. |  |

| CLKIN_FREQ_FX_LF <sup>2</sup>  | The minimum and maximum frequency for the CLKIN input to the DCM in low-frequency mode when using the FX outputs.                      |  |

| PSCLK_FREQ_LF                  | The minimum and maximum frequency for the PSCLK input to the DCM in low-frequency mode.                                                |  |

| High Frequency Mode            |                                                                                                                                        |  |

| CLKOUT_FREQ_1X_HF              | The minimum and maximum frequency for the CLK0, CLK180 outputs of the DCM in high-frequency mode.                                      |  |

| CLKOUT_FREQ_DV_HF              | The minimum and maximum frequency for the CLKDV output of the DCM in high-frequency mode.                                              |  |

| CLKOUT_FREQ_FX_HF              | The minimum and maximum frequency for the CLKFX and CLKFX180 outputs of the DCM in high-frequency mode.                                |  |

| CLKIN_FREQ_DLL_HF              | The minimum and maximum frequency for the CLKIN input<br>to the DCM in high-frequency mode when using the DLL<br>outputs.              |  |

| CLKIN_FREQ_FX_HF               | The minimum and maximum frequency for the CLKIN input<br>to the DCM in high-frequency mode when using the FX<br>outputs.               |  |

| PSCLK_FREQ_HF                  | The minimum and maximum frequency for the PSCLK input to the DCM in high-frequency mode.                                               |  |

#### Notes:

- 1. Delay-locked loop (DLL) outputs include: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV.

- 2. FX outputs include: CLKFX and CLKFX180

1

# Input Clock Tolerances

### **Timing Parameters**

| Parameter                | Description                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSCLK_PULSE <sup>1</sup> | The minimum pulse width (HIGH and LOW) that the PSCLK input to the DCM can have over a range of frequencies.                                           |

| CLKIN_PULSE              | The minimum pulse width (HIGH and LOW) that the CLKIN input to the DCM can have over a range of frequencies. Also applies to PSCLK.                    |

| CLKFB_DELAY_VAR_EXT      | The maximum allowed variation in delay (across<br>environmental changes) of the feedback clock path<br>when routed externally for board-level de-skew. |

| Low Frequency Mode       |                                                                                                                                                        |

| CLKIN_CYC_JITT_DLL_LF    | The maximum cycle-to-cycle jitter the CLKIN input to<br>the DCM can have when using the DLL outputs in<br>low-frequency mode.                          |

| CLKIN_CYC_JITT_FX_LF     | The maximum cycle-to-cycle jitter the CLKIN input to<br>the DCM can have when using the FX outputs in low-<br>frequency mode.                          |

| CLKIN_PER_JITT_DLL_LF    | The maximum period jitter the CLKIN input to the DCM can have when using the DLL outputs in low-frequency mode.                                        |

| CLKIN_PER_JITT_FX_LF     | The maximum period jitter the CLKIN input to the DCM can have when using the FX outputs in low-frequency mode.                                         |

| High Frequency Mode      |                                                                                                                                                        |

| CLKIN_CYC_JITT_DLL_HF    | The maximum cycle-to-cycle jitter the CLKIN input to<br>the DCM can have when using the DLL outputs in<br>high-frequency mode.                         |

| CLKIN_CYC_JITT_FX_HF     | The maximum cycle-to-cycle jitter the CLKIN input to<br>the DCM can have when using the FX outputs in high-<br>frequency mode.                         |

| CLKIN_PER_JITT_DLL_HF    | The maximum period jitter the CLKIN input to the DCM can have when using the DLL outputs in high-frequency mode.                                       |

| CLKIN_PER_JITT_FX_HF     | The maximum period jitter the CLKIN input to the DCM can have when using the FX outputs in high-frequency mode.                                        |

#### Notes:

The frequencies applicable to CLKIN\_PULSE range from 1 to >400 MHz. These frequencies also apply to PSCLK\_PULSE. Since PSCLK can be less than 1 MHz, the pulse width under this condition is specified for PSCLK only.

# **Output Clock Precision**

### **Timing Parameters**

| Parameter             | Description                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------|

| CLKOUT_PER_JITT_0     | The maximum period jitter of the CLK0 output clock from the DCM (worst case).                         |

| CLKOUT_PER_JITT_90    | The maximum period jitter of the CLK90 output clock from the DCM (worst case).                        |

| CLKOUT_PER_JITT_180   | The maximum period jitter of the CLK180 output clock from the DCM (worst case).                       |

| CLKOUT_PER_JITT_270   | The maximum period jitter of the CLK270 output clock from the DCM (worst case).                       |

| CLKOUT_PER_JITT_2X    | The maximum period jitter of the CLK2X and CLK2X180 output clocks from the DCM (worst case).          |

| CLKOUT_PER_JITT_DV1   | The maximum period jitter of the CLKDV (integer division) output clock from the DCM (worst case).     |

| CLKOUT_PER_JITT_DV2   | The maximum period jitter of the CLKDV (non-integer division) output clock from the DCM (worst case). |

| CLKOUT_PER_JITT_FX    | The maximum period jitter of the FX output clocks from the DCM (worst case).                          |

| CLKIN_CLKFB_PHASE     | Maximum phase offset between the CLKIN and CLKFB inputs to the DCM.                                   |

| CLKOUT_PHASE          | Maximum phase offset between any DCM clock outputs.                                                   |

| CLKOUT_DUTY_CYCLE_DLL | The duty-cycle precision for all DLL outputs.                                                         |

| CLKOUT_DUTY_CYCLE_FX  | The duty-cycle precision for the FX outputs.                                                          |

# Miscellaneous DCM Timing Parameters

#### Table 1-2: Miscellaneous DCM Timing Parameters

| Parameter           | Description                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------|

| LOCK_DLL            | Time required for DCM to lock over a range of clock frequencies when using the DLL outputs. |

| LOCK_FX             | Time required for DCM to lock when using the FX outputs.                                    |

| LOCK_DLL_FINE_SHIFT | Additional lock time when performing fine phase shifting.                                   |

| FINE_SHIFT_RANGE    | Absolute range for fine phase shifting.                                                     |

| DCM_TAP             | Resolution of delay line.                                                                   |

The waveforms in Figure 1-27 demonstrate the relationship between clock tolerance, jitter, and phase.

Period Tolerance: the allowed input clock period change in nanoseconds.

Figure 1-27: DCM Jitter, Phase, and Tolerance Timing Waveforms

Output jitter is period jitter measured on the DLL output clocks, excluding input clock jitter.

Phase offset between CLKIN and CLKFB is the worst-case fixed time difference between rising edges of CLKIN and CLKFB, excluding output jitter and input clock jitter.

Phase offset between clock outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, excluding output jitter and input clock jitter.

Maximum phase difference between CLKIN an CLKFB is the sum of output jitter and phase offset between CLKIN and CLKFB, or the greatest difference between CLKIN and CLKFB rising edges due to DLL alone (excluding input clock jitter).

Maximum phase difference between clock outputs on the DLL is the sum of output jitter and phase offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (excluding input clock jitter).