# Using Block SelectRAM<sup>™</sup> Memory

# Introduction

In addition to distributed SelectRAM memory, Virtex-II devices feature a large number of 18 Kb block SelectRAM memories. The block SelectRAM memory is a True Dual-Port<sup>™</sup> RAM, offering fast, discrete, and large blocks of memory in the device. The memory is organized in columns, and the total amount of block SelectRAM memory depends on the size of the Virtex-II device. The 18 Kb blocks are cascadable to enable a deeper and wider memory implementation, with a minimal timing penalty incurred through specialized routing resources.

Embedded dual- or single-port RAM modules, ROM modules, synchronous and asynchronous FIFOs, and data width converters are easily implemented using the Xilinx CORE Generator "Block Memory" modules. Asynchronous FIFOs can also be generated using the CORE Generator Asynchronous FIFO module. Starting with IP Update #3, the designer can also generate synchronous FIFOs using Block Memory.

# Synchronous Dual-Port and Single-Port RAM

## Data Flow

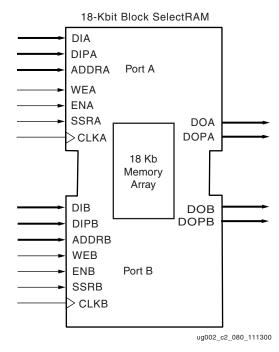

The 18Kb block SelectRAM dual-port memory consists of an 18-Kb storage area and two completely independent access ports, A and B. The structure is fully symmetrical, and both ports are interchangeable.

Data can be written to either port and can be read from the same or the other port. Each port is synchronous, with its own clock, clock enable, and write enable. Note that the read operation is also synchronous and requires a clock edge.

Figure 2-42: Dual-Port Data Flows

As described below, there are three options for the behavior of the data output during a write operation on its port. There is no dedicated monitor to arbitrate the result of identical addresses on both ports. It is up to the user to time the two clocks appropriately. However, conflicting simultaneous writes to the same location never cause any physical damage.

## **Operating Modes**

To maximize utilization of the True Dual-Port memory at each clock edge, the block SelectRAM memory supports three different write modes for each port. The "read during write" mode offers the flexibility of using the data output bus during a write operation on the same port. Output behavior is determined by the configuration. This choice increases the efficiency of block SelectRAM memory at each clock cycle and allows designs that use maximum bandwidth.

### **Read Operation**

The read operation uses one clock edge. The read address is registered on the read port, and the stored data is loaded into the output latches after the RAM access interval passes.

## Write Operations

A write operation is a single clock-edge operation. The write address is registered on the write port, and the data input is stored in memory.

Three different modes are used to determine data available on the output latches after a write clock edge.

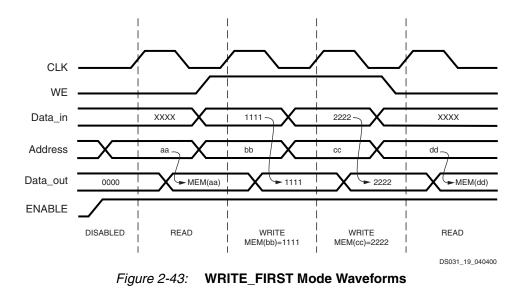

#### WRITE\_FIRST or Transparent Mode (Default)

In WRITE\_FIRST mode, the input data is simultaneously written into memory and stored in the data output (transparent write), as shown in Figure 2-43.

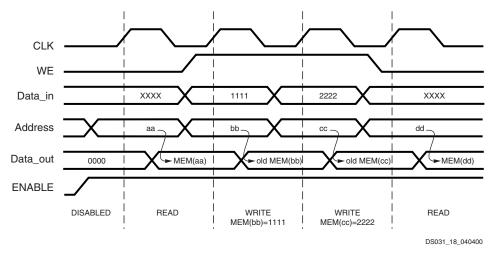

#### READ\_FIRST or Read-Before-Write Mode

In READ\_FIRST mode, data previously stored at the write address appears on the output latches, while the input data is being stored in memory (read before write). See Figure 2-44.

Figure 2-44: **READ\_FIRST Mode Waveforms**

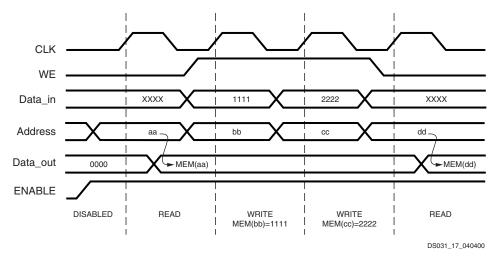

#### NO\_CHANGE Mode

In NO\_CHANGE mode, the output latches remain unchanged during a write operation. As shown in Figure 2-45, data output is still the last read data and is unaffected by a write operation on the same port.

Mode selection is set by configuration. One of these three modes is set individually for each port by an attribute. The default mode is WRITE\_FIRST.

Figure 2-45: NO\_CHANGE Mode Waveforms

## **Conflict Resolution**

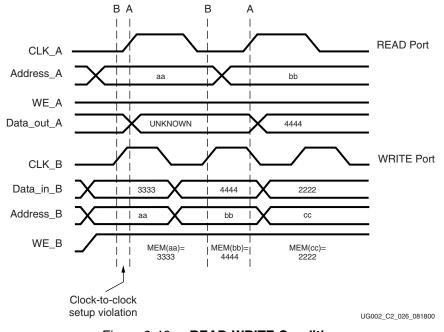

Virtex-II block SelectRAM memory is a True Dual-Port RAM that allows both ports to simultaneously access the same memory cell. When one port writes to a given memory cell, the other port must not address that memory cell (for a write or a read) within the clock-to-clock setup window. Figure 2-46 describes this asynchronous operation.

Figure 2-46: **READ-WRITE Conditions**

If port A and port B are configured with different widths, only the overlapping bits are invalid when conflicts occur.

#### Asynchronous Clocks

The first CLK\_A clock edge violates the clock-to-clock setup parameter, because it occurs too soon after the last CLK\_B clock edge. The write operation on port B is valid, and the read operation on port A is invalid.

At the second rising edge of the CLK\_B pin, the write operation is valid. The memory location (bb) contains 4444. The second rising edge of CLK\_A reads the new data at the same location (bb), which now contains 4444.

The clock-to-clock setup timing parameter is specified together with other block SelectRAM switching characteristics in the <u>Virtex-II Data Sheet</u>.

#### Synchronous Clocks

When both clocks are synchronous or identical, the result of simultaneous accesses from both ports to the same memory cell is best described in words:

- If both ports read simultaneously from the same memory cell: Both Data\_out ports will have the same data.

- If both ports write simultaneously into the same memory cell: The data stored in that cell becomes invalid (unless both ports write identical data).

- If one port writes and the other one reads from the same memory cell: The write operation succeeds, and the write port's Data\_out behaves as determined by the read output mode (write\_first, read\_first, or no\_change).

If the write port is in read\_first mode, the read port's Data\_out represents the previous content of the memory cell. If the write port is in write\_first mode or in no\_change mode, the read port's Data\_out becomes invalid. Obviously, the read port's mode setting does not affect this operation.

# Characteristics

- A write operation requires only one clock edge.

- A read operation requires only one clock edge.

- All inputs are registered with the port clock and have a setup-to-clock timing specification.

- All outputs have a read-through function or one of three read-during-write functions, depending on the state of the WE pin. The outputs relative to the port clock are available after the clock-to-out timing interval.

- Block SelectRAM cells are true synchronous RAM memories and do not have a combinatorial path from the address to the output.

- The ports are completely independent of each other (that is, clocking, control, address, read/write functions, initialization, and data width) without arbitration.

- Output ports are latched with a self-timed circuit, guaranteeing glitch-free reads. The state of the output port does not change until the port executes another read or write operation.

- Data input and output signals are always busses; that is, in a 1-bit width configuration, the data input signal is DI[0] and the data output signal is DO[0].

## Library Primitives

The input and output data busses are represented by two busses for 9-bit width (8+1), 18-bit width (16+2), and 36-bit width (32+4) configurations. The ninth bit associated with each byte can store parity or error correction bits. No specific function is performed on this bit.

The separate bus for parity bits facilitates some designs. However, other designs safely use a 9-bit, 18-bit, or 36-bit bus by merging the regular data bus with the parity bus. Read/write and storage operations are identical for all bits, including the parity bits.

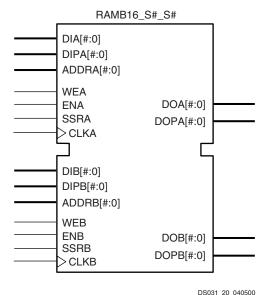

Figure 2-47 shows the generic dual-port block RAM primitive. DIA, DIPA, ADDRA, DOA, DOPA, and the corresponding signals on port B are busses.

.....

Figure 2-47: Dual-Port Block RAM Primitive

| Primitive      | Port A Width | Port B Width |

|----------------|--------------|--------------|

| RAMB16_S1_S1   |              | 1            |

| RAMB16_S1_S2   |              | 2            |

| RAMB16_S1_S4   | 1            | 4            |

| RAMB16_S1_S9   | 1            | (8+1)        |

| RAMB16_S1_S18  |              | (16+2)       |

| RAMB16_S1_S36  |              | (32+4)       |

| RAMB16_S2_S2   |              | 2            |

| RAMB16_S2_S4   |              | 4            |

| RAMB16_S2_S9   | 2            | (8+1)        |

| RAMB16_S2_S18  |              | (16+2)       |

| RAMB16_S2_S36  |              | (32+4)       |

| RAMB16_S4_S4   |              | 4            |

| RAMB16_S4_S9   | 4            | (8+1)        |

| RAMB16_S4_S18  | 4            | (16+2)       |

| RAMB16_S4_S36  |              | (32+4)       |

| RAMB16_S9_S9   |              | (8+1)        |

| RAMB16_S9_S18  | (8+1)        | (16+2)       |

| RAMB16_S9_S36  |              | (32+4)       |

| RAMB16_S18_S18 | (16+2)       | (16+2)       |

| RAMB16_S18_S36 | (10+2)       | (32+4)       |

| RAMB16_S36_S36 | (32+4)       | (32+4)       |

Table 2-9 lists the available dual-port primitives for synthesis and simulation.Table 2-9:Dual-Port Block RAM Primitives

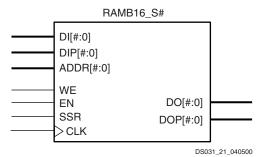

Figure 2-48 shows the generic single-port block RAM primitive. DI, DIP, ADDR, DO, and DOP are busses.

Figure 2-48: Single-Port Block RAM Primitive

Table 2-10 lists all of the available single-port primitives for synthesis and simulation.Table 2-10:Single-Port Block RAM Primitives

| Primitive  | Port Width |  |  |  |  |  |  |  |

|------------|------------|--|--|--|--|--|--|--|

| RAMB16_S1  | 1          |  |  |  |  |  |  |  |

| RAMB16_S2  | 2          |  |  |  |  |  |  |  |

| RAMB16_S4  | 4          |  |  |  |  |  |  |  |

| RAMB16_S9  | (8+1)      |  |  |  |  |  |  |  |

| RAMB16_S18 | (16+2)     |  |  |  |  |  |  |  |

| RAMB16_S36 | (32+4)     |  |  |  |  |  |  |  |

|            |            |  |  |  |  |  |  |  |

# VHDL and Verilog Instantiation

VHDL and Verilog instantiation templates are available as examples (see "VHDL and Verilog Templates" on page 207).

In VHDL, each template has a component declaration section and an architecture section. Each part of the template should be inserted within the VHDL design file. The port map of the architecture section should include the design signal names.

The SelectRAM\_Ax templates (with x = 1, 2, 4, 9, 18, or 36) are single-port modules and instantiate the corresponding RAMB16\_Sx module.

SelectRAM\_Ax\_By templates (with x = 1, 2, 4, 9, 18, or 36 and y = 1, 2, 4, 9, 18, or 36) are dual-port modules and instantiate the corresponding RAMB16\_Sx\_Sy module.

# Port Signals

Each block SelectRAM port operates independently of the other while accessing the same set of 18K-bit memory cells.

#### Clock - CLK[AIB]

Each port is fully synchronous with independent clock pins. All port input pins have setup time referenced to the port CLK pin. The data bus has a clock-to-out time referenced to the CLK pin. Clock polarity is configurable (rising edge by default).

#### Enable - EN[AIB]

The enable pin affects the read, write, and set/reset functionality of the port. Ports with an inactive enable pin keep the output pins in the previous state and do not write data to the memory cells. Enable polarity is configurable (active High by default).

## Write Enable - WE[AIB]

Both EN and WE are active when the contents of the data input bus is written to memory at the address pointed to by the address bus. The output latches are loaded or not loaded according to the write configuration (WRITE\_FIRST, READ\_FIRST, NO\_CHANGE). When inactive, a read operation occurs, and the contents of the memory cells referenced by the address bus reflect on the data-out bus, regardless of the write mode attribute. Write enable polarity is configurable (active High by default).

## Set/Reset - SSR[AIB]

The SSR pin forces the data output latches to contain the value "SRVAL" (see "Attributes" on page 205). The data output latches are synchronously asserted to 0 or 1, including the parity bit. In a 36-bit width configuration, each port has an independent SRVAL[A | B] attribute of 36 bits. This operation does not affect RAM memory cells and does not disturb write operations on the other port. Like the read and write operation, the set/reset function is active only when the enable pin of the port is active. Set/reset polarity is configurable (active High by default).

# Address Bus - ADDR[AIB]<#:0>

The address bus selects the memory cells for read or write. The width of the port determines the required address bus width, as shown in Table 2-11.

| Port Data Width | Depth  | ADDR Bus | DI Bus / DO Bus | DIP Bus / DOP Bus |

|-----------------|--------|----------|-----------------|-------------------|

| 1               | 16,384 | <13:0>   | <0>             | NA                |

| 2               | 8,192  | <12:0>   | <1:0>           | NA                |

| 4               | 4,096  | <11:0>   | <3:0>           | NA                |

| 9               | 2,048  | <10:0>   | <7:0>           | <0>               |

| 18              | 1,024  | <9:0>    | <15:0>          | <1:0>             |

| 36              | 512    | <8:0>    | <31:0>          | <3:0>             |

Table 2-11: Port Aspect Ratio

# Data-In Busses - DI[A|B]<#:0> & DIP[A|B]<#:0>

Data-in busses provide the new data value to be written into RAM. The regular data-in bus (DI) and the parity data-in bus (when available) have a total width equal to the port width. For example the 36-bit port data width is represented by DI<31:0> and DIP<3:0>, as shown in Table 2-11.

# Data-Out Busses - DO[AIB]<#:0> & DOP[AIB]<#:0>

Data-out busses reflect the contents of memory cells referenced by the address bus at the last active clock edge during a read operation. During a write operation (WRITE\_FIRST or READ\_FIRST configuration), the data-out busses reflect either the data-in busses or the stored value before write. During a write operation in NO\_CHANGE mode, data-out busses are not affected. The regular data-out bus (DO) and the parity data-out bus (DOP) (when available) have a total width equal to the port width, as shown in Table 2-11.

## **Inverting Control Pins**

For each port, the four control pins (CLK, EN, WE, and SSR) each have an individual inversion option. Any control signal can be configured as active High or Low, and the clock can be active on a rising or falling edge (active High on rising edge by default) without requiring other logic resources.

#### **Unused Inputs**

Non-connected Data and/or address inputs should be connected to logic "1".

## GSR

The global set/reset (GSR) signal of a Virtex-II device is an asynchronous global signal that is active at the end of device configuration. The GSR can also restore the initial Virtex-II state at any time. The GSR signal initializes the output latches to the INIT, or to the INIT\_A and INIT\_B value (see "Attributes" on page 205). A GSR signal has no impact on internal memory contents. Because it is a global signal, the GSR has no input pin at the functional level (block SelectRAM primitive).

# Address Mapping

Each port accesses the same set of 18,432 memory cells using an addressing scheme dependent on the width of the port. The physical RAM locations addressed for a particular width are determined using the following formula (of interest only when the two ports use different aspect ratios):

END = ((ADDR + 1) \* Width) -1 START= ADDR \* Width

Table 2-12 shows low-order address mapping for each port width.

#### Table 2-12: Port Address Mapping

| Port<br>Width | Parity<br>Locations | Data Locations |                        |   |   |   |       |  |       |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |     |

|---------------|---------------------|----------------|------------------------|---|---|---|-------|--|-------|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| 1             |                     | 31             | 1 30 29 28 27 26 25 24 |   |   |   |       |  | 23    | 22 | 21  | 20  | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 98 | 76 | 554 | 3 2 | 1 0 |

| 2             | N.A.                | 1              | 5                      | 1 | 4 | 1 | 13 12 |  | 11 10 |    | 9 8 |     | 3  | 7  |    | 6  | 5  | 5  | 5  | 4  | 3  | 2  | 1  | 0  |     |     |     |

| 4             |                     | 7 6 5 4 3 2    |                        |   |   |   |       |  |       |    |     | 1 0 |    | 0  |    |    |    |    |    |    |    |    |    |    |     |     |     |

| 8 + 1         | 3 2 1 0             |                | 3 2 1 0                |   |   |   |       |  |       |    |     | 0   |    |    |    |    |    |    |    |    |    |    |    |    |     |     |     |

| 16 + 2        | 1 0                 |                | 1 0                    |   |   |   |       |  |       |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |     |

| 32 + 4        | 0                   |                | 0                      |   |   |   |       |  |       |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |     |

# Attributes

## Content Initialization - INIT\_xx

INIT\_xx attributes define the initial memory contents. By default block SelectRAM memory is initialized with all zeros during the device configuration sequence. The 64 initialization attributes from INIT\_00 through INIT\_3F represent the regular memory contents. Each INIT\_xx is a 64-digit hex-encoded bit vector. The memory contents can be partially initialized and are automatically completed with zeros.

The following formula is used for determining the bit positions for each INIT\_xx attribute. Given yy = conversion hex-encoded to decimal (xx), INIT\_xx corresponds to the memory cells as follows:

- from [(yy + 1) \* 256] -1

- to (yy) \* 256

For example, for the attribute INIT\_1F, the conversion is as follows:

- yy = conversion hex-encoded to decimal X"1F" = 31

- from [(31+1) \* 256] -1 = 8191

- to 31 \* 256 = 7936

More examples are given in Table 2-13.

#### Table 2-13: Block SelectRAM Initialization Attributes

| Attribute | Memo  | ory Cell |

|-----------|-------|----------|

| Allibule  | from  | to       |

| INIT_00   | 255   | 0        |

| INIT_01   | 511   | 256      |

| INIT_02   | 767   | 512      |

|           |       |          |

| INIT_0E   | 3839  | 3584     |

| INIT_0F   | 4095  | 3840     |

| INIT_10   | 4351  | 4096     |

|           |       |          |

| INIT_1F   | 8191  | 7936     |

| INIT_20   | 8447  | 8192     |

|           |       |          |

| INIT_2F   | 12287 | 12032    |

| INIT_30   | 12543 | 12288    |

|           |       |          |

| INIT_3F   | 16383 | 16128    |

## Content Initialization - INITP\_xx

INITP\_xx attributes define the initial contents of the memory cells corresponding to DIP/DOP busses (parity bits). By default these memory cells are also initialized to all zeros. The eight initialization attributes from INITP\_00 through INITP\_07 represent the memory contents of parity bits. Each INITP\_xx is a 64-digit hex-encoded bit vector and behaves like a regular INIT\_xx attribute. The same formula can be used to calculate the bit positions initialized by a particular INITP\_xx attribute.

## Output Latches Initialization - INIT (INIT\_A & INIT\_B)

The INIT (single-port) or INIT\_A and INIT\_B (dual-port) attributes define the output latches values after configuration. The width of the INIT (INIT\_A & INIT\_B) attribute is the port width, as shown in Table 2-14. These attributes are hex-encoded bit vectors and the default value is 0.

## Output Latches Synchronous Set/Reset - SRVAL (SRVAL\_A & SRVAL\_B)

The SRVAL (single-port) or SRVAL\_A and SRVAL\_B (dual-port) attributes define output latch values when the SSR input is asserted. The width of the SRVAL (SRVAL\_A and SRVAL\_B) attribute is the port width, as shown in Table 2-14. These attributes are hexencoded bit vectors and the default value is 0.

| Port Data Width | DOP Bus | DO Bus | INIT / SRVAL  |

|-----------------|---------|--------|---------------|

| 1               | NA      | <0>    | 1             |

| 2               | NA      | <1:0>  | 2             |

| 4               | NA      | <3:0>  | 4             |

| 9               | <0>     | <7:0>  | (1+8) = 9     |

| 18              | <1:0>   | <15:0> | (2+16) = 18   |

| 36              | <3:0>   | <31:0> | (4 + 32) = 36 |

Table 2-14: Port Width Values

# Initialization in VHDL or Verilog Codes

Block SelectRAM memory structures can be initialized in VHDL or Verilog code for both synthesis and simulation. For synthesis, the attributes are attached to the block SelectRAM instantiation and are copied in the EDIF output file to be compiled by Xilinx Alliance Series<sup>TM</sup> tools. The VHDL code simulation uses a generic parameter to pass the attributes. The Verilog code simulation uses a defparam parameter to pass the attributes.

The XC2V\_RAMB\_1\_PORT block SelectRAM instantiation code examples (in VHDL and Verilog) illustrate these techniques (see "VHDL and Verilog Templates" on page 207).

# **Location Constraints**

Block SelectRAM instances can have LOC properties attached to them to constrain placement. Block SelectRAM placement locations differ from the convention used for naming CLB locations, allowing LOC properties to transfer easily from array to array.

The LOC properties use the following form:

```

LOC = RAMB16_X#Y#

```

The RAMB16\_X0Y0 is the bottom-left block SelectRAM location on the device.

206

# Applications

# **Creating Larger RAM Structures**

Block SelectRAM columns have specialized routing to allow cascading blocks with minimal routing delays. Wider or deeper RAM structures are achieved with a smaller timing penalty than is encountered when using normal routing resources.

The CORE Generator program offers the designer a painless way to generate wider and deeper memory structures using multiple block SelectRAM instances. This program outputs VHDL or Verilog instantiation templates and simulation models, along with an EDIF file for inclusion in a design.

## Multiple RAM Organizations

The flexibility of block SelectRAM memories allows designs with various types of RAM in addition to regular configurations. Application notes at <u>www.xilinx.com</u> describe some of these designs, with VHDL and Verilog reference designs included.

Virtex-II block SelectRAM can be used as follows:

- Two independent single-port RAM resources

- One 72-bit single-port RAM resource

- One triple-port (1 Read/Write and 2 Read ports) RAM resource

Application notes with VHDL and Verilog reference designs at <u>www.xilinx.com</u> also describe other implementations using block SelectRAM memory, such as:

- <u>xapp258</u> "FIFOs Using Virtex-II Block RAM"

- <u>xapp260</u> "Fast Read/Write CAM Solution"

# VHDL and Verilog Templates

VHDL and Verilog templates are available for all single-port and dual-port primitives. The A and B numbers indicate the width of the ports.

The following are single-port templates:

- SelectRAM\_A1

- SelectRAM\_A2

- SelectRAM\_A4

- SelectRAM\_A9

- SelectRAM\_A18

- SelectRAM\_A36

The following are dual-port templates:

- SelectRAM\_A1\_B1

- SelectRAM\_A1\_B2

- SelectRAM\_A1\_B4

- SelectRAM\_A1\_B9

- SelectRAM\_A1\_B18

- SelectRAM\_A1\_B36

- SelectRAM\_A2\_B2

- SelectRAM\_A2\_B4

- SelectRAM\_A2\_B9

- SelectRAM\_A2\_B18

- SelectRAM\_A2\_B36

- SelectRAM\_A4\_B4

- SelectRAM\_A4\_B9

- SelectRAM\_A4\_B18

- SelectRAM\_A4\_B36

- SelectRAM\_A9\_B9

- SelectRAM\_A9\_B18

- SelectRAM\_A9\_B36

- SelectRAM\_A18\_B18

- SelectRAM\_A18\_B36

- SelectRAM\_A36\_B36

## VHDL Template

As an example, the XC2V\_RAMB\_1\_PORT.vhd file uses the SelectRAM\_A36 template:

```

-- Module: XC2V_RAMB_1_PORT

-- Description: 18Kb Block SelectRAM example

-- Single Port 512 x 36 bits

-- Use template "SelectRAM_A36.vhd"

- -

-- Device: Virtex-II Family

_____

library IEEE;

use IEEE.std logic 1164.all;

- -

-- Syntax for Synopsys FPGA Express

-- pragma translate off

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

-- pragma translate on

entity XC2V RAMB 1 PORT is

port (

DATA_IN : in std_logic_vector (35 downto 0);

ADDRESS : in std_logic_vector (8 downto 0);

ENABLE: in std_logic;

WRITE_EN : in std_logic;

SET_RESET : in std_logic;

CLK : in std logic;

DATA OUT

: out std logic vector (35 downto 0)

);

end XC2V RAMB 1 PORT;

- -

architecture XC2V_RAMB_1_PORT_arch of XC2V_RAMB_1_PORT is

- -

-- Components Declarations:

component BUFG

port (

I: in std logic;

0: out std logic

);

end component;

- -

-- Syntax for Synopsys FPGA Express

component RAMB16 S36

-- pragma translate off

generic (

-- "Read during Write" attribute for functional simulation

WRITE_MODE : string := "READ_FIRST" ; -- WRITE_FIRST(default)/

READ_FIRST/ NO_CHANGE

```

#

```

-- Output value after configuration

INIT : bit vector(35 downto 0) := X"000000000";

-- Output value if SSR active

SRVAL : bit vector(35 downto 0) := X"012345678";

-- Plus bits initial content

INITP 00 : bit vector(255 downto 0) :=

INITP 01 : bit vector(255 downto 0) :=

INITP 02 : bit vector(255 downto 0) :=

INITP 03 : bit vector(255 downto 0) :=

INITP 04 : bit vector(255 downto 0) :=

INITP 05 : bit vector(255 downto 0) :=

INITP 06 : bit vector(255 downto 0) :=

INITP 07 : bit vector(255 downto 0) :=

-- Regular bits initial content

INIT 00 : bit vector(255 downto 0) :=

INIT 01 : bit vector(255 downto 0) :=

INIT 02 : bit vector(255 downto 0) :=

... (cut)

INIT_3E : bit_vector(255 downto 0) :=

INIT_3F : bit_vector(255 downto 0) :=

);

-- pragma translate_on

port (

DI

: in std_logic_vector (31 downto 0);

DIP

: in std_logic_vector (3 downto 0);

ADDR

: in std logic vector (8 downto 0);

ΕN

: in STD LOGIC;

: in STD LOGIC;

WE

SSR

: in STD_LOGIC;

CLK

: in STD LOGIC;

DO

: out std_logic_vector (31 downto 0);

: out std logic vector (3 downto 0)

DOP

);

end component;

-- Attribute Declarations:

attribute WRITE_MODE : string;

attribute INIT: string;

attribute SRVAL: string;

attribute INITP 00: string;

attribute INITP 01: string;

attribute INITP 02: string;

attribute INITP 03: string;

attribute INITP 04: string;

attribute INITP_05: string;

attribute INITP 06: string;

attribute INITP 07: string;

```

```

attribute INIT_00: string;

attribute INIT 01: string;

attribute INIT 02: string;

... (cut)

attribute INIT_3E: string;

attribute INIT 3F: string;

- -

-- Attribute "Read during Write mode" = WRITE FIRST(default) /

READ FIRST/ NO CHANGE

attribute WRITE MODE of U RAMB16 S36: label is "READ FIRST";

attribute INIT of U RAMB16 S36: label is "000000000";

attribute SRVAL of U RAMB16 S36: label is "012345678";

-- RAMB16 memory initialization for Alliance

-- Default value is "0" / Partial initialization strings are padded

-- with zeros to the left

attribute INITP 00 of U RAMB16 S36: label is

attribute INITP 01 of U RAMB16 S36: label is

attribute INITP 02 of U RAMB16 S36: label is

attribute INITP 03 of U RAMB16 S36: label is

attribute INITP 04 of U RAMB16 S36: label is

attribute INITP 05 of U RAMB16 S36: label is

attribute INITP_06 of U_RAMB16_S36: label is

attribute INITP 07 of U RAMB16 S36: label is

- -

attribute INIT 00 of U RAMB16 S36: label is

attribute INIT_01 of U_RAMB16_S36: label is

attribute INIT_02 of U_RAMB16_S36: label is

... (cut)

attribute INIT_3E of U_RAMB16_S36: label is

attribute INIT 3F of U RAMB16 S36: label is

- -

- -

-- Signal Declarations:

- -

-- signal VCC : std logic;

-- signal GND : std_logic;

signal CLK BUFG: std logic;

signal INV SET RESET : std logic;

- -

begin

-- VCC <= '1';

-- GND <= '0';

-- Instantiate the clock Buffer

U BUFG: BUFG

port map (

I => CLK,

```

O => CLK BUFG

# XILINX®

```

);

- -

-- Use of the free inverter on SSR pin

INV SET RESET <= NOT SET RESET;

-- Block SelectRAM Instantiation

U RAMB16 S36: RAMB16 S36

port map (

=> DATA IN (31 downto 0), -- insert 32 bits data-in bus

DI

(<31 downto 0>)

=> DATA IN (35 downto 32), -- insert 4 bits parity data-

DIP

in bus (or <35 downto 32>)

ADDR => ADDRESS (8 downto 0), -- insert 9 bits address bus

EN

=> ENABLE, -- insert enable signal

=> WRITE EN, -- insert write enable signal

WE

=> INV_SET_RESET, -- insert set/reset signal

SSR

=> CLK_BUFG, -- insert clock signal

CLK

=> DATA OUT (31 downto 0), -- insert 32 bits data-out bus

DO

(<31 downto 0>)

=> DATA_OUT (35 downto 32) -- insert 4 bits parity data-

DOP

out bus (or <35 downto 32>)

);

_ _

end XC2V_RAMB_1_PORT_arch;

_____

```

## Verilog Template

// Module: XC2V\_RAMB\_1\_PORT // Description: 18Kb Block SelectRAM-II example // Single Port 512 x 36 bits // Use template "SelectRAM A36.v" 11 // Device: Virtex-II Family -----//----module XC2V\_RAMB\_1\_PORT (CLK, SET\_RESET, ENABLE, WRITE\_EN, ADDRESS, DATA\_IN, DATA\_OUT); input CLK, SET\_RESET, ENABLE, WRITE\_EN; input [35:0] DATA\_IN; input [8:0] ADDRESS; output [35:0] DATA\_OUT; wire CLK\_BUFG, INV\_SET\_RESET; //Use of the free inverter on SSR pin assign INV\_SET\_RESET = ~SET\_RESET; // initialize block ram for simulation // synopsys translate off defparam //"Read during Write" attribute for functional simulation U RAMB16 S36.WRITE MODE = "READ FIRST", //WRITE FIRST(default)/ READ FIRST/ NO CHANGE //Output value after configuration U RAMB16 S36.INIT = 36'h00000000, //Output value if SSR active U\_RAMB16\_S36.SRVAL = 36'h012345678,

#

```

//Plus bits initial content

U RAMB16 S36.INITP 00 =

U RAMB16 S36.INITP 01 =

U RAMB16 S36.INITP 02 =

U RAMB16 S36.INITP 03 =

U RAMB16 S36.INITP 04 =

U RAMB16 S36.INITP 05 =

U RAMB16 S36.INITP 06 =

U RAMB16 S36.INITP 07 =

//Regular bits initial content

U RAMB16 S36.INIT 00 =

U RAMB16 S36.INIT 01 =

U RAMB16 S36.INIT 02 =

...<cut>

U RAMB16 S36.INIT 3E =

U RAMB16 S36.INIT 3F =

// synopsys translate on

//Instantiate the clock Buffer

BUFG U BUFG ( .I(CLK), .O(CLK BUFG));

//Block SelectRAM Instantiation

RAMB16 S36 U RAMB16 S36 ( .DI(DATA IN[31:0]),

.DIP(DATA_IN-PARITY[35:32]),

.ADDR (ADDRESS) ,

.EN(ENABLE),

.WE(WRITE EN),

.SSR(INV_SET_RESET),

.CLK(CLK BUFG),

.DO(DATA_OUT[31:0]),

.DOP(DATA OUT-PARITY[35:32]));

// synthesis attribute declarations

/* synopsys attribute

WRITE_MODE "READ_FIRST"

INIT "00000000"

SRVAL "012345678"

INITP 00

INITP 01

INITP 02

INITP 03

```

#### INITP\_04

INIT\_00

INIT 3E

endmodule