# **Using Digitally Controlled Impedance (DCI)**

# Introduction

As FPGAs get bigger and system clock speeds get faster, PCB board design and manufacturing has become more difficult. With ever faster edge rates, maintaining signal integrity becomes a critical issue. Designers must make sure that most PC board traces are terminated properly to avoid reflections or ringing.

To terminate a trace, resistors are traditionally added to make the output and/or input match the impedance of the receiver or driver to the impedance of the trace. However, due to the increase in the device I/O counts, adding resistors close to the device pins increases the board area and component count and might even be physically impossible. To address these issues and to achieve better signal integrity, Xilinx developed a new I/O technology for the Virtex-II device family, Digitally Controlled Impedance (DCI).

DCI adjusts the output impedance or input termination to accurately match the characteristic impedance of the transmission line. DCI actively adjusts the impedance of the I/O to equal an external reference resistance. This compensates for changes in I/O impedance due to process variation. It also continuously adjusts the impedance of the I/O to compensate for variations of temperature and supply voltage fluctuations.

In the case of controlled impedance drivers, DCI controls the driver impedance to match two reference resistors, or optionally, to match half the value of these reference resistors. DCI eliminates the need for external termination resistors.

DCI provides the termination for transmitters or receivers. This eliminates the need for termination resistors on the board, reduces board routing difficulties and component count, and improves signal integrity by eliminating stub reflection. Stub reflection occurs when termination resistors are located too far from the end of the transmission line. With DCI, the termination resistors are as close as possible to the output driver or the input buffer, thus, eliminating stub reflections completely.

# Xilinx DCI

DCI uses two multi-purpose reference pins in each bank to control the impedance of the driver or the parallel termination value for all of the I/Os of that bank. The N reference pin (VRN) must be pulled up to  $V_{CCO}$  by a reference resistor, and the P reference pin (VRP) must be pulled down to ground by another reference resistor. The value of each reference resistor should be equal to the characteristic impedance of the PC board traces, or should be twice that value (configuration option).

When a DCI I/O standard is used on a particular bank, the two multi-purpose reference pins cannot be used as regular I/Os. however, if DCI I/O standards are not used in the bank, these pins are available as regular I/O pins. Check the Virtex-II pinout for detailed pin descriptions.

DCI adjusts the impedance of the I/O by selectively turning transistors in the I/Os on or off. The impedance is adjusted to match the external reference resistors. The impedance adjustment process has two phases. The first phase, which compensates for process variations, is done during the device startup sequence. The second phase, which maintains the impedance in response to temperature and supply voltage changes, begins immediately after the first phase and continues indefinitely, even while the part is operating. By default, the DONE pin does not go High until the impedance adjustment process has completed.

For controlled impedance output drivers, the impedance can be adjusted either to match the reference resistors or half the resistance of the reference resistors. For on-chip termination, the termination is always adjusted to match the reference resistors. DCI can configure output drivers to be the following types:

- 1. Controlled Impedance Driver (Source Termination)

- 2. Controlled Impedance Driver with Half Impedance (Source Termination)

It can also configure inputs to have he following types of on-chip terminations:

- 1. Termination to V<sub>CCO</sub> (Single Termination)

- 2. Termination to V<sub>CCO</sub>/2 (Split Termination, Thevenin equivalent)

For bidirectional operation, both ends of the line can be DCI-terminated permanently:

- 1. Termination to V<sub>CCO</sub> (Single Termination)

- 2. Termination to V<sub>CCO</sub>/2 (Split Termination, Thevenin equivalent)

Alternatively, bidirectional point-to-point lines can use controlled-impedance drivers (with 3-state buffers) on both ends.

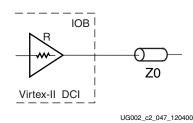

### Controlled Impedance Driver (Source Termination)

Some I/O standards, such as LVTTL, LVCMOS, etc., must have a drive impedance that matches the characteristic impedance of the driven line. DCI can provide a controlled impedance output drivers that eliminate reflections without an external source termination. The impedance is set by the external reference resistors, whose resistance should be equal to the trace impedance. Figure 2-96 illustrates a controlled impedance driver inside Virtex-II device. The DCI I/O standards that support Controlled Impedance Driver are: LVDCI\_15, LVDCI\_18, LVDCI\_25, and LVDCI\_33.

Figure 2-96: Controlled Impedance Driver

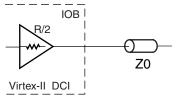

### Controlled Impedance Driver With Half Impedance (Source Termination)

DCI can also provide drivers with one half of the impedance of the reference resistors. The DCI I/O standards that support controlled impedance driver with half impedance are: LVDCI\_DV2\_15, LVDCI\_DV2\_18, LVDCI\_DV2\_25, and LVDCI\_DV2\_33

Figure 2-97 illustrates a controlled driver with half impedance inside a Virtex-II device.

UG002\_c2\_052\_120400

Figure 2-97: Controlled Impedance Driver With Half Impedance

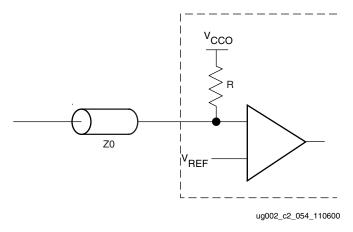

# Termination to V<sub>CCO</sub> (Single Termination)

Some I/O standards, such as HSTL Class III, IV, etc., require an input termination to  $V_{CCO}$ . See Figure 2-98.

*Figure 2-98:* Single Termination Without DCI

DCI can provide this termination to  $V_{CCO}$  using single termination. The termination resistance is set by the reference resistors. For GTL and HSTL standards, they should be controlled by 50-ohm reference resistors. The DCI I/O standards that support single termination are: GTL\_DCI, GTLP\_DCI, HSTL\_III\_DCI, and HSTL\_IV\_DCI.

Figure 2-99 illustrates single termination inside a Virtex-II device.

Figure 2-99: Single Termination Using DCI

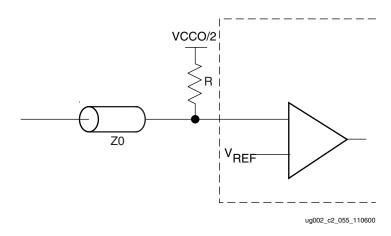

# Termination to V<sub>CCO</sub>/2 (Split Termination)

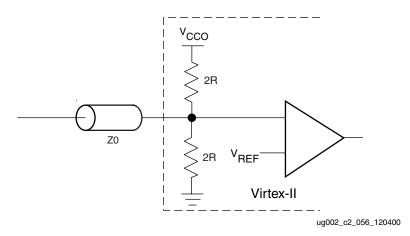

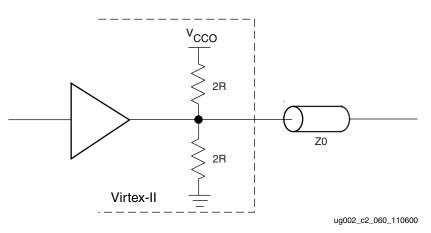

Some I/O standards, such as HSTL Class I, II, SSTL3\_I, etc., require an input termination voltage of  $V_{CCO}/2$ . See Figure 2-100.

Figure 2-100: Split Termination Without DCI

This is equivalent to having a split termination composed of two resistors. One terminates to  $V_{CCO}$ , the other to ground. The resistor values are 2R. DCI provides termination to  $V_{CCO}/2$  using split termination. The termination resistance is set by the external reference resistors, i.e., the resistors to  $V_{CC}$  and ground are each twice the reference resistor value. If users are planning to use HSTL or SSTL standards, the reference resistors should be 50-ohms. The DCI I/O standards that support split termination are: HSTL\_I\_DCI, HSTL\_II\_DCI, SSTL2\_I\_DCI, SSTL2\_II\_DCI, SSTL3\_I\_DCI, and SSTL3\_II\_DCI.

Figure 2-101 illustrates split termination inside a Virtex-II device.

Figure 2-101: Split Termination Using DCI

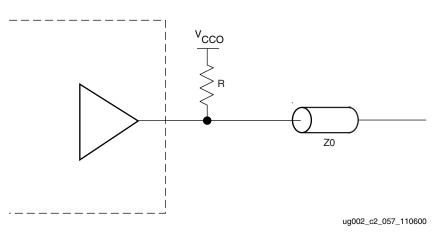

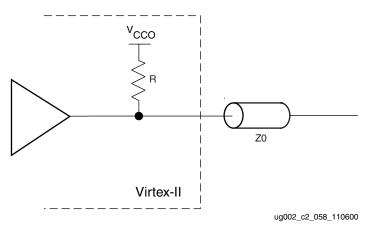

# **Driver With Single Termination**

Some I/O standards, such as HSTL Class IV, require an output termination to  $V_{CCO}$ . Figure 2-102 illustrates the output termination to  $V_{CCO}$ .

Figure 2-102: Driver With Single Termination Without DCI

DCI can provide this termination to  $V_{CCO}$  using single termination. In this case, DCI only controls the impedance of the termination, but not the driver. If users are planning to use GTL or HSTL standards, the external reference resistors should be 50-ohms. The DCI I/O standards that support a driver with single termination are: GTL\_DCI, GTLP\_DCI, and HSTL\_IV\_DCI.

Figure 2-103 illustrates a driver with single termination inside a Virtex-II device

Figure 2-103: Driver With Single Termination Using DCI

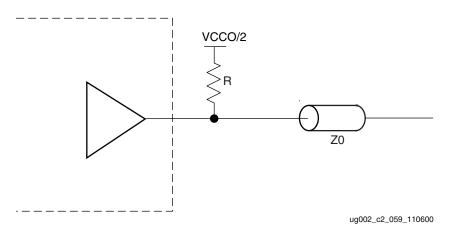

# **Driver With Split Termination**

Some I/O standards, such as HSTL Class II, require an output termination to  $V_{CCO}/2$ . See Figure 2-104.

Figure 2-104: Driver With Split Terminating

DCI can provide this termination to  $V_{CCO}/2$  using split termination. It only controls the impedance of the termination, but not the driver. For HSTL or SSTL standards, the external reference resistors should be 50-ohms. The DCI I/O standards that support a Driver with split termination are: HSTL\_II\_DCI, SSTL2\_II\_DCI, and SSTL3\_II\_DCI.

Figure 2-105 illustrates a driver with split termination inside a Virtex-II device.

Figure 2-105: Driver With Split Termination Using DCI

# Software Support

This section lists the valid DCI I/O buffer library components and describes how to use DCI in the Xilinx software.

# DCI I/O Buffer Library Components

The DCI input buffer library components, including global clock buffer, are the following:

- IBUFG\_GTLP\_DCI

- IBUFG\_GTL\_DCI

- IBUFG\_HSTL\_I\_DCI

- IBUFG\_HSTL\_II\_DCI

- IBUFG\_HSTL\_III\_DCI

- IBUFG\_HSTL\_IV\_DCI

- IBUFG\_LVDCI\_15

- IBUFG\_LVDCI\_18

- IBUFG\_LVDCI\_25

- IBUFG\_LVDCI\_33

- IBUFG\_LVDCI\_DV2\_15

- IBUFG\_LVDCI\_DV2\_18

- IBUFG\_LVDCI\_DV2\_25

- IBUFG\_LVDCI\_DV2\_33

- IBUFG\_SSTL2\_I\_DCI

- IBUFG\_SSTL2\_II\_DCI

- IBUFG\_SSTL3\_I\_DCI

- IBUFG\_SSTL3\_II\_DCI

- IBUF\_GTLP\_DCI

- IBUF\_GTL\_DCI

- IBUF\_HSTL\_I\_DCI

- IBUF\_HSTL\_II\_DCI

- IBUF\_HSTL\_III\_DCI

- IBUF\_HSTL\_IV\_DCI

- IBUF\_LVDCI\_15

- IBUF\_LVDCI\_18

- IBUE LVDCL 25

- IBUF\_LVDCI\_25IBUF\_LVDCI\_33

- IBUF\_LVDCI\_33

- IBUF\_LVDCI\_DV2\_15

- IBUF\_LVDCI\_DV2\_18

- IBUF\_LVDCI\_DV2\_25

- IBUF\_LVDCI\_DV2\_33

- IBUF\_SSTL2\_I\_DCI

- IBUF\_SSTL2\_II\_DCI

- IBUF\_SSTL3\_I\_DCI

- IBUF\_SSTL3\_II\_DCI

The following are DCI output buffer library components:

- OBUF\_GTLP\_DCI

- OBUF\_GTL\_DCI

- OBUF\_HSTL\_I\_DCI

- OBUF\_HSTL\_II\_DCI

- OBUF\_HSTL\_III\_DCI

- OBUF\_HSTL\_IV\_DCI

- OBUF\_LVDCI\_15

- OBUF\_LVDCI\_18

- OBUF\_LVDCI\_25

- OBUF\_LVDCI\_33

- OBUF\_LVDCI\_DV2\_15

- OBUF\_LVDCI\_DV2\_18

- OBUF\_LVDCI\_DV2\_25

- OBUF\_LVDCI\_DV2\_33

- OBUF\_SSTL2\_I\_DCI

- OBUF\_SSTL2\_II\_DCI

- OBUF\_SSTL3\_I\_DCI

- OBUF\_SSTL3\_II\_DCI

The following are DCI 3 state output buffer library components:

- OBUFT\_GTLP\_DCI

- OBUFT\_GTL\_DCI

- OBUFT\_HSTL\_I\_DCI

- OBUFT\_HSTL\_II\_DCI

- OBUFT\_HSTL\_III\_DCI

- OBUFT\_HSTL\_IV\_DCI

- OBUFT\_LVDCI\_15

- OBUFT\_LVDCI\_18

- OBUFT\_LVDCI\_25

- OBUFT\_LVDCI\_33

- OBUFT\_LVDCI\_DV2\_15

- OBUFT\_LVDCI\_DV2\_18

- OBUFT\_LVDCI\_DV2\_25

- OBUFT\_LVDCI\_DV2\_33

- OBUFT\_SSTL2\_I\_DCI

- OBUFT\_SSTL2\_II\_DCI

- OBUFT\_SSTL3\_I\_DCI

- OBUFT\_SSTL3\_II\_DCI

The following are DCI I/O buffer library components:

- IOBUF\_GTLP\_DCI

- IOBUF\_GTL\_DCI

- IOBUF\_HSTL\_II\_DCI

- IOBUF\_HSTL\_IV\_DCI

- IOBUF\_SSTL2\_II\_DCI

- IOBUF\_SSTL3\_II\_DCI

- IOBUF\_LVDCI\_15

- IOBUF\_LVDCI\_18

- IOBUF\_LVDCI\_25

- IOBUF\_LVDCI\_33

- IOBUF\_LVDCI\_DV2\_15

- IOBUF\_LVDCI\_DV2\_18

- IOBUF\_LVDCI\_DV2\_25

- IOBUF\_LVDCI\_DV2\_33

### How to Use DCI in the Software

There are two ways for users to use DCI for Virtex-II devices:

- 1. Use the IOSTANDARD attribute in the constraint file.

- 2. Instantiate DCI input or output buffers in the HDL code.

### **IOSTANDARD** Attribute

The IOSTANDARD attribute can be entered through the NCF or UCF file. The syntax is as follows:

NET <net name> IOSTANDARD = LVDCI\_25;

Where <net name> is the name between the IPAD and IBUF or OPAD or OBUF. For HDL designs, this name is the same as the port name.

The following are valid DCI attributes for output drivers:

- LVDCI\_15

- LVDCI\_18

- LVDCI\_25

- LVDCI\_33

- LVDCI\_DV2\_15

- LVDCI\_DV2\_15

- LVDCI\_DV2\_25

- LVDCI\_DV2\_33

The following are valid DCI attributes for terminations:

- GTL\_DCI

- GTLP\_DCI

- HSTL\_I\_DCI

- HSTL\_II\_DCI

- HSTL\_III\_DCI

- HSTL\_IV\_DCI

- SSTL2\_I\_DCI

- SSTL2\_II\_DCI

- SSTL3\_I\_DCI

- SSTL3\_II\_DCI

### **VHDL Example**

Instantiating DCI input and output buffers is the same as instantiating any other I/O buffers. Users must make sure that the correct I/O buffer names are used and follow the standard syntax of instantiation.

For example, to instantiate a HSTL Class I output DCI buffer, the following syntax can be used:

HSTL\_DCI\_buffer: OBUF\_HSTL\_I\_DCI port map (I=>data\_out, O=>data\_out\_DCI); Below is an example VHDL code that instantiates four 2.5 V LVDCI drivers and four HSTL Class I outputs.

```

-- Module: DCI TEST

- -

-- Description: VHDL example for DCI SelectI/O

-- Device: Virtex-II Family

------

------

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic unsigned.all;

entity dci_test is

port (clk, reset, ce, control : in std logic;

A, B : in std_logic_vector (3 downto 0);

Dout : out std_logic_vector (3 downto 0);

muxout : out std logic vector (3 downto 0));

end dci_test;

architecture dci arch of dci test is

--DCI output buffer component declaration

component OBUF LVDCI 25 port (I : in std logic; 0 : out std logic);

end component;

attribute syn black box of OBUF LVDCI 25 : component is true;

attribute black box pad pin of OBUF LVDCI 25 : component is "O";

--HSTL Class I DCI output buffer component declaration

component OBUF HSTL I DCI port (I : in std logic; O: out std logic);

end component;

attribute syn black box of OBUF HSTL I DCI : component is true;

attribute black box pad pin of OBUF HSTL I DCI : component is "O";

signal muxout_int : std_logic_vector (3 downto 0);

signal dout int : std logic vector (3 downto 0);

begin

process (clk, reset)

begin

if (reset = '1') then

dout int<="0000";</pre>

elsif (clk'event and clk='1') then

```

#

```

dout_int<=dout_int+1;</pre>

end if;

end process;

process (controls, A, B, DOUT_INT)

begin

if (control='1') then

muxout int<=A and B;</pre>

else

muxout_int<=Dout_int;</pre>

end if;

end process;

U0 : OBUF LVDCI 25 port map(

I=>dout int(0),

O = > dout(0));

U1 : OBUF LVDCI 25 port map(

I=>dout_int(1),

O=>dout(1));

U2 : OBUF LVDCI 25 port map(

I=>dout int(2),

O=>dout(2));

U3 : OBUF LVDCI 25 port map(

I=>dout_int(3),

O=>dout(3));

K0 : OBUF_HSTL_I_DCI port map(

I=>muxout int(0),

O=>muxout(0));

K1 : OBUF HSTL I DCI port map(

I=>muxout int(1),

O = > muxout(1));

K2 : OBUF_HSTL_I_DCI port map(

I=>muxout int(2),

O=>muxout(2));

K3 : OBUF HSTL I DCI port map(

I=>muxout_int(3),

O = > muxout(3));

```

# end dci\_arch;

# DCI in Virtex-II Hardware

DCI only works with certain single-ended I/O standards and does not work with any differential I/O standard. DCI supports the following Virtex-II standards:

LVDCI, LVDCI\_DV2, GTL\_DCI, GTLP\_DCI, HSTL\_I\_DCI, HSTL\_II\_DCI, HSTL\_III\_DCI, HSTL\_IV\_DCI, SSTL2\_I\_DCI, SSTL2\_II\_DCI, SSTL3\_I\_DCI, and SSTL3\_II\_DCI.

To correctly use DCI in a Virtex-II device, users must follow the following rules:

- 1.  $V_{CCO}$  pins must be connected to the appropriate  $V_{CCO}$  voltage based on the IOSTANDARDs in that bank.

- 2. Correct DCI I/O buffers must be used in the software either by using IOSTANDARD attributes or instantiations in the HDL code.

- 3. External reference resistors must be connected to multi-purpose pins (VRN and VRP) in the bank cannot be used as regular I/Os. Refer to the Virtex-II pinouts for the

specific pin locations. Pin VRN must be pulled up to  $V_{CCO}$  by its reference resistor. Pin VRP must be pulled down to ground by its reference resistor.

- 4. The value of the external reference resistors should be selected to give the desired output impedance. If using GTL\_DCI, HSTL\_DCI, or SSTL\_DCI I/O standards, then they should be 50 ohms.

- 5. The values of the reference resistors must be within the supported range. Availability of this range is planned for the next release of the <u>Virtex-II Data Sheet</u>. ( $\sim$ 30 to 100  $\Omega$ )

- 6. Follow the DCI I/O banking rules.

The DCI I/O banking rules are the following:

- 1. V<sub>REF</sub> must be compatible for all of the inputs in the same bank.

- 2. V<sub>CCO</sub> must be compatible for all of the inputs and outputs in the same bank.

- 3. No more than one DCI I/O standard using Single Termination type is allowed per bank.

- 4. No more than one DCI I/O standard using Split Termination type is allowed per bank.

- 5. Single Termination and Split Termination, Controlled Impedance Driver, and Controlled Impedance Driver with Half Impedance can co-exist in the same bank.

The behavior of DCI 3-state outputs is as follows:

If a LVDCI or LVDCI\_DV2 driver is in 3-state, the driver is 3-stated. If a Driver with Single or Split Termination is in 3-state, the driver is 3-stated but the termination resistor remains.

The following section lists any special care actions that must be taken for each DCI I/O standard.

### LVDCI\_15, LVDCI\_18, LVDCI\_25, LVDCI\_33

Using these buffers configures the outputs as controlled impedance drivers. The number extension at the end indicates the V<sub>CCO</sub> voltage that should be used. For example, 15 means V<sub>CCO</sub>=1.5 V, etc. There is no slew rate control or drive strength settings for LVDCI drivers.

# LVDCI\_DV2\_15, LVDCI\_DV2\_18, LVDCI\_DV2\_25, LVDCI\_DV\_33

Using these buffers configures the outputs as controlled drivers with half impedance. The number extension at the end indicates the  $V_{CCO}$  voltage that should be used. For example, 15 means  $V_{CCO}$ =1.5 V, etc. There is no slew rate control or drive strength settings for LVDCI\_DV2 drivers.

### GTL\_DCI

GTLP does not require a V<sub>CCO</sub> voltage. However, for GTL\_DCI, V<sub>CCO</sub> must be connected to 1.2 V. GTL\_DCI provides single termination to V<sub>CCO</sub> for inputs or outputs.

# GTLP\_DCI

GTL+ does not require a V<sub>CCO</sub> voltage. However, for GTLP\_DCI, V<sub>CCO</sub> must be connected to 1.5 V. GTLP\_DCI provides single termination to V<sub>CCO</sub> for inputs or outputs.

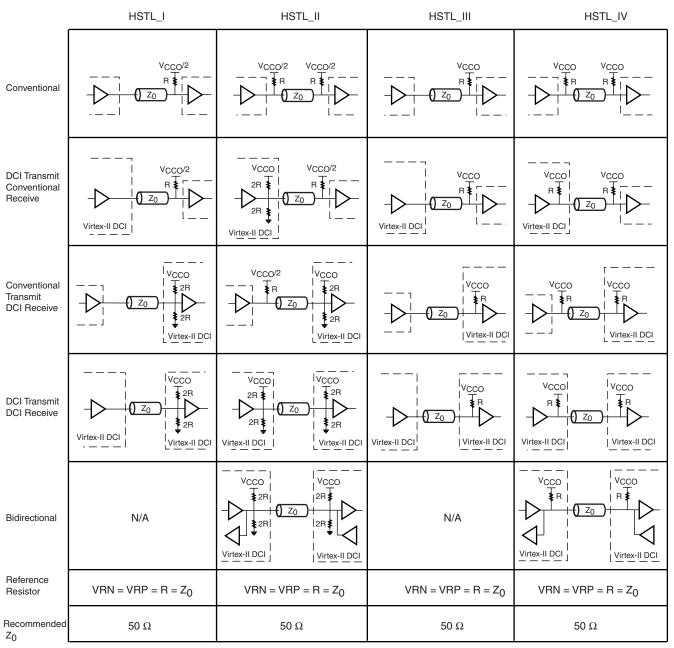

# HSTL\_I\_DCI, HSTL\_III\_DCI

HSTL\_I\_DCI provides split termination to  $V_{\rm CCO}/2$  for inputs. HSTL\_III\_DCI provides single termination to  $V_{\rm CCO}$  for inputs.

# HSTL\_II\_DCI, HSTL\_IV\_DCI

HSTL\_II\_DCI provides split termination to  $V_{CCO}/2$  for inputs or outputs. HSTL\_IV\_ DCI provides single termination to  $V_{CCO}$  for inputs or outputs.

2

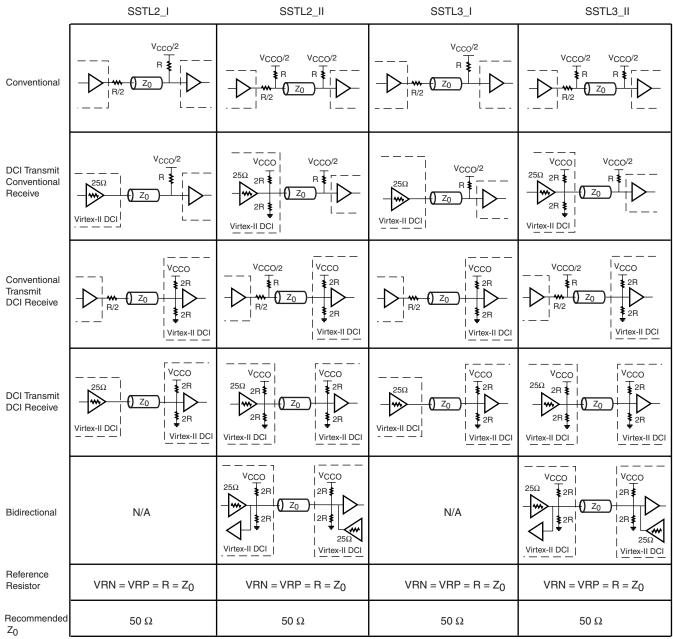

# SSTL2\_I\_DCI, SSTL3\_I\_DCI

SSTL2\_I\_DCI and SSTL3\_I\_DCI provide split termination to  $\rm V_{CCO}/2$  for inputs. Then I/O standards are SSTL compatible.

# SSTL2\_II\_DCI, SSTL3\_II\_DCI

SSTL2\_II\_DCI and SSTL3\_II\_DCI provide split termination to  $\rm V_{CCO}/2$  for inputs. Then I/O standards are SSTL compatible.

Figure 2-106 provides examples illustrating the use of the HSTL\_I\_DCI, HSTL\_II\_DCI, HSTL\_III\_DCI, and HSTL\_IV\_DCI I/O standards.

DS031\_65a\_100201

# Figure 2-107 provides examples illustrating the use of the SSTL2\_I\_DCI, SSTL2\_II\_DCI, SSTL3\_I\_DCI, and SSTL3\_II\_DCI I/O standards.

DS031\_65b\_100201

Figure 2-107: SSTL DCI Usage Examples