# **Using Global Clock Networks**

## Introduction

Virtex-II devices support very high frequency designs and thus require low-skew advanced clock distribution. With device density up to 10 million system gates, numerous global clocks are necessary in most designs. Therefore, to provide a uniform and portable solution (soft-IP), all Virtex-II devices from XC2V40 to XC2V8000 have 16 global clock buffers and support 16 global clock domains. Up to eight of these clocks can be used in any quadrant of the device by the synchronous logic elements (that is, registers, 18Kb block RAM, pipeline multipliers) and the IOBs. The software tools place and route these global clocks automatically.

If the design uses between 8 and 16 clocks, it must be partitioned into quadrants, with up to 8 clocks per quadrant. If more than 16 clocks are required, the backbone (24 horizontal and vertical long lines routing resources) can be used as additional clock network.

In addition to clock distribution, the 16 clock buffers are also "glitch-free" synchronous 2:1 multiplexers. These multiplexers are capable of switching between two asynchronous (or synchronous) clocks at any time. No particular phase relations between the two clocks are needed. The clock multiplexers can also be configured as a global clock buffer with a clock enable. The clock can be stopped High or Low at the clock buffer output.

## **Clock Distribution Resources**

The various resources available to manage and distribute the clocks include:

- 16 clock pads that can be used as regular user I/Os if not used as clock inputs. The 16 clock pads can be configured for any I/O standard, including differential standards (for example, LVDS, LVPECL, and so forth).

- 16 "IBUFG" elements that represent the clock inputs in a VHDL or Verilog design.

- 8 "IBUFGDS" elements (that is, attributes LVPECL\_33, LVDS\_25, LVDS\_33, LDT\_25, or ULVDS\_25) that represent the differential clock input pairs in a VHDL or Verilog design. Each IBUFGDS replaces two IBUFG elements.

- 4 to 12 Digital Clock Managers (DCMs), depending on the device size, to de-skew and generate the clocks. For more information on DCMs, see "Using Digital Clock Managers (DCMs)" on page 175.

- 16 "BUFGMUX" elements that can consist of up to 16 global clock buffers (BUFG), global clock buffers with a clock enable (BUFGCE), or global clock multiplexers (BUFGMUX).

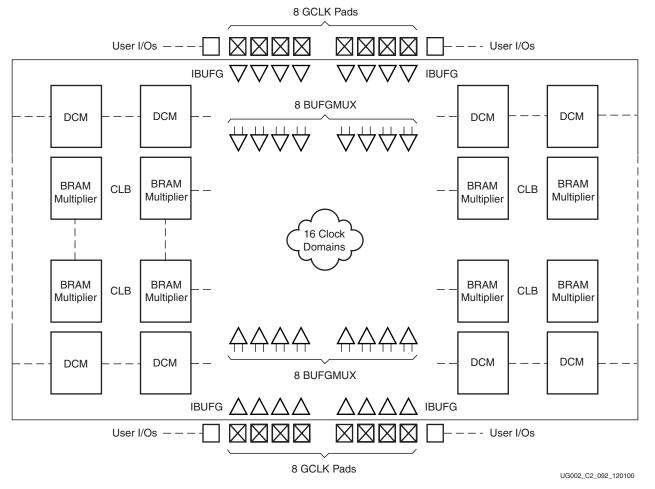

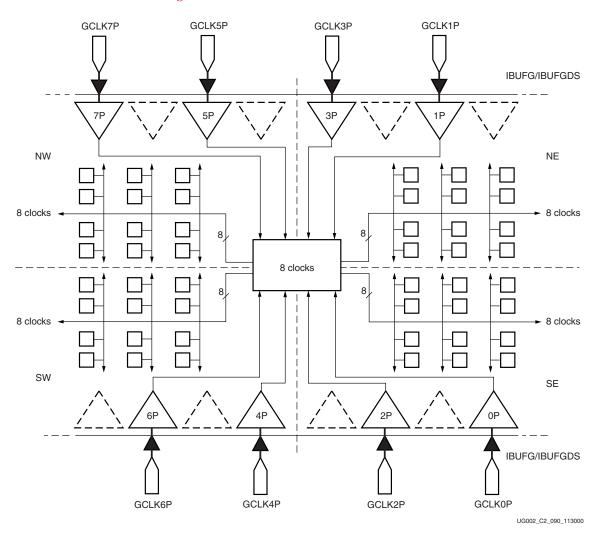

Figure 2-1 illustrates the placement of these clock resources in Virtex-II devices (the XC2V250 through the XC2V2000) that have eight DCMs.

Figure 2-1: Clock Resources in Virtex-II Devices

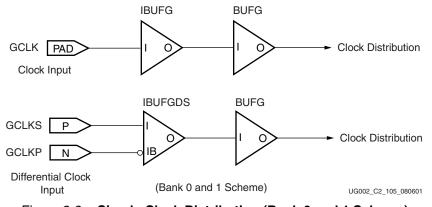

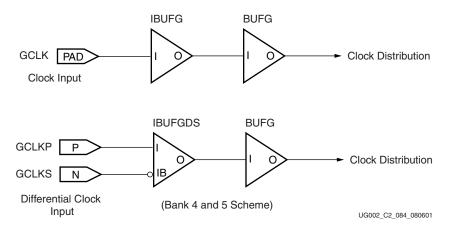

The simple scheme to distribute an external clock in the device is to implement a clock pad with an IBUFG input buffer connected to a BUFG global buffer, as shown in Figure 2-2 and Figure 2-3. The primary (GCLKP) and secondary (GCLKS) clock pads have no relationship with the P-side and N-side of differential clock inputs. In banks 0 and 1, the GCLKP corresponds to the N-side, and the GCLKS corresponds to the P-side of a differential clock input. In banks 4 and 5, this correspondence is reversed.

Figure 2-2: Simple Clock Distribution (Bank 0 and 1 Scheme)

Figure 2-3: Simple Clock Distribution (Bank 4 and 5 Scheme)

Major synthesis tools automatically infer the IBUFG and BUFG when the corresponding input signal is used as a clock in the VHDL or Verilog code.

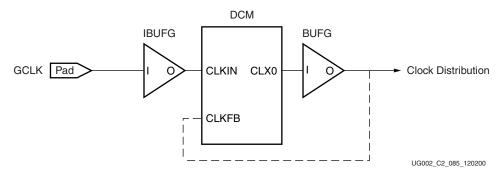

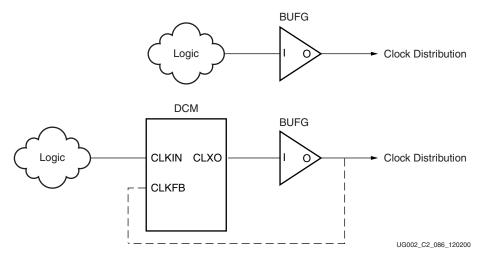

A high frequency or adapted (frequency, phase, and so forth) clock distribution with low skew is implemented by using a DCM between the output of the IBUFG and the input of the BUFG, as shown in Figure 2-4. "Using Digital Clock Managers (DCMs)" on page 175 provides details about DCMs and their use.

Figure 2-4: Clock Distribution with DCM

Clock distribution from internal sources is also possible with a BUFG only or with a DCM, as shown in Figure 2-5.

Figure 2-5: Internal Logic Driving Clock Distribution

## **Global Clock Inputs**

The clock buffer inputs are fed either by one of the 16 clock pads (refer to the <u>Virtex-II Data</u> <u>Sheet</u>), by the outputs of the DCM, or by local interconnect. Each clock buffer can be a synchronous "glitch-free" 2:1 multiplexer with two clock inputs and one select input. Internal logic (or alternatively a regular IOB) can feed the clock inputs. Any internal or external signal can drive the select input or clock enable input.

The possible inputs driving a global clock buffer or multiplexer are summarized in Table 2-1.

| Table 2-1: | Inputs Driving Global Clock Buffers or DCMs |

|------------|---------------------------------------------|

|------------|---------------------------------------------|

|                                         | Destination                                |                      |                                           |                         |                                   |  |  |

|-----------------------------------------|--------------------------------------------|----------------------|-------------------------------------------|-------------------------|-----------------------------------|--|--|

| Source                                  | BUFG(I) or<br>BUFGCE(I)                    | BUFGCE<br>(CE)       | BUFGMUX<br>(I0 or I1)                     | BUFGMUX<br>(S)          | DCM<br>(CLKIN)                    |  |  |

| External Clock via IBUFG(O)             | Dedicated in<br>same quadrant <sup>1</sup> | NA                   | Dedicated in same quadrant <sup>1</sup>   | NA                      | Same edge                         |  |  |

| DCM Clock Outputs                       | Same edge (top<br>or bottom) <sup>2</sup>  | NA                   | Same edge (top<br>or bottom) <sup>2</sup> | NA                      | General interconnect <sup>3</sup> |  |  |

| Internal Logic                          | General<br>interconnect                    | General interconnect | General<br>interconnect                   | General<br>interconnect | General interconnect <sup>3</sup> |  |  |

| User I/O Pad via IBUF(O)<br>(not IBUFG) | General<br>interconnect                    | General interconnect | General<br>interconnect                   | General<br>interconnect | General interconnect <sup>3</sup> |  |  |

| BUFG(O)                                 | NA                                         | NA                   | NA                                        | NA                      | Global clock<br>net               |  |  |

| BUFGMUX(O)                              | NA                                         | NA                   | General<br>interconnect                   | NA                      | Global clock<br>net               |  |  |

#### Notes:

1. Not all IBUFGs in the quadrant have a dedicated connection to a specific BUFG. Others would require general interconnect to be hooked up.

2. Same edge (top or bottom) enables use of dedicated routing resources.

3. Pad to DCM input skew is not compensated.

All BUFG (BUFGCE, BUFGMUX) outputs are available at the quadrant boundaries.

The output of the global clock buffer can be routed to non-clock pins.

## Primary and Secondary Global Multiplexers

Each global clock buffer is a self-synchronizing circuit called a clock multiplexer.

The 16 global clock buffers or multiplexers are divided as follows:

- Eight primary clock multiplexers

- Eight secondary clock multiplexers

No hardware difference exists between a primary and a secondary clock multiplexer. However, some restrictions apply to primary/secondary multiplexers, because they share input connections, as well as access to a quadrant.

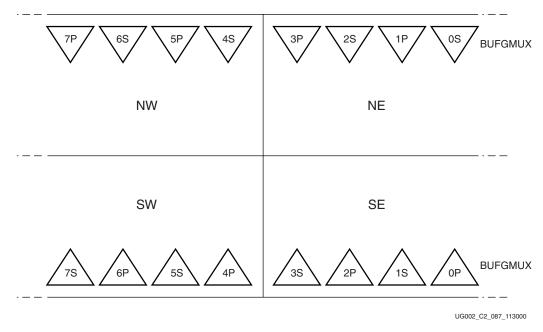

Each Virtex-II device is divided into four quadrants: North-West, South-West, North-East, and South-East. Each quadrant has two primary and two secondary clock multiplexers. The clock multiplexers are indexed 0 to 7, with one primary and one secondary for each index, alternating on the top and on the bottom (i.e., clock multiplexer "0P" at the bottom is facing clock multiplexer "0S" at the top).

In each device, the eight top/bottom clock multiplexers are divided into four primary and four secondary, indexed 0 to 7, as shown in Figure 2-6.

Figure 2-6: Primary and Secondary Clock Multiplexer Locations

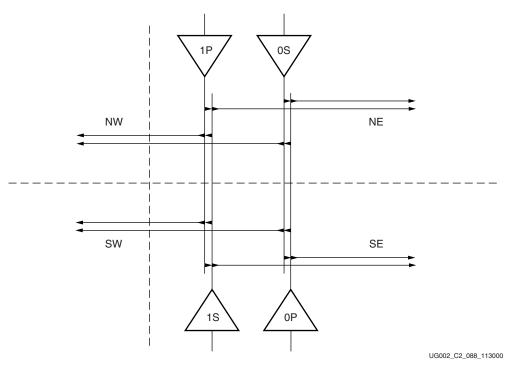

### Primary/Secondary: Rule 1

Considering two "facing" clock multiplexers (BUFG#P and BUFG#S), one or the other of these clock outputs can enter any quadrant of the chip to drive a clock within that quadrant, as shown in Figure 2-7. Note that the clock multiplexers "xP" and "xS" compete for quadrant access. For example, BUFG0P output cannot be used in the same quadrant as BUFG0S.

Figure 2-7: Facing BUFG#P and BUFG#S Connections

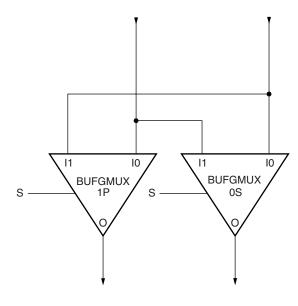

### Primary/Secondary: Rule 2

In a BUFGCE or BUFGMUX configuration, shared inputs have to be considered. Any two adjacent clock multiplexers share two inputs, as shown in Figure 2-8. The clock multiplexer "1P" and "0S" have common I0/I1 and I1/I0 inputs.

UG002\_C2\_089\_113000

#### Figure 2-8: Clock Multiplexer Pair Sharing Clock Multiplexer Inputs

Table 2-2 lists the clock multiplexer pairs in any Virtex-II device. The primary multiplexer inputs I1/I0 are common with the corresponding secondary multiplexer inputs I0/I1 (i.e., Primary I1 input is common with secondary I0 input, and primary I0 input is common with secondary I1 input).

Table 2-2: Top Clock Multiplexer Pairs

| Primary I1/I0   | 1P | 3P | 5P | 7P |

|-----------------|----|----|----|----|

| Secondary I0/I1 | 0S | 2S | 4S | 6S |

#### Table 2-3: Bottom Clock Multiplexer Pairs

| Primary I1/I0   | 0P | 2P | 4P | 6P |

|-----------------|----|----|----|----|

| Secondary I0/I1 | 15 | 3S | 5S | 7S |

### Primary/Secondary Usage

For up to eight global clocks, it is safe to use the eight primary global multiplexers (1P, 3P, 5P, 7P on the top and 0P, 2P, 4P, 6P on the bottom). Because of the shared inputs, a maximum of eight independent global clock multiplexers can be used in a design, as shown in Figure 2-9.

Figure 2-9: Eight Global Clocks Design

## DCM Clocks

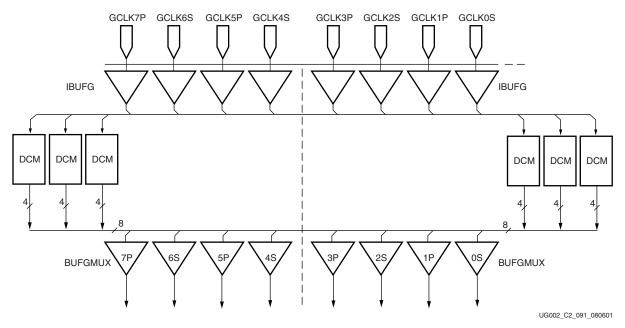

The four clock pins (IBUFG) in a quadrant can feed all DCMs in the same edge of the device. The clock-to-out and setup times are identical for all DCMs. Up to four clock outputs per DCM can be used to drive any clock multiplexer on the same edge (top or bottom), as shown in Figure 2-10.

#### **BUFG Exclusivity**

Each DCM has a restriction on the number of BUFGs it can drive on its (top or bottom) edge. Pairs of buffers with shared dedicated routing resources exist such that only one buffer from each dedicated pair can be driven by a single DCM. The exclusive pairs for each edge are: 1:5, 2:6, 3:7, and 4:8.

Figure 2-10: DCM Clocks

## Clock Output

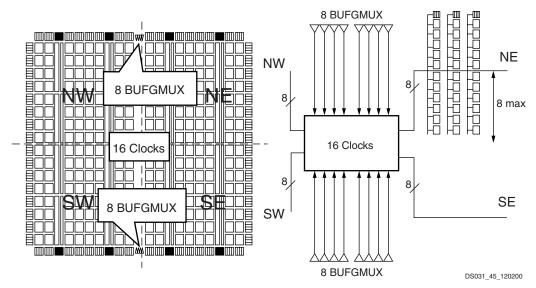

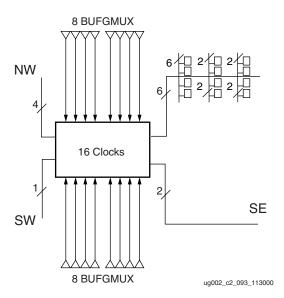

The clock distribution is based on eight clock trees per quadrant. Each clock multiplexer output is driving one global clock net. The Virtex-II device has eight dedicated low-skew clock nets. The device is divided into four quadrants (NW, NE, SW and SE) with eight global clocks available per quadrant.

Eight clock buffers are in the middle of the top edge and eight are in the middle of the bottom edge. Any of these 16 clock buffer outputs can be used in any quadrant, up to a maximum of eight clocks per quadrant, as illustrated in Figure 2-11, provided there is not a primary vs. secondary conflict.

Figure 2-11: Clock Buffer Outputs per Quadrant

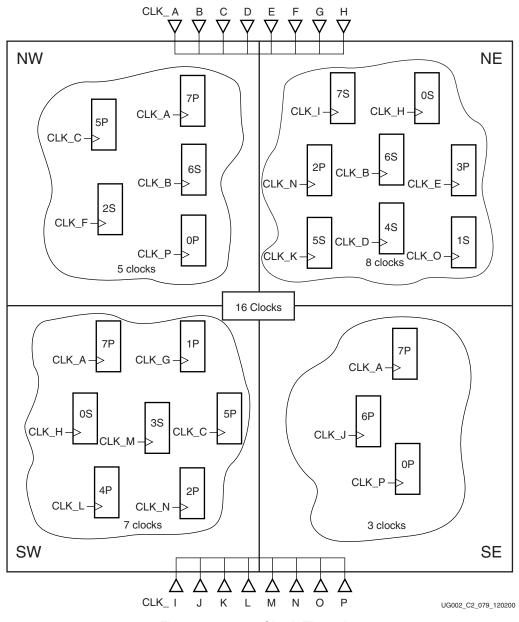

Designs with more than eight clocks must be floorplanned manually or automatically, distributing the clocks in each quadrant. As an example, a design with 16 clocks can be floorplanned as shown in Figure 2-12.

Figure 2-12: 16-Clock Floorplan

| The clock n | ets and clock buffers in this example are associated as shown in Table 2-4. |

|-------------|-----------------------------------------------------------------------------|

| Table 2-4:  | Clock Net Association With Clock Buffers                                    |

| Clock Net (top edge)    | CLK_A | CLK_B | CLK_C | CLK_D | CLK_E | CLK_F | CLK_G | CLK_H |

|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| BUFG                    | 7P    | 6S    | 5P    | 4S    | 3P    | 2S    | 1P    | 0S    |

| Clock Net (bottom edge) | CLK_I | CLK_J | CLK_K | CLK_L | CLK_M | CLK_N | CLK_O | CLK_P |

| BUFG                    | 7S    | 6P    | 5S    | 4P    | 3S    | 2P    | 1S    | 0P    |

| Quadrant NW             | CLK_A | CLK_B | CLK_C | -     | -     | CLK_F | -     | CLK_P |

| Quadrant SW             | CLK_A | -     | CLK_C | CLK_L | CLK_M | CLK_N | CLK_G | CLK_H |

| Quadrant NE             | CLK_I | CLK_B | CLK_K | CLK_D | CLK_E | CLK_N | CLK_O | CLK_H |

| Quadrant SE             | CLK_A | CLK_J | _     | _     | -     | -     | -     | CLK_P |

CLK\_A is used in three quadrants, and the other clocks are used in one or two quadrants, regardless of the position of the clock buffers (multiplexers), as long as they are not competing to access the same quadrant. (That is, CLK\_A (BUFG7P) cannot be used in the same quadrant with CLK\_I (BUFG7S). Refer to "Primary/Secondary: Rule 1" on page 160.) In other words, two buffers with the same index (0 to 7) cannot be used in the same quadrant. Each register, block RAM, registered multiplier, or DDR register (IOB) can be connected to any of the eight clock nets available in a particular quadrant.

Note that if a global clock (primary buffer) is used in four quadrants, the corresponding secondary buffer is not available.

## **Power Consumption**

Clock trees have been designed for low skew and low-power operation. Any unused branch is disconnected, as shown in Figure 2-13.

Figure 2-13: Low-Power Clock Network

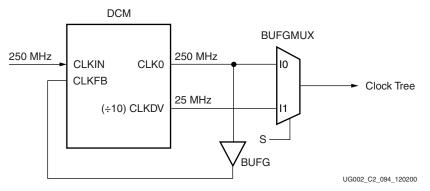

Also available to reduce overall power consumption are the BUFGCE feature, for dynamically driving a clock tree only when the corresponding module is used, and the BUFGMUX feature, for switching from a high-frequency clock to a low-frequency clock. The frequency synthesizer capability of the DCM can generate the low (or high) frequency clock from a single source clock, as illustrated in Figure 2-14. (See "Using Digital Clock Managers (DCMs)" on page 175).

Figure 2-14: Dynamic Power Reduction Scheme

## Library Primitives and Submodules

The primitives in Table 2-5 are available with the input, output, and control pins listed.

#### Table 2-5: Clock Primitives

| Primitive | Input  | Output | Control |

|-----------|--------|--------|---------|

| IBUFG     | Ι      | 0      | -       |

| IBUFGDS   | I, IB  | 0      | _       |

| BUFG      | Ι      | 0      | _       |

| BUFGMUX   | I0, I1 | 0      | S       |

| BUFGMUX_1 | I0, I1 | 0      | S       |

Refer to "Using Single-Ended SelectI/O Resources" on page 258 for a list of the attributes available for IBUFG and Refer to "Using LVDS I/O" on page 317 for a list of the attributes available for IBUFGDS.

The submodules in Table 2-6 are available with the input, output, and control pins listed.

| Table 2-6: | Clock | Submodules |

|------------|-------|------------|

|            |       | ••••••     |

| Submodule | Input | Output | Control |

|-----------|-------|--------|---------|

| BUFGCE    | Ι     | 0      | CE      |

| BUFGCE_1  | Ι     | 0      | CE      |

## **Primitive Functions**

#### IBUFG

IBUFG is an input clock buffer with one clock input and one clock output.

#### **IBUFGDS**

IBUFGDS is a differential input clock buffer with two clock inputs (positive and negative polarity) and one clock output.

#### BUFG

All Virtex-II devices have 16 global clock buffers (each of which can be used as BUFG, BUFGMUX, or BUFGCE).

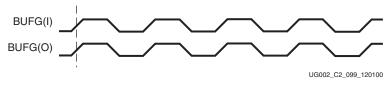

BUFG is a global clock buffer with one clock input and one clock output, driving a lowskew clock distribution network. The output follows the input, as shown in Figure 2-15.

Figure 2-15: BUFG Waveforms

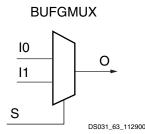

#### BUGMUX and BUFGMUX\_1

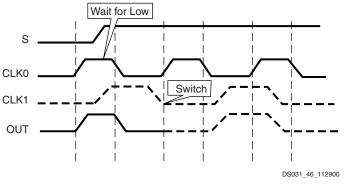

BUFGMUX (see Figure 2-16) can switch between two unrelated, even asynchronous clocks. Basically, a Low on S selects the CLK0 input, a High on S selects the S1 input. Switching from one clock to the other is done in such a way that the output High and Low time is never shorter than the shortest High or Low time of either input clock. As long as the presently selected clock is High, any level change of S has no effect.

BUFGMUX is the preferred circuit for rising edge clocks, while BUFGMUX\_1 is preferred for falling edge clocks.

Figure 2-16: Virtex-II BUFGMUX or BUFGMUX 1 Function

#### Operation of the BUFGMUX Circuit

If the presently selected clock is Low while S changes, or if it goes Low after S has changed, the output is kept Low until the other ("to-be-selected") clock has made a transition from High to Low. At that instant, the new clock starts driving the output.

The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock; that is, prior to the rising edge of the BUFGMUX output O. Violating this setup time requirement can result in an undefined runt pulse output.

Figure 2-17 shows a switchover from CLK0 to CLK1.

Figure 2-17: BUFGMUX Waveform Diagram

- The current clock is CLK0.

- S is activated High.

- If CLK0 is currently High, the multiplexer waits for CLK0 to go Low.

- Once CLK0 is Low, the multiplexer output stays Low until CLK1 transitions High to Low.

- When CLK1 transitions from High to Low, the output switches to CLK1.

- No glitches or short pulses can appear on the output.

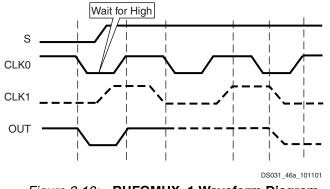

#### Operation of the BUFGMUX\_1 Circuit

If the presently selected clock is High while S changes, or if it goes High after S has changed, the output is kept High until the other ("to-be-selected") clock has made a transition from Low to High. At that instant, the new clock starts driving the output.

The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the falling edge of the presently selected clock; that is, prior to the falling edge of the BUFGMUX output O. Violating this setup time requirement can result in an undefined runt pulse output.

Figure 2-18 shows a switchover from CLK0 to CLK1.

Figure 2-18: BUFGMUX\_1 Waveform Diagram

- The current clock is CLK0.

- S is activated High.

- If CLK0 is currently Low, the multiplexer waits for CLK0 to go High.

- Once CLK0 is High, the multiplexer output stays High until CLK1 transitions Low to High.

- When CLK1 transitions from Low to High, the output switches to CLK1.

- No glitches or short pulses can appear on the output.

## Submodules

### BUFGCE and BUFGCE\_1

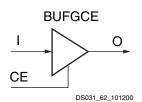

BUFGCE and BUFGCE\_1 are submodules based on BUFGMUX and BUFGMUX\_1, respectively. BUFGCE and BUFGCE\_1 are global clock buffers incorporating a smart enable function that avoids output glitches or runt pulses. The select signal must meet the setup time for the clock.

BUFGCE is the preferred circuit for clocking on the rising edge, while BUFGCE\_1 is preferred when clocking on the falling edge.

#### Operation of the BUFGCE Circuit

If the CE input (see Figure 2-19) is active (High) prior to the incoming rising clock edge, this Low-to-High-to-Low clock pulse passes through the clock buffer. Any level change of CE during the incoming clock High time has no effect.

Figure 2-19: Virtex-II BUFGCE or BUFGCE\_1 Function

If the CE input is inactive (Low) prior to the incoming rising clock edge, the following clock pulse does not pass through the clock buffer, and the output stays Low. Any level change of CE during the incoming clock High time has no effect. CE must not change during a short setup window just prior to the rising clock edge on the BUFGCE input I. Violating this setup time requirement can result in an undefined runt pulse output.

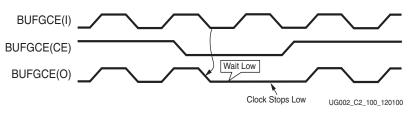

This means the output stays Low when the clock is disabled, but it completes the clock-High pulse when the clock is being disabled, as shown in Figure 2-20.

Figure 2-20: BUFGCE Waveforms

## Operation of the BUFGCE\_1 circuit

If the CE input is active (High) prior to the incoming falling clock edge, this High-to-Lowto-High clock pulse passes through the clock buffer. Any level change of CE during the incoming clock Low time has no effect.

If the CE input is inactive (Low) prior to the incoming falling clock edge, the following clock pulse does not pass through the clock buffer, and the output stays High. Any level change of CE during the incoming clock Low time has no effect. CE must not change during a short setup window just prior to the falling clock edge on the BUFGCE input I. Violating this setup time requirement can result in an undefined runt pulse output.

This means the output stays High when the clock is disabled, but it completes the clock-Low pulse when the clock is being disabled, as shown in Figure 2-21.

Figure 2-21: BUFGCE\_1 Waveforms

When BUFGCE (or BUFGCE\_1) is used with DCM outputs, a second BUFG can be used for clock feedback. Buffer sharing the inputs with BUFGCE is the preferred solution.

### Summary

Table 2-7 shows the maximum resources available per Virtex-II device.

Table 2-7: Resources per Virtex-II Device (from XC2V40 to XC2V8000)

| Resource                     | Maximum Number |

|------------------------------|----------------|

| Single-ended IBUFG (pads)    | 16             |

| Differential IBUFGDS (pairs) | 8              |

| BUFG (Global Clock Buffer)   | 16             |

| BUFGCE (or BUFGCE_1)         | 8              |

| BUFGMUX (or BUFGMUX_1)       | 8              |

## **Characteristics**

The following are characteristics of global clocks in Virtex-II devices:

- Low-skew clock distribution.

- Synchronous "glitch-free" multiplexer that avoids runt pulses. Switching between two asynchronous clock sources is usually considered unsafe, but it is safe with the Virtex-II global clock multiplexer.

- Any level change on S must meet a setup time requirement with respect to the signal on the output O (rising edge for BUFGMUX, falling edge for BUFGMUX\_1). Any level change on CE must meet a setup time requirement with respect to the signal on the Input I (rising edge for BUFGCE, falling edge for BUFGCE\_1).

- Two BUFGMUX (or BUFGMUX\_1) resources can be cascaded to create a 3 to 1 clock multiplexer.

## Location Constraints

BUFGMUX and BUFGMUX\_1 (primitives) and IBUFG (IBUFGDS) instances can have LOC properties attached to them to constrain placement. The LOC properties use the following form to constrain a clock net:

NET "clock\_name" LOC="BUFGMUX#P/S";

Each clock pad (or IBUFG) has a direct connection with a specific global clock multiplexer (input I0). A placement that does not conform to this rule causes the software to send a warning.

If the clock pad (or IBUFG) has LOC properties attached, the DCM allows place and route software maximum flexibility, as compared to a direct connection to the global clock buffer (BUFG).

## Secondary Clock Network

If more clocks are required, the 24 horizontal and vertical long lines in Virtex-II devices can be used to route additional clock nets. Skew is minimized by the place and route software, if the USELOWSKEWLINES constraint is attached to the net.

## VHDL and Verilog Instantiation

VHDL and Verilog instantiation templates are available as examples (see "VHDL and Verilog Templates" on page 170) for all primitives and submodules.

In VHDL, each template has a component declaration section and an architecture section. Each part of the template should be inserted within the VHDL design file. The port map of the architecture section should include the design signal names.

## VHDL and Verilog Templates

The following are templates for primitives:

- BUFGMUX\_INST

- BUFGMUX\_1\_INST

The following are templates for submodules:

- BUFGCE\_SUBM

- BUFGCE\_1\_SUBM

As examples, the BUFGMUX\_INST.vhd, BUFGMUX\_1\_INST.vhd, BUFGCE\_SUBM.vhd, and BUFGCE\_1\_SUBM.vhd VHDL templates are shown. In addition, the BUFGMUX\_INST.v, BUFGMUX\_1\_INST.v, BUFGCE\_1\_SUBM.v, and BUFGCE\_SUBM.v Verilog templates are shown.

#### **VHDL** Template

- -- Module: BUFGMUX\_INST

- -- Description: VHDL instantiation template

- -- Global Clock Multiplexer (Switch Low)

- -- Device: Virtex-II Family

```

-----

```

-- Component Declarations:

# XILINX®

```

component BUFGMUX

port (

: in std_logic;

ΙO

I1 : in std logic;

: in std logic;

S

: out std logic

0

);

end component;

- -

-- Architecture section:

- -

-- Global Clock Buffer Instantiation

U BUFGMUX: BUFGMUX

port map (

=> , -- insert clock input used when select (S) is Low

ΤO

=> , -- insert clock input used when select (S) is High

Τ1

=> , -- insert Mux-Select input

S

0

=> -- insert clock output

);

- -

_____

-- Module: BUFGMUX 1 INST

-- Description: VHDL instantiation template

-- Global Clock Multiplexer (Switch High)

- -

-- Device: Virtex-II Family

_____

-- Component Declarations:

component BUFGMUX 1

port (

: in std logic;

ТΟ

I1 : in std_logic;

S : in std logic;

0 : out std logic

);

end component;

-- Architecture section:

- -

-- Global Clock Buffer Instantiation

U_BUFGMUX_1: BUFGMUX_1

port map (

=> , -- insert clock input used when select (S) is Low

ТО

I1

=> , -- insert clock input used when select (S) is High

S

=> , -- insert Mux-Select input

=> -- insert clock output

0

);

- -

_ _ _ _

_____

-- Module: BUFGCE_SUBM

-- Description: VHDL instantiation template

-- Global Clock Buffer with Clock Enable:

-- Input Clock Buffer to BUFGMUX - Clock disabled = Low

-- Device: Virtex-II Family

_____

library IEEE;

use IEEE.std logic 1164.all;

- -

-- pragma translate_off

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

-- pragma translate on

```

- -

```

entity BUFGCE SUBM is

port (

I: in std_logic;

CE: in std_logic;

0: out std logic

);

end BUFGCE_SUBM;

- -

architecture BUFGCE SUBM arch of BUFGCE SUBM is

- -

-- Component Declarations:

component BUFGMUX

port (

: in std logic;

ΙO

I1 : in std_logic;

: in std_logic;

S

0

: out std logic

);

end component;

- -

-- signal declarations

signal GND : std_logic;

signal CE_B : std_logic;

- -

begin

GND <= '0';

- -

CE_B <= not CE;

- -

-- Global Clock Buffer Instantiation

U_BUFGMUX: BUFGMUX

port map (

ΙO

=> I,

=> GND,

I1

=> CE_B,

S

0

=> O

);

- -

end BUFGCE SUBM arch;

_____

-- Module: BUFGCE_1_SUBM

-- Description: VHDL instantiation template

-- Global Clock Buffer with Clock Enable:

-- Input Clock Buffer to BUFGMUX 1 - Clock disabled = High

-- Device: Virtex-II Family

_ _ _ _ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

library IEEE;

use IEEE.std logic 1164.all;

- -

-- pragma translate off

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

-- pragma translate_on

- -

entity BUFGCE_1_SUBM is

port (

I: in std logic;

CE: in std_logic;

0: out std_logic

);

end BUFGCE_1_SUBM;

```

```

- -

architecture BUFGCE_1_SUBM_arch of BUFGCE_1_SUBM is

- -

-- Component Declarations:

component BUFGMUX 1

port (

: in std logic;

ΙO

I1 : in std_logic;

S : in std logic;

0 : out std logic

);

end component;

-- signal declarations

signal VCC : std logic;

signal CE_B : std_logic;

begin

VCC <= '1';

- -

CE B <= not CE;

- -

-- Global Clock Buffer Instantiation

U BUFGMUX 1: BUFGMUX 1

port map (

=> I,

ΙO

=> VCC,

I1

S

=> CE_B,

0

=> 0

);

- -

end BUFGCE 1 SUBM arch;

```

### Verilog Template

```

//-----

// Module: BUFGMUX INST

// Description: Verilog Instantiation Template

// Global Clock Multiplexer (Switch Low)

//

11

// Device: Virtex-II Family

//-----

11

//BUFGMUX Instantiation

BUFGMUX U BUFGMUX

(.IO(), // insert clock input used when select(S) is Low

.I1(), // insert clock input used when select(S) is High

.S(), // insert Mux-Select input

.0()

// insert clock output

);

//-----

// Module:

BUFGMUX_1_INST

// Description: Verilog Instantiation Template

// Global Clock Multiplexer (Switch High)

11

11

// Device: Virtex-II Family

//-----

11

//BUFGMUX 1 Instantiation

BUFGMUX_1 U_BUFGMUX_1

```

www.xilinx.com 1-800-255-7778

#

```

(.IO(), // insert clock input used when select(S) is Low

.I1(), // insert clock input used when select(S) is High

// insert Mux-Select input

.s(),

.0()

// insert clock output

);

//-----

// Module:

BUFGCE SUBM

// Description: Verilog Submodule

// Global Clock Buffer with Clock Enable:

// Input Clock Buffer to BUFGMUX - Clock disabled = Low

11

// Device: Virtex-II Family

//-----

module BUFGCE_SUBM (I,

CE,

0);

I,

input

CE;

output 0;

wire GND;

assign GND = 1'b0;

BUFGMUX U_BUFGMUX

(.IO(I),

.I1(GND),

.S(~CE),

.0(0)

);

11

endmodule

//-----

// Module: BUFGCE_1_SUBM

// Description: Verilog Submodule

// Global Clock Buffer with Clock Enable:

// Input Clock Buffer to BUFGMUX_1 - Clock disabled = High

11

// Device: Virtex-II Family

//-----

module BUFGCE_1_SUBM (I,

CE,

0);

input

I,

CE;

output O;

wire VCC;

assign VCC = 1'b1;

BUFGMUX 1 U BUFGMUX 1

(.IO(I),

.I1(VCC),

.S(~CE),

.0(0)

);

11

```

```

endmodule

```