# **Using LVDS I/O**

## Introduction

Low Voltage Differential Signaling (LVDS) is a very popular and powerful high-speed interface in many system applications. Virtex-II I/Os are designed to comply with the IEEE electrical specifications for LVDS to make system and board design easier. With the addition of an LVDS current-mode driver in the IOBs, which eliminates the need for external source termination in point-to-point applications, and with the choice of two different voltage modes and an extended mode, Virtex-II devices provide the most flexible solution for doing an LVDS design in an FPGA.

Table 2-59 lists all LVDS primitives that are available for Virtex-II devices.

| Input             | Output            | 3-State            | Clock              | <b>Bi-Directional</b> |

|-------------------|-------------------|--------------------|--------------------|-----------------------|

| IBUF_LVDS         | OBUF_LVDS         | OBUFT_LVDS         | IBUFG_LVDS         | IOBUF_LVDS            |

| IBUFDS_LVDS_25    | OBUFDS_LVDS_25    | OBUFTDS_LVDS_25    | IBUFGDS_LVDS_25    |                       |

| IBUFDS_LVDS_33    | OBUFDS_LVDS_33    | OBUFTDS_LVDS_33    | IBUFGDS_LVDS_33    |                       |

| IBUFDS_LVDSEXT_25 | OBUFDS_LVDSEXT_25 | OBUFTDS_LVDSEXT_25 | IBUFGDS_LVDSEXT_25 |                       |

| IBUFDS_LVDSEXT_33 | OBUFDS_LVDSEXT_33 | OBUFTDS_LVDSEXT_33 | IBUFGDS_LVDSEXT_33 |                       |

Table 2-59: Available Virtex-II LVDS Primitives

The primitives in **bold** type are pre-existing LVDS primitives used in Virtex-E and earlier designs. They are not current-mode drivers and are still required for BLVDS (Bus LVDS) applications.

\*DS\_LVDS\_25 = 2.5V V<sub>CCO</sub> LVDS Buffer

\*DS\_LVDS\_33 = 3.3V V<sub>CCO</sub> LVDS Buffer

There is no difference in the AC characteristics of either voltage-mode LVDS I/O. These choices now provide more flexibility for mixed-I/O banking rules; that is, an LVTTL I/O can coexist with the 3.3V LVDS buffer in the same bank.

\*DS\_LVDSEXT\* = Extended mode LVDS buffer

This buffer provides a higher drive capability and voltage swing (350 - 750 mV), which makes it ideal for long-distance or cable LVDS links.

The output AC characteristics of this LVDS driver are not within the EIA/TIA specifications. This LVDS driver is intended for situations that require higher drive capabilities in order to produce an LVDS signal that is within EIA/TIA specification at the receiver.

## Creating an LVDS Input/Clock Buffer

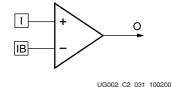

Figure 2-116 illustrates the LVDS input and clock buffer primitives shown in Table 2-60. The pin names used are the same as those used in the HDL library primitives.

Table 2-60: LVDS Input and Clock Buffer Primitives

| LVDS Inputs       | LVDS Clocks        |  |

|-------------------|--------------------|--|

| IBUFDS_LVDS_25    | IBUFGDS_LVDS_25    |  |

| IBUFDS_LVDS_33    | IBUFGDS_LVDS_33    |  |

| IBUFDS_LVDSEXT_25 | IBUFGDS_LVDSEXT_25 |  |

| IBUFDS_LVDSEXT_33 | IBUFGDS_LVDSEXT_33 |  |

IBUFDS\_LVDS\*/IBUFGDS\_LVDS\*

Figure 2-116: LVDS Input and Clock Primitives

To create an LVDS input, instantiate the desired mode (2.5 V, 3.3 V, or Extended) LVDS input buffer. Notice that the P and N channels are included in the primitive (I = P, IB = N). Software automatically uses the appropriate pin from an adjacent IOB for the N channel. The same applies to LVDS clocks: Use IBUFGDS\_LVDS\*

### LVDS Input HDL Examples

#### **VHDL** Instantiation

Verilog Instantiation

IBUFDS\_LVDS\_25 U1 ( .I(data\_in\_P), .IB(data\_in\_N), .O(data\_in) );

### Port Signals

I = P-channel data input to the LVDS input buffer

IB = N-channel data input to the LVDS input buffer

O = Non-differential input data from LVDS input buffer

#### Location Constraints

NET "data\_in\_P" LOC= "NS";

### LVDS Receiver Termination

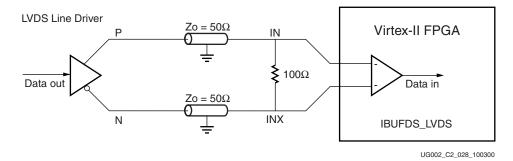

All LVDS receivers require standard termination. Figure 2-117 is an example of a typical termination for an LVDS receiver on a board with  $50\Omega$  transmission lines.

Figure 2-117: LVDS Receiver Termination

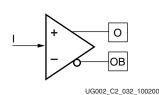

## Creating an LVDS Output Buffer

Figure 2-118 illustrates the LVDS output buffer primitives:

- OBUFDS\_LVDS\_25

- OBUFDS\_LVDS\_33

- OBUFDS\_LVDSEXT\_25

- OBUFDS\_LVDSEXT\_33

The pin names used are the same as those used in the HDL library primitives.

OBUFDS\_LVDS\*

Figure 2-118: LVDS Output Buffer Primitives

To create an LVDS output, instantiate the desired mode (2.5, 3.3V, or Extended) LVDS output buffer. Notice that the P and N channels are included in the primitive (O = P, OB = N). Software automatically uses the appropriate pin from an adjacent IOB for the N channel.

### LVDS Output HDL Examples

#### **VHDL** Instantiation

#### Verilog Instantiation

OBUFDS\_LVDS\_25 U1 ( .I(data\_out), .O(data\_out\_P), .OB(data\_out\_N) );

#### Port Signals

I = data input to the LVDS input buffer

O = P-channel data output

OB = N-channel data output

### Location Constraints

NET "data out P" LOC= "NS";

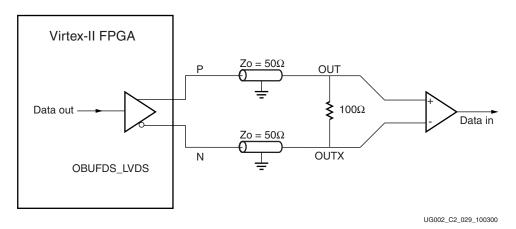

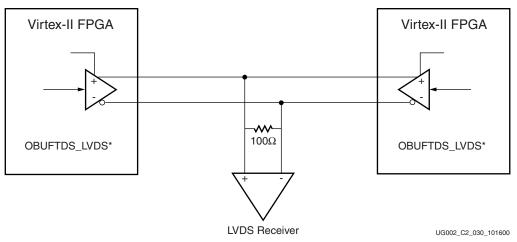

### LVDS Transmitter Termination

The Virtex-II LVDS transmitter does not require any termination. Table 2-59 lists primitives that correspond to the Virtex-II LVDS current-mode drivers. Virtex-II LVDS current-mode drivers are a true current source and produce the proper (IEEE/EIA/TIA compliant) LVDS

signal. Figure 2-119 illustrates a Virtex-II LVDS transmitter on a board with  $50\Omega$  transmission lines.

## Creating an LVDS Output 3-State Buffer

Figure 2-120 illustrates the LVDS 3-State buffer primitives:

- OBUFTDS\_LVDS\_25

- OBUFTDS\_LVDS\_33

- OBUFTDS\_LVDSEXT\_25

- OBUFTDS\_LVDSEXT\_33

The pin names used are the same as those used in the HDL library primitives.

UG002\_C2\_033\_100200

Figure 2-120: LVDS 3-State Primitives

To create an LVDS 3-State output, instantiate the desired mode (2.5V, 3.3V, or Extended) LVDS 3-State buffer. Notice that the P and N channels are included in the primitive (O = P, OB = N). Software automatically uses the appropriate pin from an adjacent IOB for the N channel.

### LVDS 3-State HDL Example

#### **VHDL** Instantiation

www.xilinx.com

1-800-255-7778

2

#### Verilog Instantiation

```

OBUFTDS_LVDS_25 U1 ( .I(data_out),

.T(tri),

.O(data_out_P),

.OB(data_out_N)

);

```

### Port Signals

I = data input to the 3-state output buffer

T = 3-State control signal

O = P-channel data output

OB = N-channel data output

### Location Constraints

NET "data\_out\_P" LOC = "NS";

### LVDS 3-State Termination

The Virtex-II LVDS 3-state buffer does not require any termination. Table 2-59 lists primitives that correspond to Virtex-II LVDS current-mode drivers. These drivers are a true current source, and they produce the proper (IEEE/EIA/TIA compliant) LVDS signal. Figure 2-121 illustrates a simple redundant point-to-point LVDS solution with two LVDS 3-state transmitters sharing a bus with one LVDS receiver and the required termination for the circuit.

Figure 2-121: LVDS 3-State Termination

## Creating a Bidirectional LVDS Buffer

Since LVDS is intended for point-to-point applications, BLVDS (Bus-LVDS) is not an IEEE/EIA/TIA standard implementation and requires careful adaptation of I/O and PCB layout design rules. The primitive supplied in the software library for bi-directional LVDS does not use the Virtex-II LVDS current-mode driver. Therefore, source termination is required. Refer to <u>xapp243</u> for examples of BLVDS termination.

The following are VHDL and Verilog instantiation examples of Virtex-II BLVDS primitves.

### **VHDL** Instantiation

### Verilog Instantiation

### Port Signals

I = data output: internal logic to LVDS I/O buffer

T = 3-State control to LVDS I/O buffer

IO = P-channel data I/O to or from BLVDS pins

IOB = N-channel data I/O to or from BLVDS pins

O = Data input: off-chip data to LVDS I/O buffer

### Location Constraints

Only the P or N channel must be constrained. Software automatically places the corresponding channel of the pair on the appropriate pin.

## LDT

Lightning Data Transport (LDT) is a new high speed interface and protocol introduced by Advanced Micro Devices. LDT is a differential signaling based interface that is very similar to LVDS. Virtex-II IOBs are equipped with LDT buffers. These buffers also have corresponding software primitives as follows:

IBUFDS\_LDT\_25 IBUFGDS\_LDT\_25 OBUFDS\_LDT\_25 OBUFTDS\_LDT\_25

## LDT Implementation

LDT implementation is the same as LVDS with DDR, so follow all of the rules and guidelines set forth earlier in this chapter for LVDS-DDR, and replace the LVDS buffer with the corresponding LDT buffer. For more information on Virtex-II LDT electrical specification, refer to the <u>Virtex-II Data Sheet</u>.