# Chapter 3

# Configuration

# Summary

This chapter covers the following topics:

- Introduction

- Configuration Solutions

- Master Serial Programming Mode

- Slave Serial Programming Mode

- Master SelectMAP Programming Mode

- Slave SelectMAP Programming Mode

- JTAG/ Boundary Scan Programming Mode

- Boundary-Scan for Virtex-II Devices Using IEEE Standard 1149.1

- Boundary-Scan for Virtex-II Devices Using IEEE Standard 1532

- Configuration With MultiLINX

- Configuration Details

- Readback

# Introduction

Virtex-II devices are configured by loading application-specific configuration data into internal memory. Configuration is carried out using a subset of the device pins, some of which are dedicated, while others can be reused as general-purpose inputs and outputs after configuration is complete.

Depending on the system design, several configuration modes are selectable via mode pins. The mode pins M2, M1, and M0 are dedicated pins. An additional pin, HSWAP\_EN, is used in conjunction with the mode pins to select whether user I/O pins have pull-up resistors during configuration. By default, HSWAP\_EN is tied High (internal pull-up resistor), which shuts off pull-up resistors on the user I/O pins during configuration. When HSWAP\_EN is tied Low, the pull-up resistors are on and therefore, the user I/Os have pull-up resistors during configuration.

Other dedicated pins are:

- CCLK the configuration clock pin

- DONE configuration status pin

- TDI, TDO, TMS, TCK boundary-scan pins

- PROG\_B configuration reset pin

Depending on the configuration mode selected, CCLK can be an output generated by the Virtex-II FPGA or an input accepting externally generated clock data. For correct operation, these pins require a  $V_{CCAUX}$  of 3.3 V to permit low-voltage transistor-to-transistor logic (LVTTL) operations.

All dual-function configuration pins are contained in banks 4 and 5. Bank 4 contains pins used in serial configuration modes, and banks 4 and 5 contain pins used for SelectMAP modes.

A persist option is available, which can be used to force pins to retain their configuration function even after device configuration is complete. If the persist option is not selected, then the configuration pins with the exception of CCLK, PROG\_B, and DONE can be used for user I/O in normal operation. The persist option does not apply to boundary-scan related pins. The persist feature is valuable in applications that employ partial reconfiguration, dynamic reconfiguration, or readback.

# **Configuration Modes**

Virtex-II supports the following configuration modes:

- Master-Serial

- Slave-Serial (default)

- Master SelectMAP

- Slave SelectMAP

- Boundary-Scan (IEEE 1532 and IEEE 1149)

Table 3-1 shows Virtex-II configuration mode pin settings.

| Configuration Mode <sup>1</sup> | M2 | M1 | MO | CCLK Direction | Data Width | Serial Dout <sup>2</sup> |

|---------------------------------|----|----|----|----------------|------------|--------------------------|

| Master Serial                   | 0  | 0  | 0  | Out            | 1          | Yes                      |

| Slave Serial                    | 1  | 1  | 1  | In             | 1          | Yes                      |

| Master SelectMAP                | 0  | 1  | 1  | Out            | 8          | No                       |

| Slave SelectMAP                 | 1  | 1  | 0  | In             | 8          | No                       |

| Boundary Scan                   | 1  | 0  | 1  | N/A            | 1          | No                       |

Table 3-1: Virtex-II Configuration Mode Pin Settings

#### Notes:

- 1. The HSWAP\_EN pin controls the pullups. Setting M2, M1, and M0 selects the configuration mode, while the HSWAP\_EN pin controls whether or not the pullups are used.

- 2. Daisy chaining is possible only in modes where Serial Dout is used. For example, in SelectMAP modes, the first device does NOT support daisy chaining of downstream devices.

Table 3-2 lists the total number of bits required to configure each device:

Table 3-2: Virtex-II Bitstream Lengths

| Total Number of Configuration Bits<br>(including header) |  |  |  |  |  |

|----------------------------------------------------------|--|--|--|--|--|

| 360,096                                                  |  |  |  |  |  |

| 635,296                                                  |  |  |  |  |  |

| 1,697,184                                                |  |  |  |  |  |

| 2,761,888                                                |  |  |  |  |  |

| 4,082,592                                                |  |  |  |  |  |

| 5,659,296                                                |  |  |  |  |  |

| 7,492,000                                                |  |  |  |  |  |

| 10,494,368                                               |  |  |  |  |  |

| 15,659,936                                               |  |  |  |  |  |

| 21,849,504                                               |  |  |  |  |  |

| 29,063,072                                               |  |  |  |  |  |

|                                                          |  |  |  |  |  |

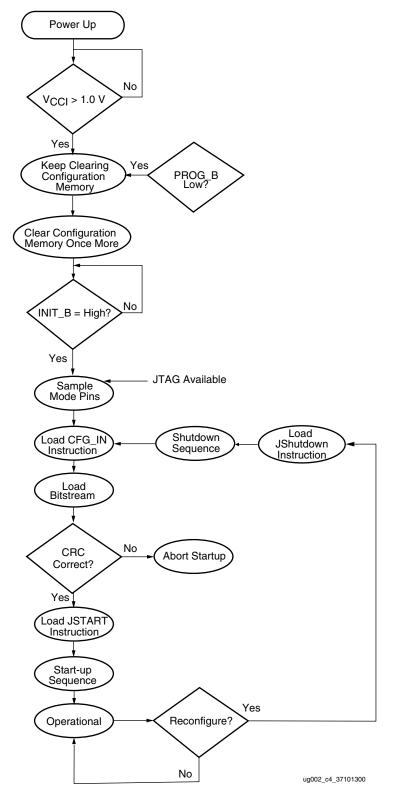

# **Configuration Process and Flow**

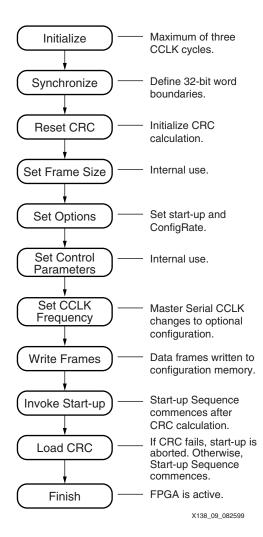

The configuration process involves loading the configuration bitstream into the FPGA using the selected mode. There are four major phases in the configuration process:

- Clearing Configuration Memory

- Initialization

- Loading Configuration Data

- Device Startup

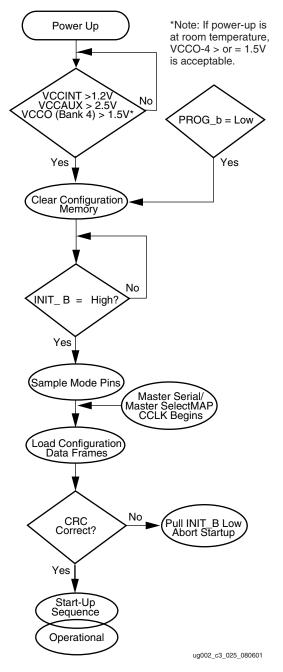

Figure 3-1 illustrates the configuration process flow.

Figure 3-1: Configuration Process

#### Power Up

The V<sub>CCINT</sub> power pins must be supplied with a 1.5 V source. (Refer to the <u>Virtex-II Data</u> <u>Sheet</u> for DC characteristics.) The IOB voltage input for Bank 4 (V<sub>CCO\_4</sub>) and the auxiliary voltage input (V<sub>CCAUX</sub>) are also used as a logic input to the Power-On-Reset (POR) circuitry. Even if this bank is not being used, V<sub>CCO\_4</sub> must be connected to a 1.5 V or greater source.

#### **Clearing Configuration Memory**

In the memory clear phase, non-configuration I/O pins are 3-stated with optional pull-up resistors. The INIT\_B and DONE pins are driven Low by the FPGA, and the memory is cleared. After PROG\_B transitions High, memory is cleared twice and initialization can begin.

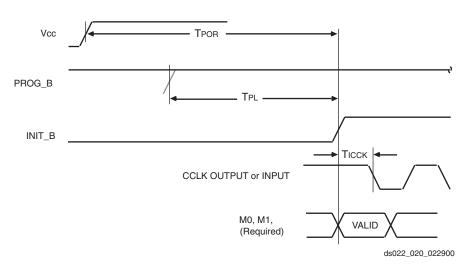

The INIT\_B pin transitions High when the clearing of configuration memory is complete. A logic Low on the PROG\_B input resets the configuration logic and holds the FPGA in the clear configuration memory state. When PROG\_B is released, the FPGA continues to hold INIT\_B Low until it has completed clearing all of the configuration memory. The minimum Low pulse time for PROG\_B is defined by the T<sub>PROGRAM</sub> timing parameter. There is no maximum value. The power-up timing of configuration signals is shown in Figure 3-2 and the corresponding timing characteristics are listed in Table 3-3.

Figure 3-2: Power-Up Timing Configuration Signals

| Table 3-3: | Power-Up | Timing | Characteristics |

|------------|----------|--------|-----------------|

|------------|----------|--------|-----------------|

| Description         | Symbol               | Value                    | Units              |

|---------------------|----------------------|--------------------------|--------------------|

| Program Latency     | T <sub>PL</sub>      | T <sub>PL</sub> (2V8000) | 4 μs per frame max |

| Power-on-Reset      | T <sub>POR</sub>     | $T_{PL}$ +2              | ms, max            |

| CCLK (output) Delay | Τ                    | 0.5                      | μs, min            |

| CCER (output) Delay | T <sub>ICCK</sub>    | 4.0                      | μs, max            |

| Program Pulse Width | T <sub>PROGRAM</sub> | 300                      | ns, min            |

## Initialization

For the initialization phase, the INIT\_B pin is released, the mode pins are sampled, the appropriate pins become active, and the configuration process begins. It is possible to delay configuration by externally holding INIT\_B Low.

## **Delaying Configuration**

The INIT\_B pin can also be held Low externally to delay configuration of the FPGA. The FPGA samples its mode pins on the rising edge of INIT\_B. After INIT\_B transitions to High, configuration can begin. No additional time-out or waiting periods are required, but configuration does not need to commence immediately after the transition of INIT\_B. The configuration logic does not begin processing data until the synchronization word from the bitstream is loaded.

## Loading Configuration Data

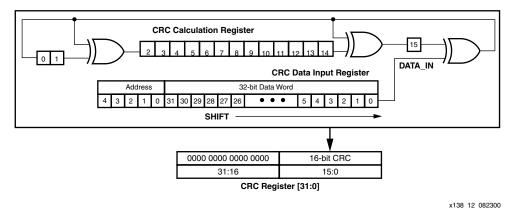

Once configuration begins, the target FPGA starts to receive data frames. Cyclic Redundancy Checking (CRC) is performed before and after the last data frame. CRC is also automatically checked after each block write to an internal data register (FDRI). If the CRC checks prove valid, the device start-up phase can begin.

If the CRC values do not match, INIT\_B is asserted Low to indicate that a CRC error has occurred, startup is aborted, and the FPGA does not become active.

To reconfigure the device, the PROG\_B pin should be asserted to reset the configuration logic. Recycling power also resets the FPGA for configuration. For more information on CRC calculation, see "Cyclic Redundancy Checking Algorithm" on page 395.

The details of loading configuration data in each of the five modes are discussed in the following sections:

- "Master Serial Programming Mode" on page 359

- "Master SelectMAP Programming Mode" on page 362

- "Slave Serial Programming Mode" on page 360

- "Slave SelectMAP Programming Mode" on page 364

- "JTAG/ Boundary Scan Programming Mode" on page 368

## **Device Startup**

Device startup is a transition phase from the configuration mode to normal programmed device operation. Although the order of the start-up events are user programmable via software, the default sequence of events is as follows:

Upon completion of the start-up sequence, the target FPGA is operational.

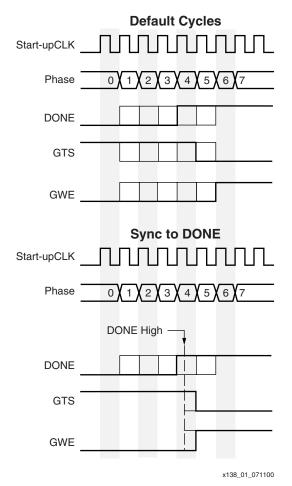

The Start-Up Sequencer is an 8-phase sequential state machine that counts from phase 0 to phase 7. (See Figure 3-3.)

The Start-Up Sequencer performs the following tasks:

- Release the DONE pin.

- Negate GTS, activating all of the I/Os.

- Assert GWE, allowing all RAMs and flip-flops to change state.

- Assert EOS. The End-Of-Start-Up flag is always set in phase 7. This is an internal flag that is not user accessible.

BitGen options control the order of the Start-Up Sequence. The default Start-Up Sequence is the bold line in Figure 3-3. The Start-Up Sequence can also be stalled at any phase until either DONE has been externally forced High, or a specified DCM or DCI has established LOCK. For details, see Appendix B, "BitGen and PROMGen Switches and Options."

At the cycle selected for the DONE to be released, the sequencer always waits in that state until the DONE is externally released. However, this does not delay the GTS or GWE if they are selected to be released prior to DONE. Therefore, DONE is selected first in the sequence for default settings.

Figure 3-3: Default Start-Up Sequence

# **Configuration Pins**

Certain pins in the FPGA are designated for configuration and are listed in Table 3-4. Some pins are dedicated to the configuration function and others are dual-function pins that can be user I/O after configuration.

| Name          | Direction    | Driver Type             | Description                                                        |

|---------------|--------------|-------------------------|--------------------------------------------------------------------|

| Dedicated Pir | ıs           |                         |                                                                    |

| CCLK          | Input/Output | Active                  | Configuration clock. Output in Master mode.                        |

| PROG_B        | Input        |                         | Asynchronous reset to configuration logic.                         |

| DONE          | Input/Output | Active/<br>Open-Drain   | Configuration status and start-up control.                         |

| M2, M1, M0    | Input        |                         | Configuration mode selection.                                      |

| HSWAP_EN      | Input        |                         | I/O pullups during configuration.                                  |

| TMS           | Input        |                         | Boundary Scan Mode Select.                                         |

| ТСК           | Input        |                         | Boundary Scan Clock.                                               |

| TDI           | Input        |                         | Boundary Scan Data Input.                                          |

| TDO           | Output       | Active                  | Boundary Scan Data Output.                                         |

| Dual Function | n Pins       |                         |                                                                    |

| DIN (D0)      | Input/Output | Active<br>Bidirectional | Serial configuration data input/SelectMAP readback data output.    |

| D1:D7         | Input/Output | Active<br>Bidirectional | SelectMAP configuration data input, readback data output.          |

| CS_B          | Input        |                         | Chip Select (SelectMAP mode only).                                 |

| RDWR_B        | Input        |                         | Active Low write select, read select<br>(SelectMAP mode only).     |

| BUSY/DOUT     | Output       | Active                  | Serial configuration data output for serial daisy-chains (active). |

| INIT_B        | Input/Output | Open-Drain              | Delay configuration, indicate configuration error.                 |

Table 3-4: Configuration Pins

## Mixed Voltage Environments

Virtex-II devices have separate voltage sources.  $V_{CCINT} = 1.5$  V powers the internal circuitry,  $V_{CCAUX} = 3.3$  V powers the input buffers and auxiliary circuitry, and  $V_{CCO}$  (1.5, 1.8, 2.5, or 3.3 V) powers the IOB circuitry. SelectI/O is separated into eight banks of I/O groups. Each bank can be configured with one of several I/O standards. Refer to the Design Considerations section for I/O banking rules and available I/O standards. Before and during configuration, all I/O banks are set for the LVTTL standard, which requires an output voltage ( $V_{CCO}$ ) of 3.3 V for normal operation.

If  $V_{CCO}$  is less than 3.3 V on banks 4 and 5, serial and SelectMAP configuration modes might have a lower frequency. (See Table 3-5).

| Configuration Mode | Pins Used                                     | V <sub>CCO_4</sub> | V <sub>CCO_5</sub> |

|--------------------|-----------------------------------------------|--------------------|--------------------|

| JTAG               | Dedicated Pins                                | not a concern      | not a concern      |

| Serial             | Dedicated Pins plus<br>DOUT, DIN, and<br>INIT | 3.3 V              | not a concern      |

| SelectMAP          | Dedicated Pins plus<br>dual-function pins     | 3.3 V              | 3.3 V              |

Table 3-5:

Configuration Modes and V<sub>CCO</sub> Voltages

#### Notes:

1. If less than 3.3 V ( $V_{CCO_4/5} = 2.5$  V), the configuration frequency might be as low as half of the typical frequency.

All dedicated configuration pins are powered by  $V_{CCAUX}$ . All dual-function configuration pins are located within banks 4 and 5. As described under Configuration Process and Flow, the  $V_{CCO_4}$  input voltage is used as a logic input to the power-on-reset (POR) circuitry.

For JTAG configuration mode, JTAG inputs are independent of  $V_{CCO}$  and work between 2.5 V and 3.3 V TTL levels. The JTAG output (TDO) is sourced from  $V_{CCAUX}$ .

For serial configuration mode, V<sub>CCO\_4</sub> pins require a 3.3 V supply for output configuration pins to operate normally. In serial mode, all of the configuration pins are in bank 4.

For SelectMAP configuration mode,  $V_{CCO_4}$  and  $V_{CCO_5}$  pins require a 3.3 V supply for output configuration pins to operate normally. In SelectMAP mode, all of the configuration pins are in banks 4 and 5.

If the Virtex-II device is being configured in serial or SelectMAP mode, and banks 4 and 5 are being configured for an I/O standard that requires a V<sub>CCO</sub> other than 3.3 V, then V<sub>CCO\_4</sub> and V<sub>CCO\_5</sub> (SelectMAP only) must be switched from 3.3 V and used during configuration at the same voltage required after configuration. If readback is performed using SelectMAP mode after configuration, then V<sub>CCO\_4</sub> and V<sub>CCO\_5</sub> require a 3.3 V supply after configuration, as well.

# **Configuration Solutions**

Several configuration solutions are available to support Virtex-II, each targeted to specific application requirements. Guidance and support (application notes, reference designs, and so forth) is also available for designers looking to develop and implement their own configuration solution for Virtex FPGAs.

# System Advanced Configuration Environment (System ACE™) Series

The System ACE series of configuration solutions offers a system-level configuration manager for designers using multiple FPGAs or FPGAs requiring multiple bitstreams. This solution combines standard industry Flash storage with Xilinx-designed configuration control. Features common to the entire System ACE family include:

- Support for multiple bitstreams

- Built-in support for embedded processors in FPGAs

- Support for reconfiguring, updating, or debugging systems over a network

- Built-in system interface

- Scalability (density) and re-useability (across many designs)

- Centralization of configuration control for reduced board space and simpler debugging

- Use of excess storage capacity for non-configuration, system storage

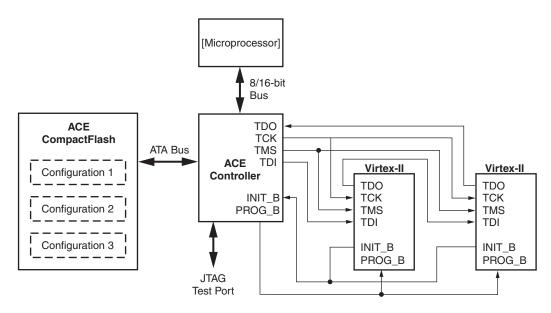

## System ACE CF

System ACE CF (CompactFlash<sup>TM</sup>) solution combines a standard CompactFlash Association (CFA) Type-I or Type-II memory module (CompactFlash or 1" disk drive) with a Xilinx-designed ACE Controller<sup>TM</sup> configuration control chip. See Figure 3-4.

UG002\_C4\_041\_092001

Figure 3-4: System ACE CompactFlash and Controller

The CompactFlash card stores an unlimited number of bitstreams and ranges in density from 128 Mb to 3 Gb. This card is capable of storing one large bitstream or several smaller bitstreams. If several bitstreams are used, the system can be set up so that individual bitstreams are callable as needed, allowing for dynamic reconfiguration of the Virtex-II device and other Xilinx FPGAs in the JTAG chain.

The ACE Controller drives bits through the FPGA JTAG chain and has three other ports:

- A port for interfacing with a microprocessor, a network, or a MultiLINX cable

- A port for interfacing with the CompactFlash card

- A port that provides access to the FPGA JTAG chain for FPGA testing or configuration via automatic test equipment or via desktop or third-party programmers

For further information on any System ACE product, visit the <u>www.xilinx.com/systemace</u> website.

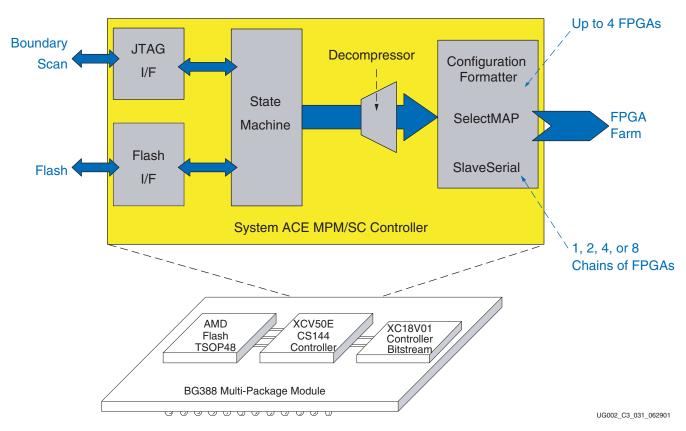

## System ACE Multi-Package Module (MPM)

System ACE MPM is a multi-package module consisting of a packaged standard Flash from AMD, a packaged FPGA, and a packaged configuration PROM, all in a 388-pin BGA package. The Flash stores configuration and other data, while the FPGA acts as an advanced configuration controller and is configured by the PROM. This solution provides high density and high-speed configuration capability in a single package, helping to simplify the design and manufacturing process. It is available in 16-Mbit, 32-Mbit, and 64-Mbit densities.

## System ACE Soft Controller (SC)

System ACE SC is a downloadable version of the configuration controller found in System ACE MPM; versions are provided that support various standard Flash interfaces. System ACE SC provides all of the features of System MPM without the Single Package. It allows designers to use the Flash memory already in their system to store configuration data. The System ACE SC controller is available free of charge in the form of a PROM file that can be downloaded from the System ACE website. This pre-engineered solution is implemented by connecting up to four Flash chips on a board to an FPGA that will be used as a configuration controller and then downloading the controller file into a PROM. Figure 3-5 describes the controller for both System ACE MPM and System ACE SC.

#### Figure 3-5: System ACE MPM/SC Controller

System ACE MPM and System ACE SC have these unique features:

- High speed configuration up to 154 Mb/sec

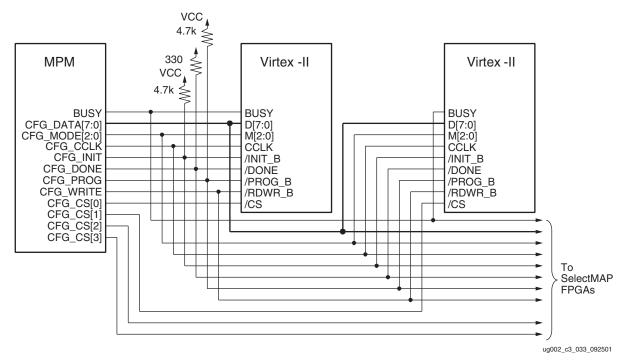

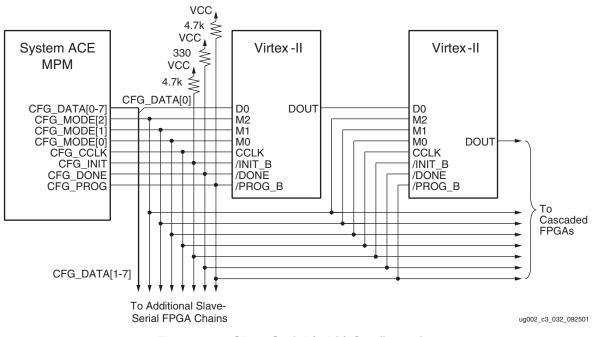

- Support for both SelectMAP (8-bit) (see Figure 3-6) and Slave Serial (1-bit) (see Figure 3-7) configuration

- Configuration of multiple FPGAs in parallel

- Bitstream compression for increased storage capability

- Storage of up to 8 different bitstreams

Figure 3-6: SelectMAP (8-bit) Configuration

Figure 3-7: Slave Serial (1-bit) Configuration

# **Configuration PROMs**

## Using XC18V00 PROMs

The XC18V00 family of Flash in-system programmable (ISP) configuration PROMs offers the flexibility of re-programmability and multiple package offerings, combined with both serial and SelectMAP FPGA configurability. This family is JTAG programmable and ranges in density from 256 Kb to 4 Mb; these PROMs can also be cascaded to support larger bitstreams.

The 18V00 family offers data throughput rates of up to 264 Mb/s. It is also capable of triggering FPGA reconfiguration via a JTAG command. The parts can be JTAG programmed via cable, HW-130, or standard third party programmers. The XC18V00 PROMs are available in SO20, PC20, VQ44, and PC44 packages. Refer to Appendix C, "XC18V00 Series PROMs" for the latest version of the XC18V00 PROMs data sheet and package diagrams for the entire PROM family. See Table 3-8 to determine which PROMs go with which Virtex-II FPGAs.

## Using XC17V00 PROMs

The XC17V00 family of one-time programmable (OTP) PROMs provides a proven, lowcost, compact, and pre-engineered configuration solution. Ranging from 1 Mb to 16 Mb, this family is also the PROM density leader; it can also be daisy-chained to support larger bitstreams. This family supports serial configuration of Virtex-II FPGAs; in addition, the XC17V08 and XC17V16 support SelectMAP configuration modes.

The XC17V00 family can be used for stabilized designs that are in a high-volume production flow and/or for designs requiring a low-cost solution. XC17V00 PROMs can be programmed either by using the HW-130 or by using a variety of third-party programmers. The XC17V00 PROMs are available in VO8, SO20, PC20, VQ44, and PC44 packages. Data sheets for PROMs are available at <u>www.xilinx.com</u>. See Table 3-8 to determine which PROMs go with which Virtex-II FPGAs and see Appendix C, "XC18V00 Series PROMs" for package diagrams.

# Flash PROMs With a CPLD Configuration Controller

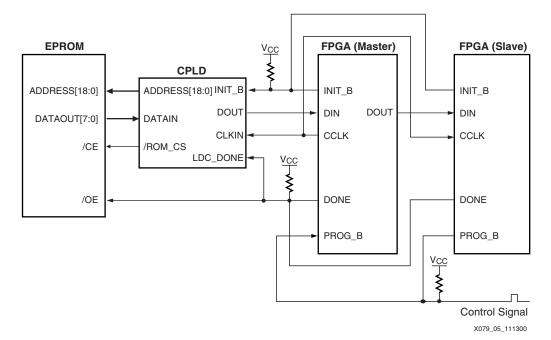

Some designers prefer to leverage existing Flash memory in their system to store the configuration bitstreams. A small CPLD-based configuration controller can provide the mechanism to access the bitstreams in the FLASH and deliver them quickly to Virtex-II devices. The following application notes describe the details for a serial or SelectMAP configuration architecture using FLASH memories and CPLDs:

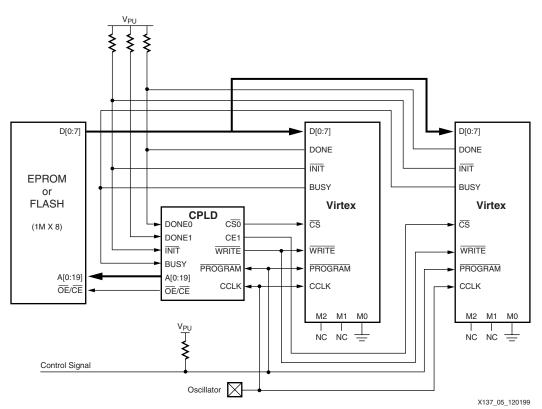

• XAPP079: *Configuring* Xilinx *FPGAs Using an XC9500 CPLD and Parallel PROM* (www.xilinx.com/apps/xappsumm.htm#xapp079) describes an architecture that configures a chain of Virtex-II devices using Master-Serial mode. See Figure 3-8 for an example of FPGA configuration using a CPLD and a parallel PROM.

#### *Figure 3-8:* Configuring Virtex-II Using a CPLD and Parallel PROM

• XAPP137: *Configuring Virtex FPGAs From Parallel EPROMs With a CPLD* (www.xilinx.com/apps/xappsumm.htm#xapp137) describes an architecture that configures one or more Virtex-II devices using the Slave SelectMAP mode. See Figure 3-9 for an example of FPGA configuration using a CPLD and a parallel EPROM.

# **Embedded Solutions**

## Using an Embedded Microcontroller

XAPP058: Xilinx *In-System Programming Using an Embedded Microcontroller* (www.xilinx.com/apps/xappsumm.htm#xapp058) describes a compact and robust process that (re)configures Virtex-II devices directly from a microprocessor through the JTAG test port of the Virtex-II device. The process additionally supports (re)configuration of XC18V00 ISP PROMs and CPLDs that reside on the JTAG scan chain. Portable, reference Ccode is provided with the application note for rapid implementation.

## Using IEEE Standard 1532

Systems that implement an IEEE Standard 1532 player are able to configure Virtex-II devices and any other 1532-compliant devices using the device BSDL file and 1532 data file.

## Using MultiLINX or Other Cables

During the development or prototype design stage, designers can program their Virtex-II devices directly in system via the Xilinx Parallel Cable III or MultiLINX programming cables using the Xilinx JTAG Programmer software or Integrated Logic Analyzer (ILA) ChipScope software. The operating system (see Table 3-6) and configuration mode (see Table 3-7) determine the appropriate cable selection.

| Cable                 | Connection       | Windows 98 | Windows NT | Windows 2000 | Solaris   | HP-UX     |

|-----------------------|------------------|------------|------------|--------------|-----------|-----------|

| Parallel<br>Cable III | Parallel<br>Port | Supported  | Supported  | Supported    | N/A       | N/A       |

| MultiLINX             | USB              | Supported  | N/A        | Supported    | N/A       | N/A       |

| MultiLINX             | RS-232           | Supported  | Supported  | Supported    | Supported | Supported |

Table 3-6: Xilinx Cable Operating System Support

| Table 3-7: Xilinx Cat | le Configuration | Mode Support |

|-----------------------|------------------|--------------|

|-----------------------|------------------|--------------|

| Cable              | JTAG      | Slave Serial | Slave SelectMAP |

|--------------------|-----------|--------------|-----------------|

| Parallel Cable III | Supported | Supported    | N/A             |

| MultiLINX          | Supported | Supported    | Supported       |

SelectMAP is the fastest cable configuration mode. JTAG and serial modes provide roughly equivalent configuration speeds but are slower than SelectMAP.

# **PROM Selection Guide**

Use Table 3-8 to determine which PROMs go with which Virtex-II FPGAs.

| Virtex-II | Bitstream        | PROM              | Family         |                  | PR   | OM Pac           | kage |                  |

|-----------|------------------|-------------------|----------------|------------------|------|------------------|------|------------------|

| Device    | Length<br>(bits) | 18Vxx             | 17Vxx          | V08              | SO20 | PC20             | PC44 | VQ44             |

| XCV2V40   | 360,096          | 18V01             | 17V01          | x <sup>(1)</sup> | x    | х                |      | x <sup>(2)</sup> |

| XCV2V80   | 635,296          | 18V01             | 17V01          | x <sup>(1)</sup> | x    | x                |      | x <sup>(2)</sup> |

| XCV2V250  | 1,697,184        | 18V02             | 17V02          |                  |      | x <sup>(1)</sup> | x    | x                |

| XCV2V500  | 2,761,888        | 18V04             | 17V04          |                  |      | x <sup>(1)</sup> | x    | x                |

| XCV2V1000 | 4,082,592        | 18V04             | 17V04          |                  |      | x <sup>(1)</sup> | x    | x                |

| XCV2V1500 | 5,659,296        | 18V04<br>18V02    | 17V08          |                  |      |                  | x    | x                |

| XCV2V2000 | 7,492,000        | 2, 18V04          | 17V08          |                  |      |                  | x    | x                |

| XCV2V3000 | 10,494,368       | 3, 18V04          | 17V16          |                  |      |                  | x    | x                |

| XCV2V4000 | 15,659,936       | 4, 18V04          | 17V16          |                  |      |                  | x    | x                |

| XCV2V6000 | 21,849,504       | 5, 18V04<br>18V02 | 17V16<br>17V08 |                  |      |                  | x    | x                |

| XCV2V8000 | 29,063,072       | 7,18V04           | 2, 17V16       |                  |      |                  | x    | x                |

Table 3-8: Using Virtex-II Devices With PROMs

#### Notes:

1. 17Vxx only

2. 18Vxx only

# **Master Serial Programming Mode**

In serial configuration mode, the FPGA is configured by loading one bit per CCLK cycle. In Master Serial mode, the FPGA drives the CCLK pin. In Slave Serial mode, the FPGAs CCLK pin is driven by an external source. In both serial configuration modes, the MSB of each data byte is always written to the DIN pin first.

The Master Serial mode is designed so the FPGA can be configured from a Serial PROM, Figure 3-10. The speed of the CCLK is selectable by BitGen options, see Appendix B, "BitGen and PROMGen Switches and Options." Be sure to select a CCLK speed supported by the PROM.

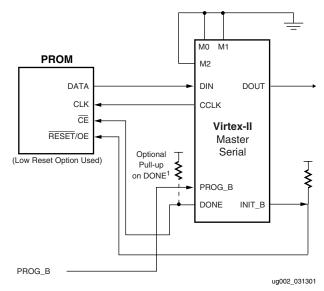

Figure 3-10 shows a Master Serial FPGA configuring from a PROM.

Figure 3-10: Master Serial Mode Circuit Diagram

#### Notes:

1. If the Virtex-II device has not selected the DriveDONE option, then an external pull-up resistor of  $330\Omega$  should be added to the DONE pin. This pull-up resistor is not needed if DriveDONE = Yes.

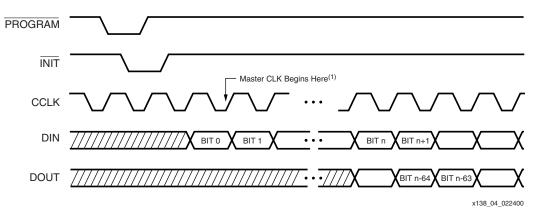

Figure 3-11: Master Serial Configuration Cloaking Sequence

#### Notes:

1. For Master configurations, the CCLK does not transition until after initialization as indicated by the arrow.

# **Slave Serial Programming Mode**

In serial configuration mode, the FPGA is configured by loading one bit per CCLK cycle. In Slave Serial mode, the FPGAs CCLK pin is driven by an external source. In both serial configuration modes, the MSB of each data byte is always written to the DIN pin first.

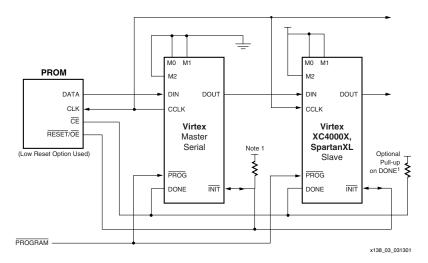

The Slave Serial configuration mode allows for FPGAs to be configured from other logic devices, such as microprocessors, or in a daisy-chain fashion. Figure 3-12 shows a Master Serial FPGA configuring from a PROM with a Slave Serial FPGA in a daisy-chain with the Master.

# **Daisy-Chain Configuration**

Virtex-II FPGAs can be used in a daisy-chain configuration only with XC4000X, SpartanXL, Spartan-II or other Virtex FPGAs. There are no restrictions on the order of the chain. However, if a Virtex-II FPGA is placed as the Master and a non-Virtex-II FPGA is placed as a slave, select a configuration CCLK speed supported by *all* devices in the chain.

The separate bitstreams for the FPGAs in a daisy-chain are required to be combined into a single PROM file, by using either the PROM File Formatter or the PROMGen utility (see Appendix B, "BitGen and PROMGen Switches and Options"). Separate PROM files can *not* be simply concatenated together to form a daisy-chain bitstream.

Figure 3-12: Master/Slave Serial Mode Circuit Diagram

#### Notes:

1. If none of the devices have been selected to DriveDONE, then an external pull-up resistor of 330  $\Omega$  should be added to the common DONE line. This pull-up resistor is not needed if DriveDONE = Yes. If used, DriveDONE should be selected only for the last device in the configuration chain.

The first device in the chain is the first to be configured. No data is passed onto the DOUT pin until all the data frames, start-up command, and CRC check have been loaded. CRC checks only include the data for the current device, not for any others in the chain. After finishing the first stream, data for the next device is loaded. The data for the downstream device appears on DOUT typically about 80 CCLK cycles after being loaded into DIN. This is due to internal packet processing. Each daisy-chained bitstream carries its own synchronization word. Nothing of the first bitstream is passed to the next device in the chain other than the daisy-chained configuration data.

The DONE\_cycle must be set before GTS, or during the same cycle to guarantee each Virtex-II device to move to the operation state when all the DONE pins have been released. When daisy-chaining multiple devices, either set the last device in the chain to DriveDONE, or add external pull-up resistors to counteract the combined capacitive loading on DONE. If non-Virtex devices are included in the daisy-chain, it is important to set their bitstreams to SyncToDONE with BitGen options. For more information on Virtex BitGen options, see Appendix B, "BitGen and PROMGen Switches and Options.".

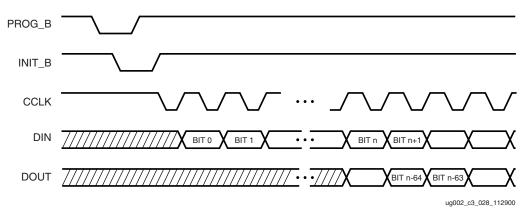

#### Figure 3-13: Serial Configuration Clocking Sequence

#### Notes:

1. For Slave configurations, a free running CCLK can be used, as shown in Figure 3-13.

|      | Description                                              | Symbol                 | Values    | Units    |

|------|----------------------------------------------------------|------------------------|-----------|----------|

|      | DIN setup/hold, slave mode                               | $T_{DCC}/T_{CCD}$      | 5.0/0.0   | ns, min  |

|      | DIN setup/hold, master mode                              | $T_{DSCK}/T_{SCKD}$    | 5.0/0.0   | ns, min  |

|      | DOUT                                                     | T <sub>CCO</sub>       | 12.0      | ns, max  |

| CCLK | High time                                                | T <sub>CCH</sub>       | 5.0       | ns, min  |

|      | Low time                                                 | T <sub>CCL</sub>       | 5.0       | ns, min  |

|      | Maximum Frequency                                        | F <sub>CC_SERIAL</sub> | 66        | MHz, max |

|      | Frequency Tolerance, master mode with respect to nominal |                        | +45% -30% |          |

Table 3-9:

Master/Slave Serial Mode Programming Switching

# Master SelectMAP Programming Mode

The SelectMAP mode provides an 8-bit bidirectional data bus interface to the Virtex-II configuration logic that can be used for both configuration and readback. Virtex-II devices can not be serially daisy-chained when the SelectMAP interface is used. However, they can be connected in a parallel-chain as shown in Figure 3-16. The DATA pins (D0:D7), CCLK, RDWR\_B, BUSY, PROG\_B, DONE, and INIT\_B can be connected in common between all of the devices. CS\_B inputs should be kept separate so each device can be accessed individually. If all devices are to be configured with the same bitstream, readback is not being used, and CCLK is less than F<sub>CC</sub>\_SelectMAP, the CS\_B pins can be connected to a common line so the devices are configured simultaneously.

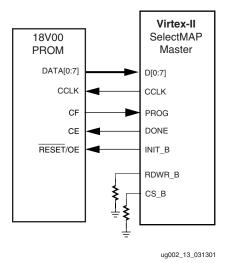

Figure 3-14: Virtex-II Interfaced With an 18V00 PROM

#### Notes:

1. If none of the Virtex-II devices have been selected to DriveDONE, add an external 330  $\Omega$  pull-up resistor to the common DONE line. This pull-up resistor is not needed if DriveDONE is selected. If used, DriveDONE should be selected only for the last device in the configuration chain.

The following pins are involved in Master SelectMAP configuration mode:

# DATA Pins (D[0:7])

The D0 through D7 pins function as a bidirectional data bus in the SelectMAP mode. Configuration data is written to the bus, and readback data is read from the bus. The bus direction is controlled by the RDWR\_B signal. see "Configuration Details" on page 387. The D0 pin is considered the MSB of each byte.

## RDWR\_B

When asserted Low, the RDWR\_B signal indicates that data is being written to the data bus. When High, the RDWR\_B signal indicates that data is being read from the data bus.

## CS\_B

The Chip Select input (CS\_B) enables the SelectMAP data bus. To write or read data onto or from the bus, the CS\_B signal must be asserted Low. When CS\_B is High, Virtex-II devices do not drive onto or read from the bus.

# CCLK

The CCLK pin is a clock output in the Master SelectMAP interface. It synchronizes all loading and reading of the data bus for configuration and readback. The CCLK pin is driven by the FPGA.

## Data Loading

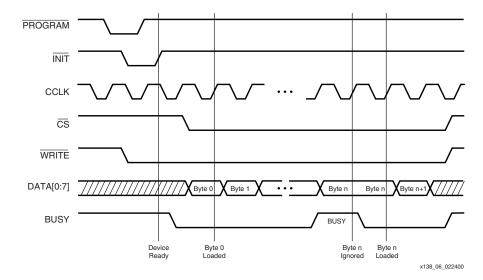

To load data in the Master SelectMAP mode, a data byte is loaded on every rising CCLK edge as shown in Figure 3-15. If the CCLK frequency is less than  $F_{CC}$  SelectMAP, this can be done without handshaking. For frequencies above  $F_{CC}$  SelectMAP, the BUSY signal must be monitored. If BUSY is High, the current byte must be reloaded when BUSY is Low.

The first byte can be loaded on the first rising CCLK edge that INIT\_B is High, and when both CS\_B and RDWR\_B are asserted Low. CS\_B and RDWR\_B can be asserted anytime before or after INIT\_B has gone High. However, the SelectMAP interface is not active until after INIT\_B has gone High. The order of CS\_B and RDWR\_B does not matter, but RDWR\_B must be asserted throughout configuration. If RDWR\_B is de-asserted before all data has been loaded, the FPGA aborts the operation. To complete configuration, the FPGA must be reset by PROG\_B and reconfigured with the entire stream. For applications that need to de-assert RDWR\_B between bytes, see "Controlled CCLK" on page 367.

Figure 3-15: Data Loading in SelectMAP

# Slave SelectMAP Programming Mode

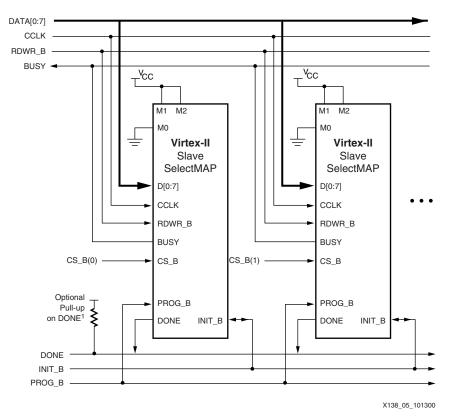

The SelectMAP mode provides an 8-bit bidirectional data bus interface to the Virtex-II configuration logic that can be used for both configuration and readback. Virtex-II devices can not be serially daisy-chained when the SelectMAP interface is used. However, they can be connected in a parallel-chain as shown in Figure 3-16. The DATA pins (D0:D7), CCLK, RDWR\_B, BUSY, PROG\_B, DONE, and INIT\_B can be connected in common between all of the devices. CS\_B inputs should be kept separate so each device can be accessed individually. If all devices are to be configured with the same bitstream, readback is not being used, and CCLK is less than  $F_{CC}$ \_SelectMAP, the CS\_B pins can be connected to a common line so the devices are configured simultaneously.

Although Figure 3-16 does not show a control module for the SelectMAP interface, the SelectMAP interface is typically driven by a processor, micro controller, or some other logic device such as an FPGA or a CPLD.

Figure 3-16: Slave SelectMAP Mode Circuit Diagram

#### Notes:

1. If none of the Virtex-II devices have been selected to DriveDONE, add an external 330  $\Omega$  pull-up resistor to the common DONE line. This pull-up resistor is not needed if DriveDONE = Yes. If used, DriveDONE should be selected only for the last device in the configuration chain.

The following pins are involved in Slave SelectMAP configuration mode:

www.xilinx.com

1-800-255-7778

# DATA Pins (D[0:7])

The D0 through D7 pins function as a bidirectional data bus in the SelectMAP mode. Configuration data is written to the bus, and readback data is read from the bus. The bus direction is controlled by the RDWR\_B signal. see "Configuration Details" on page 387.. The D0 pin is considered the MSB of each byte. When asserted Low, the RDWR\_B signal indicates that data is being written to the data bus. When asserted High, the RDWR\_B signal indicates that data is being read from the data bus.

# CS\_B

The Chip Select input (CS\_B) enables the SelectMAP data bus. To write or read data onto or from the bus, the CS\_B signal must be asserted Low. When CS\_B is High, Virtex-II devices do not drive onto or read from the bus.

# BUSY

When CS\_B is asserted, the BUSY output indicates when the FPGA can accept another byte. If BUSY is Low, the FPGA reads the data bus on the next rising CCLK edge where both CS\_B and RDWR\_B are asserted Low. If BUSY is High, the current byte is ignored and must be reloaded on the next rising CCLK edge when BUSY is Low. When CS\_B is *not* asserted, BUSY is 3-stated.

BUSY is only necessary for CCLK frequencies above  $F_{CC}$  SelectMAP. For frequencies at or below  $F_{CC}$  SelectMAP, BUSY is ignored, see "Data Loading" on page 363. For parallel chains, as shown in Figure 3-16, where the same bitstream is to be loaded into multiple devices simultaneously, BUSY should not be used. Thus, the maximum CCLK frequency for such an application must be less than  $F_{CC}$  SelectMAP.

# CCLK

Unlike the Master SelectMAP mode of configuration, the CCLK pin is an input in the Slave SelectMAP mode interface. The CCLK signal synchronizes all loading and reading of the data bus for configuration and readback. Additionally, the CCLK drives internal configuration circuitry. The CCLK can be driven either by a free running oscillator or an externally-generated signal.

Several scenarios exist when configuring the FPGA in SelectMAP mode, depending on the source of CCLK.

## Free-Running CCLK

A free-running oscillator can be used to drive Virtex-II CCLK pins. For applications that can provide a continuous stream of configuration data, refer to the timing diagram discussed in "Data Loading" on page 363. For applications that cannot provide a continuous data stream, missing the clock edges, refer to the timing diagram discussed in "Non-Contiguous Data Strobe" on page 366. An alternative to a free-running CCLK is discussed in "Controlled CCLK" on page 367.

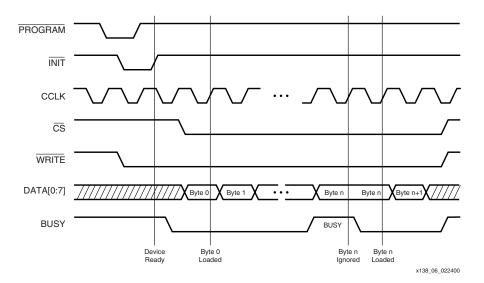

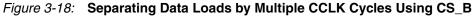

## Express-Style Loading

In express-style loading, a data byte is loaded on every rising CCLK edge as shown in Figure 3-17. If the CCLK frequency is less than  $F_{CC}$  SelectMAP, this can be done without handshaking. For frequencies above  $F_{CC}$  SelectMAP, the BUSY signal must be monitored. If BUSY is High, the current byte must be reloaded when BUSY is Low.

The first byte can be loaded on the first rising CCLK edge that INIT\_B is High, and when both CS\_B and RDWR\_B are asserted Low. CS\_B and RDWR\_B can be asserted anytime before or after INIT\_B has gone High. However, the SelectMAP interface is not active until after INIT\_B has gone High. The order of CS\_B and RDWR\_B does not matter, but RDWR\_B must be asserted throughout configuration. If RDWR\_B is de-asserted before all data has been loaded, the FPGA aborts the operation. To complete configuration, the FPGA must be reset by PROG\_B and reconfigured with the entire stream.

For applications that need to de-assert RDWR\_B between bytes, see "Controlled CCLK" on page 367.

Figure 3-17: "Express Style" Continuous Data Loading in SelectMAP

#### Non-Contiguous Data Strobe

In applications where multiple clock cycles might be required to access the configuration data before each byte can be loaded into the SelectMAP interface, data might not be ready for each consecutive CCLK edge. In such a case, the CS\_B signal can be de-asserted until the next data byte is valid on the DATA[0:7] pins. This is demonstrated in Figure 3-18. While CS\_B is High, the SelectMAP interface does not expect any data and ignores all CCLK transitions. However, RDWR\_B must continue to be asserted while CS\_B is asserted. If RDWR\_B is High during a positive CCLK transition while CS\_B is asserted, the FPGA aborts the operation. For applications that need to de-assert the RDWR\_B signal without de-asserting CS\_B, see "Controlled CCLK".

## Controlled CCLK

Some applications require that RDWR\_B be de-asserted between the loading of configuration data bytes asynchronously from the CS\_B. Typically, this would be due to the RDWR\_B signal being a common connection to other devices on the board, such as memory storage elements. In such a case, driving CCLK as a controlled signal instead of a free-running oscillator makes this type of operation possible. In Figure 3-19, the CCLK, CS\_B, and RDWR\_B are asserted Low while a data byte becomes active. Once the CCLK has gone High, the data is loaded. RDWR\_B can be de-asserted and re-asserted as many times as necessary, just as long as it is Low before the next rising CCLK edge.

Figure 3-19: Controlling CCLK for RDWR\_B De-Assertion

|      | Description                         | Symbol                                   | Value   | Units    |  |  |  |

|------|-------------------------------------|------------------------------------------|---------|----------|--|--|--|

|      | D <sub>0-7</sub> Setup/Hold         | T <sub>SMDCC</sub> /T <sub>SMCCD</sub>   | 5.0/0.0 | ns, min  |  |  |  |

| CCLK | CS_B Setup/Hold                     | T <sub>SMCSCC</sub> /T <sub>SMCCCS</sub> | 7.0/0.0 | ns, min  |  |  |  |

|      | RDWR_B Setup/Hold                   | T <sub>SMCCW</sub> /T <sub>SMWCC</sub>   | 7.0/0.0 | ns, min  |  |  |  |

|      | BUSY Propagation Delay              | T <sub>SMCKBY</sub>                      | 12.0    | ns, max  |  |  |  |

|      | Maximum Frequency                   | F <sub>CC</sub> _SelectMAP               | 66      | MHz, max |  |  |  |

|      | Maximum Frequency with no handshake | F <sub>CCNH</sub>                        | 66      | MHz, max |  |  |  |

Table 3-10: SelectMAP Write Timing Characteristics

# JTAG/ Boundary Scan Programming Mode

# Introduction

Virtex-II devices support the new IEEE 1532 standard for In-System Configuration (ISC), based on the IEEE 1149.1 standard. The IEEE 1149.1 Test Access Port and Boundary-Scan Architecture is commonly referred to as JTAG. JTAG is an acronym for the Joint Test Action Group, the technical subcommittee initially responsible for developing the standard. This standard provides a means to assure the integrity of individual components and the interconnections between them at the board level. With increasingly dense multi-layer PC boards, and more sophisticated surface mounting techniques, boundary-scan testing is becoming widely used as an important debugging standard.

Devices containing boundary-scan logic can send data out on I/O pins in order to test connections between devices at the board level. The circuitry can also be used to send signals internally to test the device specific behavior. These tests are commonly used to detect opens and shorts at both the board and device level.

In addition to testing, boundary-scan offers the flexibility for a device to have its own set of user-defined instructions. The added common vendor specific instructions, such as configure and verify, have increased the popularity of boundary-scan testing and functionality.

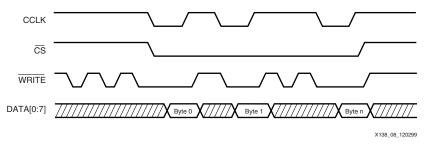

# Boundary-Scan for Virtex-II Devices Using IEEE Standard 1149.1

The Virtex-II family is fully compliant with the IEEE Standard 1149.1 Test Access Port and Boundary-Scan Architecture. The architecture includes all mandatory elements defined in the IEEE 1149.1 Standard. These elements include the Test Access Port (TAP), the TAP controller, the instruction register, the instruction decoder, the boundary-scan register, and the bypass register. The Virtex-II family also supports some optional instructions; the 32-bit identification register, and a configuration register in full compliance with the standard. Outlined in the following sections are the details of the JTAG architecture for Virtex-II devices.

## Test Access Port

The Virtex-II TAP contains four mandatory dedicated pins as specified by the protocol (Table 3-11).

| Pin              | Description      |  |

|------------------|------------------|--|

| TDI Test Data In |                  |  |

| TDO              | Test Data Out    |  |

| TMS              | Test Mode Select |  |

| TCK Test Clock   |                  |  |

Table 3-11:

Virtex-II TAP Controller Pins

There are three input pins and one output pin to control the 1149.1 boundary-scan TAP controller. There are optional control pins, such as TRST (Test Reset) and enable pins, which might be found on devices from other manufacturers. It is important to be aware of these optional signals when interfacing Xilinx devices with parts from different vendors, because they might need to be driven.

The TAP controller is a 16-state state machine shown in Figure 3-20. The four mandatory TAP pins are outlined below.

• TMS - This pin determines the sequence of states through the TAP controller on the rising edge of TCK. TMS has an internal resistive pull-up to provide a logic High if the pin is not driven.

- TCK This pin is the JTAG test clock. It sequences the TAP controller and the JTAG registers in the Virtex-II devices.

- TDI This pin is the serial input to all JTAG instruction and data registers. The state of the TAP controller and the current instruction held in the instruction register determine which register is fed by the TDI pin for a specific operation. TDI has an internal resistive pull-up to provide a logic High to the system if the pin is not driven. TDI is applied into the JTAG registers on the rising edge of TCK.

- TDO This pin is the serial output for all JTAG instruction and data registers. The state of the TAP controller and the current instruction held in the instruction register determine which register (instruction or data) feeds TDO for a specific operation. TDO changes state on the falling edge of TCK and is only active during the shifting of instructions or data through the device. This pin is 3-stated at all other times.

#### Notes:

As specified by the IEEE Standard, the TMS and TDI pins all have internal pull-up resistors. These internal pull-up resistors of 50-150 k $\Omega$  are active, regardless of the mode selected.

JTAG inputs are independent of  $\rm V_{CCO}$  and work between 2.5 V and 3.3 V TTL levels. TDO is sourced from  $\rm V_{CCAUX}.$

#### **TAP Controller**

Figure 3-20 diagrams a 16-state finite state machine. The four TAP pins control how data is scanned into the various registers. The state of the TMS pin at the rising edge of TCK determines the sequence of state transitions. There are two main sequences, one for shifting data into the data register and the other for shifting an instruction into the instruction register.

NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

x139\_01\_112399

#### Figure 3-20: State Diagram for the TAP Controller

3

## **Boundary-Scan Instruction Set**

To determine the operation to be invoked, an instruction is loaded into the Instruction Register (IR). The Instruction Register is 6 bits long in Virtex-II devices to support the new IEEE Standard 1532 for In-System Configurable (ISC) devices. Table 3-12 lists the available instructions for Virtex-II devices.

| Boundary Scan<br>CommandBinary Code(5:0) |                 | Description                                             |  |  |

|------------------------------------------|-----------------|---------------------------------------------------------|--|--|

| EXTEST                                   | 000000          | Enables boundary-scan EXTEST operation                  |  |  |

| SAMPLE                                   | 000001          | Enables boundary-scan SAMPLE operation                  |  |  |

| USER1                                    | 000010          | Access user-defined register 1                          |  |  |

| USER2                                    | 000011          | Access user-defined register 2                          |  |  |

| CFG_OUT                                  | 000100          | Access the configuration bus for readback               |  |  |

| CFG_IN                                   | 000101          | Access the configuration bus for configuration          |  |  |

| INTEST                                   | 000111          | Enables boundary-scan INTEST operation                  |  |  |

| USERCODE                                 | 001000          | Enables shifting out user code                          |  |  |

| IDCODE                                   | 001001          | Enables shifting out of ID code                         |  |  |

| HIGHZ                                    | 001010          | 3-states output pins while enabling the bypass register |  |  |

| JSTART                                   | 001100          | Clocks the start-up sequence when StartClk is TCK       |  |  |

| JSHUTDOWN                                | 001101          | Clocks the shutdown sequence                            |  |  |

| BYPASS                                   | 111111          | Enables BYPASS                                          |  |  |

| JPROG_B                                  | 001011          | Equivalent to and has the same affect as PROG_B         |  |  |

| RESERVED                                 | All other codes | Xilinx reserved instructions                            |  |  |

Table 3-12: Virtex-II Boundary Scan Instructions

The mandatory IEEE 1149.1 commands are supported in Virtex-II devices, as well as several Xilinx vendor-specific commands. Virtex-II devices have a powerful command set. The EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions are all included. The TAP also supports two internal user-defined registers (USER1 and USER2) and configuration/readback of the device. The Virtex-II boundary-scan operations are independent of mode selection. The boundary-scan mode in Virtex-II devices overrides other mode selections. For this reason, boundary-scan instructions using the boundary-scan register (SAMPLE/PRELOAD, INTEST, EXTEST) must not be performed during configuration. All instructions except USER1 and USER2 are available before a Virtex-II device is configured. After configuration, all instructions are available.

JSTART and JSHUTDOWN are instructions specific to the Virtex-II architecture and configuration flow. As described in Table 3-12, the JSTART and JSHUTDOWN instructions clock the startup sequence when the appropriate bitgen option is selected. The instruction does not work correctly without the correct bitgen option selected.

bitgen -g startupclk:jtagclk designName.ncd

For details on the standard boundary-scan instructions EXTEST, INTEST, and BYPASS, refer to the IEEE Standard. The user-defined registers (USER1/USER2) are described in "USER1, USER2 Registers" on page 374.

## Boundary-Scan Architecture

Virtex-II device registers include all registers required by the IEEE 1149.1 Standard. In addition to the standard registers, the family contains optional registers for simplified testing and verification (Table 3-13).

| Register Name Register Length     |         | Description                                                                           |  |  |

|-----------------------------------|---------|---------------------------------------------------------------------------------------|--|--|

| Instruction register              | 6 bits  | Holds current instruction OPCODE and captures internal device status.                 |  |  |

| Boundary scan register 3 bits per |         | Controls and observes input, output, and output enable.                               |  |  |

| Bypass register                   | 1 bit   | Device bypass.                                                                        |  |  |

| Identification register           | 32 bits | Captures device ID.                                                                   |  |  |

| JTAG configuration register       | 64 bits | Allows access to the configuration bus when using the CFG_IN or CFG_OUT instructions. |  |  |

| USERCODE register                 | 32 bits | Captures user-programmable code                                                       |  |  |

Table 3-13: Virtex-II JTAG Registers

# Boundary-Scan Register

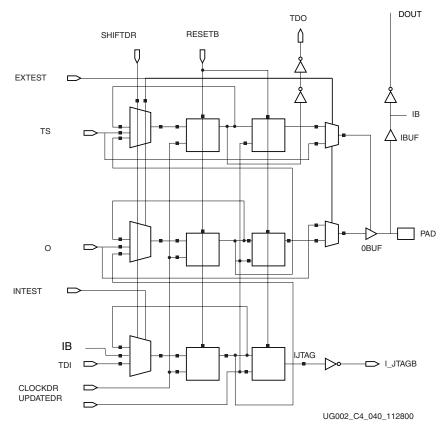

The test primary data register is the boundary-scan register. Boundary-scan operation is independent of individual IOB configurations. Each IOB, bonded or un-bonded, starts as bidirectional with 3-state control. Later, it can be configured to be an input, output, or 3-state only. Therefore, three data register bits are provided per IOB (Figure 3-21).

When conducting a data register (DR) operation, the DR captures data in a parallel fashion during the CAPTURE-DR state. The data is then shifted out and replaced by new data during the SHIFT-DR state. For each bit of the DR, an update latch is used to hold the input data stable during the next SHIFT-DR state. The data is then latched during the UPDATE-DR state when TCK is Low.

The update latch is opened each time the TAP Controller enters the UPDATE-DR state. Care is necessary when exercising an INTEST or EXTEST to ensure that the proper data has been latched before exercising the command. This is typically accomplished by using the SAMPLE/PRELOAD instruction.

Consider internal pull-up and pull-down resistors when developing test vectors for testing opens and shorts. The boundary-scan mode determines if the IOB has a pull-up resistor. Figure 3-21 is a representation of Virtex-II Boundary-Scan Architecture.

Figure 3-21: Virtex Series Boundary Scan Logic

## **Bit Sequence**

The order in each non-TAP IOB is described in this section. The input is first, then the output, and finally the 3-state IOB control. The 3-state IOB control is closest to the TDO. The input-only pins contribute only the input bit to the boundary-scan I/O data register. The bit sequence of the device is obtainable from the "Boundary-Scan Description Language Files" (BSDL files) for the Virtex family. These files can be obtained from the Xilinx software download area. The bit sequence is independent of the design. It always has the same bit order and the same number of bits.

## **Bypass Register**

The other standard data register is the single flip-flop BYPASS register. It passes data serially from the TDI pin to the TDO pin during a bypass instruction. This register is initialized to zero when the TAP controller is in the CAPTURE-DR state.

#### Instruction Register

The instruction register is a 6-bit register that loads the OPCODE necessary for the Virtex-II boundary-scan instruction set. This register loads the current OPCODE and captures internal device status.

#### Configuration Register (Boundary-Scan)

The configuration register is a 64-bit register. This register allows access to the configuration bus and readback operations.

#### Identification Register

Virtex devices have a 32-bit identification register, commonly referred to as the IDCODE register. This register is based upon IEEE Standard 1149.1 and allows easy identification of the part being tested or programmed via boundary scan.

#### Virtex-II Identification Register

The Virtex-II JTAG ID Code register has the following format.

```

3322 222222 211111111 11000000000

1098 7654321 098765432 109876543210

vvvv:fffffff:aaaaaaaaa:ccccccccccl bit positions(00 to 31)

```

#### where

```

v is the revision code and

```

- f is the 7-bit family code = 0001000 0x08

- a is the number of array rows in the part expressed in 9 bits.

| XC2V40   | = | 8 =   | 0x08  |

|----------|---|-------|-------|

| XC2V80   | = | 10 =  | 0x010 |

| XC2V250  | = | 24 =  | 0x018 |

| XC2V500  | = | 32 =  | 0x020 |

| XC2V1000 | = | 40 =  | 0x028 |

| XC2V1500 | = | 48 =  | 0x030 |

| XC2V2000 | = | 56 =  | 0x038 |

| XC2V3000 | = | 64 =  | 0x040 |

| XC2V4000 | = | 80 =  | 0x050 |

| XC2V6000 | = | 96 =  | 0x060 |

| XC2V8000 | = | 112 = | 0x070 |

c is the company code = 00001001001 = 0x049\*

\*Since the last bit of the JTAG IDCODE is always one, the last three hex digits appear as 0x093.

|           | vvvv | ffff | fff | а | aaaa | aaaa | CCCC | CCCC | CCCC |

|-----------|------|------|-----|---|------|------|------|------|------|

| XC2V250   |      | 0001 | 000 | 0 | 0001 | 1000 | 0000 | 1001 | 0011 |

| AC2 V 250 | v    | 1    | 0   |   | 1    | 8    | 0    | 9    | 3    |

| XC2V500   | v    | 1    | 0   |   | 2    | 0    | 0    | 9    | 3    |

ID Codes assigned to Virtex-II FPGAs are shown in Table 3-14.

| FPGA     | IDCODE    |

|----------|-----------|

| XC2V40   | v01008093 |

| XC2V80   | v01010093 |

| XC2V250  | v01018093 |

| XC2V500  | v01020093 |

| XC2V000  | v01028093 |

| XC2V1500 | v01030093 |

| XC2V2000 | v01038093 |

| XC2V3000 | v01040093 |

| XC2V4000 | v01050093 |

| XC2V6000 | v01060093 |

| XC2V8000 | v01070093 |

Table 3-14:

Virtex-II Device ID Codes

Notes:

1. The "v" in the IDCODE is the revision code field.

#### **USERCODE** Register

USERCODE is supported in the Virtex family as well. This register allows a user to specify a design-specific identification code. The USERCODE can be programmed into the device and read back for verification at a later time. The USERCODE is embedded into the bitstream during bitstream generation (bitgen -g UserID option) and is valid only after configuration.

## **USER1, USER2 Registers**

The USER1 and USER2 registers are only valid after configuration. These two registers must be defined by the user within the design. These registers can be accessed after they are defined by the TAP pins.

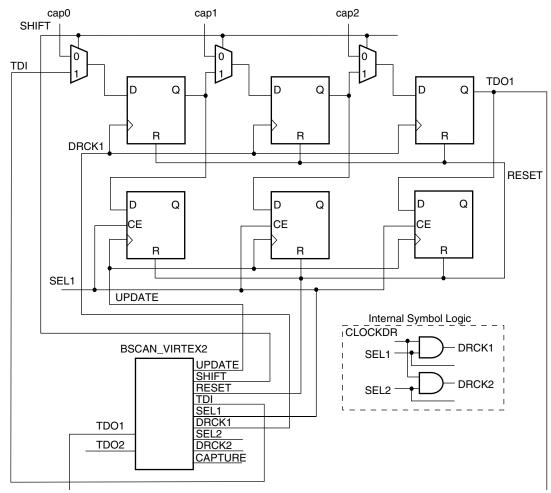

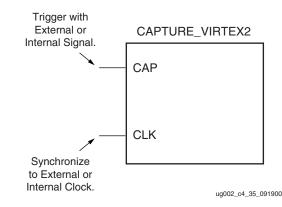

The BSCAN\_VIRTEX2 library macro is required when creating these registers. This symbol is only required for driving internal scan chains (USER1 and USER2). The BSCAN\_VIRTEX2 macro provides two user pins (SEL1 and SEL2) for determining usage of USER1 or USER2 instructions respectively. For these instructions, two corresponding pins (TDO1 and TDO2) allow user scan data to be shifted out of TDO. In addition, there are individual clock pins (DRCK1 and DRCK2) for each user register. There is a common input pin (TDI) and shared output pins that represent the state of the TAP controller (RESET, SHIFT, and UPDATE). Unlike earlier FPGA families that required the BSCAN macro to dedicate TAP pins for boundary scan, Virtex-II TAP pins are dedicated and do not require the BSCAN\_VIRTEX2 macro for normal boundary-scan instructions or operations.

Note that these are user-defined registers. The example (Figure 3-22) is one of many implementations. For HDL, the BSCAN\_VIRTEX2 macro needs to be instantiated in the design.

3

Figure 3-22: BSCAN\_VIRTEX2 (Example Usage)

www.xilinx.com 1-800-255-7778

# Using Boundary Scan in Virtex-II Devices

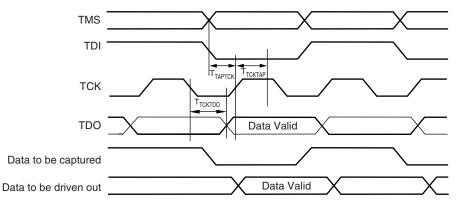

Characterization data for some of the most commonly requested timing parameters shown in Figure 3-23 is listed in Table 3-15.

x139\_05\_020300

Figure 3-23: Virtex-II Boundary Scan Port Timing Waveforms

#### Table 3-15: Boundary-Scan Port Timing Specifications

| Symbol              | Parameter                            | Value | Units    |

|---------------------|--------------------------------------|-------|----------|

| T <sub>TAPTCK</sub> | TMS and TDI setup time before TCK    | 4.0   | ns, min  |

| T <sub>TCKTAP</sub> | TMS and TDI hold times after TCK     | 2.0   | ns, min  |

| T <sub>TCKTDO</sub> | TCK falling edge to TDO output valid | 11.0  | ns, min  |

| F <sub>TCK</sub>    | Maximum TCK clock frequency          | 33.0  | MHz, max |

For further information on the Startup sequence, bitstream, and internal configuration registers referenced here, refer to "Readback" on page 396.

## Configuring Through Boundary-Scan

One of the most common boundary-scan vendor-specific instructions is the configure instruction. An individual Virtex-II device is configured via JTAG on power-up using TAP. If the Virtex-II device is configured on power-up, it is advisable to the mode pins to the boundary-scan configuration mode settings; 101 (M2 = 1, M1 = 0, M0 = 1).

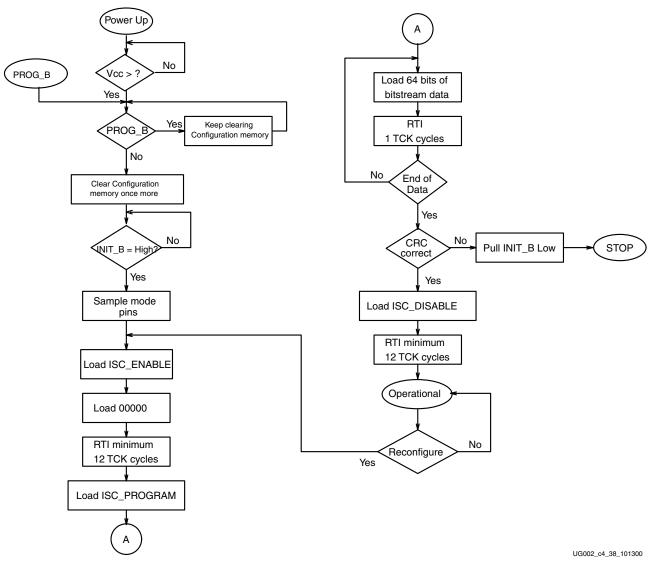

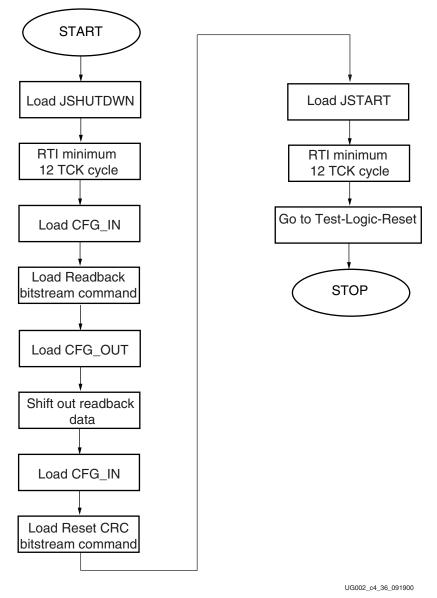

Configuration flow for Virtex-II device configuration with JTAG is shown in Figure 3-24. The sections that follow describe how the Virtex-II device can be configured as a single device via boundary-scan or as part of a multiple-device scan chain.

A configured device can be reconfigured by toggling the TAP and entering a CFG\_IN instruction after pulsing the PROG\_B pin or issuing the shut-down sequence. (Refer to "Power Up" on page 347). For additional details on power-up or the start-up sequence in Virtex-II devices, see "Device Startup" on page 349.

For additional detailed information on using Virtex devices in an embedded solution, see Xilinx application note XAPP058.

Figure 3-24: Device Configuration Flow Diagram

#### Single Device Configuration

Configure a Virtex-II part as a single device via boundary-scan operations as follows. Ensure that the bitstream is generated with the JTAG clock option.

bitgen -g startupclk:jtagclk designName.ncd

Also, when using JTAG Programmer software, verify that the most current version is being used.

Table 3-16 describes the TAP controller commands required to configure a Virtex-II device. Refer to Figure 3-20 for TAP controller states. These TAP controller commands are issued automatically if configuring the part with the JTAG Programmer software.

| TAD Controller Stor Description |                                                                                                                                      | Set & H                           | old | # of Clocks                |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|----------------------------|

|                                 | TAP Controller Step Description                                                                                                      |                                   | TMS | тск                        |

| 1                               | On power-up, place a logic "one" on the TMS and clock the TCK five times. This ensures starting in the TLR (Test-Logic-Reset) state. | х                                 | 1   | 5                          |

| 2                               | Move into the RTI state.                                                                                                             | Х                                 | 0   | 1                          |

| 3                               | Move into the SELECT-IR state.                                                                                                       | Х                                 | 1   | 2                          |

| 4                               | Enter the SHIFT-IR state.                                                                                                            | Х                                 | 0   | 2                          |

| 5                               | Start loading the CFG_IN instruction.                                                                                                | 00101                             | 0   | 5                          |

| 6                               | Load the last bit of CFG_IN instruction when exiting SHIFT-IR. as defined in the IEEE standard.                                      | 0                                 | 1   | 1                          |

| 7                               | Enter the SELECT-DR state.                                                                                                           | Х                                 | 1   | 2                          |

| 8                               | Enter the SHIFT-DR state.                                                                                                            | Х                                 | 0   | 2                          |

| 9                               | Shift in the Virtex-II bitstream. $Bit_n$ (MSB) is the first bit in the bitstream <sup>1</sup> .                                     | bit <sub>1</sub> bit <sub>n</sub> | 0   | (bits in<br>bitstream) – 1 |

| 10                              | Shift in the last bit of the bitstream. $Bit_0$ (LSB) shifts on the transition to EXIT1-DR.                                          | bit <sub>0</sub>                  | 1   | 1                          |

| 11                              | Enter UPDATE-DR state.                                                                                                               | Х                                 | 1   | 1                          |

| 12                              | Enter the SELECT-IR state.                                                                                                           | Х                                 | 1   | 2                          |

| 13                              | Move to the SHIFT-IR state.                                                                                                          | Х                                 | 0   | 2                          |

| 14                              | Start loading the JSTART instruction. The JSTART instruction initializes the startup sequence.                                       | 01100                             | 0   | 5                          |

| 15                              | Load the last bit of the JSTART instruction.                                                                                         | 0                                 | 1   | 1                          |

| 16                              | Move to RTI and clock the STARTUP sequence by applying a minimum of 12 clock cycles to the TCK.                                      | х                                 | 0   | ≥12                        |

| 17                              | Move to the TLR state. The device is now functional.                                                                                 | Х                                 | 1   | 3                          |

Table 3-16: Single Device Configuration Sequence

#### Notes:

1. In the Configuration Register, data is shifted in from the right (TDI) to the left (TDO).

#### Multiple Device Configuration

It is possible to configure multiple Virtex-II devices in a chain. The devices in the JTAG chain are configured one at a time. The multiple device configuration steps are described generally to be applied to any size chain. Ensure the bitstream is generated with the JTAG clock option.

bitgen -g startupclk:jtagclk designName.ncd

Refer to the State Diagram in Figure 3-20 for the following TAP controller steps.

- 1. On power-up, place a logic "one" on the TMS and clock the TCK five times. This ensures starting in the TLR (Test-Logic-Reset) state.

- 2. Load the CFG\_IN instruction into the target device (and BYPASS in all other devices).Go through RTI (RUN-TEST/IDLE).

Repeat steps 2 through 4 for each successive device.

- 3. Load the JSTART command into all devices.

- 4. Go to RTI and clock TCK 12 times.

All devices are active at this point.

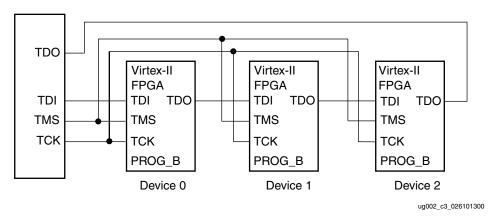

Figure 3-25: Boundary Scan Chain of Devices

Notes:

1. PROG\_B pin should be deasserted during JTAG operation.

## Reconfiguring Through Boundary Scan

The ability of Virtex-II devices to perform partial reconfiguration is the reason that the configuration memory is not cleared when reconfiguring the device. When reconfiguring a chain of devices, refer to step 3 in Table 3-16. There are two methods to reconfigure Virtex-II devices without possible internal contention. The first method is to pulse the PROG\_B pin which resets the internal configuration memory. The alternate method is to perform a shutdown sequence, placing the device in a safe state. The following shutdown sequence includes using internal registers. (For details on internal registers, refer to "Readback" on page 396.)

- 1. Load the CFG\_IN instruction.

- 2. In SHIFT-DR state, load the synchronization word followed by the Reset CRC Register (RCRC) command.

| 1111 | 1111 | 1111 | 1111 | 1111 | 1111 | 1111 | 1111 | -> Dummy word                    |

|------|------|------|------|------|------|------|------|----------------------------------|

| 1010 | 1010 | 1001 | 1001 | 0101 | 0101 | 0110 | 0110 | -> Synchronization word          |

| 0011 | 0000 | 0000 | 0000 | 1000 | 0000 | 0000 | 0001 | -> Header: Write to CMD register |

| 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 | -> RCRC command                  |

| 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | -> flush pipe                    |

| 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | -> flush pipe                    |

|      |      |      |      |      |      |      |      |                                  |

- 3. Load JSHUTDOWN.

- 4. Go to RTI and clock TCK at least 12 times to clock the shutdown sequence.

- 5. Proceed to SHIFT-IR state and load the CFG\_IN instruction again.

- 6. Go to SHIFT-DR state and load the configuration bits. Make sure the configuration bits contain AGHIGH command, which asserts the global signal GHIGH\_B. This prevents contention while writing configuration data.

- 7. When all configuration bits have been loaded, go to SHIFT-IR state and load the JSTART instruction.

- 8. Go to RTI and clock TCK at least 12 times to clock the startup sequence.

- 9. Go to TLR state to complete the reconfiguration process.

## **Debugging Configuration**

To verify successful configuration, there are several options. Some of the most helpful verification steps include using TAP pins and the readback command. Using the Virtex-II TAP controller and status pins is discussed first.

When using TAP controller pins, TDO is driven only in the SHIFT-DR and SHIFT-IR state. If the output of the TDO can be changed via an external pull-up resistor, the TAP is not in SHIFT-IR or SHIFT-DR. If the TAP can be controlled precisely, use this to test the application.

In JTAG configuration, the status pin (DONE) functions the same as in the other configuration modes. The DONE pin can be monitored to determine if a bitstream has been completely loaded into the device. If DONE is Low, the entire bitstream has not been sent or the start-up sequence is not finished. If DONE is High, the entire bitstream has been received correctly. The INIT\_B pin functions similar to a normal INIT\_B but does not indicate a configuration error in boundary-scan configuration.

In addition to external pin monitoring, an internal test can be conducted. The second method includes the following steps to capture the internal device status register contents:

- 1. Move the TAP to TLR state.

- 2. Go to SHIFT-IR state and load in the CFG\_IN instruction.

- 3. Go to SHIFT-DR state and shift in the following 64-bit pattern with the MSB (left-most bit), shifted in first.

1. Since the JTAG readback shift register is 64-bit long, two 32-bit words are needed to fill the shift register.

- 4. After shifting in the pattern, load the CFG\_OUT instruction in the SHIFT-IR state.

- 5. Move to SHIFT-DR state and clock TCK 32 times while reading TDO. The data seen on TDO is the content of the status register. The last bit out is a one if a CRC error occurred. If successful, it should read as follows.

Notes:

1. MMM is the mode pins value.

2. Assuming that the device is in normal operation mode.

Since the read status activity causes the crc\_error status to be asserted, it is important to clear the crc\_error status to ensure normal device operation. This can be done by writing the precalculated CRC value to the CRC register or writing an RCRC command.

- 6. Go to SHIFT-IR state and load the CFG\_IN instruction again.

- 7. Move to SHIFT-DR state and shift in the following bit pattern:

0011

0000

0000

1000

0000

0001 -> Header: Write to CMD register

0000

0000

0000

0000

0000

0111 -> RCRC command

0000

0000

0000

0000

0000

0000 -> flush pipe

0000

0000

0000

0000

0000

0000 -> flush pipe

8. Put the TAP in TLR state when finished.

The device status register also gives the status of the DONE and INIT\_B signals. For information on the status register, refer to Figure 3-30.

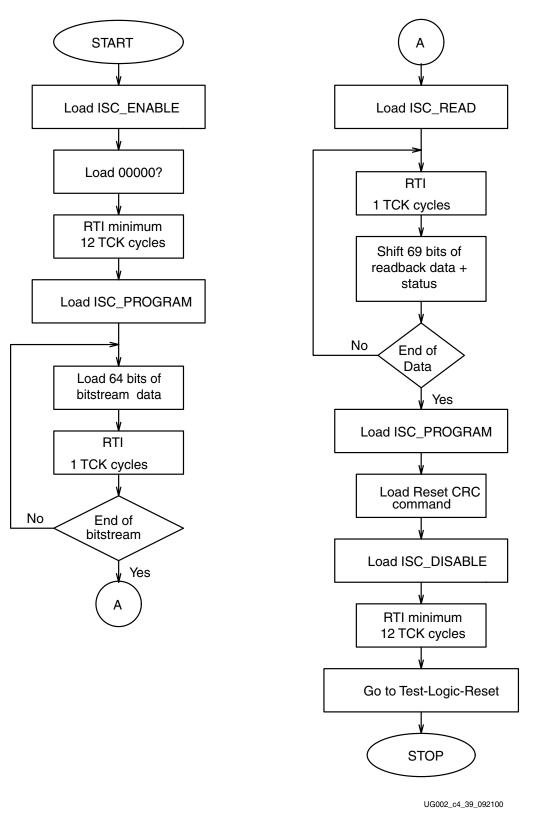

## Boundary-Scan for Virtex-II Devices Using IEEE Standard 1532

**ISC Modal States**

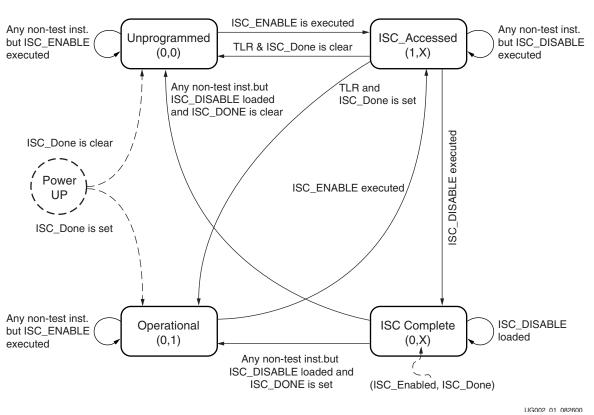

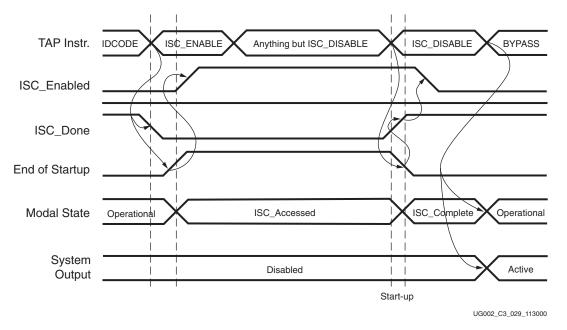

Figure 3-26: ISC Modal States

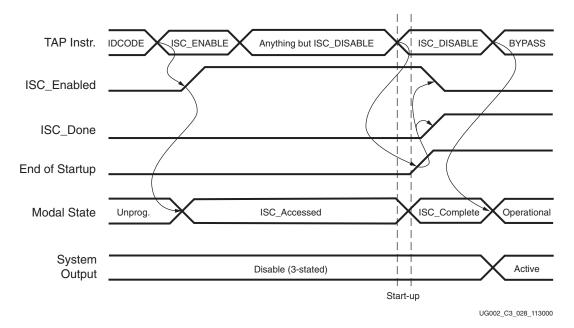

Once the device is powered up, it goes to an Unprogrammed state. The I/Os are all either 3-stated or pulled up. When ISC\_ENABLE is successfully executed, the ISC\_Enabled signal is asserted, and the device moves to ISC\_Accessed state. When the device moves to ISC\_Accessed state from Operational state, the shutdown sequence is executed. The I/Os are all either 3-stated or pulled up.

The StartUp sequence is executed when in the ISC\_Accessed state. At the end of the StartUp Sequence, ISC\_Enabled is cleared and the device moves to ISC\_Complete. The minimum clock cycle requirement is the number of clock cycles required to complete the StartUp sequence. At the completion of the minimum required clock cycles, ISC\_Enabled is deasserted.

Whether the StartUp sequence is successful or not is determined by CRC or configuration error status from the configuration processor. If the startup is completed, ISC\_Done is asserted; otherwise, ISC\_Done stays Low. The I/Os are either 3-stated or pulled up.