Digital TV

# FPGAs Provide Flexibility in Digital TV Development

Cost sensitive consumer applications, such as digital TVs, can now benefit from the many advantages of Spartan series programmable logic devices.

by Robert Green, Manager Strategic Solutions, Digital Audio-Video Xilinx, Inc. robert.green@xilinx.com

Broadcasters are very interested in creating new revenue from digital television services. However, a vast range of evolving digital television (DTV) standards in transmission, image processing, interconnectivity, and display interfaces can create considerable barriers to speedy implementation. Yet, the industry promotes digital broadcasting, highlighting better video and sound quality to attract new subscribers from the analog world. Consumer adoption of digital TV is important if broadcasters are to adhere to the schedule of analog switch-off.

Bandwidth is precious; to make the most of it, compression schemes have steadily improved and new algorithms are in development to push the envelope even further. As such, system-processing rates have increased over time, and real-time image processing is now an ideal way of meeting these requirements while removing memory overhead. At the same time, Moore's Law has resulted in low cost programmable logic devices, such as the new Spartan<sup>TM</sup>-IIE FPGAs, that provide the same functionality and performance previously only found in expensive professional broadcast products.

# Which Standard Do I Use?

The transition from analog to digital technology is providing opportunities for broadcasters to offer new services, and competition is fierce between OEMs to produce cost-effective systems that are attractive to consumers. As with many technology shifts, this introduces many new proposed standards as companies vie for market leadership. It's possible that the first company to market becomes a de facto standard regardless of the efforts of standards bodies to ensure interoperability and fair competition. Even when standards bodies successfully produce internationally recognized specifications, there are often many versions of a standard that can be adhered to as they try to address many member companies' needs. Add to this the inevitable revisions to standards during development, and it is easy to see why the flexibility of a fully reprogrammable solution is so compelling.

For example, your return on investment would be much greater if you were able to reprogram your system so that it complies with the latest revision of an emerging forward error correction algorithm. Replacing an aging encryption scheme such as DES with a new, more robust version (AES) is another example.

Table 1 shows a summary of broadcast formats defined by the Advanced Television Standards Committee, and is referred to in the broadcast industry as "Table 3" (from the ATSC A53 specification). There are 36 options that equipment manufacturers need to support in this table alone. There are also regional variations to broadcast standards, with DVB, ISDB, and the proposed DMB used in different parts of the world. Although ASSPs (Application Specific Standard Products) are available, it frequently means that different chips are required for each format.

An FPGA solution, easily supporting data rates exceeding those required by HDTV, would enable all the formats to be supportdramatically. For example, an HDTV display of 1920 x 1080 resolution, 24-bit pixels, and 30 progressive frames per second, requires a total uncompressed bandwidth of around 1.5 Gbps. Even in areas where high-definition images aren't actually broadcast, HD pictures are still used in all post production stages .

The latest low cost programmable logic devices (the Spartan series) now have multiple I/Os with LVDS (low voltage differential signaling) that support these sorts of data rates. Therefore, even uncompressed video data can be brought on- and off-chip and processed in real time. Performing real-time video processing, even at HDTV rates, allows you to reduce external memory requirements.

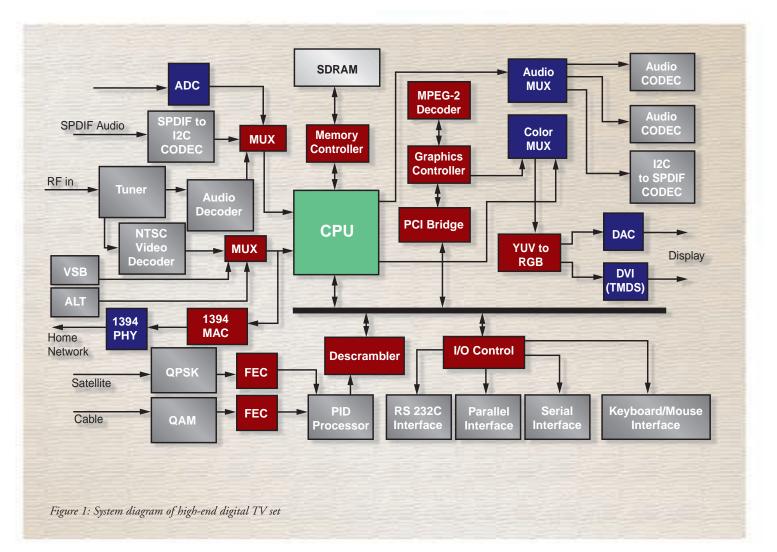

Multiple frame stores and data buffers are often used in current digital TV systems because the video signal processor portion of the design becomes a bottleneck. Using the parallel signal processing capabilities of FPGAs means that smaller, or even single, frame stores can be used, and data buffers can be eliminated. The limitations of standard DSPs for real-time image processing has led to the development of specially designed devices. Although performance is integrated, allowing it to receive digital broadcasts. FPGAs can have many areas of responsibility within digital TV sets, as shown in Figure 1. Interfacing between standard chipsets, as "glue logic," has always been a strong application of FPGAs, but many more image processing tasks (such as color space conversion) and support for network interfaces (such as IEEE 1394) are now possible in low cost programmable devices.

One driver of the trend to offload imageprocessing tasks to FPGAs is the result of the industry-coined phrase "digital convergence." This arises from the need to send high bandwidth video data over new and extremely difficult transmission channels, such as wireless networks, while still maintaining an acceptable quality-of-service (QoS). This has lead to wide ranging research in how to improve error-correction, compression and image processing technology, much of it based around implementation in an FPGA.

## **Product Differentiation**

By using FPGAs, it is possible for you to differentiate your standard-compliant systems from your competitor's products. With the MPEG-2 compression scheme,

| Definition    | Lines/Frame | Pixels/Line | Aspect Ratios | Frame Rates                                         |

|---------------|-------------|-------------|---------------|-----------------------------------------------------|

| High (HD)     | 1080        | 1920        | 16:9          | 23.976p, 24p, 29.97p, 29.97i, 30p, 30i              |

| High (HD)     | 720         | 1280        | 16:9          | 23.976p, 24p, 29.97p, 30p, 59.94p, 60p              |

| Standard (SD) | 480         | 704         | 4:3, 16:9     | 23.976p, 24p, 29.97p, 29.97i, 30p, 30i, 59.94p, 60p |

| Standard (SD) | 480         | 640         | 16:9          | 23.976p, 24p, 29.97p, 29.97i, 30p, 30i, 59.94p, 60p |

for example, it's possible to offload the IDCT (inverse discrete cosine transform) portion of the algorithm from an MPEG processor, to an FPGA, to increase the bandwidth. IDCT (and DCT

Table 1 - ATSC broadcast formats

ed with one device that is reprogrammed depending on the equipment or operational mode it is used in. Such flexibility in a standard, off-the-shelf component reduces your bill of materials and removes any risk of supply problems from an ASSP provider.

### **Pixels and Performance**

With the advent of high-definition broadcasts in many parts of the world, video signal processing requirements have increased greatly improved, these devices have often proved to be too inflexible in all but a narrow range of applications and can still suffer from performance bottlenecks.

### **FPGAs in Consumer Digital TVs**

FPGAs have historically only been found in expensive professional broadcast systems. However, due to low costs, Spartan series FPGAs can be used in high volume consumer products such as digital TVs where set-top box functionality is fully at the encoder) can be implemented extremely efficiently using FPGAs, and optimized IP cores are readily available to include in MPEG based designs.

By integrating proprietary techniques for other image processing functions alongside defined blocks such as DCT, it's possible to produce a low cost, single chip solution that increases processing bandwidth and gives higher quality images than your competitor. By avoiding systems that rely just on standard ASSP solutions, you no longer need to be perceived as providing just another product in a number of similarly specified products in the market. Plus, with FPGAs you can easily modify your design at any time to meet new standards or fix bugs – even after your product is in your customers' hands.

## Time to Market and Time in Market

As well as enhancing DTV systems and increasing processing performance, FPGAs also get your products to market quicker and keep them generating more revenue once they are in the field. Xilinx FPGAs are based on SRAM technology, which allows you to easily reprogram the device during the development phase. This allows simple debugging of your system, but also enables last minute changes to be made to the product if needed. Because FPGAs are reprogrammable, there's no waiting for development of a new ASSP chipset to support the latest revision, or a costly and time consuming ASIC re-spin if chip development is done in-house. New ways of programming devices in the field are giving the added benefit of being able to transmit hardware updates via the Internet or some other communications channel. For example, Xilinx IRL<sup>TM</sup> (Internet Reconfigurable Logic) technology allows you to automatically reconfigure your product, remotely, at any time. The power of this feature is highlighted in situations where first-to-market is key, such as in consumer set-top boxes. It means that boxes can be shipped to customers without necessarily having a complete design features can be added later.

### Conclusion

FPGAs provide both professional and consumer digital broadcast OEMs with real-time image processing capabilities that address the system requirements of new and emerging video applications. Compared to other technologies, FPGAs offer an unrivalled flexibility that enables you to get your products to market quickly. Remote field upgradeability means that systems can be shipped now and features, upgrades, or design fixes added later.

FPGAs also have significant performance advantages over conventional digital signal processors and have the added benefit of allowing you to differentiate your products from the many solutions on the market. Programmable logic is the ideal balance between the flexibility of DSPs and the performance of ASSPs for digital TV development.  $\Sigma$