# Using In-System Programming in Boundary Scan Systems

# Summary

This application note discusses basic design considerations for in-system programming (ISP) of multiple XC9500<sup>™</sup> devices in a Boundary Scan chain and shows how to design systems that contain multiple XC9500 devices as well as other IEEE 1149.1-compatible devices.

#### Notes:

- 1. The fundamental information herein also applies to XC9500XL/XC9500XV, XC10V00, CoolRunner™/CoolRunner-II, Spartan™-II/Spartan-IIE, and Virtex™ platform FPGA families.

- 2. The data sheets of each family should be consulted for proper timing and voltage specifications.

# Introduction

The XC9500 family performs both in-system programming and IEEE 1149.1 Boundary Scan (JTAG) testing via a single 4-wire Test Access Port (TAP). This simplifies system designs and allows standard Automatic Test Equipment (ATE) to perform both functions. Xilinx also provides the software that programs and tests XC9500 devices.

# XC9500 TAP Characteristics

The AC and DC characteristics of the XC9500 TAP are described below.

#### **TAP Timing**

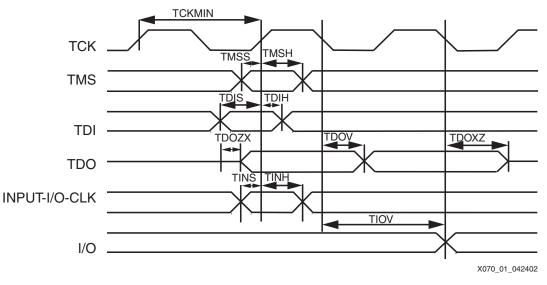

Figure 1 shows the timing relationships of the TAP signals. These TAP timing characteristics are identical for both Boundary Scan and ISP operations. The timing for the INPUT-I/O-CLK and I/O signals is relevant to boundary scan operations (such as EXTEST) that activate or strobe the system pins.

© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

#### **TAP AC Parameters**

Table 1 shows the timing parameters for the TAP waveforms shown in Figure 1.

| Symbol | Parameter                 | Min | Max |

|--------|---------------------------|-----|-----|

| TCKMIN | TCK Minimum Clock Period  | 100 |     |

| TMSS   | TMS Setup Time            | 10  |     |

| TMSH   | TMS Hold Time             | 10  |     |

| TDIS   | TDI Setup Time            | 15  |     |

| TDIH   | TDI Hold Time             | 25  |     |

| TDOZX  | TDO Float to Valid Delay  |     | 35  |

| TDOXZ  | TDI Valid to Float Delay  |     | 35  |

| TDOV   | TDO Valid Delay           |     | 35  |

| TINS   | I/O Setup Time            | 15  |     |

| TINH   | I/O Hold Time             | 30  |     |

| TIOV   | EXTEST Output Valid Delay |     | 55  |

Table 1: XC9500 Test Access Port Timing Parameters (ns)

#### **Terminating TAP Pins**

The XC9500 TDI and TMS pins have internal  $15-k\Omega$  pull-up resistors required by the IEEE 1149.1 standard. Because these pins are internally terminated, no further termination is required on the TAP connections.

#### **Capacitive Decoupling**

Decouple the Vcc input with a 0.1  $\mu$ F capacitor connected to the nearest ground plane (low inductance surface mount capacitors are recommended). Decouple the printed circuit board power inputs with 0.1  $\mu$ F ceramic and 100  $\mu$ F electrolytic capacitors. This helps to provide a stable, noise-free power supply to the ISP parts.

#### **Free Running Oscillators**

Boundary Scan operations often involve the transmission of long streams of data through long and complex paths that traverse the entire system. Often, the presence of active clocks and free running oscillators will couple noise onto the Boundary Scan chain TAP signals. To increase the reliability of Boundary Scan and ISP operations, equip your system with a clock and oscillator disable. The disable should be activated for all test and program operations when using the download cable, ATE, or third party systems.

#### **Calculating Maximal Chain Lengths**

The XC9500 TAP pins have approximately 5 pF of signal loading. Because each TDI input is driven by only one TDO output (or equivalent single drive), there are no signal limitations related to those connections beyond those of standard board interconnect design rules.

The maximum TDO frequency will be 1/2 of the maximum TCK frequency. Because TCK and TMS are parallel driven signals, the maximum number of parts in a single Boundary Scan chain is determined by the ability of the TCK and TMS drivers to deliver the signals at the appropriate frequencies to the parts in the Boundary Scan chain. Standard board-layout design rules also apply here.

If the Boundary Scan chain includes more than six devices, buffered distribution of TMS and TCK are recommended.

#### Part Enable Ordering

The ISPEX instruction allows the flexibility to enable parts in an arbitrary order. In some systems, the order in which parts are enabled is critical. For instance, if a slave device awakens before its controller, it may enter an error condition from which it cannot exit.

The iMPACT software enables each part immediately after programming. In concurrent mode, the parts are enabled simultaneously.

# Creating Boundary Scan Chains

There are a number of possibilities for creating boundary scan chains, several of which are discussed in the following sections

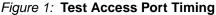

#### **Single Port Serial Chain**

The most simple and widely-used Boundary Scan configuration is the single port serial chain shown in Figure 2, and only this type of configuration is supported by the iMPACT software. In this configuration, four pins are allocated in the system to facilitate connection of the TCK (clock), TMS (mode), TDI (Test Data Input), and TDO (Test Data Output) signals.

All devices in the chain share the TCK and TMS signals. The system TDI signal is connected to the TDI input of the first device in the Boundary Scan chain. The TDO signal from that first device is connected to the TDI input of the second device in the chain and so on. The last device in the chain has its TDO output connected to the system TDO pin.

Other more complex chain variations are discussed later in this application note. Software supplied by third-party Boundary Scan tool vendors supports these complex chain configurations.

Figure 2: Single-Port Serial Boundary Scan Chain

#### **Star Configuration**

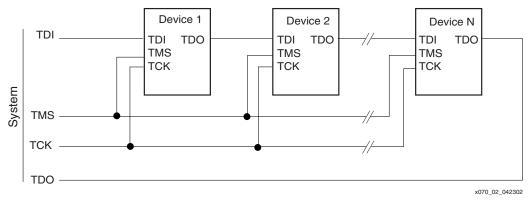

The single port serial chain, shown in Figure 3, configuration has a significant limitation due to the possibility that a defect in the backplane wiring or the removal of a board from the system will break the chain. This would make ISP and system testing impossible. In order to overcome this limitation and make the 1149.1 standard practical for very large systems, the standard allows the connection of Boundary Scan chains in star configuration in which the four pins of the TAP are multiplexed. The costs of this approach are the additional overhead required to switch between scan paths, and the reduced TCK frequency due to TMS routing delays.

Figure 3: Star Configuration

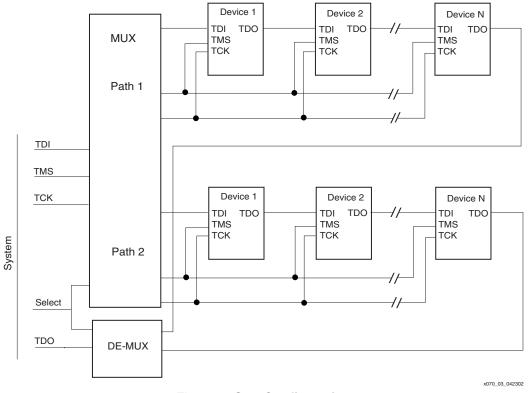

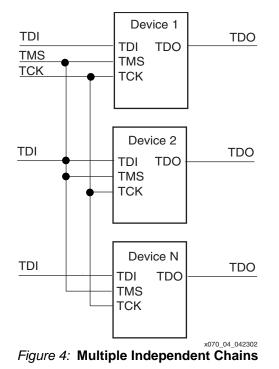

#### **Multiple Independent Paths**

In the topology shown in Figure 4, the TDI and TDO paths are independent allowing data to be streamed into and out of the portions of the system independently.

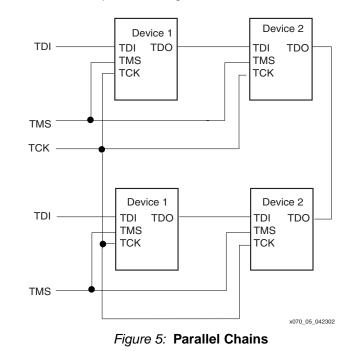

#### **Parallel Chains**

In the topology shown in Figure 5, TDI and TMS inputs are independent but the TDO is shared. This means that although data can be streamed into portions of the system independently, data being streamed out is time multiplexed through TMS control.

# \_\_\_\_\_

# In-System Programming

#### **Using the Xilinx Download Cables**

The iMPACT software can be used with any of the Xilinx download cables.

Windows PC-compatible systems can use the Xilinx high speed Parallel Cable IV. The cable pod includes port protection and drive circuitry. This cable operates TCK at a frequency of up to 5 MHz.

Sun and HP workstations (as well as Windows PC-compatible systems) can use the Xilinx MultiLINX cable.

#### **Concurrent Program and Erase Modes**

One operating mode of the iMPACT software performs concurrent erasing and programming. The advantage of this approach is speed; the overall programming time is dictated by the slowest part in the Boundary Scan chain. Also, the total number of vectors required is optimized. The disadvantage of this approach is that the system must supply a peak operating current equal to that required by all parts being programmed or erased concurrently. For more information on how to use this feature in iMPACT, please see the Xilinx *iMPACT User's Guide*.

**Note**: although XC9500 parts can be programmed concurrently, the current iMPACT software does not generate an SVF file that supports this operation. The current iMPACT generates an SVF file that bypasses all parts except the one being programmed.

#### **ISP Mode I/O Behavior**

The functional pins of the device transition to a high-impedance state when ISP mode is entered using the ISPEN instruction. At the completion of an ISP programming or erase operation, the ISPEX instruction is executed. When leaving ISPEX mode (by shifting in an new Boundary Scan instruction other than ISPEN), the device initializes to its programmed state; the functional pins take on their selected operations (input, output, or bidirectional) and the device registers take on their pre-selected initial values.

# System-Level Design Issues

The normal operating mode of a system or a device in the system is known as mission mode which is different from test mode. When operating a device in Boundary Scan test mode (such as when using either INTEST or EXTEST) as well as when performing ISP operations, the device is effectively disconnected from the overall system. When the operation is completed, the device is re-connected to the system. This can sometimes result in unpredictable system behavior. Additional discussion regarding this problem can be found in "The Boundary Scan Handbook" by Ken Parker. Fortunately, the XC9500 family supplies two proprietary Boundary Scan instructions that serve to alleviate this problem.

## **XC9500 Mission Mode Exit and Re-Entry Techniques**

The XC9500 devices support two Boundary Scan instructions that can be used to help alleviate the problems associated with exiting and re-entering mission mode. The instructions are ISPEN (ISP enable) and ISPEX (ISP exit).

- **ISPEN** The ISPEN instruction is used at the beginning of every block of ISP operations that will attempt to access for alteration or read the device internal program memory (such as program, erase, verify, etc.). When the device is in ISPEN mode, the device I/O pins immediately enter a state in which they are floating with a weak pull-up resistor enabled on each pin. The device pins therefore neither drive nor sense external signal levels.

- **ISPEX** The ISPEX instruction is used to conclude every block of ISP operations that have either been read from or written to the device internal program memory. As long as the ISPEX instruction remains in the instruction register the functional pins remain in their lightly pulled-up high impedance state. Once the ISPEX instruction is replaced with any other Boundary Scan instruction (except ISPEN), the device returns to its initial power state with the pins configured to their programmed states (input, output, or bidirectional) and with the device flip-flops taking on their initial states.

The ISPEX operation takes approximately 100 microseconds to complete. If the ISPEX instruction is held in the instruction register for longer than 100 microseconds, the ISPEX operation will not take effect until the ISPEX instruction is displaced from the instruction register.

In order to ensure safe operation, all INTEST, EXTEST, and ISP operations involving the XC9500 parts should be bracketed by ISPEN and ISPEX instructions.

The designer must also be careful to select an initial condition that is "system-safe" so that when the ISPEX instruction is released the XC9500 part in question will safely resume operation with the rest of the system.

#### **Basic Boundary Scan Design Guidelines**

The following guidelines will help ensure a successful design.

- Make certain that all parts in the Boundary Scan chain have 1149.1 compatible test access ports.

- Use simple buffering for TCK/TMS signals, to simplify test considerations for the Boundary Scan TAP.

- Do not invert TCK or TMS pathways, to guarantee complete test software compatibility.

- Group similar device families, and have a single level converter interface between them, for TCK, TMS, TDI, TDO, and system pins.

- Check that the mission logic is safe from any possible errors that might arise while the Boundary Scan data is being shifted through the Boundary Scan chain. For example, pay close attention to bus enable or chip select signals that might be enabled simultaneously, causing unexpected bus contention.

- Provide the capability for the ATE to disable conventional (non Boundary Scan) IC's whose run-time node values might introduce conflicts with Boundary Scan logic values during test operations.

- Verify that the entire system is held in a benign state during Boundary Scan test operations.

- Verify that the set-up and hold times of TDI and TMS with respect to TCK are met by the system.

#### **Debugging Boundary Scan Systems**

The following guidelines and helpful information will help isolate potential problems.

- When traversing the IR states, the CAPTURE-IR value specified in the BSDL file is always shifted out on TDO at SHIFT-IR. This fact can be used to test Boundary Scan chain continuity.

- After exit from Test-Logic-Reset, if the system transitions directly to Shift-DR, the values shifted out on TDO must be either the IDCODE (if implemented) or the BYPASS register contents. If all logic 0s are shifted in at TDI, then the first incidence of a logic 1 on TDO represents the first bit of an IDCODE. This fact can be used for blind interrogation of the Boundary Scan chain and for further Boundary Scan chain continuity checks.

- When entering ISP mode via the ISPEN instruction, all XC9500 function pins float to a weakly pulled-up high impedance state. The pins can easily be tested for this behavior.

- When ISPEX is shifted out of the instruction register, the XC9500 devices should take on their programmed values with the functional pins acting immediately as inputs or outputs, as programmed. The pins can easily be tested for this behavior.

- TDO assumes its defined value at the falling edge of TCK.

- When not in SHIFT-IR or SHIFT-DR, TDO exhibits high impedance.

- The last valid TDI bit clocks into the TAP with TMS high.

- In BYPASS mode, TDO equals the applied TDI data one TCK pulse earlier.

## Conclusion

When designing ISP systems, common-sense rules related to electronic system design and board layout should be adhered to. In order to benefit from the synergies associated with the integration of test and programming operations, the designer must consciously design with the entire system life cycle in mind.

# References

- IEEE 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- Colin Maunder and Rod Tulloss, The Test Access Port and Boundary Scan Architecture, ISBN: 0-8186-9070-4.

- Kenneth P. Parker, The Boundary Scan Handbook, ISBN: 0-7923-9270-1.

- Harry Bleeker et al., Boundary Scan Test A Practical Approach, ISBN: 0-792-9296-5.

- Hideo Fujiwara, Logic Testing and Design for Testability, ISBN: 0-262-06096-5.

- M. Montrose, Printed Circuit Board Design Techniques, ISBN: 0780311310.

# Revision History

The following table shows the revision history for this document.

| Date     | Version | Revision                |

|----------|---------|-------------------------|

| 07/01/97 | 1.0     | Xilinx initial release. |

| 05/22/02 | 2.0     | Revised release.        |