# Virtex-II Pro 3.3V PCI Reference Design

## **Summary**

This application note describes the Virtex-II Pro™ 3.3V PCI solution.

Virtex-II Pro Basic Requirements for PCI Designs

The 3.3V regulator reference design associated with this application note has been verified to work with Virtex-II Pro 3.3V I/O pins using the PCI I/O standard. The <u>Virtex-II Pro User Guide</u> has further details on Virtex-II Pro devices and the PCI standard.

#### **Overview**

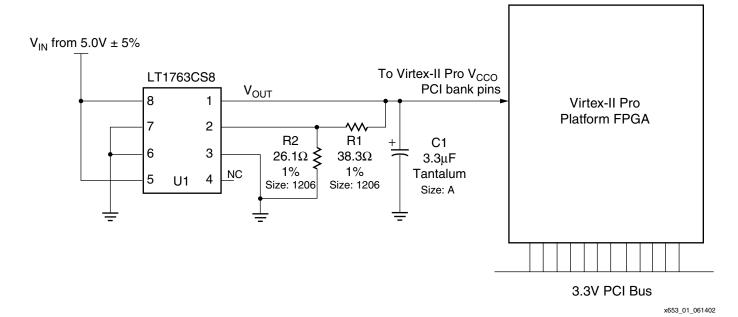

The reference design provides a number of features including full electrical compliance to the PCI standard for Virtex-II Pro designs. This low cost solution can be accomplished using minimal PC board space. This proven easy-to-use design is shown in Figure 1.

Figure 1: Reference Design Schematic

### **PCI Compliance**

The PCI bus specification for minimum input voltage is -0.5V. Although the absolute maximum specification for Virtex-II Pro input  $(V_{IN})$  is -0.3V when  $V_{CCO}$  is at 3.45V, this lower limit is changed from -0.3V to -0.5V when  $V_{CCO}$  is lowered to 3.0V.

The signal level below -0.5V is clamped by the intrinsic diode in the I/O. The PCI compliance specification requires the clamp diode to withstand a -3.5V input voltage for more than 11 ns in an undershoot test. In this scenario, the voltage across the clamp diode could be as high as -0.9V. However, the diode passes this undershoot test without concern.

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

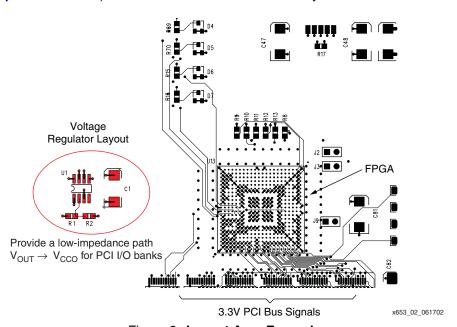

#### **Regulator Implementation**

The highlighted elements in Figure 2 (U1, R1, R2, and C1) comprise the regulator implementation on a typical FPGA PCB layout. This configuration supplies a V<sub>OUT</sub> regulated at 3.0V for the 3.3V PCI V<sub>CCO</sub> banks. The LT1763CS8 covers an industrial operating temperature range, since the regulator has a junction temperature range of –40°C to +125°C. The reference design provides a fully compliant PCI electrical interface for Virtex-II Pro devices. Depending on PCI performance requirements, use the PCI33 or PCI66 I/O standard for the I/Os connecting to the PCI bus. The user is cautioned to not substitute alternative solutions. Alternative designs should be analyzed at Xilinx by the Hotline (by opening a web case at <a href="https://www.support.xilinx.com">www.support.xilinx.com</a>) or with documented concurrence by a local Xilinx FAE.

Figure 2: Layout Area Example

#### **Linear Technology - LT1763CS8 Devices**

Linear Technology makes the low noise, low dropout, micropower LT1763 series of regulators. These devices are capable of supplying 500 mA of output current with a dropout voltage of 300mV. Internal protection circuitry includes reverse battery protection, current limiting, thermal limiting, and reverse current protection. The LT1763CS8 regulator used for this application is an adjustable device with a 1.22V reference voltage. Refer to the following URL for more details. <a href="http://www.linear.com/prod/datasheet.html?datasheet=520">http://www.linear.com/prod/datasheet.html?datasheet=520</a>

#### **Solution Cost**

The total cost of the solution shown in Figure 1 is estimated to be less than \$2.00 in 1000 piece quantities. This estimate includes the LT1763CS8 regulator, resistors, and  $3.3\mu$ F capacitor.

# Revision History

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                |

|----------|---------|-----------------------------------------------------------------------------------------|

| 06/17/02 | 1.0     | Initial Xilinx release.                                                                 |

| 02/06/03 | 1.1     | Added PCI Compliance section. Added I/O standard suggestions for connecting to PCI bus. |