DS119 (v1.1) February 14, 2003

# XCR3032XL 32 Macrocell Automotive IQ CPLD

### **Advance Product Specification**

### **Features**

- Guaranteed to meet full electrical specifications over T<sub>A</sub>

= -40°C to +125°C

- Technology: 0.35 μm EEPROM process

- Full Boundary Scan Test (IEEE 1149.1) for flexible in-system device and system testing

- Fast programming times in production saves time and money

- Increases system reliability through reduced device handling

- High-speed pin-to-pin delays of 10 ns (100 MHz)

- Slew rate control per output to reduce EMI

- 100% routable which enables all device resources to be utilized

- Refer to XPLA3 Family data sheet (DS012) for architecture description

- Refer to XCR3032XL data sheet (DS023) for pin descriptions

### **Description**

The CoolRunner™ XCR3032XL-Q CPLD Automotive IQ product is targeted for low power systems that include portable, handheld, automotive, and power sensitive applications. This device includes Fast Zero Power™ (FZP) design technology that combines low power and high speed. With this design technique, the XCR3032XL-Q delivers low standby current without the need for "turbo bits" or other power down schemes. By replacing conventional sense amplifier methods for implementing product terms (a technique that has been used in PLDs since the bipolar era) with a cascaded chain of pure CMOS gates, the dynamic power is also substantially lower than any other CPLD. CoolRunner devices are the only TotalCMOS PLDs, as they use both a CMOS process technology and the patented full CMOS FZP design technique.

The CoolRunner XCR3032XL-Q employs a full PLA structure for logic allocation within a functon block. The PLA provides maximum flexibility and logic density, with superior pin locking capability, while maintaining deterministic timing.

The CoolRunner XCR3032XL-Q is supported by Web-PACK™ and WebFITTER™ from Xilinx and industry standard CAE tools (Cadence/OrCAD, Exemplar Logic, Mentor, Synopsys, ViewLogic, and Synplicity), using text (ABEL, VHDL, Verilog) and schematic capture design entry. Design verification uses industry standard simulators for functional and timing simulation. Development is supported on personal computer, Sparc, and HP platforms.

The XCR3032XL-Q features also include industry-standard, IEEE 1149.1, JTAG interface through which boundary-scan testing and In-System Programming (ISP) and reprogramming of the device can occur. This device is electrically reprogrammable using industry standard device programmers.

Table 1: CoolRunner XCR3032XL-Q

|                           | XCR3032XL-Q |

|---------------------------|-------------|

| Macrocells                | 32          |

| Usable Gates              | 750         |

| Registers                 | 32          |

| F <sub>SYSTEM</sub> (MHz) | 95          |

| User I/O (44-pin VQFP)    | 36          |

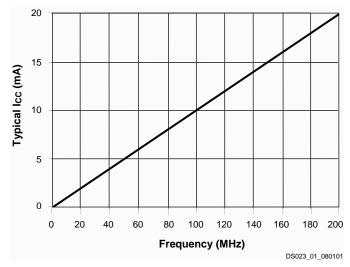

Figure 1: I<sub>CC</sub> vs. Frequency at V<sub>CC</sub> = 3.3V, 25°C

Table 2:  $I_{CC}$  vs. Frequency ( $V_{CC} = 3.3V, 25^{\circ}C$ )

| Frequency (MHz)              | 0    | 1    | 5    | 10   | 20   | 50  | 100   | 200  |

|------------------------------|------|------|------|------|------|-----|-------|------|

| Typical I <sub>CC</sub> (mA) | 0.02 | 0.13 | 0.54 | 1.06 | 2.09 | 5.2 | 10.26 | 20.3 |

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

## **Absolute Maximum Ratings**(1)

| Symbol           | Parameter                                     | Min. | Max.               | Unit |

|------------------|-----------------------------------------------|------|--------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>(2)</sup> relative to GND | -0.5 | 4.0                | V    |

| VI               | Input voltage <sup>(3)</sup> relative to GND  | -0.5 | 5.5 <sup>(4)</sup> | V    |

| I <sub>OUT</sub> | Output current, per pin                       | -100 | 100                | mA   |

| T <sub>J</sub>   | Maximum junction temperature                  | -40  | 150                | °C   |

| T <sub>STR</sub> | Storage temperature                           | -65  | 150                | °C   |

### Notes:

- Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional

operation at these or any other condition above those indicated in the operational and programming specification is not implied.

- 2. The chip supply voltage must rise monotonically.

- 3. Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, the device pins may undershoot to -2.0V or overshoot to 7.0V, provided this over- or undershoot lasts less than 10 ns and with the forcing current being limited to 200 mA.

- 4. External I/O voltage may not exceed V<sub>CC</sub> by 4.0V.

### **Recommended Operating Conditions**

| Symbol          | Parameter                | Min. | Max.            | Unit |

|-----------------|--------------------------|------|-----------------|------|

| T <sub>A</sub>  | Ambient temperature      | -40  | +125            | °C   |

| V <sub>CC</sub> | Supply voltage           | 3.0  | 3.6             | V    |

| V <sub>IL</sub> | Low-level input voltage  | 0    | 0.8             | V    |

| V <sub>IH</sub> | High-level input voltage | 2.0  | 5.5             | V    |

| V <sub>O</sub>  | Output voltage           | 0    | V <sub>CC</sub> | V    |

| T <sub>R</sub>  | Input rise time          | -    | 20              | ns   |

| T <sub>F</sub>  | Input fall time          | -    | 20              | ns   |

## **Quality and Reliability Characteristics**

| Symbol          | Parameter                                                | Min    | Max | Units  |

|-----------------|----------------------------------------------------------|--------|-----|--------|

| T <sub>DR</sub> | Data retention                                           | 20     | -   | Years  |

| N <sub>PE</sub> | Program/erase cycles (Endurance) @ T <sub>A</sub> = 70°C | 10,000 | -   | Cycles |

## **DC Electrical Characteristics Over Recommended Operating Conditions**

| Symbol                         | Parameter                              | Test Conditions              |                                   | Min.                              | Max. | Unit |

|--------------------------------|----------------------------------------|------------------------------|-----------------------------------|-----------------------------------|------|------|

| V <sub>OH</sub> <sup>(1)</sup> | Output High voltage                    | I <sub>OH</sub> = -500 μA    |                                   | 90%V <sub>CC</sub> <sup>(2)</sup> | -    | V    |

|                                |                                        | $V_{CC} = 3.0V, I_{OH} = -8$ | mA                                | 2.4                               | -    | V    |

| V <sub>OL</sub>                | Output Low voltage                     |                              | I <sub>OL</sub> = 8 mA            | -                                 | 0.4  | V    |

| I <sub>IL</sub> (3)            | Input leakage current                  |                              | $V_{IN} = GND \text{ or } V_{CC}$ | -10                               | 10   | μΑ   |

| I <sub>IH</sub> (3)            | I/O High-Z leakage current             |                              | $V_{IN} = GND \text{ or } V_{CC}$ | -10                               | 10   | μΑ   |

| I <sub>CCSB</sub>              | Standby current                        |                              | V <sub>CC</sub> = 3.6V            | -                                 | 1.0  | mA   |

| I <sub>CC</sub>                | Dynamic current <sup>(4)</sup>         |                              | f = 1 MHz                         | -                                 | 2.0  | mA   |

|                                |                                        |                              | f = 50 MHz                        | -                                 | 10   | mA   |

| C <sub>IN</sub>                | Input pin capacitance <sup>(5)</sup>   |                              | f = 1 MHz                         | -                                 | 8    | pF   |

| C <sub>CLK</sub>               | Clock input capacitance <sup>(5)</sup> |                              | f = 1 MHz                         | -                                 | 12   | pF   |

| C <sub>I/O</sub>               | I/O pin capacitance <sup>(5)</sup>     |                              | f = 1 MHz                         | -                                 | 10   | pF   |

#### Notes:

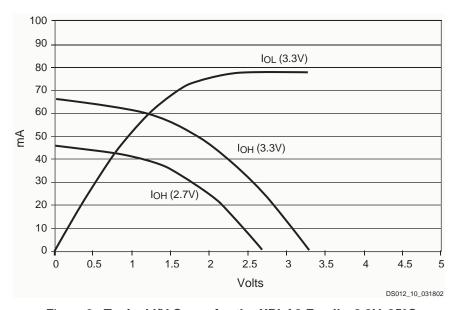

- 1. See Figure 2 for output drive characteristics of the XPLA3 family.

- 2. This parameter guaranteed by design and characterization, not by testing.

- 3. Typical leakage current is less than 1  $\mu$ A.

- 4. This parameter measured with a 16-bit, resetable up/down counter loaded into every function block, with all outputs disabled and unloaded. Inputs are tied to V<sub>CC</sub> or ground. This parameter guaranteed by design and characterization, not testing.

- 5. Typical values, not tested.

Figure 2: Typical I/V Curve for the XPLA3 Family, 3.3V, 25°C

## AC Electrical Characteristics Over Recommended Operating Conditions<sup>(1)</sup>

|                                    |                                                |      | -10  |      |  |

|------------------------------------|------------------------------------------------|------|------|------|--|

| Symbol                             | Parameter                                      | Min. | Max. | Unit |  |

| T <sub>PD1</sub>                   | Propagation delay time (single p-term)         | -    | 9.1  | ns   |  |

| T <sub>PD2</sub>                   | Propagation delay time (OR array)              | -    | 10.0 | ns   |  |

| T <sub>CO</sub>                    | Clock to output (global synchronous pin clock) | -    | 6.5  | ns   |  |

| T <sub>SUF</sub>                   | Setup time (fast input register)               | 3.0  | -    | ns   |  |

| T <sub>SU1</sub> <sup>(2)</sup>    | Setup time (single p-term)                     | 5.4  | -    | ns   |  |

| T <sub>SU2</sub>                   | Setup time (OR array)                          | 6.3  | -    | ns   |  |

| T <sub>H</sub> <sup>(2)</sup>      | Hold time                                      | 0    | -    | ns   |  |

| T <sub>WLH</sub> <sup>(2)</sup>    | Global Clock pulse width (High or Low)         | 4.0  | -    | ns   |  |

| T <sub>PLH</sub> <sup>(2)</sup>    | P-term clock pulse width                       | 6.0  | -    | ns   |  |

| T <sub>R</sub> <sup>(2)</sup>      | Input rise time                                | -    | 20   | ns   |  |

| T <sub>L</sub> <sup>(2)</sup>      | Input fall time                                | -    | 20   | ns   |  |

| f <sub>SYSTEM</sub> <sup>(2)</sup> | Maximum system frequency                       | -    | 95   | MHz  |  |

| T <sub>CONFIG</sub> <sup>(2)</sup> | Configuration time <sup>(3)</sup>              | -    | 60   | μs   |  |

| T <sub>INIT</sub>                  | ISP initialization time                        | -    | 60   | μs   |  |

| T <sub>POE</sub> <sup>(2)</sup>    | P-term OE to output enabled                    |      | 11.2 | ns   |  |

| T <sub>POD</sub> <sup>(2)</sup>    | P-term OE to output disabled <sup>(4)</sup>    | -    | 11.2 | ns   |  |

| T <sub>PCO</sub> <sup>(2)</sup>    | P-term clock to output                         | -    | 10.7 | ns   |  |

| T <sub>PAO</sub> <sup>(2)</sup>    | P-term set/reset to output valid - 11.2        |      |      |      |  |

#### Notes:

- 1. Specifications measured with one output switching.

- 2. These parameters guaranteed by design and/or characterization, not testing.

- 3. Typical current draw during configuration is 3 mA at 3.6V.

- 4. Output  $C_L = 5 pF$ .

## Internal Timing Parameters<sup>(1)</sup>

|                    |                                                 | -           | 10   |              |

|--------------------|-------------------------------------------------|-------------|------|--------------|

| Symbol             | Parameter                                       | Min.        | Max. | Unit         |

| Buffer De          | ays                                             |             |      | <del>!</del> |

| T <sub>IN</sub>    | Input buffer delay                              | -           | 2.2  | ns           |

| T <sub>FIN</sub>   | Fast Input buffer delay                         | -           | 3.1  | ns           |

| T <sub>GCK</sub>   | Global Clock buffer delay                       | -           | 1.3  | ns           |

| T <sub>OUT</sub>   | Output buffer delay                             | -           | 3.6  | ns           |

| T <sub>EN</sub>    | Output buffer enable/disable delay              | -           | 5.7  | ns           |

| Internal R         | egister, Product Term, and Combinatorial Delays | <del></del> |      | •            |

| T <sub>LDI</sub>   | Latch transparent delay                         | -           | 2.0  | ns           |

| T <sub>SUI</sub>   | Register setup time                             | 1.2         | -    | ns           |

| T <sub>HI</sub>    | Register hold time                              | 0.7         | -    | ns           |

| T <sub>ECSU</sub>  | Register clock enable setup time                | 3.0         | -    | ns           |

| T <sub>ECHO</sub>  | Register clock enable hold time                 | 5.5         | -    | ns           |

| T <sub>COI</sub>   | Register clock to output delay                  | -           | 1.6  | ns           |

| T <sub>AOI</sub>   | Register async. S/R to output delay             | -           | 2.1  | ns           |

| T <sub>RAI</sub>   | Register async. recovery                        | -           | 6.0  | ns           |

| T <sub>PTCK</sub>  | Product term clock delay                        | -           | 3.3  | ns           |

| T <sub>LOGI1</sub> | Internal logic delay (single p-term)            | -           | 3.3  | ns           |

| T <sub>LOGI2</sub> | Internal logic delay (PLA OR term)              | -           | 4.2  | ns           |

| Feedback           | Delays                                          | ·           |      |              |

| T <sub>F</sub>     | ZIA delay                                       | -           | 2.9  | ns           |

| Time Add           | ers                                             |             |      |              |

| T <sub>LOGI3</sub> | Fold-back NAND delay                            | -           | 3.0  | ns           |

| T <sub>UDA</sub>   | Universal delay                                 | -           | 2.5  | ns           |

| T <sub>SLEW</sub>  | Slew rate limited delay                         | -           | 6.0  | ns           |

### Notes:

<sup>1.</sup> These parameters guaranteed by design and characterization, not testing.

## **Switching Characteristics**

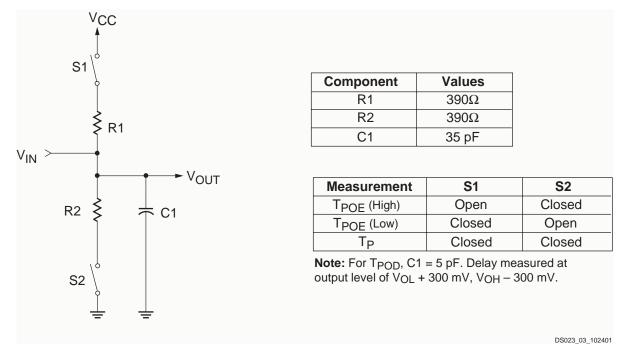

Figure 3: Typical AC Load Circuit

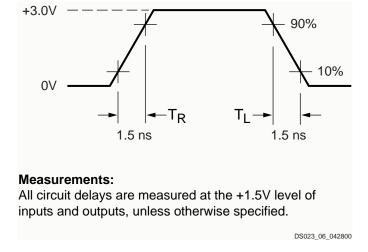

Figure 4: Typical Voltage Waveform

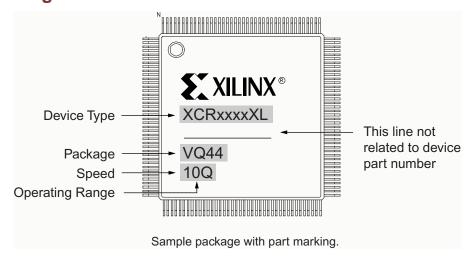

## **Device Part Marking**

## **Ordering Combination Information**

| Device Ordering and Part<br>Marking Number | Speed<br>(pin-to-pin<br>delay) | Pkg.<br>Symbol | No. of<br>Pins | Package Type                    | Operating<br>Range <sup>(1)</sup> |

|--------------------------------------------|--------------------------------|----------------|----------------|---------------------------------|-----------------------------------|

| XCR3032XL-10VQ44Q                          | 10 ns                          | VQ44           | 44             | Very Thin Quad Flat Pack (VQFP) | Q                                 |

### Notes:

1. Q = Automotive:  $T_A = -40^{\circ}$  to  $+125^{\circ}$ C

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                  |

|----------|---------|-------------------------------------------|

| 10/28/02 | 1.0     | Initial Xilinx release.                   |

| 02/14/03 | 1.1     | Deleted architecture and pinout sections. |