# Virtex-II Pro™ System Wake-Up Solutions

UG028 (v1.0) March 8, 2002

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, Selectl/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418;

4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5.831.907; 5.835.402; 5.838.167; 5.838.901; 5.838.954; 5.841.296; 5.841.867; 5.844.422; 5.844.424; 5.844.829; 5.844.844; 5.847.577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2001 Xilinx, Inc. All Rights Reserved.

# Virtex-II Pro<sup>™</sup> System Wake-Up Solutions

UG028 (v1.0) March 8, 2002

The following table shows the revision history for this document.

|          | Version | Revision                |

|----------|---------|-------------------------|

| 03/08/02 | 1.0     | Initial Xilinx release. |

Virtex-II Pro™ System Wake-Up Solutions

# **Contents**

# Managing Hardware and Software Data with Virtex-II Pro Devices 1

| Summary                          | 1 |

|----------------------------------|---|

| Overview                         | 1 |

| System ACE CompactFlash Solution | 3 |

| System ACE MPM/SC Solution       | 4 |

| Xilinx PROMs                     | 5 |

| External Non-Volatile Memory     | 6 |

# Basic and Advanced Virtex-II Pro Wake-Up Solutions 7

| Basic Virtex-II Pro Wake-Up Solution    | . 7 |

|-----------------------------------------|-----|

| Overview                                | . 7 |

| Basic System Architecture               | . 7 |

| Basic Solution Wake-Up Flow             | 8   |

| Basic Software Flow                     | 9   |

| Advanced Virtex-II Pro Wake-Up Solution |     |

| Overview                                | 10  |

| Advanced System Architecture            | 10  |

| Advanced Solution Wake-Up Flow          | 11  |

| Virtex-II Pro JTAG Test Access Port     |     |

| Advanced Software Flow                  | 12  |

# Chapter 1

# Managing Hardware and Software Data with Virtex-II Pro Devices

# Summary

The Virtex-II Pro Platform FPGA solution is a powerful system solution with numerous advanced features, including IBM PowerPC<sup>™</sup> processors and Rocket I/O<sup>™</sup> multi-gigabit transceiver blocks. The advanced features introduce new options that need to be considered when selecting a customized system wake-up solution. The system wake-up is the process necessary to bring the Virtex-II Pro devices to an operational stage for the system application and typically consists of two steps, configuring the FPGA logic and booting up the PowerPC processor for successful system operation.

The Virtex-II Pro PowerPC (PPC) microprocessor can be initialized as part of the system wake-up. This document briefly describes the various options available for system wake-up and highlights the two most efficient solutions for basic and advanced systems.

# **Overview**

The following section gives an overview of the different methods available to configure the Virtex-II Pro device and to allow the PowerPC (PPC) to boot up and access memory for code storage and software execution.

The four system wake-up solutions for Virtex-II Pro Platform FPGAs are:

- 1. System ACE CF CompactFlash-based configuration management

- 2. System ACE MPM Parallel Flash-based Multi-Package Module

- 3. XILINX PROM Serial Programmable Read Only Memory

- 4. External Non-volatile Memory Flash, Read Only Memory, and other equivalent solutions.

Table 1-1 provides the available solutions for the Virtex-II Pro system wake-up.

| Solution                                                                                 | Density                | Mode<br>Support                                                  | Configuration<br>Speed                               | Technology                        | I/O Voltage<br>Tolerance | Feature Support                                                                                                                                                               |

|------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------|------------------------------------------------------|-----------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XC18Vxx<br>PROM                                                                          | Up to<br>4 Mb          | Slave-Serial,<br>SelectMAP                                       | Up to<br>264 Mb/s                                    | Flash                             | Down to 2.5V             | Devices are<br>reprogrammable<br>(IEEE 1149.1 and<br>IEEE 1532)                                                                                                               |

| XC17Vxx<br>PROM                                                                          | Up to<br>16 Mb         | Slave-Serial,<br>SelectMAP<br>(available<br>for 17V08/<br>17V16) | Up to<br>120 Mb/s                                    | EPROM                             | 3.3V                     | One Time<br>Programmable<br>(OTP)                                                                                                                                             |

| System ACE<br>MPM (Multi-<br>Package<br>Module) or<br>System ACE SC<br>(Soft Controller) | 16 Mb<br>to<br>64 Mb   | Slave-Serial,<br>SelectMAP                                       | Select Map-<br>152 Mb/s<br>Slave Serial -<br>66 Mb/s | Parallel Flash-<br>based solution | Down to<br>2.5V          | <ul> <li>Native Flash<br/>Interface</li> <li>Configuration<br/>management –<br/>multiple Design<br/>set support</li> <li>Network<br/>Reconfigurable</li> </ul>                |

| System ACE CF<br>CompactFlash                                                            | 64 Mb<br>up to<br>8 Gb | JTAG<br>(IEEE<br>1149.1, IEEE<br>1532)                           | Up to 30 Mb/s                                        | CompactFlash-<br>based solution   | Down to<br>2.5V          | <ul> <li>MPU Interface<br/>(PPC405<br/>compatible)</li> <li>Configuration<br/>management –<br/>multiple Design<br/>set support</li> <li>Network<br/>reconfigurable</li> </ul> |

#### Notes:

1. The XC2VP2 device which does not contain a CPU can be configured in the same manner as a Virtex-II device with a similar density.

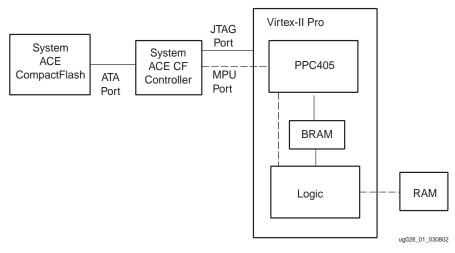

# System ACE CF (CompactFlash) Solution

The System ACE CF is a pre-engineered interface solution between a CompactFlash or one-inch Microdrive disk drive and a Virtex-II Pro FPGA. It features a built-in microprocessor interface and can support the configuration of multiple devices, boards, and bitstreams (multiple designs), as well as processor core initialization and software storage. This drop-in configuration solution delivers a dense, flexible, pre-engineered solution that reduces design time while supporting the complex needs of a microprocessor-based solution. For more information, see: http://www.xilinx.com/isp/systemace/systemacecf.htm

When the System ACE CF solution is used with the Virtex-II Pro Platform FPGA, the wakeup sequence is as follows:

- 1. Configure the Virtex-II Pro FPGA logic from the CompactFlash (CF) via JTAG.

- 2. Transfer boot code from CompactFlash to Block SelectRAM<sup>™</sup> (BRAM) or external RAM (DRAM or SRAM) via JTAG.

- 3. The PPC405 boots up from BRAM or RAM.

- 4. PPC405 can access the CompactFlash memory via the MPU port of the System ACE CF Controller for code storage and software execution. The PPC405 can also transfer software from the CompactFlash to BRAM, RAM, or a combination of both for faster execution.

Figure 1-1: System ACE CF Solution for Virtex-II Pro Wake-Up

# System ACE MPM/SC Solution

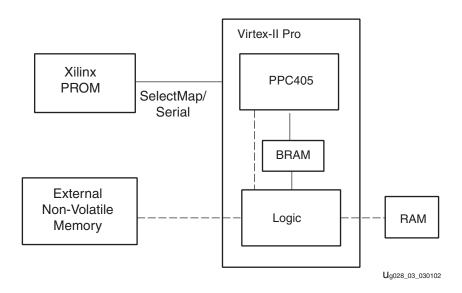

The System ACE MPM is a pre-engineered multi-package module and the System ACE SC is a functionally identical solution provided as a soft controller and not pre-packaged in a single module. Both solutions interface between an on-board industry standard Flash and a Virtex-II Pro FPGA. Both solutions feature a native flash (EPROM) and boundary scan interface and can support the configuration of multiple devices, board, and bitstreams (multiple designs), as well as processor core initialization. These drop-in configuration solutions provide high-performance bitstream delivery (Slave Serial and SelectMAP modes), while reducing design time for supporting the complex needs of a microprocessor-based solution. For more information, see: <a href="http://www.xilinx.com/isp/systemace/systemacempm.htm">http://www.xilinx.com/isp/systemace/systemacempm.htm</a>

When the System ACE MPM is used with a Virtex-II Pro device (Figure 1-2), the wake up sequence is:

- 1. Configure the Virtex-II Pro FPGA logic and transfer boot code from MPM via SelectMap or Serial to BRAM.

- 2. The BRAM boots up the PPC405.

- 3. The PPC405 can access unused portions of ACE MPM via the MPM Flash Interface for code storage and software execution. The PPC405 can transfer software from ACE MPM to BRAM, RAM, or a combination of both for faster execution.

Figure 1-2: Xilinx System ACE MPM/SC Solution for Virtex-II Pro Wake-Up

## Xilinx PROMs

Xilinx has developed a wide variety of configuration PROMs to provide an easy-to-use, high-performance programming solution. PROM products include In-System Programmable (ISP) as well as One-time Programmable (OTP) families in industry leading densities and packages.

When a Xilinx Configuration PROM is used with a Virtex-II Pro device (Figure 1-3), the wake up sequence is as follows:

- 1. Configure the FPGA portion of Virtex-II Pro device and transfer boot code from PROM via SelectMap or Serial to BRAM.

- 2. The BRAM boots up the PPC405.

- 3. The PPC405 can access the external non-volatile memory, like standard Flash, for code storage and software execution. The PPC405 can transfer software from the external non-volatile memory to BRAM, RAM, or a combination of both for faster execution.

Figure 1-3: Xilinx PROM Solution for Virtex-II Pro System Wake-Up

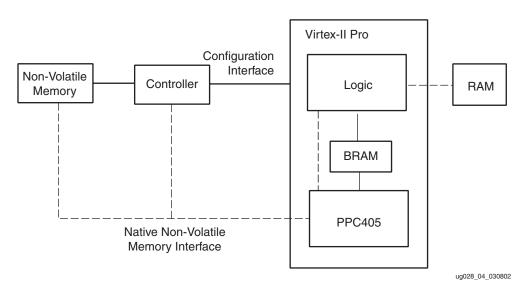

## **External Non-Volatile Memory**

External non-volatile memory can be used to configure a Virtex-II Pro device including Flash-based memory (such as standard Flash, CF cards, SD cards, etc.), as well as and hard disk drives. Using an external non-volatile memory requires a controller to configure the Virtex-II Pro device on wake-up. For the controller design, refer to the following application notes:

- XAPP058 ("Xilinx In-System Programming Using an Embedded Microcontroller") or

- XAPP079 ("Configuring Xilinx FPGAs Using an XC9500 CPLD and Parallel PROM")

The sequence of wake-up for a Virtex-II Pro device using an external non-volatile memory is as follows:

- 1. Configure the FPGA portion of the Virtex-II Pro device and transfer the boot code from external non-volatile memory to either BRAM or RAM.

- 2. Either BRAM or RAM boots up the PPC405.

The PPC405 can access external non-volatile memory, via the non-volatile memory interface, for code storage and software execution. The PPC405 can transfer software from the external non-volatile memory to BRAM, RAM, or a combination of both for faster execution.

Figure 1-4: Non-Volatile Memory Solution for Virtex-II Pro Wake-Up

# Chapter 2

# Basic and Advanced Virtex-II Pro Wake-Up Solutions

# **Basic Virtex-II Pro Wake-Up Solution**

#### **Overview**

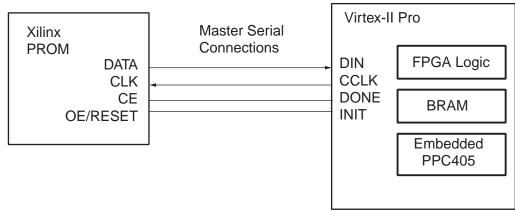

The first method to be described is a well-known setup used with other Xilinx FPGA families. The setup requires very little external hardware and minimal connections. The only external device required for this setup is a Serial PROM storage device. The PROM is used to store the traditional configuration data for the Virtex-II Pro device.

The new level of complexity that must be addressed is the storage location of the Virtex-II Pro PowerPC<sup>™</sup> boot-code. In this basic setup, the Virtex-II Pro FPGA Block SelectRAM (also referred to as BRAM) is utilized for the PPC boot code storage. The BRAM contents are loaded in the configuration data that is stored in the PROM, thereby, eliminating the need for an additional external RAM device to store the PPC contents.

#### **Basic System Architecture**

**Figure 2-1** shows the connections to the Xilinx PROM required for the Master Serial configuration mode. Figure 2-1 also shows a simplified block diagram of the Virtex-II Pro device before configuration. In this setup, both the FPGA logic and BRAM load on configuration from the PROM and the PPC boot-ups from the BRAM.

ug028\_05\_022502

Figure 2-1: Virtex-II Pro Basic System Wake-Up Solution

www.xilinx.com 1-800-255-7778

#### Notes:

1. Other modes can also be used in a similar manner with additional hardware connections. Refer to the appropriate Xilinx PROM data sheet for guidelines and the required VCC/GND pullup/pulldown and optional connections.

This basic setup requires less hardware and external connections, but the trade-off is that the maximum storage space available for the boot-code and software is limited by the BRAM. Each available BRAM contains 18 Kbits. Table 2-1 displays the total amount of BRAM memory available for each member of the Virtex-II Pro family.

Table 2-1:Available Virtex-II Pro Platform FPGA family BRAM andMicroprocessor Cores

| Device  | Columns | No. of PPC | Total SelectRAM <sup>1, 2</sup> Memory |          |           |  |

|---------|---------|------------|----------------------------------------|----------|-----------|--|

| Device  | Columns | Cores      | Blocks                                 | In Kbits | In Bits   |  |

| XC2VP4  | 4       | 1          | 28                                     | 504      | 516,096   |  |

| XC2VP7  | 6       | 1          | 44                                     | 792      | 811,008   |  |

| XC2VP20 | 8       | 2          | 88                                     | 1,584    | 1,622,016 |  |

| XC2VP50 | 12      | 4          | 216                                    | 3,888    | 3,981,312 |  |

#### Notes:

- 1. The XC2VP2 does not contain PPC cores, so standard Virtex-II configuration solutions can be utilized.

- 2. 16 Kbits of the BRAM are available for direct interfacing with the Virtex-II Pro PPC.

## **Basic Solution Wake-Up Flow**

#### Step 1

The Configuration stage is similar to other Virtex FPGA families. During this stage, the Virtex-II Pro device is powered on and completes three major phases:

- Clearing configuration memory

- Initialization

- Loading the bitstream.

Phase 1 and 2 simply prepare the device to receive the configuration data from the PROM. The FPGA's memory is cleared and the mode pin settings are sampled to determine the correct download mode. The appropriate pins become active to signify the loading of the configuration data. The loading of the bitstream defines the functional operation of the internal blocks, such as function look-up tables (LUTs), flip-flops (FFs), multiplexers, buffers, pullup/pulldown, slew rate, etc., and their interconnections.

#### Step 2

Device startup is a transition stage from the configuration mode to the normal programmed device operation. The startup sequence performs the following tasks:

- Release the DONE pin,

- Negate Global Tristate Signal (GTS) which activates all I/Os,

- Assert Global Write Enable (GWE) which allows all RAMS and flip-flops to change state, and finally,

- Assert End-Of-Startup (EOS) internal flag.

#### Step 3

At this stage, the FPGA has completed configuration and the PPC starts to execute code from the reset vector.

#### **Basic Software Flow**

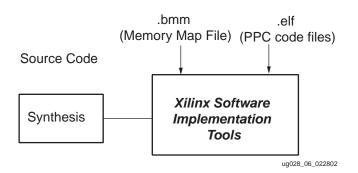

This section describes the software flows necessary to generate a valid programming bitstream with the Virtex-II Pro PPC boot code. It also explains how to convert this bitstream into a PROM file required for this solution.

The flow through the Xilinx software tools to create a valid bitstream for the Virtex-II Pro device in general is the same as it is for any other Xilinx FPGA. The standard flow takes a design originating from HDL or schematic source code through the design front-end tools to create a standard netlist. This netlist is taken through the Xilinx implementation tool suite to physically map, then place and route the design into the desired Virtex-II Pro architecture. For further details on these software tools, refer to the on-line software manual, the *Development Systems Reference Guide*.

The deviation from the most standard flow for Xilinx FPGA families to a flow targeting the Virtex-II Pro device is in the setup required to allow the PPC to execute code from the BRAM. Two additional files are utilized to enable this functionality, the Block SelectRAM Memory Map file (.bmm) and the software code file (.elf). For additional information on the creation and usage of these two files, refer to the *Virtex-II Pro Developer's Kit* (Vols. 4 and 6.

Figure 2-2: Xilinx Tool Software Flow for Bitstream Generation with BRAM Initialization

The last step in this software flow is the creation of the PROM file for programming the PROM. The PROM File is created in iMPACT software. The merged bitstream created from the Data2BRAM flow is used as the input file for iMPACT. The user targets the appropriate PROM density and .mcs format to create a serial formatted PROM file for the target solution. For a detailed flow, refer to the on-line software manual <u>iMPACT User</u> <u>Guide</u>.

# **Advanced Virtex-II Pro Wake-Up Solution**

### Overview

The second method discussed is for advanced users who want to take advantage of the configuration management and auxiliary storage capabilities of the System ACE CompactFlash (CF) solution.

The System ACE CF can manage up to eight separate designs for the Virtex-II Pro device. By default, one design is delivered at power-up to configure the Virtex-II Pro device and boot the PPC. On command, the System ACE CF can reconfigure the Virtex-II Pro with any of the eight possible designs stored in the CF.

The System ACE CF controller has a microprocessor (MPU) port that provides access to the CompactFlash. The Virtex-II Pro PPC can be connected to the System ACE CF MPU port to access data in the standard file structure within the CF.

The System ACE CF provides a centralized solution for system wake-up and the storage of auxiliary application code and data.

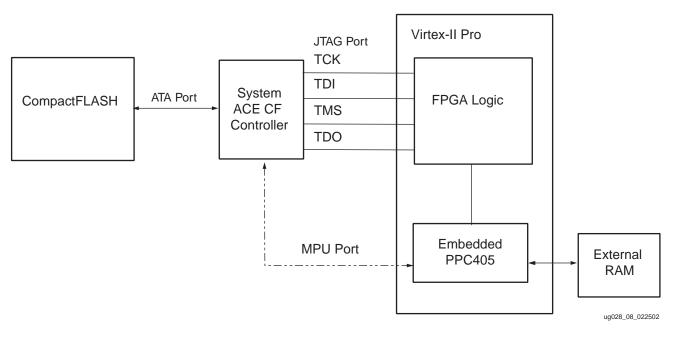

## Advanced System Architecture

The advanced system contains the CompactFlash storage device, the System ACE CompactFlash controller, the Virtex-II Pro device, and external RAM. The System ACE CF controller acts as the master controller for the CompactFlash device. At power-up or on command, the System ACE CF controller extracts a selected configuration file from the CompactFlash and delivers the configuration data to the Virtex-II Pro device via the JTAG Test Access Port (TAP). The System ACE CF configuration process includes the delivery of both the FPGA fabric configuration bits and the initialization of the external RAM with the code and data. See below for details on the configuration delivery scheme.

The optional MPU port connection between the Virtex-II Pro device and the System ACE CF controller gives the PPC access to the CompactFlash file structure for reading and writing additional application code and data.

# Advanced Solution Wake-Up Flow

The Virtex-II Pro JTAG configuration flow is designed to support reconfiguration as well as initial configuration. Thus, the Virtex-II Pro wake-up flow begins with a JTAG shutdown command sequence that disables the active logic in the FPGA. The FPGA configuration and startup stages are the same as in the Basic setup. However, two extra stages are required to load the PPC code and wake up the PPC.

The five stages of the wake-up flow are accomplished through JTAG command sequences from the System ACE CF.

#### Step 1

The shutdown stage halts the PPC and disables the active logic in the FPGA. This stage prepares the FPGA to receive new configuration data. In the case of a reconfiguration, this stage eliminates the danger of contention between the new configuration and the previously loaded configuration.

#### Step 2

The configuration stage is similar to the other Virtex FPGA families' configuration stages. During this stage, the new bitstream is downloaded to the Virtex-II Pro device. The bitstream defines the functional operation of the internal logic blocks, the I/O pins, and the PPC interconnects to internal and peripheral devices, such as the external RAM.

#### Step 3

Startup is a transition stage from the configuration mode to the normal programmed device operation. The startup sequence performs the following tasks:

- Releases the DONE pin,

- Negates Global Tristate Signal (GTS) which activates all I/Os,

- Asserts Global Write Enable (GWE) which allows all RAMS and flip-flops to change state, and finally

- Assert End-Of-Startup (EOS) internal flag.

At the completion of this stage, the FPGA fabric is active including the PPC interconnects.

#### Step 4

The PPC software loading stage fills the external RAM with the PPC boot code and data through the PPC control logic.

#### Step 5

The PPC boot stage consists of the setting of the PPC program counter to the starting location of the boot code and releasing the PPC into its normal run mode.

# Virtex-II Pro JTAG Test Access Port (TAP)

The JTAG TAP in the Virtex-II Pro device is tightly integrated with the FPGA configuration logic as well as the PPC control logic. The JTAG TAP and FPGA configuration logic integration allows the FPGA to be configured through the JTAG TAP. The JTAG TAP and PPC control logic integration allows the PPC to be controlled through the JTAG TAP.

JTAG control of the PPC is the key to the memory initialization and PPC wake-up scheme. The System ACE CF can instruct the PPC through the JTAG TAP to write the initial memory image. The System ACE CF can also instruct the PPC to start from a specific code location through the JTAG TAP.

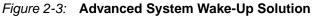

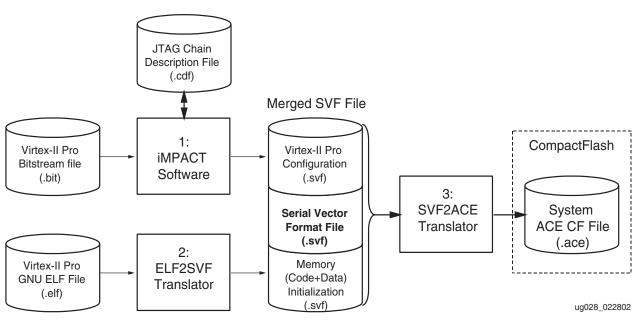

## Advanced Software Flow

A single System ACE CF configuration (.ace) file contains all the JTAG commands that are necessary to configure the Virtex-II Pro device and wake the PPC in the advanced system. The System ACE CF configuration file is created from two sources: the FPGA configuration bitstream (.bit) file and the PPC code and data (.elf) file. See the *Virtex-II Pro Developer's Kit* for descriptions of the flows that create the .bit and .elf files.

Because the target Virtex-II Pro device can be in a JTAG scan chain with an arbitrary number of JTAG devices, the System ACE CF configuration file preparation process must understand the JTAG scan chain layout. The System ACE CF solution delivers the configuration and code through serial JTAG vectors. These serial JTAG vectors are saved in an intermediate *de facto* standard Serial Vector Format (SVF) file.

Figure 2-4: Advanced Virtex-II Pro Software Flow

Transformation of the .bit and .elf files into the unified .ace file requires three software steps:

#### Step 1

The iMPACT software generates the JTAG vectors for delivering the bitstream to the target Virtex-II Pro within the JTAG scan chain. The result is an SVF file with vectors to shut down, configure, and start up the FPGA logic. (See the *iMPACT User Guide* for detailed instructions on defining the JTAG scan chain and creating an SVF file to program the Virtex-II Pro device.)

#### Step 2

The ELF2SVF translates the PPC code and data (.elf) file into JTAG instructions for the PPC to fill the appropriate memory locations. In addition, the ELF2SVF translator appends JTAG instructions to preset the PPC program counter to the starting location of the boot code and to put the PPC into its run state with the preset program counter value. The resulting SVF is appended to the bitstream configuration SVF file.

#### Step 3

Convert the combined SVF file into the corresponding System ACE CompactFlash (ACE) file.

The ACE file is copied to the CompactFlash unit for system deployment. (See the *System ACE CompactFlash User Guide* for detailed instructions on the System ACE CompactFlash operation and file structure.)

In the target system, the System ACE CF controller executes the ACE file from the CompactFlash to configure and wake up the PPC.