# CORE Generator Guide

Introduction

**Getting Started**

Using the CORE Generator

Understanding CORE Generator Design Flows

Understanding the HDL Design Flow

Troubleshooting the CORE Generator System

CORE Generator Guide

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5.717.340: 5.719.506: 5.719.507: 5.724.276: 5.726.484: 5.726.584: 5.734.866: 5.734.868: 5.737.234: 5.737.235:

5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5.847.993: 5.852.323: 5.861.761: 5.862.082: 5.867.396: 5.870.309: 5.870.327: 5.870.586: 5.874.834: 5.875.111: 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5.990.704: 5.991.523: 5.991.788: 5.991.880: 5.991.908: 5.995.419: 5.995.744: 5.995.988: 5.999.014: 5.999.025: 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This manual describes the Xilinx CORE Generator<sup>™</sup> Tool, which is used for parameterizing cores optimized for Xilinx FPGAs.

Note This Xilinx software release is certified Year 2000 compliant.

### **Manual Contents**

This manual covers the following topics:

- Chapter 1, "Introduction"—Introduces the Xilinx CORE Generator System by describing the process for installation and how to obtain new and updated COREs.

- Chapter 2, "Getting Started"—Provides information for setting up your environment and installing the CORE Generator.

- Chapter 3, "Using the CORE Generator"—Describes the CORE browser, customizing a CORE, updating COREs, and integrating the CORE Generator into applications.

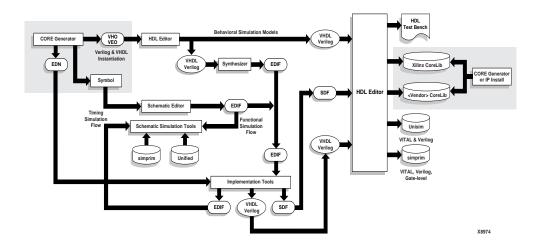

- Chapter 4, "Understanding CORE Generator Design Flows"— Describes how to integrate a CORE Generator module into a design through the use of various design flows; schematic and HDL.

- Chapter 5, "Understanding the HDL Design Flow"—Describes the elements and procedures in a HDL design flow.

- Appendix A, "Troubleshooting the Core Generator System"— Contains solutions and resources for using the CORE Generator System.

## **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/<br>index.htm                                                                                                          |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                 |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                           |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-<br>specific information on Xilinx device characteristics, including readback,<br>boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                      |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/<br>index.htm                                                                                                                 |

# Conventions

This manual uses the following conventions. An example illustrates each convention.

### Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{ }" in Courier bold are not literal and square brackets "[ ]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

File  $\rightarrow$  Open

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

.

A horizontal ellipsis " " indica

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2locn;

### **Online Document**

The following conventions are used for online documents.

• Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference. • Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# Contents

#### **About This Manual**

| Manual Contents      | . v  |

|----------------------|------|

| Additional Resources | . vi |

#### Conventions

| Typographical   | vii  |

|-----------------|------|

| Online Document | viii |

#### Chapter 1 Introduction

| CORE Generator System                            | 1-1 |

|--------------------------------------------------|-----|

| CORE Generator Components                        | 1-4 |

| New and Updated Cores                            | 1-4 |

| System Requirements and Installation Information | 1-4 |

| Additional Resources                             | 1-4 |

#### Chapter 2 Getting Started

| Starting the CORE Generator System              | 2-1 |

|-------------------------------------------------|-----|

| CORE Generator System Installation Requirements | 2-2 |

| Setting Preferences                             | 2-2 |

| Setting Up Projects                             | 2-3 |

| Creating a New Project                          | 2-4 |

| Opening an Existing Project                     | 2-4 |

| Selecting Design Entry Options                  | 2-6 |

| Schematic Design Environment                    | 2-6 |

| HDL Synthesis Design Environment                | 2-6 |

| Selecting Target XILINX FPGA Family Options     | 2-7 |

| Changing Project Design Entry Options           | 2-7 |

| Installing Setup Files                   | 2-8 |

|------------------------------------------|-----|

| coregen.prj                              |     |

| corelib.xml                              | 2-8 |

| .coregen.prf                             | 2-9 |

| Using the Web Browser and the PDF Viewer |     |

### Chapter 3 Using the CORE Generator

| Using the CORE Browser                                        | 3-1  |

|---------------------------------------------------------------|------|

| Customizing a Core                                            | 3-4  |

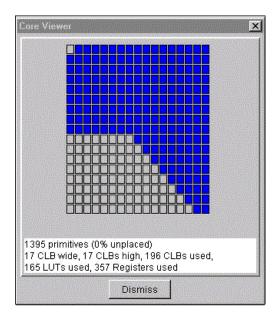

| Displaying the CoreViewer                                     | 3-5  |

| Naming CORE Generator Modules                                 |      |

| Using the Generate, Cancel, and Data Sheet Buttons            | 3-8  |

| Illegal or Invalid Values                                     | 3-8  |

| .COE Files                                                    |      |

| Specifying Command Files                                      |      |

| coregen.ini/coregen_ <i>user_name</i> .ini                    |      |

| User-Generated Command Files                                  |      |

| XCO Files                                                     |      |

| coregen.log                                                   |      |

| Generating Cores in Batch Mode                                |      |

| Defining CORE Generator Command Line Options                  |      |

| -b command_file_name                                          |      |

| -i coregen_ini_file_name                                      |      |

| –p project_path                                               |      |

| –q polling_dir_path                                           |      |

|                                                               |      |

| Listing the CORE Generator Commands                           |      |

| Listing the CORE Generator Global Properties                  |      |

| Listing Project Properties                                    |      |

| Updating Cores in the CORE Generator<br>Downloading New Cores |      |

| Updating a Core Version in an Existing Project                |      |

| Understanding the Update Project Cores Menu                   |      |

| Removing Cores                                                |      |

| Using the get_models Command                                  |      |

| Integrating CORE Generator into Applications                  |      |

| Polling Mode                                                  |      |

| Output Polling Files                                          |      |

| Input Polling Files                                           |      |

| ASY and XSF Files                                             |      |

| Listing Inputs and Outputs Files                              |      |

|                                                               | 0 20 |

#### Chapter 4 Understanding CORE Generator Design Flows

| Understanding CORE Generator Design Flow Basics               | . 4-1  |

|---------------------------------------------------------------|--------|

| Describing the CORE Generator Schematic Design Flow           | 4-2    |

| Starting a Schematic Design Flow with Viewlogic               | . 4-3  |

| Creating a Viewlogic Project                                  | 4-4    |

| Creating Output Files                                         | 4-6    |

| Foundation Design Flow                                        | 4-8    |

| Foundation ISE Design Flow                                    | 4-8    |

| Mentor Design Flow                                            | 4-8    |

| Cadence Design Flow                                           |        |

| Describing the HDL Behavioral Model Delivery System Features. | 4-8    |

| XilinxCoreLib Simulation Library                              | . 4-9  |

| coredb                                                        | . 4-9  |

| Instantiation Template Files                                  | . 4-9  |

| Support for Unused Optional Pins                              | . 4-10 |

| verilog_analyze_order File                                    | . 4-10 |

| vhdl_analyze_order File                                       | . 4-10 |

| Using the CORE Generator Verilog Design Flow Procedure        | . 4-11 |

| Using Instantiation Templates                                 | . 4-12 |

| Using a .VEO Instantiation Template File                      | . 4-12 |

| Verilog Instantiation Template for an 8-Bit Adder             | . 4-12 |

| Using the CORE Generator VHDL Design Flow Procedure           | . 4-14 |

| Using a .VHO Instantiation Template File                      | 4-15   |

| VHDL Instantiation Template for an 8-Bit Adder                | . 4-15 |

|                                                               |        |

#### Chapter 5 Understanding the HDL Design Flow

| Using the HDL Behavioral Model Delivery System | 5-1  |

|------------------------------------------------|------|

| Understanding the Verilog HDL Design Flow      | 5-2  |

| Describing the Verilog Design Flow Procedure   | 5-2  |

| Implementation Using Cadence Verilog-XL        |      |

| and MTI Model Sim/VLOG                         | 5-17 |

| Understanding the VHDL HDL Design Flow         | 5-18 |

| Describing the VHDL Design Flow Procedure      | 5-19 |

#### Appendix A Troubleshooting the Core Generator System

| Finding Solutions          | A-1 |

|----------------------------|-----|

| Additional Resources       | A-2 |

| AllianceCORE Modules       | A-2 |

| Obtaining Customer Support | A-2 |

# Chapter 1

# Introduction

This chapter introduces the Xilinx CORE Generator System, an easy to use design tool that delivers parameterizable COREs optimized for Xilinx FPGAs.

The following topics are included in this chapter:

- "CORE Generator System"

- "CORE Generator Components"

- "New and Updated Cores"

- "System Requirements and Installation Information"

- "Additional Resources"

### **CORE Generator System**

The CORE Generator System's main Graphical User Interface (GUI) allows central access to COREs, data sheets, variable options, and help functions, as shown in the following figure:

| Xilinx CORE Generator 2.1i       File     Project       Quere     Help       Image: State S | oject Path: C:/yourdir/yourprojectdir 🔽 |      |         |          | _     |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|---------|----------|-------|---|

| View Catalog: by Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |      |         |          |       |   |

| Target Family: Virtex   Sasic Elements  Communication & Networking  Jugital Signal Processing  Microprocessors, Controllers & Peripherals  ProtoType & Development Hardware Products Standard Bus Interfaces  Storage Elements & Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Contents of:<br>Name                    | Туре | Version | <u>.</u> | Vendo | r |

| Set current Project to C:/yourdir/yourprojectdir<br>New Preference options have been updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                       |      |         |          |       |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |      |         |          | A 19  | 8 |

#### Figure 1-1 CORE Generator GUI

The Xilinx CORE Generator System provides you with a catalog of ready-made functions ranging in complexity from simple arithmetic operators such as adders, accumulators and multipliers, to systemlevel building blocks including filters, transforms and memories.

The words "function" and "core" are used interchangeably in this guide to mean a design entity like a multiplier or FIR filter which the CORE Generator System can generate for the designer.

Cores are organized by functional type into folders that expand or contract on demand. Detailed information on each core is included in a specification or data sheet (Acrobat format), which is easily accessed by clicking on the Datasheet button in the core customization window or by clicking on the Datasheet icon in the main CORE Generator application toolbar. This launches the Adobe Acrobat Reader and calls up the datasheet for the selected core. Datasheets include the following items:

- Functional information

- Area and performance data for some cores

- Pinouts and interface signal names

- Details on how to use the core in an application, making it easy for you to determine whether a core meets your design requirements

The CORE Generator System can customize a generic functional building block such as a FIR filter or a multiplier to meet the needs of your application and simultaneously deliver high levels of performance and area efficiency. This is accomplished by using Xilinx's core-friendly FPGA architectures and Xilinx Smart-IP<sup>TM</sup> technology. Smart-IP technology leverages the following items:

- Xilinx FPGA architectural advantages such as look-up tables (LUTs), distributed RAM, segmented routing and floorplanning information

- Relative location constraints and expert logic mapping to optimize performance of a given core instance in a given Xilinx FPGA architecture

Smart-IP technology delivers the following:

- Physical layout optimized for high performance

- Predictable performance and resource utilization

- Reduced power requirements through compact design and interconnect minimization

- Performance independent of device size

- Ability to use multiple cores without deterioration of performance

- Reduced compile time over competing architectures

- Reduced compile time over competing architectures

Parameterization provides the ability to generate cores which meet design flexibility needs and which meet design size constraints. For each core, the CORE Generator System delivers the following:

- A customized EDIF netlist

- Verilog<sup>®</sup> or VHDL behavioral simulation models

- Verilog or VHDL Instantiation templates

- Foundation<sup>™</sup> or Viewlogic<sup>®</sup> schematic symbols

### **CORE Generator Components**

The Xilinx CORE Generator system consists of the following three distinct products:

- CORE Generator application

- Acrobat<sup>™</sup> Reader application

- JAVA<sup>TM</sup> Runtime Support

### **New and Updated Cores**

New cores can be downloaded and easily added to the CORE Generator from the Xilinx Website at either

http://www.xilinx.com/ipcenter/coregen/updates.htm

or at

http://www.xilinx.com/products/logicore/coregen

Please review the CORE Generator Web page before starting a new design. You need to verify that you have the latest version of each core and core datasheet.

### System Requirements and Installation Information

See the 3.1i Release Notes for information on system requirements and installation instructions for the CORE Generator System or the Xilinx Alliance Quick Start Guide or Foundation Quick Start Guide.

Adobe Acrobat v 3.0 or later is needed to launch and view the cores datasheets.

For Viewlogic users, the CORE Generator System interface to Viewlogic requires that both the Viewlogic and the Xilinx implementation Tools be set up on your system.

### Additional Resources

The following section details additional online documentation resources and how to access the information.

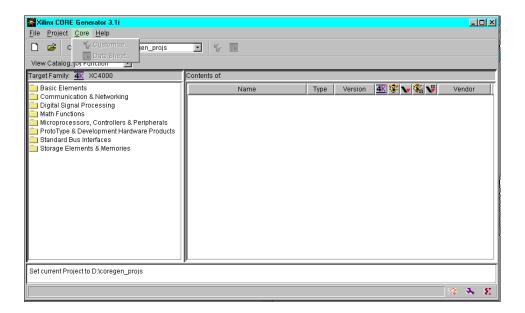

Links to the IP Center are available from the CORE Generator Help Menu with the following path:

| Xilinx CORE Generator 3.1i                                                              |                       |      |         |                   |       | _      |   |

|-----------------------------------------------------------------------------------------|-----------------------|------|---------|-------------------|-------|--------|---|

| <u>File Project Core H</u> elp                                                          |                       |      |         |                   |       |        |   |

| Current F Online Documentation                                                          |                       |      |         |                   |       |        |   |

| View Catalog: by Fur About CORE Generator                                               | • Q IP <u>C</u> enter |      |         |                   |       |        |   |

|                                                                                         | Support and Services  |      |         |                   |       |        |   |

| Target Family: 4K XC4000                                                                | 🗧 🌋 Xilinx Home Page  |      |         | 1                 |       |        |   |

| Basic Elements                                                                          | Name                  | Туре | Version | _ <u>4K</u> 😻 🍾 🖗 | ĥ 😽 🔜 | /endor |   |

| Communication & Networking                                                              |                       |      |         |                   |       |        |   |

| 🚞 Math Functions                                                                        |                       |      |         |                   |       |        |   |

| Microprocessors, Controllers & Peripherals<br>ProtoType & Development Hardware Products |                       |      |         |                   |       |        |   |

| Standard Bus Interfaces                                                                 |                       |      |         |                   |       |        |   |

| Storage Elements & Memories                                                             |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

|                                                                                         |                       |      |         |                   |       |        |   |

| J                                                                                       | · JJ                  |      |         |                   |       |        |   |

| The project has been updated to use the latest vers                                     | ion of all cores.     |      |         |                   |       |        | ÷ |

|                                                                                         |                       |      |         |                   |       |        |   |

#### $\mathtt{Help} \to \mathtt{Help}$ on the $\mathtt{Web} \to \mathtt{IP}$ Center

#### Figure 1-2 Help Menu

For an overview of the supported design flows, refer to Chapter 4, "Understanding CORE Generator Design Flow Basics" in this manual.

# Chapter 2

# **Getting Started**

This chapter describes the various elements of the CORE Generator System. Review this information before starting a design using the cores offered with the CORE Generator System. The following sections are described in this chapter:

- "Starting the CORE Generator System"

- "Setting Up Projects"

- "Opening an Existing Project"

- "Selecting Design Entry Options"

- "Selecting Target XILINX FPGA Family Options"

- "Changing Project Design Entry Options"

- "Installing Setup Files"

- "Using the Web Browser and the PDF Viewer"

### Starting the CORE Generator System

This section describes the functions performed by the user in initiating, designing, and maintaining core designs in Xilinx CORE Generator System's GUI environment.

#### **CORE Generator System Installation Requirements**

To install the CORE Generator in either your Windows or UNIX workstation environments, do one of the following:

- (Windows) Select Start  $\rightarrow$  Programs  $\rightarrow$  Xilinx Alliance Series 2.1i  $\rightarrow$  Accessories  $\rightarrow$  CORE Generator System.

- (UNIX Workstation) At a UNIX shell prompt, type coregen. This starts the CORE Generator System. Make sure your environment is setup to run the Xilinx software as specified in the *Xilinx Alliance Quick Start Guide* or *Foundation Quick Start Guide*. The two required settings are 1) *XILINX* variable, set to your Xilinx installation directory, and 2) *PATH* variable, set to \$XILINX/bin/*platform*. The platform is either sol or hp.

**Note** For detailed information on CORE Generator installation for both the PC and the Unix Workstation, refer to the *Xilinx Alliance Quick Start Guide* or *Foundation Quick Start Guide*.

The CORE Generator application is installed from one of the following main Xilinx software release CDs:

- Alliance 3.1i

- Foundation 3.1i

### **Setting Preferences**

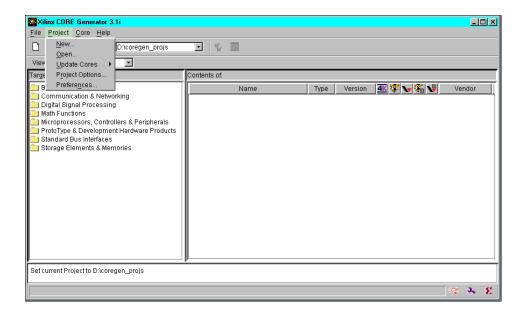

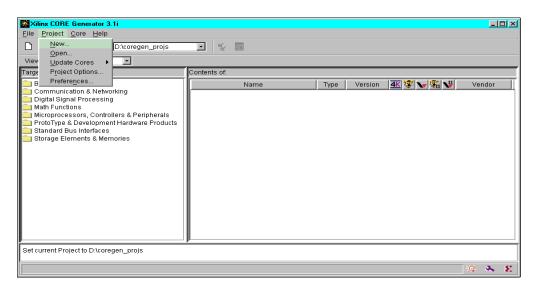

Your preferences are set through the preferences dialog box and are maintained on a per user basis, as shown in the following figure:

| Xilinx CORE Generator 3.1i                 |                |              |           |        |     |

|--------------------------------------------|----------------|--------------|-----------|--------|-----|

| <u>File</u> Project Core Help              |                |              |           |        |     |

| <u>New</u> D:tcoregen_projs                |                |              |           |        |     |

| View Update Cores                          |                |              |           |        |     |

| Targe Project Options                      | Contents of:   |              |           |        | _   |

| Preferences                                |                | True Vention |           | Mandan | _   |

| Communication & Networking                 | Name           | Type Version | 🛛 🕂 😵 🗸 🖓 | Vendor | - 1 |

| 🛅 Digital Signal Processing                |                |              |           |        |     |

| Math Functions                             | 1              |              |           |        |     |

| Microprocessors, Controllers & Peripherals | 1              |              |           |        |     |

| 🚞 Standard Bus Interfaces                  | 1              |              |           |        |     |

| 🚞 Storage Elements & Memories              | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

|                                            | 1              |              |           |        |     |

| Performent Disjoint to Difference on proje | μ <sup>μ</sup> |              |           |        | _   |

| Set current Project to D:\coregen_projs    |                |              |           |        |     |

|                                            |                |              |           | 19 A   | 8   |

#### Figure 2-1 Preference Dialog Box

The location for Preferences on various platforms are as follows:

- (Windows) Preferences are stored in the registry and written to the Windows registry.

- (UNIX workstation) Preferences are stored in your home directory in the file, coregen.prf.

# **Setting Up Projects**

The following section describes creating new projects, opening up existing projects, selecting design entry options, and other similar topics.

### **Creating a New Project**

This next section describes the procedure for creating a new project using the Xilinx CORE Generator System.

1. Select  $Project \rightarrow New$

In the New Project screen, you can type the path to the new project directory into the **Directory** text field or you can click on the **Browse** button and navigate to it.

**Note** The Xilinx CORE Generator System is designed to operate within the directory structure of a pre-existing design entry environment. Because of this, the CORE Generator System does not create directories. You must make sure a directory exists before browsing to it.

When a new project is created the cores displayed in the CORE Generator System's main window are the latest versions of the cores.

2. Specify your Electronic Design Automation (EDA) Vendor from the following selection: Foundation, Viewlogic, Cadence, Mentor, or Other).

If you select Other, you need to specify the Netlist Bus Format for individual bus bits. The B represents the name of the bus and the I represents the bus index, for example B<I>, B[I], or BI. Selecting any of the other vendors automatically sets the Netlist Bus Format setting to the correct value for that vendor.

### **Opening an Existing Project**

You can track the actual number of previously opened projects through the **Project**  $\rightarrow$  **Preferences** option in the main CORE Generator GUI.

- 1. Select a project from the Project Path list in the dialog box. Select the CORE Generator project that you want to work in and click OK.

- 2. You may also place a check mark in the Always Open Last Project check box in the following figure. Selecting this box causes the CORE Generator System to bypass the CORE Generator dialog box, and to return to the last project worked on.

| Open Project |                  |        | ×   |

|--------------|------------------|--------|-----|

|              |                  |        |     |

|              |                  |        | - 1 |

| Directory    | D:\coregen_projs | Browse | B   |

| Describer    | -11              |        |     |

| Recent Pro   | ojects:          |        |     |

| D:\corege    | n_projs          |        |     |

|              |                  |        |     |

|              |                  |        |     |

|              |                  |        |     |

|              |                  |        | _   |

|              |                  |        |     |

|              |                  |        |     |

| 🖌 🗹 Always O | pen Last Project |        |     |

|              |                  |        |     |

|              | OK Cancel        |        |     |

|              |                  |        |     |

#### Figure 2-2 Open Project Box

Note When starting up the CORE Generator System, select Open Project and deselect the Always Open Last Project check box in the Open Project dialog box. This restores the launching of the CORE Generator project dialog box

For each user, the CORE Generator remembers the last n projects that you opened. You can S+=elect a project from this list or browse to any valid CORE Generator project. Each project maintains a list of the cores visible to that project and their version. If a new IP has been added to the repository or removed from it, the CORE Generator pops up a dialog asking if you want to update the list of visible cores for that project.

When a project is opened by CORE Generator, it is locked to prevent other users from working in the same project and potentially overwriting files. If another user tries to open the project, they receive a dialog showing who has the project locked. The lock can be removed from this file. If the original CORE Generator session loses its lock, then the next time you attempt to generate a core, you will receive a dialog showing who overrode the lock.

## **Selecting Design Entry Options**

From the Project Options dialog, select the Design Entry that you would like to use. Selecting one of the following entries shows the corresponding vendor(s) supported in the Vendor box:

### Schematic Design Environment

The CORE Generator design environment currently supports the following schematic design tools:

- Viewlogic

- Foundation

- Mentor<sup>®</sup>

- Cadence<sup>®</sup>

**Note** Limited Cadence support is currently available as described in the "Cadence Design Flow" section.

### **HDL Synthesis Design Environment**

The CORE Generator design environment currently supports the following Hardware Descriptive Language (HDL) Synthesis tools, which consist of VHDL or Verilog:

- Synopsys<sup>®</sup> FPGA Express

- Synopsys FPGA Compiler

- Exemplar

- Synplicity

When you chose VHDL or Verilog, the corresponding instantiation template is generated in module\_name.vho or module\_name.veo. These files contain commented HDL code that can be used to instantiate a CORE Generator module in an HDL design, and also contain code that supports behavioral simulation. If you select VHDL as the design entry, then a .VHO file is generated. If you select Verilog as the design entry, then a .VEO file is generated. Vendor specific files may also be generated for schematic symbols and other uses. Based on the Vendor chosen, the output EDIF netlist contains the appropriate bus delimiter for the module (), <>, [], or none. This is necessary so that the ports in the CORE Generator module match the port references in the EDIF netlist for your top level design. The vendor option also controls the generation of vendor specific pin and symbol files.

# Selecting Target XILINX FPGA Family Options

The Xilinx CORE Generator System tailors the cores to the selected Target Family setting. All cores are optimized to the selected Xilinx architecture and do not work if integrated into a design targeted to a different Xilinx FPGA family. Cores, that were targeted to the Spartan architecture when they were generated, do not work if placed in a Virtex design. You need to select the Target Family based on the Xilinx architecture that you are targeting. Changing architectures requires you to regenerate any cores you have already created.

After you have selected all the project options, click OK. The Xilinx CORE Generator System initializes the new project. This initialization may take several seconds. A coregen.prj file is written to the new project. The coregen.prj file contains a record of all installed cores at the time of project creation and their available versions. In order for the list of cores available to be displayed, you need to specify a valid CORE Generator project.

# **Changing Project Design Entry Options**

You may change the Project Design Entry Options as follows:

1. Select  $Project \rightarrow Project$  Options menu.

This opens a Project Options dialog box. You can change any of the Design Entry, Vendor, Behavioral Simulation, and Family options.

2. Click OK when you have finished modifying these options.

**Note** Changing the project options only affects new cores that you generate. Cores created before making the project changes still reflect the old options. Regenerate any cores that need to inherit the new project options.

### **Installing Setup Files**

The following section describes in some detail the setup files in the CORE Generator. The setup file is required to properly configure your CORE Generator session.

#### coregen.prj

The coregen.prj is the CORE Generator project file and is written to your home directory on your UNIX workstation. The coregen.prj file is automatically created whenever you create a new project. It contains a record of project-specific property settings, information on versions of the cores available to the project, and user-specified output files. A valid CORE Generator project directory must contain a coregen.prj file.

The information in the coregen.prj file includes a list of all the IP cores and versions that are available to the project, as well as the version of every core actually used in the project.

The coregen.prj file is a configuration file which is created, read, and modified by the CORE Generator System for project management purposes and should not be altered by the user.

#### corelib.xml

The CORE catalog file is called corelib.xml and is located in \$XILINX/coregen/ip. You build this catalog by scanning each of the cores found in \$XILINX/coregen/ip. This catalog is used by CORE Generator at runtime to identify and locate all the cores that are present in a CORE Generator software installation. You can also update the catalog manually using the coredb utility.

The corelib.xml is present in the initial installation and updated with the installation of each ip update. There is a utility coredb that you can use to regenerate it if necessary. CORE Generator generates corelib.xml if it is not present or out of synch with the ip repository. If the corelib.xml needs to be built and you cannot write to \$XILINX/ coregen/ip, CORE Generator can run but startup time is impacted by trying to rebuild corelib.xml each time.

#### .coregen.prf

The .coregen.prf is the Xilinx CORE Generator preferences file for UNIX workstations. This is an ASCII option settings file that records various user specific settings for the CORE Generator GUI. This file consists of a mix of comment lines and property specification lines. Comment lines begin with the # (octothorpe) character and designate a line which is ignored when the file is read by the CORE Generator System. The format for a line specifying a property in the preference file is PropertyName=Value.For example,

AlwaysOpenLastProject=true

Each Property Name represents a particular property within the Xilinx CORE Generator, and the corresponding Value Field is the value to be applied to that property. Your preference settings are stored in your home directory on a PC vendors platform. This is recorded in the Windows registry. The name of your preference file should be

During start-up, and after any optional coregen.ini file is read (Workstations only), CORE Generator System searches the preferences directory for a .coregen.prf file. If this file is found, it is loaded and all preferences contained in it override the default CORE Generator System preference settings. If no preference file is found for the user (as in the case of a first-time user), the various preference values take on their hardcoded default values.

.coregen.prf.

The first time you start up the CORE Generator System, you will not see a preference file. The preference file, .coregen.prf, is created the first time you exit out of the CORE Generator System. The file is automatically written to \$XILINX/coregen/preferences when you exit the CORE Generator application, based on settings you have specified during a project session.

### Using the Web Browser and the PDF Viewer

Another feature of the Xilinx CORE Generator System, is the ability to link to sites on the Web. You can click to the Xilinx CORE Generator System Home page or the Xilinx support.xilinx.com site. You can also link to the AllianceCORE partner Websites. The Xilinx CORE Generator System also provides all core datasheets in Adobe Acrobat PDF format.

| Logi CKRLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Accumulator V1.0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 17, 1999                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Product Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Kirv Inc.<br>2100 Logic Drup<br>Ban Jose, CA 95124<br>Phona: +1 400-559-7770<br>Fait: +1 400-559-7174<br>Lift: www.xiirv.com/spcentar<br>www.xiirv.com/spcentar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Optional clock enable, asynchronous and synchronous controls     Optional non-registered output     Optional pages (Lood) capability     Incorporates (Lood) capability     Incorporates (Lood) capability     Incorporates (Incod) capability     To be used with version 2.1i and later of the XBrox CORE Generator System <b>Functional Description</b> The Accumulator module can generate adder-based, soft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Features  • Oropin module for Viriac, Virtee <sup>114</sup> : E and Speram <sup>114</sup> E if Speram <sup>11</sup> | Transition-based and addentivabletative-based accumulater operating an eigend or uneigend or uneigend or uneigend or the registrater or insplater to operating the part of the registrater or insplatered on the registrater of the registrate |

#### Figure 2-3 Data Sheets

The location of both the Web browser and the PDF Viewer can be set with the Preference Options dialog box, as shown in the following figure:

#### Figure 2-4 Preference Dialog Box

To locate the Web Browser and the PDF Viewer, use the following procedure:

1. Select Project  $\rightarrow$  Preferences

The Preference Options dialog box appears.

| Preference Options          |                                                 | × |

|-----------------------------|-------------------------------------------------|---|

| Number of projects to keep  | 8                                               |   |

| Location of Web Browser     | C:\Program Files\Netscape\Communicator\P Browse |   |

| Location of PDF Viewer      | C:\Acrobat3\Exchange\AcroEx32.exe Browse        |   |

| 🗹 Automatically open last p | roject                                          |   |

| Automatically overwrite of  | utput files                                     |   |

|                             | OK Cancel Reset                                 |   |