# Timing Analyzer Guide

Introduction

**Getting Started**

**Timing Analysis**

**Using the Timing Analyzer**

**Glossary**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT step Advanced, XACT step Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235;

5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

### **About This Manual**

This manual describes Xilinx's Timing Analyzer program, a graphical user interface tool that performs static timing analysis of an FPGA or CPLD design.

The illustrations and examples in this user guide are based on the UNIX workstation version of the Timing Analyzer software. In most cases there are only minor differences in the appearance of the Timing Analyzer on all supported platforms. Any significant differences between platforms are described in this user guide.

Before using this manual, you should be familiar with the operations that are common to all Xilinx software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," describes the Timing Analyzer's function, place in the Xilinx design flow, key features, inputs and outputs, and the architectures with which it works. It also outlines the basic procedure for using the tool.

- Chapter 2, "Getting Started," describes how to access and exit the Timing Analyzer; how to use its menus, icons, Console window, dialog boxes, and filters; and how to use its online help facility.

- Chapter 3, "Timing Analysis," describes the basic path types and explains how the Timing Analyzer solves some basic design analysis problems.

- Chapter 4, "Using the Timing Analyzer," explains how to perform most of the Timing Analyzer's major functions.

- "Glossary" defines all the terms that you should understand to use the Timing Analyzer effectively.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                          |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools Search this database using the search function at http://support.xilinx.com/support/searchtd.htm                                                                                             |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                    |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |  |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                               |  |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                 |  |

### **Conventions**

This manual uses the following conventions. An example illustrates each convention.

# **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: - 100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt del net=

```

Courier bold also indicates commands that you select from a menu.

```

File \rightarrow Open

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on|off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

```

allow block block_name loc1 loc2locn;

```

### **Online Document**

The following conventions are used for online documents.

Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference. • Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Contents**

| About This | Manual                                                                                                                                                     |                                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|            | Manual Contents                                                                                                                                            |                                               |

| Convention | s                                                                                                                                                          |                                               |

|            | TypographicalOnline Document                                                                                                                               |                                               |

| Chapter 1  | Introduction                                                                                                                                               |                                               |

|            | Design Flow Inputs and Outputs Architectures Features Interface Reports Path Filtering Commands Macros Analysis Interrupt Online Help                      | 1-3<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5        |

| Chapter 2  | Getting Started                                                                                                                                            |                                               |

|            | Starting the Timing Analyzer From the Design Manager Stand-Alone Tool From the Command Line Timing Analyzer Window Menus Toolbar Status Bar Console Window | 2-1<br>2-2<br>2-2<br>2-3<br>2-4<br>2-5<br>2-5 |

|           | Dialog Boxes                                 | 2-6  |

|-----------|----------------------------------------------|------|

|           | Common Fields                                | 2-6  |

|           | Analysis Dialog Tabs                         |      |

|           | Using Filters with Commands                  |      |

|           | Valid Inputs and Wildcards                   |      |

|           | Matching Text Strings                        |      |

|           | Basic Timing Analysis Procedure              |      |

|           | Obtaining Help                               |      |

|           | Help Menu                                    |      |

|           | Context-Sensitive Help                       |      |

|           | Toolbar Button                               |      |

|           | Help Button in Dialog Boxes                  |      |

|           | F1 Key                                       |      |

|           | Exiting the Timing Analyzer                  | 2-11 |

| Chapter 3 | Timing Analysis                              |      |

|           | Basic Path Types                             | 3-1  |

|           | Clock to Setup                               |      |

|           | Clock to Pad                                 |      |

|           | Paths Ending at Clock Pin of Flip-Flops      |      |

|           | Setup to Clock at the Pad                    |      |

|           | Clock Pad to Output Pad                      |      |

|           | Pad to Pad                                   |      |

|           | Pad to Setup                                 |      |

|           | Design Analysis Issues                       |      |

|           | Feedback Loops                               |      |

|           | Timing Constraints                           |      |

|           | Clock Skew                                   | 3-17 |

|           | Negative Clock Skew                          | 3-18 |

|           | Positive Clock Skew                          |      |

|           | During Timing Analysis                       | 3-19 |

|           | Off-Chip Delay                               | 3-21 |

| Chapter 4 | Using the Timing Analyzer                    |      |

|           | Opening a Design                             | 4-1  |

|           | Apply Physical Constraints Files             |      |

|           | Manually Opening a Physical Constraints File |      |

|           | Viewing a Physical Constraints File          |      |

|           | Viewing Settings                             |      |

|           | Viewing Clocks                               |      |

|           | Querying for Information                     |      |

|           |                                              |      |

| Query Nets Report                                 | 4-7  |  |

|---------------------------------------------------|------|--|

| Net Characteristics                               |      |  |

| Delay Value                                       | 4-8  |  |

| Query Time Groups Report                          | 4-9  |  |

| Creating Reports                                  | 4-9  |  |

| Timing Constraints Analysis                       |      |  |

| Analyze Against Auto Generated Design Constraints |      |  |

| Analysis Report                                   | 4-15 |  |

| Analyze Against User Specified Paths by Defining  |      |  |

| Endpoints Analysis Report                         | 4-22 |  |

| Viewing a Report                                  | 4-25 |  |

| Saving a Report                                   | 4-27 |  |

| Searching for Text in a Report                    | 4-27 |  |

| Printing a Report                                 | 4-28 |  |

| Closing a Report                                  |      |  |

| Using Menu Commands                               | 4-29 |  |

| Using the Mouse                                   |      |  |

| Using the Keyboard                                |      |  |

| Opening a Saved Report                            |      |  |

| Specifying Report Appearance and Content          | 4-31 |  |

| Creating a Summary Report                         | 4-32 |  |

| Setting the Maximum Number of Paths Per Timing    |      |  |

| Constraint                                        |      |  |

| Reporting Delays Less Than a Value                |      |  |

| Reporting Delays Greater Than a Value             |      |  |

| Sorting Path Report Order                         |      |  |

| Reporting Only Longest Paths Between Points       |      |  |

| Generating Wide Reports                           |      |  |

| Changing the Speed Grade                          |      |  |

| Using Path Filtering Commands                     |      |  |

| Timing Constraint Filters                         |      |  |

| Custom Filters                                    |      |  |

| Selecting Sources                                 |      |  |

| Selecting Destinations                            |      |  |

| Common Filters                                    |      |  |

| Including Paths with Nets                         |      |  |

| Excluding Paths with Nets                         |      |  |

| Path Tracing                                      |      |  |

| Resetting Path Filters to Defaults                |      |  |

| Using the Console Window                          |      |  |

| Executing a Command                               |      |  |

| Re-Executing Commands                             | 4-40 |  |

### Timing Analyzer Guide

| Using Macros                         | 4-40 |

|--------------------------------------|------|

| Creating a Macro                     |      |

| Saving a New Macro                   | 4-42 |

| Running a Macro                      | 4-43 |

| Editing a Macro                      |      |

| Overwriting an Existing Macro        | 4-44 |

| Saving an Edited Macro to a New File | 4-45 |

| Suppressing Informational Messages   | 4-46 |

# Chapter 1

### Introduction

The Timing Analyzer performs static timing analysis of an FPGA or CPLD design. The FPGA design must be mapped and can be partially or completely placed, routed or both. The CPLD design must be completely placed and routed. A static timing analysis is a point-to-point analysis of a design network. It does not include insertion of stimulus vectors.

The Timing Analyzer verifies that the delay along a given path or paths meets your specified timing requirements. It organizes and displays data that allows you to analyze the critical paths in your circuit, the cycle time of the circuit, the delay along any specified paths, and the paths with the greatest delay. It also provides a quick analysis of the effect of different speed grades on the same design.

The Timing Analyzer works with synchronous systems composed of flip-flops and combinatorial logic. In synchronous design, the Timing Analyzer takes into account all path delays, including clock-to-Q and setup requirements, while calculating the worst-case timing of the design. However, the Timing Analyzer does not perform setup and hold checks; you must use a simulation tool to perform these checks.

This chapter briefly describes the Timing Analyzer's function, place in the design flow, major features, inputs and outputs, and the architectures with which it works. It also outlines the basic procedure for using the tool. This chapter contains these sections.

- "Design Flow"

- "Inputs and Outputs"

- "Architectures"

- "Features"

- "Online Help"

# **Design Flow**

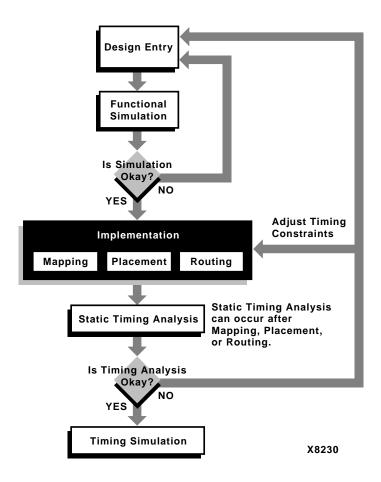

You use the Timing Analyzer after mapping, placing, and routing, as shown in the following figure.

Figure 1-1 Timing Analyzer in the Design Flow

### **Inputs and Outputs**

The Timing Analyzer has the following input and output capabilities:

- Accepts NCD design files and physical constraints files (PCF) output by the mapper for FPGAs

- Accepts VM6 (CPLD) design files output by the fitting software

- Loads macro files (XTM) as input

- Creates timing report (TWR) files as output

- Creates macro (XTM) files

**Note** Load PCF files from the Mapper only. When you load a design, the Timing Analyzer also loads the default PCF file if it is present. The default PCF file is the physical constraints file with the same name and located in the same directory as the NCD file. You can load a different PCF file after the design is loaded. The order of the timing constraints in the PCF file is reflected in the Timing Analyzer reports. CPLD physical constraints information is contained in the VM6 file itself.

### **Architectures**

You can use the Timing Analyzer with the following Xilinx devices:

- Spartan<sup>™</sup>/XL/-II

- Virtex<sup>TM</sup>/-E/-II

- XC9500<sup>TM</sup>/XL/XV

- XC4000<sup>TM</sup>E/L/EX/XL/XV/XLA

- XC3000™A/L

- XC3100™A/L

- XC5200™

### **Features**

The Timing Analyzer offers the following interface, report, filters, macro, and analysis interrupt features.

### Interface

You can issue Timing Analyzer commands from the menus, toolbar, or Console window. You can also activate commands by running macros. The instructions in this user guide use only the menu commands or toolbar buttons. The equivalent command-line syntax is provided in the Timing Analyzer Online Help.

### Reports

The Timing Analyzer can create the following reports.

- Timing Constraints Analysis report compares design performance to the timing constraints.

- Analyze Against Auto Generated Design Constraints Analysis

report displays the results of analyzing the constraints specified

in the constraints file for FPGAs. If no constraints are specified,

this report displays the maximum clock frequencies for all clocks

in the design and the worst-case timing for all clock paths. For

CPLDs, it displays all external synchronous path delays which

include: pad-to-pad (tPD), clock pad-to-output pad (tCO), setupto-clock-at-the-pad (tSU), and internal clock-to-setup (tCYC)

paths.

- Analyze Against User Specified Paths by Defining Endpoint Analysis report contains a detailed analysis of all specified paths and includes the worst-case path delays for all paths in the design. You can filter this report.

- Analyze Against User Specified Paths by Defining Clock and IO report generates the analysis report, for user specified Period, Timegroups of Pads, Offset in before constraints, and Offset out after constraints.

- Clocks report lists the names of all clocks in the design.

- Settings report lists the current settings set with commands in the Path Filters and Options menus.

- Query Nets report displays net delay information. (FPGA only)

- Query TimeGroups displays time group information. (FPGA only)

### **Path Filtering Commands**

You can customize Timing Analyzer reports by specifying filters in the Filter Paths by Net tab accessed through the commands in the Analyze menu. The Reset Path Filters command resets the path filters to default settings. The Filter Paths by Net tab is included in all Analyze Against dialog boxes which have the following functionality:

- Analyze Against Timing Constraint Filters commands affect only the Timing Constraints Analysis and Analyze Against Auto Generated Design Constraints reports.

- Analyze Against User Specified Paths by Defining Endpoint

Filters commands deal with specific paths whose starting points

and ending points you can define. These commands apply to the

Analyze Against User Specified Paths by Defining Endpoint

reports.

- Common Filters commands exclude or include paths with specific nets and control path tracing. These commands apply to the Analyze Against Timing Constraints Analysis, Analyze Against Auto Generated Design Constraints Analysis, Analyze Gaussian User Specified Paths by Defining Endpoint Analysis and Gaussian User Specified Paths by Defining Clock and IO Timing Analysis reports.

### **Macros**

You can create macros that execute multiple Timing Analyzer commands in one step. Macros are script files for running Timing Analyzer commands and options. The Console window records all the commands that you execute in any Timing Analyzer session. After entering the desired series of commands in this window, you can copy and paste the sequence into a macro document, save the macro document, and run it.

### **Analysis Interrupt**

The commands in the Analyze menu have an interrupt function when analyzing FPGA designs. A Timing Analysis in Progress dialog box with an Abort button appears. Clicking the button, the Esc key, or the Enter/Return key stops analysis. A report is not generated or displayed.

# **Online Help**

The Timing Analyzer offers both context-sensitive help and a Help menu. See the "Obtaining Help" section of the "Getting Started" chapter for more information on the online help and instructions for accessing it.

# Chapter 2

# **Getting Started**

This chapter describes starting and exiting the Timing Analyzer, using menus, buttons, Console windows, dialog boxes, and online help. It contains these sections.

- "Starting the Timing Analyzer"

- "Timing Analyzer Window"

- "Console Window"

- "Dialog Boxes"

- "Basic Timing Analysis Procedure"

- "Obtaining Help"

- "Exiting the Timing Analyzer"

# **Starting the Timing Analyzer**

The Timing Analyzer runs on PCs and workstations. On the PC, the graphical user interface is based on Microsoft Windows. On the workstation, the interface is based on OSF Motif.

You can start the Timing Analyzer from the Windows Program Manager, the Xilinx Design Manager, or the command line.

### From the Design Manager

To start the Timing Analyzer from the Design Manager window (PC or workstation), click on the Timing Analyzer icon (shown in the following figure) or select  $\mathtt{Tools} \rightarrow \mathtt{Timing}$  Analyzer.

### Stand-Alone Tool

If you installed the Timing Analyzer as a stand-alone tool on a PC, click on the Timing Analyzer icon (shown in the previous figure) on the Windows desktop or select timingan.exe from the Windows 95 or Windows NT Start button.

### From the Command Line

To start the Timing Analyzer from a UNIX command line, type the following command.

#### timingan

These are a number of variations for starting the Timing Analyzer from the command line.

• To run the tool as a background process, end the command with an ampersand (&).

#### timingan &

To start the Timing Analyzer and open an existing FPGA or CPLD design, type the following.

```

timingan {design_name.ncd|design_name.vm6}

```

For FPGA designs, if a physical constraints file (PCF) exists in the same directory as the design and has the same name, except for the extension, that design\_name.pcf file is automatically opened.

• To start the tool, open an existing FPGA design and the corresponding physical constraints file, type the following. Physical constraints files only apply to FPGAs.

```

timingan design_name.ncd -pcfpcf_file_name.pcf

```

Use the -run option followed by a macro file name to run a macro. If a design and PCF file are specified on the command line also, the macro is run after the design and PCF file are loaded. The macro may contain an Exit command. timingan design\_name.ncd -pcfpcf\_file\_name.pcf

-run macro name

To start the tool and open a Timing Analyzer report in a Hierarchical Report viewing window, type the following.

timingan filname.twr

• To start the tool and open a Timing Analyzer report in a text editor window, type the following.

timingan filname

• To unload a default PCF file, use the -nopcf option.

## **Timing Analyzer Window**

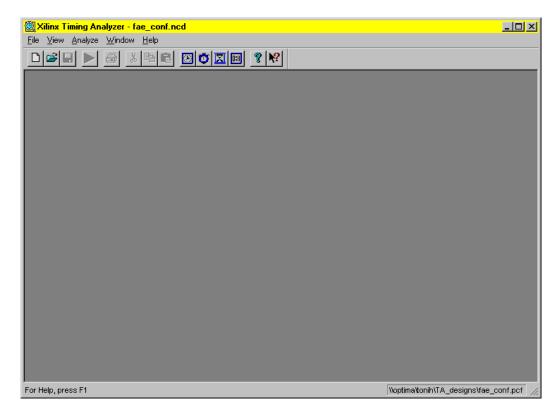

This section describes the Timing Analyzer's main window, menus, toolbar, and status bar. You can execute Timing Analyzer commands from the menus, toolbar, or the Console Window.

When you start the application, the Timing Analyzer window appears. The window contains pull-down menus, a toolbar at the top of the window, and a status bar at the bottom of the window. The menus are described in the "Menus" section.

**Note** The Edit menu is only enabled when a design, report, or macro file is open and is the active window. Also, most of the toolbar buttons are not enabled unless a file is open and active.

Figure 2-1 Timing Analyzer Window

The toolbar and status bar appear by default when you start the Timing Analyzer. You can hide them from view by selecting the Toolbar or the Status Bar commands, respectively, from the View menu.

### Menus

Most of the Timing Analyzer commands are available in the pull-down menus. However, unless a design is loaded, most of the commands are disabled and not available. Certain commands and some command options are disabled and not available, depending whether the open design is an FPGA or a CPLD design.

You can select menu commands with the mouse or the keyboard. With the mouse, click the left mouse button on the desired command.

With the keyboard, press the Alt key and type in the letter underlined in the menu for that command. When you select a menu command with either method, a brief description of the command's function appears in the Status Bar at the bottom of the Timing Analyzer window.

For complete command descriptions, select  $\mathtt{Help} \to \mathtt{Help}$  Topics or see the Timing Analyzer on-line help for more information.

### **Toolbar**

The toolbar appears at the top of the window, just below the menu bar. The toolbar provides button access to frequently used commands in the menus. Textual labels for the buttons appear when you move the cursor arrow over a button. This feature is called a tool tip. A longer description also appears in the status bar. See the Timing Analyzer OnlineHelp for more information.

### Status Bar

By default, the status bar appears at the bottom of the window. When you select a menu command, a brief description of the command's function appears in the status bar. As the Timing Analyzer processes, status messages are dynamically updated and displayed.

To hide or show the status bar, select  $View \rightarrow Status$  Bar

### **Console Window**

The Console window displays the sequence of commands that you have used in a Timing Analyzer session. It is primarily used for creating macros, but it has a command line field, in which you can type and execute keyboard commands. The Console window also contains a Show Command Status box that you can click on to display or hide status messages. For information on creating and using macros, see the "Using Macros" section of the "Using the Timing Analyzer" chapter.

Commands that you can enter in the Console window are described in the Timing Analyzer Online Help.

You can open the Console window by selecting  $View \rightarrow Console$ .

## **Dialog Boxes**

Many Timing Analyzer menu commands display dialog boxes in which you can enter information and set options. This section describes dialog box common fields, tabs within the Analysis dialog boxes, and how to use filters.

### **Common Fields**

The fields shown in the following table are common to most dialog boxes.

**Table 2-1 Common Dialog Box Fields**

| Dialog Box Field | Function                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------|

| ОК               | Closes the dialog box and implements the intended action according to the settings in the dialog box |

| Cancel           | Closes the dialog box without effecting any action                                                   |

| Help             | Displays information on that particular dialog box                                                   |

# **Analysis Dialog Tabs**

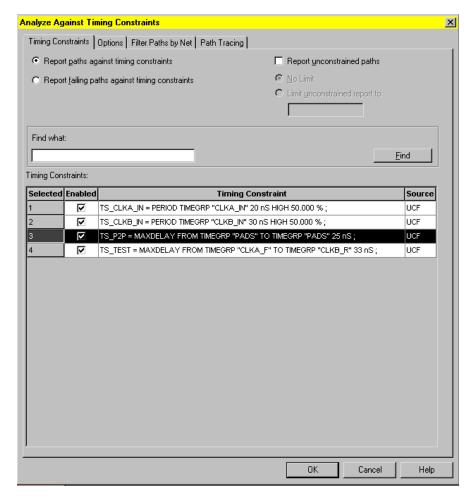

Many of the dialog boxes in the Timing Analyzer feature menu tabs with grid based selection items, such as Analyze Against Timing Constraints in the next figure. You can select the various tabs that include all the filter settings and options that apply to that type of analysis.

Figure 2-2 Tabs Within the Analyze Against Timing Constraints Dialog Box

### **Using Filters with Commands**

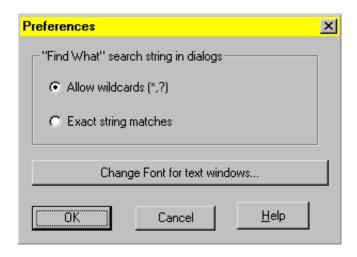

To use filters with commands select File →Preferences, the Preference dialog appears. The following figure displays an example of the Preferences dialog box. User can select the Allow Wildcards (8,?) or the Exact string matches radio buttons to set the Find What search strings in all tab dialogs.

Figure 2-3 Preferences Dialog Box

### **Valid Inputs and Wildcards**

In the find what (filter fields), you can enter a text string consisting of characters and wildcards.

- Characters can be any alphanumeric characters, text spaces, and the characters that appear on the top of the number keys on a keyboard. Alphabetic characters are case-sensitive. No control characters are permitted.

- A wildcard can be an asterisk (\*), which can represent any number of characters, or a question mark (?), which represents a single character.

You cannot enter a range of characters in filter fields.

# **Matching Text Strings**

The Timing Analyzer does not strictly match patterns; it matches entire text strings. It does not find a string if it is embedded in a larger string, unless you use wildcards. For example, it does not find \$1N36 if it is embedded in ABC\$1N36XYZ. However, if you searched for \*\$1N36\*, it would find that string in ABC\$1N36XYZ.

## **Basic Timing Analysis Procedure**

The typical procedure for using the Timing Analyzer is as follows.

- 1. Open the Timing Analyzer and load your design.

- For FPGAs, if a physical constraints file (PCF) with the same name as your design exists in the directory, the Timing Analyzer also loads that file, by default. (The PCF file is generated when a design is mapped.)

- 2. If you are unfamiliar with the Timing Analyzer, explore its features. You can use the online help facility to help you with this process. To run the online help, select  $\mathtt{Help} \to \mathtt{Help}$  Topics

- 3. You can optionally generate a report to obtain a basic overview of the design's timing before you begin to analyze it in detail. The Analyze Against Auto Generated Design Constraints Report provides that information. Choose the Analyze Against Auto Generated Design Constraints command from the Analyze menu to generate and display an Analyze Against Auto Generated Design Constraints Analysis report.

- 4. Select commands from the Analyze menu tabbed dialogs that include all the filter setting and options that apply to specify the kinds of reports you want to generate. These settings always appear when Analyze menus are chosen.

- 5. Select commands from the Edit menu to search or edit reports.

- 6. Select commands from the File menu to save or print reports.

- 7. Optionally, you can create macros comprising the commands just issued.

These steps are described in more detail in the "Using the Timing Analyzer" chapter.

## **Obtaining Help**

You can obtain help on the Timing Analyzer's commands and procedures by selecting commands in the Help menu, by selecting the Help button in the toolbar, by clicking the Help button in dialog boxes, or by pressing the F1 key. The Help button in the toolbar, the ones contained in some menu command dialog boxes, and the F1 key

provide context-sensitive help for what you click on or that dialog box, respectively.

### Help Menu

The Help menu contains the following commands.

- Help Topics lists the online help topics available for the Timing

Analyzer. From the opening screen, you can jump to command

information or step-by-step instructions for using the Timing

Analyzer. After you start the help, you can click the Contents

button (first button in the top-left corner) in the Help window

whenever you want to return to the help topics list.

- About Timing Analyzer displays a pop-up window that displays the version number of the Timing Analyzer software.

### **Context-Sensitive Help**

You can obtain context-sensitive help on the Timing Analyzer by using the Help button in the toolbar or the Help button contained in many of the menu command dialog boxes. This section describes both methods of how to access the context-sensitive help.

#### **Toolbar Button**

To access context-sensitive help from the toolbar, follow this procedure.

1. Click on the Help button from the toolbar, shown in the following figure.

The cursor changes to an arrow and question mark, like the button.

2. For help on menu commands, click (with the left mouse button) on the menu, then click the command in that menu or submenu. For help on toolbar buttons, click once on the particular button.

The Timing Analyzer displays information about the selected command or button.

### **Help Button in Dialog Boxes**

Many of the dialog boxes associated with Timing Analyzer menu commands have a Help button. You can click on the button to obtain help on that dialog box. A window opens with the information.

### F1 Key

Pressing the F1 key when the cursor is placed on a dialog box displays help for that dialog box.

## **Exiting the Timing Analyzer**

To exit the Timing Analyzer, click File  $\rightarrow$  Exit or type exit at the prompt in the Console window.

If you have unsaved reports open, a prompt box similar to that in the next figure appears.

Figure 2-4 Exit Prompt Box

Click Yes to save the report, then follow the procedure described in the "Saving a Report" section of the "Using the Timing Analyzer" chapter.

You are prompted for confirmation before exiting, even if there is no unsaved data. However, if SetForce is on, an Exit command in a macro causes the Timing Analyzer to exit without asking for confirmation.

# **Chapter 3**

# **Timing Analysis**

This chapter explains some of the concepts involved in static timing analysis and how to use the Timing Analyzer to resolve key analysis issues.

Xilinx software tools support two different methodologies of implementing timing analysis. For FPGAs, timing is analyzed through user-defined constraints specified with Timing Analyzer commands and filters. The commands in the Analyze → Against Timing Constraints Filter Tab help you customize your analysis. See the Commands section of the Timing Analyzer Online Help and the XILINX Software Conversion Guide from XACTstep v5.x.x to XACTstep vM1.x.x for more information. CPLDs use system-defined paths for timing analysis. These paths are selected with commands in the Analysis dialog tabs found in the Analyze menu. See the Commands section of the Timing Analyzer Online Help for more information on these commands.

This chapter contains these main sections.

- "Basic Path Types"

- "Design Analysis Issues"

## **Basic Path Types**

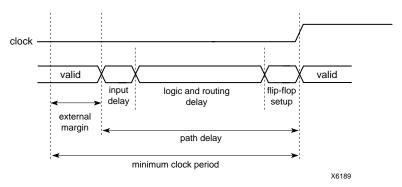

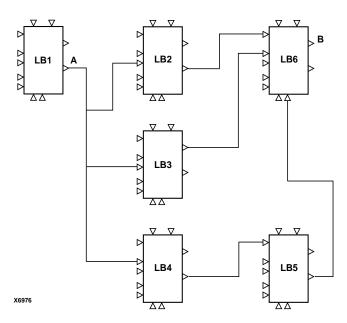

After you implement your design, you can use the Timing Analyzer to calculate your design's system performance, which is limited by seven basic types of timing paths. Each of these paths goes through a sequence of routing and logic. Because these path delays are affected by the results of the placement and routing that implement the design connectivity, these sequences can vary.

Before you read the Timing Analyzer reports, read the following sections for a description of the basic path types.

### Clock to Setup

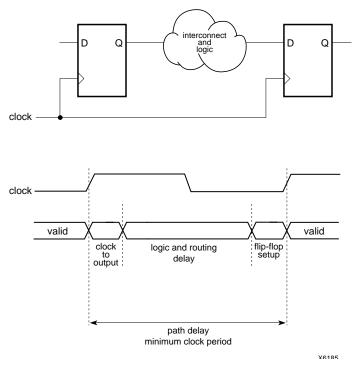

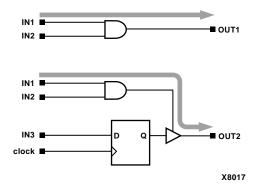

A clock-to-setup path starts at flip-flop clock inputs and ends at non-clock flip-flop register inputs, D or T, or the receiving flip-flop's tSU, where that pin has a setup requirement before a clocking signal. Along the way, it propagates through the flip-flop Q output and any number of levels of combinatorial logic. It includes the clock-to-Q delay of a flip-flop, the path delay from that flip-flop to the next flip-flop, and the setup requirement of the next flip-flop.

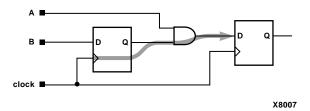

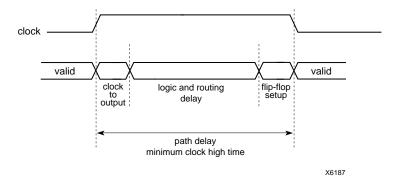

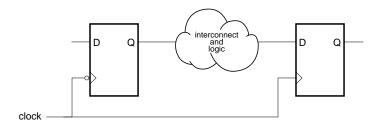

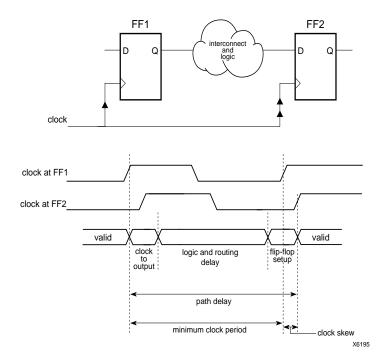

The clock-to-setup path time is the maximum time required for the data to propagate through the source flip-flop, travel through the logic and routing, and arrive at the destination before the next clock edge occurs. When these flip-flops are clocked by the same clock, the delay on this path is equivalent to the cycle time of the clock. The following figures show a clock-to-setup path which uses the same clock. Figure 3-2 also shows a timing diagram describing the path.

Figure 3-1 Clock-to-Setup Path

Figure 3-2 Clock-to-Setup Path (Same Clock) with Timing Diagram

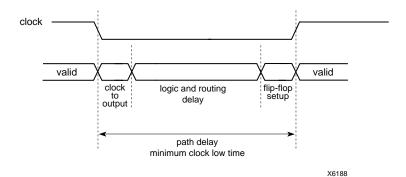

Source and destination flip-flops can be clocked by the same clock on different clock edges. In these cases, the path delay limits the minimum clock high or clock low time as shown in the following two figures.

Figure 3-3 Clock-to-Setup Path (Rising to Falling Edge)

Figure 3-4 Clock-to-Setup Path (Falling to Rising Edge)

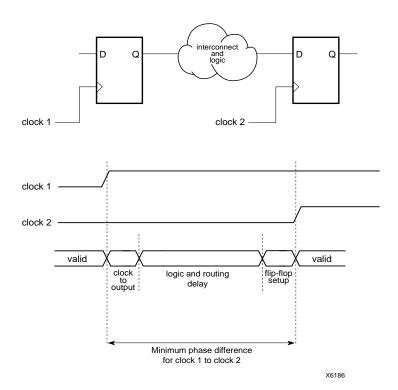

If the source and destination are clocked by different clock nets, the clock net on the destination must have a clock period greater than the path delay. The PERIOD constraints allow the Timing Analyzer to use the target flip-flop period for the delay path value. The following figure shows a path of this type.

Figure 3-5 Clock-to-Setup Path (Different Clocks)

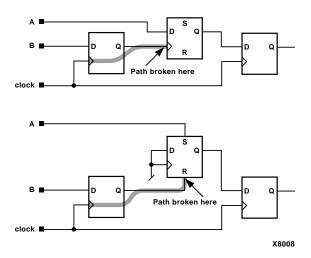

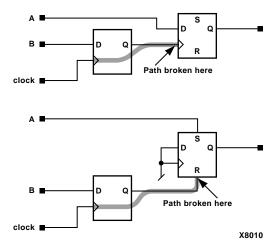

Clock-to-setup paths do not propagate from the flip-flop Q output through another flip-flop clock or asynchronous Set and Reset input as shown in the next figure. These paths are also broken at bidirectional pins.

Figure 3-6 Not Propagating Through Asynchronous Set/Reset

#### Clock to Pad

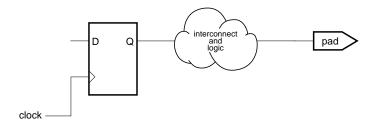

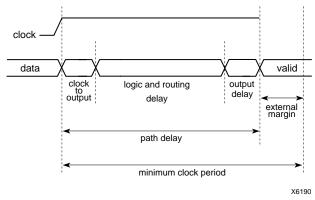

A clock-to-pad path starts at a clock input of a flip-flop, propagates through the flip-flop Q output and any number of levels of combinatorial logic, and ends at an output pad. It includes the clock-to-Q delay of the flip-flop and the path delay from that flip-flop to the chip output. The clock-to-pad path time is the maximum time required for the data to leave the source flip-flop, travel through logic and routing, and leave the chip. When using the OFFSET constraint, the clock path is also used in the path delay. The following figure illustrates a clock-to-pad path, along with a timing diagram describing the path.

Figure 3-7 Clock-to-Pad Path

Clock-to-pad paths also trace through the enable inputs of tristate controlled pads, as shown in the next figure.

Figure 3-8 Through Tristate Controlled Pads

Clock-to-pad paths do not propagate from the Q output of a flip-flop through the clock of another flip-flop or asynchronous Set and Reset input as shown in the following figure. These paths are also broken at bidirectional pins.

Figure 3-9 Clock-to-Pad Path Broken Through Set/Reset Inputs

## Paths Ending at Clock Pin of Flip-Flops

A clock input path starts at a chip input or output. It propagates through any number of levels of combinatorial logic and ends at any clock pin on a flip-flip or latch enable. These paths do not propagate through flip-flops. The clock input path time is the maximum time required for the signal to arrive at the flip-flop clock input. Clock input paths help to determine system-level design timing.

The clock input time is the maximum time only; the Timing Analyzer currently does not calculate minimum clock times.

The next figure shows a clock input path.

Figure 3-10 Paths Ending at Clock Pin of Flip-Flops

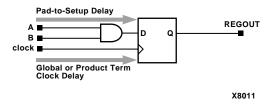

#### Setup to Clock at the Pad

A setup-to-clock-at-the-pad path starts at an input pad, propagates through input buffers and any number of levels of combinatorial logic, and ends at a flip-flop D/T input, which includes the receiving flip-flop's tSU. This path does not propagate through flip-flops and is also broken at bidirectional pins.

This delay reports tSU for data inputs relative to global or product term clock inputs. It is calculated according to the following formula for global and product term clocks.

```

tSU = Pad to Setup - Path Ending at Clock Pin of Flip-Flop

```

Global clock paths start at global clock pads, propagate through global clock buffers and end at a flip-flop clock pin. Product term clock paths start at input pads, propagate through a single level of logic implemented in a clock product term, and end at the flip-flop clock pin. All three clock-at-the-pad paths are shown in the next figure.

Figure 3-11 Setup-to-Clock-at-the-Pad Path

## **Clock Pad to Output Pad**

A clock-pad-to-output-pad path starts at input pads and trace through all paths that include a flip-flop clock input (except when that path includes a flip-flop asynchronous Set/Reset input) before ending at an output pad. Clock-pad-to-output-pad paths trace through tristate controlled pad enable inputs.

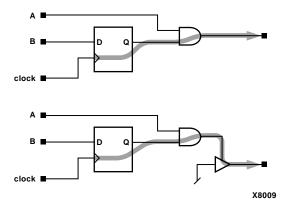

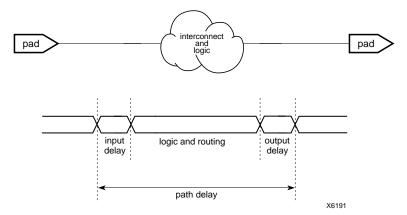

#### Pad to Pad

A pad-to-pad path starts at an input pad of the chip, propagates through one or more levels of combinatorial logic, and ends at an output pad of the chip. Combinatorial paths also trace through the enable inputs of tristate controlled pads. The pad-to-pad path time is the maximum time required for the data to enter the chip, travel through logic and routing, and leave the chip. It is not controlled or affected by any clock signal. A pad-to-pad path, along with a timing diagram describing the path is displayed in the following figure.

Figure 3-12 Pad-to-Pad Delay

Combinatorial paths are not traced through flip-flops. These paths are also broken at bidirectional pins. A second representation is shown in the next figure.

Figure 3-13 Pad-to-Pad Path

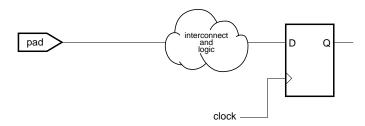

## Pad to Setup

A pad-to-setup path starts at an input pad of the chip and ends at a D/T input to a flip-flop, latch, RAM, or the receiving flip-flop's tSU, wherever there is a setup time against a control signal. Along the way, it propagates through input buffers and any number of combinatorial logic levels. Pad-to-setup paths do not propagate through flip-flops and are broken at bidirectional pins. The pad-to-setup path time is the maximum time required for the data to enter the chip,

travel through logic and routing, and arrive at the output before the clock or control signal arrives. A pad-to-setup path and timing diagram is shown in the following figure.

Figure 3-14 Pad-to-Setup Path

# **Design Analysis Issues**

The Timing Analyzer can help you resolve some of the most frequently encountered design problems. This section describes common problems and solutions.

## Feedback Loops

Asynchronous feedback paths in a design can cause many paths to be reported that may not actually be timing problems. The most common cases are feedback paths through asynchronous Set or Reset to banks of flip-flops, like a state machine or a counter. Another example is the construction of latches from function generators, which are built using asynchronous feedback paths.

To exclude specific nets that create feedback paths, such as an illegalstate Reset logic loop for a state machine, you can use the Exclude Paths with Nets command to exclude any paths that contain those nets from the timing report.

With the Control Path Tracing command, you can control some asynchronous points through logic; for example, you can exclude the asynchronous Reset of a flip-flop or TBUF input to output.

## **Timing Constraints**

If you entered timing constraints before compiling your design with the mapper, you can use the Timing Analyzer to verify whether your constraints were met. The following example of portions of a Timing Analysis report shows how the Timing Analyzer finds paths that did not meet timing constraints; five errors occurred and three constraints were not met.

\_\_\_\_\_\_

```

To

Delay type Delay(ns)

Physical Resource

Logical Resource(s)

CLB.XQ

Tcko

1.830R

$1N11

$1N11

CLB.F2

net (fanout=2) e 0.380R

$1N11

CLB.K

Tick

1.130R

$1N11

$1N15

$1N11

Total (2.960ns logic, 0.380ns route) 3.340ns

(to $1N19)

(88.6% logic, 11.4% route)

3 constraints not met.

```

```

Data Sheet report:

All values displayed in nanoseconds (ns)

Setup/Hold to clock ck1_i

----+

Setup to | Hold to |

Source Pad | clk (edge) | clk (edge) |

----+

res_i | 6.202(R)|

start_i | 2.213(R) | 0.000(R) |

----+

Table of Timegroups:

_____

TimeGroup PADS:

BELs:

OUT D C CLR

```

```

TimeGroup FFS:

BELs:

$1N11

Timing summary:

______

Timing errors: 5 Score: 15874

Constraints cover 5 paths, 0 nets, and 5

connections (100.0% coverage)

Design statistics:

Maximum path delay from/to any node: 10.716ns

Analysis completed Wed Feb 24 14:29:35 1999

```

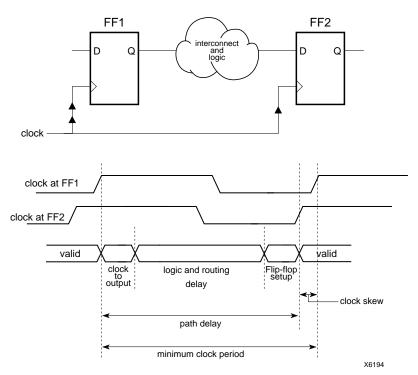

#### **Clock Skew**

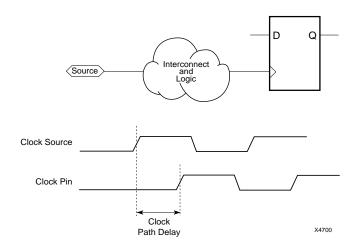

The Timing Analyzer can report clock skew, which is the difference between the time a clock signal arrives at the source flip-flop in a path and the time it arrives at the destination flip-flop on the same clock net. Clock skew occurs most often when global routing is not used to route clock nets, because other routing is less predictable. The arrival of clock signals at different times can affect the required clock period. This section describes negative and positive clock skew and how the Timing Analyzer reports clock skew.

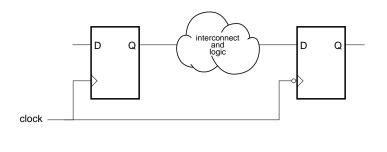

#### **Negative Clock Skew**

When the destination is clocked before the source, the clock skew is called negative clock skew. Negative clock skew means that the clock period must be longer than the path delay plus the amount of clock skew between the flip-flops. Negative clock skew is illustrated in the next figure.

Figure 3-15 Negative Clock Skew

#### Positive Clock Skew

When the source is clocked first, the clock skew is called positive clock skew. Positive clock skew means that the clock period could be shorter than the path delay by the minimum amount of clock skew. The Timing Analyzer does not account for positive clock skew; it truncates positive clock skew to zero. Positive clock skew is illustrated in the following figure.

Figure 3-16 Positive Clock Skew

#### **During Timing Analysis**

The Timing Analyzer uses the timing constraints specified in the Physical Constraints File (FPGAs) or the VM6 design file (CPLD); it does not infer extra timing constraints. The Timing Analyzer accounts for clock skew for all register to register paths. The following example shows the clock skew portion of a Analyze Against Timing Constraints Analysis report.

S

lack: 12.667ns path SOURCE to DEST relative to

- 4.633ns total path delay

- -2.300ns clock skew

15.000ns delay constraint

Path SOURCE to DEST contains 2 levels of logic:

Path starting from Comp: CLB\_R14C13.K (from SIG CLK)

To Delay type Delay(ns)

Physical Resource

Logical Resource(s)

-----

-----

CLB\_R14C13.YQ Tcko 2.090R SOURCE

BEL\_SOURCE.FFY

CLB\_R14C14.C4 net (fanout=1) 1.533R

DATA\_SRC\_DST

CLB\_R14C14.K Tdick 1.010R DEST

BEL DEST.FFY

\_\_\_\_\_

Total (3.100ns logic, 1.533ns route) 4.633ns (to SIG\_CLK)

(66.9% logic, 33.1% route)

You can use Analyze → Query Nets to generate a Query Nets report to display the clock skew across specific clock nets. See the "Querying for Information" section of the "Using the Timing Analyzer" chapter for the procedure to generate a Query Nets Report, an example of a Query Nets Report, and information on the report format.

## Off-Chip Delay

To determine system-level clock speed, you must add any external delay to paths that travel off-chip. This way, the Timing Analyzer includes this external delay when calculating the delay for the path. There is no default delay; the Timing Analyzer does not add off-chip delay unless you specify it. See the *XILINX Software Conversion Guide from XACTstep v5.x.x to XACTstep vM!.x.x* for information on how to specify these delays with the OFFSET constraint in the UCF (User Constraints File) file.

# Chapter 4

# **Using the Timing Analyzer**

This chapter describes the various functions you can perform with the Timing Analyzer. It contains the following main sections.

- "Opening a Design"

- "Apply Physical Constraints Files"

- "Viewing Settings"

- "Viewing Clocks"

- "Querying for Information"

- "Creating Reports"

- "Specifying Report Appearance and Content"

- "Changing the Speed Grade"

- "Using Path Filtering Commands"

- "Using the Console Window"

- "Using Macros"

**Note** The commands and dialog boxes in this chapter are used in the context of procedures, but they are not explained in detail. For a detailed explanation of them, see the Timing Analyzer Online Help Menu Commands.

# **Opening a Design**

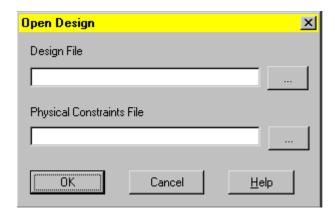

Before you can create a timing report using the Timing Analyzer, load a mapped NCD (FPGA) or a completed placed and routed VM6 (CPLD) design file. The NCD (FPGA) can be mapped, placed, or routed. To open a design for timing analysis, follow these steps.

1. Select File  $\rightarrow$  Open Design, or click on the Open Design toolbar button.

The Open Design dialog box appears, as shown in the following figure.

- 2. You can also enter a file name in the Physical Constraints File Field or use the Browse button to select a PCF file. If you do not enter a constraints file, Timing Analyzer looks for a physical constraints file with the same name as the design file, but with a .pcf extension

- 3. The Open dialog box appears.

- 4. The In the Look in/Directories list box, click on the directory containing the NCD (FPGA) or VM6 (CPLD) file to load.

- 5. Under Files of Type/List Files of Type, click on the pull-down the list box and select FPGA Designs (\*.ncd) or CPLD Designs (\*.vm6).

- All the available NCD or VM6 files are displayed in the list box.

- 6. Select an NCD or a VM6 file from the list box, or type the name in the field below File Name. (\*.ncd appears by default; backspace over the asterisk before typing in the design file name.)

#### Click OK.

The Timing Analyzer reads your design and device information, processes any timing constraints, and then loads your design. For FPGA designs, the Timing Analyzer also reads the .pcf physical constraints file with the same name as the design file, if one exists in the same directory as the design file (the PCF file contains physical constraints information). The order of the constraints in the PCF file is reflected by the Timing Analyzer.

When your design is loaded, the path name and design file name appear at the top of the Timing Analyzer window.

You can now create a timing report. Refer to the "Creating Reports" section for instructions on this procedure.

## **Warning**

If you open a design when another design is open, the Timing Analyzer resets the current settings to the defaults. If you re-open a design that is already open, the Timing Analyzer also resets the current settings to the defaults and opens the default PCF, if it exists.

# **Apply Physical Constraints Files**

Physical Constraints Files (PCF) contain physical constraint information. They apply only to FPGAs, because CPLD timing information is contained in the (VM6) design file itself. The order of the timing constraints in the PCF file is reflected by the Timing Analyzer. This section describes methods for loading and opening Physical Constraints Files.

#### Manually Opening a Physical Constraints File

If you already have a design open and wish to load a different Physical Constraints File for use with the current design, follow these steps.

- 1. Select File  $\rightarrow$  Apply Physical Constraints. The Open Physical Constraints dialog box appears.

- 2. In the Look in/Directories list box, click on the directory containing the PCF file to load.

- 3. Under Files of Type/List Files of Type, Physical Constraints (\*.pcf) is the default and the only file type you can select.

- All the available PCF files are displayed in the list box.

- 4. Select a PCF file from the list box, or type the name in the field below File name. (\*.pcf appears by default; backspace over the asterisk before typing in the physical constraints file name.)

- 5. Click ox.

The Timing Analyzer reads the PCF file and the path name appears on the right side of the status bar at the bottom of the Timing Analyzer window.

## Viewing a Physical Constraints File

In some cases you may want to open a PCF file for viewing from within the Timing Analyzer. When you open a PCF file by this method, the Timing Analyzer does not load the PCF file for use with the current design. It just opens the file for viewing but does not replace the PCF file that is loaded for use with the current design. To open a PCF file in this way, follow these steps.

- Select File → Open →Physical Constraints File.

The Open Physical Constraints dialog box appears.

- 2. Under Files of Type/List Files of Type, select All Files (\*.\*).

- 3. Select a PCF file from the list box, or type it in the field below File Name.

- 4. Click ok.

The PCF file is displayed in a window but the path name on the right side of the status bar at the bottom of the Timing Analyzer window does not change since opening a PCF file by this method does not load the PCF file for processing with the current design.

## **Viewing Settings**

4-4

To view current Timing Analyzer settings, select  $\forall iew \rightarrow Settings$ .

The Timing Analyzer displays a pop-up window with the current settings and options. The following figure displays an example of the Settings window.

```

Settings

Settings

Design: H:\TA_designs\fae_conf.ncd

# Physical Constraints File: H:\TA_designs\fae_conf.pcf

# Generated: Fri Mar 03 17:23:14 2000

# Release 3.1i - Timing Analyzer D.18

OpenPCF \\optima\tonih\TA_designs\fae_conf.pcf

Speed -4

DoHoldRaceCheck False

IncludeNets

ExcludeNets

SelectFailingTimingConstraint False

IncludeNoTimingConstraint False

Report Normal

MaxPathsPerTimingConstraint 1

DefineEndpoints ToAll

DefineEndpoints FromAll

OmitUserConstraints False

```

#### Figure 4-1 Settings Window

When this window is the active window and you change an option setting or a path filter, the change is immediately reflected in the window. If it is not the active window and you change an option or a filter, you must click inside the Settings window to update it automatically.

The contents of the window can be saved as an .xtm file to save the settings as a macro to return the system to the same state as when the settings were saved. See the "Saving a New Macro" and the "Running a Macro" sections for more information. You can also save the contents of the window to a .twr file. TWR files are listed as Timing Analysis Reports (\*.twr) under List Files of Type in File menu command dialog boxes. See the "Saving a Report" section for the procedure to save a report.

# **Viewing Clocks**

The Clocks report lists the names of all of the clocks in the design. To generate a Clocks report, select  $\mathtt{View} \to \mathtt{Clocks}$ . The Timing Analyzer displays the Clocks report in a pop-up window. You can save the contents of the window as a (.twr) file. TWR files are listed as Timing Analysis Reports (\*.twr) under List Files of Type in File menu command dialog boxes. See the "Saving a Report" section for the procedure to save a report.

# **Querying for Information**

You may want to focus on the source, destination, and timing of a particular net or time group. You can obtain information about the timing of particular nets or the members of a time group using the Query commands. These commands only applies to FPGAs; it is disabled if a CPLD design is open.

To perform a query, follow this procedure.

1. Select Analyze  $\rightarrow$  Query Nets or Analyze  $\rightarrow$  Query Timegroups.

The Query Nets or Query Timegroups dialog box appears depending on your selection.

- 2. The following information is generated for each option.

- Nets The Timing Analyzer shows the fanout, the timing from the source CLB to each of the destination CLBs, and the CLB names in the generated Query Nets Report.

- TimeGroups The Timing Analyzer lists the elements in the specified timing groups in the generated Query TimeGroups Report.

- 3. If you select Nets, enter a value in the Delay Greater Than field of the Filter for Available Nets.

- The Delay Greater Than value specifies a minimum net delay in nanoseconds. The Timing Analyzer displays only those paths that have a delay greater than or equal to the specified value.

- 4. Enter a filter in the other portion of the Filter for Available Nets/TimeGroups section, if desired, and click Apply.

If you enter a value in the Delay Greater Than and a filter in the filter field, the Timing Analyzer lists the nets that meet both criteria.

5. Select the nets or timing groups that you want to query from the Available Nets/TimeGroups list box and move specific ones or all of them to the Selected Nets/TimeGroups list box.

See the "Common Fields" section of the "Getting Started" chapter for details on selecting and moving items between list boxes.

#### 6. Click OK.

The Timing Analyzer displays the Query Nets/TimeGroups Report in a pop-up window, which can be saved as a TWR file. Nets/TimeGroups is Nets or TimeGroups, corresponding with your dialog box selection in step 1. See the "Saving a Report" section for the procedure to save a report.

## **Query Nets Report**

The following is an example of Query Nets Report.

| M | \$1N15 | \$1137.0 | 4.0  | \$1N6.F4     |

|---|--------|----------|------|--------------|

|   |        | \$114    | 45.0 | 4.0 \$1N6.F4 |

|   | \$1N32 | C.I2     | 2.0  | \$1I45.T     |

|   |        |          | 2.0  | \$1N6.F3     |

|   | \$1N34 | D.I2     | 1.0  | \$1N6.F1     |

|   | \$1N6  | \$1N6.X  | 1.0  | 01.0         |

|   |        |          | 1.0  | 02.0         |

|   | \$1N51 | A1.I2    | 0.0  | \$1145.1     |

|   | \$1N38 | B.I2     | 2.0  | \$1I37.T     |

|   | \$1N41 | A.I2     | 2.0  | \$1I37.I     |

The contents of the Query Nets Report example have been placed in the following table to illustrate the format of the report. Connections are listed by net, then by source; each is only listed once. Explanations of the information in Net Characteristics and Delay columns follow the table.

**Table 4-1 Query Nets Report Format**

| Net<br>Characteristics | Net Name | Driver Pin<br>Name | Delay Value | Load Pin Name |

|------------------------|----------|--------------------|-------------|---------------|

| M                      | \$1N15   | \$1I37.O           | 4.0         | \$1N6.F4      |

|                        |          | \$1I45.O           | 4.0         | \$1N6.F4      |

|                        | \$1N32   | C.I2               | 2.0         | \$1I45.T      |

|                        |          |                    | 2.0         | \$1N6.F3      |

|                        | \$1N34   | D.I2               | 1.0         | \$1N6.F1      |

|                        | \$1N6    | \$1N6.X            | 1.0         | 01.0          |

|                        |          |                    | 1.0         | O2.O          |

|                        | \$1N51   | A1.I2              | 0.0         | \$1I45.I      |

|                        | \$1N38   | B.I2               | 2.0         | \$1I37.T      |

|                        | \$1N41   | A-I2               | 2.0         | \$1I37.I      |

#### **Net Characteristics**

The entries in the Net Characteristics column are comprised of three characters. The characters indicate aspects of the net(s) you query. Each character position is independent of the others. The character position and values of each position are illustrated in this table.

| Left = Net Source    | Middle = Net Load | Right = If Critical                                                         |

|----------------------|-------------------|-----------------------------------------------------------------------------|

| S = No Source        |                   | $C = Net marked with CRITICAL property in the design or Net PRI is \geq 10$ |

| M = Multiple Sources |                   | - = Not Critical                                                            |

#### **Delay Value**

The entries in the Delay Value column can include asterisks (\*), question marks (?), or tildes ( $\sim$ ).

• The pin is unrouted or one or both pins are not yet placed if three asterisks (\*\*\*) appear as the delay value. An asterisk preceding a

number, \*3 for example, indicates the connection delay is estimated, if timing analysis is performed on an unrouted design. Because the Timing Analyzer can perform timing analysis on mapped FPGA designs, generating a Query Nets report can determine if a design does not meet timing requirements before a design is routed.

- A question mark (?) indicates the net was routed incorrectly.

- A tilde (~) preceding a delay value indicates that the delay value is approximate. The delay can be longer than estimated.

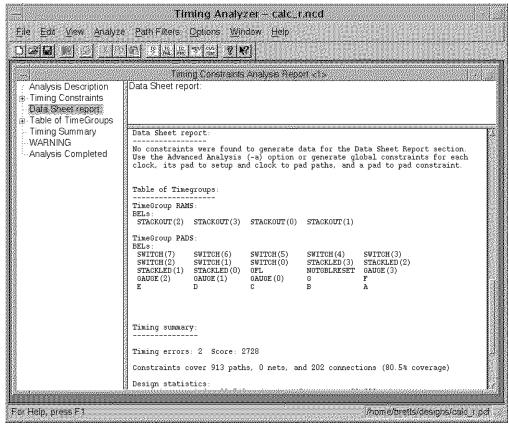

#### **Query Time Groups Report**

The Query Time Groups report lists the contents of each time group that you select. Time group information is also generated in the Timing Constraints Analysis report.

# **Creating Reports**

After you load a design file, you can decide what kind of report you want to generate. This section describes how to create all the reports available in the Timing Analyzer as well as how to save and print them.

With the Find command on the Edit menu, you can search for specific text strings in reports. Directions for this procedure are given in the "Searching for Text in a Report" section.

The Timing Analyzer has default settings that you can change using filters with various commands. Filters modify the scope of generated reports by specifying which paths you want to analyze. For more information, refer to the "Using Path Filtering Commands" section. To view the current settings, refer to the "Viewing Settings" section.

# **Timing Constraints Analysis**

The Timing Constraints Analysis report compares the design's performance to the timing constraints.

There are several ways to generate a Timing Constraints Analysis report. You can use the following toolbar button to generate a Timing Constraints Analysis report.

In addition to the button the Analyze → Against Timing Constraints dialog box includes the Timing Constraints tab that contains the following radio button options.

- Report paths against timing constraints

- Report failing paths against timing constraints

To generate a Timing Constraints Analysis report, select one of the previous options.

This command has an interrupt function when analyzing FPGA designs. A Timing Analysis in Progress dialog box with an Abort button appears.

Clicking the Abort button, the Esc key, or the Enter/Return key aborts the analysis and no report is generated or displayed.

In addition to using the above commands, you can use the following path filter options commands to modify the Timing Constraints Analysis report (See "Using Path Filtering Commands" section of the "Using the Timing Analyzer" chapter for more details).

- Disable Timing Constraints (Timing Constraints tab)

- Include Paths with Nets (Filter Paths by Net tab)

- Exclude Paths with Nets (Filter Paths by Net tab)

After processing the design, the Timing Analyzer displays the Timing Constraints Analysis report in a pop-up window. The contents of the window can be saved as a TWR file; see the "Saving a Report" section for the procedure to save a report. Following is an example of a Timing Constraints Analysis report.

```

Timing Analyzer 2.1i

Copyright (c) 1995-1999 Xilinx, Inc. All rights reserved.

Design file:

testclk.ncd

Physical constraint file: testclk.pcf

Device, speed:

xcv100,-5 (x1_0.71 1.76 Advanced)

Report level:

verbose report, limited to 1 item per

constraint

______

Timing constraint: TS ckl i = PERIOD TIMEGRP "ckl i" 20 nS

HIGH 50.000 %;

955 items analyzed, 0 timing errors detected.

Minimum period is 14.655ns.

Slack: 5.345ns path core_inst1/counter1/cont<1> to core_inst1/

counter1/cont<9> relative to

20.000ns delay constraint

Path core inst1/counter1/cont<1> to core inst1/counter1/cont<9>

contains 12 levels of logic:

Path starting from Comp: CLB_R10C8.S0.CLK (from ck1)

To

Delay type

Delay(ns) Physical Resource

Logical Resource(s)

CLB_R10C8.S0.YQ Tcko

1.203R core inst1/counter1/

cont<1>

core inst1/

counter1/

cont reg<1>

CLB_R11C10.S0.G1 net (fanout=5) 3.073R core_inst1/

counter1/

cont<1>

CLB_R11C10.S0.COUT Topcyg

1.545R core_inst1/counter1/

C9/

C3/C1/O C369

```

```

core_inst1/

counter1/

C9/C3/C1

CLB_R9C10.S1.F1 net (fanout=1) 1.491R core_inst1/

counter1/

N362

CLB_R9C10.S1.CLK Tas

1.043R core_inst1/counter1/

cont<9>

C303

core inst1/

counter1/

cont reg<9>

_____

Total (6.638ns logic, 8.017ns route) 14.655ns (to ck1)

(45.3% logic, 54.7% route)

All constraints were met.

Data Sheet report:

_____

All values displayed in nanoseconds (ns)

Setup/Hold to clock ckl_i

-----+

Setup to | Hold to |

Source Pad | clk (edge) | clk (edge) |

res i

6.202(R)

2.213(R) | 0.000(R) |

-----+

Setup/Hold to clock ck2 i

-----+

| Setup to | Hold to |

```

| Source Pad                                                                                                                         | •                   |          |                        |          |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|------------------------|----------|--|--|--|--|

| res_i                                                                                                                              | 5.861               | (R)      | <del>-</del><br> <br>+ |          |  |  |  |  |

| Clock ckl_i to Pad                                                                                                                 |                     |          |                        |          |  |  |  |  |

| Destination Pad                                                                                                                    | clk (edge<br>to PAD |          |                        |          |  |  |  |  |

|                                                                                                                                    | 16.691(<br>+        |          |                        |          |  |  |  |  |

| Clock ck2_i to Pad                                                                                                                 |                     |          |                        |          |  |  |  |  |

| clk (edge)   Destination Pad                                                                                                       |                     |          |                        |          |  |  |  |  |

| out2_o                                                                                                                             | out2_o              |          |                        |          |  |  |  |  |

| Clock to Setup on destination clock ck1_i -   Src/Dest  Src/Dest  Src/Dest  Source Clock   Rise/Rise Fall/Rise Rise/Fall Fall/Fall |                     |          |                        |          |  |  |  |  |

|                                                                                                                                    | 14.655              |          | +<br> <br>             | ++<br>   |  |  |  |  |

| Clock to Setup on destination clock ck2_i                                                                                          |                     |          |                        |          |  |  |  |  |

| Source Clock                                                                                                                       |                     | Src/Dest | Src/Dest               | Src/Dest |  |  |  |  |

| ck1_i                                                                                                                              | 11.886<br>  14.813  | •        |                        |          |  |  |  |  |

| Table of Timegroups:                                                                                                               |                     |          |                        |          |  |  |  |  |

| TimeGroup ckl_i:                                                                                                                   |                     |          |                        |          |  |  |  |  |

```

BELs:

core_inst1/counter1/regist1_reg<0> core_inst1/counter1/

regist1 reg<1> core inst1/counter1/regist1 reg<2>

core_inst1/counter1/regist1_reg<3> core_inst1/counter1/

regist1_reg<4> core_inst1/counter1/regist1_reg<5>

core_inst1/counter1/regist1_reg<6> core_inst1/counter1/

regist1_reg<7> core_inst1/counter1/regist1_reg<8>

core_inst1/counter1/regist1_reg<9> core_inst1/counter1/

regist0_reg<0> core_inst1/counter1/regist0_reg<1>

core_inst1/counter1/regist0_reg<2> core_inst1/counter1/

regist0_reg<3> core_inst1/counter1/regist0_reg<4>

core inst1/counter1/regist0 reg<5> core inst1/counter1/

regist0_reg<6> core_inst1/counter1/regist0_reg<7>

core_inst1/counter1/regist0_reg<8> core_inst1/counter1/

regist0_reg<9> core_inst1/counter1/cont_reg<0>

core_inst1/counter1/cont_reg<1>

core_inst1/counter1/

cont_reg<2> core_inst1/counter1/cont_reg<3>

core_inst1/counter1/cont_reg<4>