# Spartan-3 1.2V FPGA Family: DC and Switching Characteristics

DS099-3 (v1.1) July 11, 2003

Advance Product Specification

# **DC Electrical Characteristics**

In this section, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

**Advance:** Initial estimates based on simulation and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

**Preliminary:** Based on characterization. Further changes are not expected.

All specifications are representative of worst-case supply voltage and junction temperature conditions. All specifications are subject to change without notice.

DC and AC characteristics are specified using the same numbers for both commercial and industrial grades unless otherwise noted.

| Symbol               | Descriptior                                                                                                                                                      | Description                  |                       |                       |    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-----------------------|----|

| V <sub>CCINT</sub>   | Internal supply voltage                                                                                                                                          |                              | -0.5                  | 1.32                  | V  |

| V <sub>CCAUX</sub>   | Auxiliary supply voltage                                                                                                                                         |                              | -0.5                  | 3.00                  | V  |

| V <sub>CCO</sub>     | Output driver supply voltage                                                                                                                                     | Output driver supply voltage |                       |                       |    |

| V <sub>REF</sub>     | Input reference voltage                                                                                                                                          | -0.5                         | V <sub>CCO</sub> +0.5 | V                     |    |

| V <sub>IN</sub>      | N Voltage applied to bidirectional I/O pins as well as unidirectional input and output pins. <sup>(3)</sup> If present, driver is put in a high-impedance state. | $V_{CCO} \le 3.0 V^{(4)}$    | -0.5                  | V <sub>CCO</sub> +0.5 | V  |

|                      |                                                                                                                                                                  | V <sub>CCO</sub> > 3.0V      | -0.3                  | 3.75                  | V  |

| TJ                   | Operating junction temperature                                                                                                                                   | $V_{CCO} \le 3.0V^{(4)}$     | -                     | 125                   | °C |

|                      |                                                                                                                                                                  | V <sub>CCO</sub> > 3.0V      | -                     | 105                   | °C |

| T <sub>SOL</sub> (5) | Soldering temperature                                                                                                                                            | Soldering temperature        |                       |                       | °C |

| T <sub>STG</sub>     | Storage temperature                                                                                                                                              | -65                          | 150                   | °C                    |    |

### Table 1: Absolute Maximum Ratings<sup>(1, 2)</sup>

#### Notes:

2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

3. This specification applies to all User I/O, Multi-Function, and Dedicated pins.

4. When V<sub>CCO</sub> is 3.0 V or less, V<sub>IN</sub> overshoot may go as high as V<sub>CCO</sub> + 1.0 V for up to 11 ns provided that the current entering the I/O pin is limited to 10 mA. Also, when V<sub>CCO</sub> is 3.0 V or less, V<sub>IN</sub> undershoot may go as low as –1.0 V for up to 11 ns provided that the current entering the I/O pin is limited to 10 mA.

5. For soldering guidelines, see the information on "Packaging and Thermal Characteristics" at <u>www.xilinx.com</u>.

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

www.xilinx.com 1-800-255-7778

Stresses beyond those listed under Absolute Maximum Ratings will cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time adversely affects device reliability.

## Table 2: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                      | Min | Мах | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 0.8 | 2.0 | V     |

| V <sub>CCO4T</sub>  | Threshold for the V <sub>CCO</sub> Bank 4 supply | 0.4 | 1.0 | V     |

Notes:

1.  $V_{CCINT}\!,\,V_{CCAUX}\!,$  and  $V_{CCO}$  supplies may be applied in any order.

2. During power-on, when the V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 4, and V<sub>CCAUX</sub> voltages are rising, none may dip at any point within their respective threshold-voltage ranges.

3. All parameters representing voltages are measured with respect to GND unless otherwise specified.

### Table 3: Power Voltage Levels Necessary for Preserving RAM Contents<sup>(1)</sup>

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

Notes:

1. RAM contents include configuration data.

2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

3. The level of the V<sub>CCO</sub> supply has no effect on data retention.

### Table 4: General Recommended Operating Conditions

| Symbol                          | Descript                        | Min        | Nom   | Max   | Units |    |

|---------------------------------|---------------------------------|------------|-------|-------|-------|----|

| TJ                              | Junction temperature Commercial |            | 0     | -     | 85    | °C |

|                                 |                                 | Industrial | -40   | -     | 100   | °C |

| V <sub>CCINT</sub>              | Internal supply voltage         | 1.140      | 1.200 | 1.260 | V     |    |

| V <sub>CCO</sub> <sup>(1)</sup> | Output driver supply voltage    | 1.140      | -     | 3.450 | V     |    |

| V <sub>CCAUX</sub>              | Auxiliary supply voltage        | 2.375      | 2.500 | 2.625 | V     |    |

Notes:

The V<sub>CCO</sub> range given here spans the lowest and highest operating voltages of all supported I/O standards. The recommended V<sub>CCO</sub> range specific to each of the single-ended I/O standards is given in Table 7, and that specific to the differential standards is given in Table 9.

2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

| Symbol           | Description                                                           | Test Co                             | onditions               | Min | Nom  | Max  | Units |

|------------------|-----------------------------------------------------------------------|-------------------------------------|-------------------------|-----|------|------|-------|

| ١ <sub>L</sub>   | Leakage current at User<br>I/O, Multi-Function, and<br>Dedicated pins | Driver is in a high-impedance state |                         | -10 | -    | +10  | μA    |

| I <sub>RPU</sub> | Current through pull-up                                               | $V_{IN} = 0V$                       | $V_{CCO} = 3.3V$        | 500 | 1000 | 2000 | μA    |

|                  | resistor at User I/O,<br>Multi-Function, and<br>Dedicated pins        |                                     | $V_{\rm CCO} = 3.0 V$   | 400 | 800  | 1600 | μA    |

|                  |                                                                       |                                     | $V_{\rm CCO} = 2.5 V$   | 250 | 530  | 1100 | μA    |

|                  |                                                                       |                                     | V <sub>CCO</sub> = 1.8V | 120 | 270  | 770  | μA    |

|                  |                                                                       |                                     | $V_{\rm CCO} = 1.5 V$   | 70  | 180  | 440  | μA    |

|                  |                                                                       |                                     | V <sub>CCO</sub> = 1.2V | 40  | 100  | 300  | μA    |

| I <sub>RPD</sub> | Current through                                                       | $V_{IN} = V_{C}$                    | <sub>CO</sub> = 3.3V    | 250 | 520  | 1100 | μA    |

|                  | pull-down resistor at User<br>I/O, Multi-Function, and                | $V_{IN} = V_{CCO} = 3.0V$           |                         | 250 | 520  | 1100 | μA    |

|                  | Dedicated pins                                                        | $V_{IN} = V_{CCO} = 2.5V$           |                         | 250 | 520  | 1100 | μA    |

|                  |                                                                       | $V_{IN} = V_{CCO} = 1.8V$           |                         | 250 | 520  | 1100 | μA    |

|                  |                                                                       | $V_{IN} = V_{C}$                    | <sub>CCO</sub> = 1.5V   | 240 | 510  | 1100 | μA    |

|                  |                                                                       | $V_{IN} = V_{CCO} = 1.2V$           |                         | 230 | 480  | 1000 | μA    |

| I <sub>REF</sub> | V <sub>REF</sub> current per pin                                      |                                     |                         | -10 | -    | +10  | μA    |

| C <sub>IN</sub>  | Input capacitance                                                     |                                     |                         | 5   | -    | 11   | pF    |

# Table 5: General DC Characteristics of User I/O, Multi-Function, and Dedicated Pins

Notes:

1. The numbers in this table are guaranteed over the conditions set forth in Table 4.

## Table 6: Quiescent Supply Current Characteristics

|                                                |                                           |          | Commercial |     | Indu | strial |       |

|------------------------------------------------|-------------------------------------------|----------|------------|-----|------|--------|-------|

| Symbol Description                             | Description                               | Device   | Тур        | Max | Тур  | Max    | Units |

| I <sub>CCINTQ</sub> Quiescen                   | Quiescent V <sub>CCINT</sub> supply       | XC3S50   | 10         |     |      |        | mA    |

|                                                | current                                   | XC3S200  |            |     |      |        | mA    |

|                                                |                                           | XC3S400  |            |     |      |        | mA    |

|                                                |                                           | XC3S1000 | 40         |     |      |        | mA    |

|                                                |                                           | XC3S1500 |            |     |      |        | mA    |

|                                                |                                           | XC3S2000 |            |     |      |        | mA    |

|                                                |                                           | XC3S4000 |            |     |      |        | mA    |

|                                                |                                           | XC3S5000 |            |     |      |        | mA    |

| I <sub>CCOQ</sub> Quiescent V <sub>CCO</sub> s | Quiescent V <sub>CCO</sub> supply current | XC3S50   | 1.5        |     |      |        | mA    |

|                                                |                                           | XC3S200  |            |     |      |        | mA    |

|                                                |                                           | XC3S400  |            |     |      |        | mA    |

|                                                |                                           | XC3S1000 | 1.5        |     |      |        | mA    |

|                                                |                                           | XC3S1500 |            |     |      |        | mA    |

|                                                |                                           | XC3S2000 |            |     |      |        | mA    |

|                                                |                                           | XC3S4000 |            |     |      |        | mA    |

|                                                |                                           | XC3S5000 |            |     |      |        | mA    |

| I <sub>CCAUXQ</sub>                            | Quiescent V <sub>CCAUX</sub> supply       | XC3S50   | 7.0        |     |      |        | mA    |

|                                                | current                                   | XC3S200  |            |     |      |        | mA    |

|                                                |                                           | XC3S400  |            |     |      |        | mA    |

|                                                |                                           | XC3S1000 | 25.0       |     |      |        | mA    |

|                                                |                                           | XC3S1500 |            |     |      |        | mA    |

|                                                |                                           | XC3S2000 |            |     |      |        | mA    |

|                                                |                                           | XC3S4000 |            |     |      |        | mA    |

|                                                |                                           | XC3S5000 |            |     |      |        | mA    |

Notes:

Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. For typical values, the ambient temperature (T<sub>A</sub>) is 85 °C with V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 2.5V, and V<sub>CCAUX</sub> = 2.5V.

The supple current is the table of the supple current is the supple current in the supple current is the supple current is

2. The numbers in this table are guaranteed over the conditions set forth in Table 4.

# Table 7: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

|                                                      |         | V <sub>cco</sub> |         |         | V <sub>REF</sub> |         | VIL                      | V <sub>IH</sub>          |

|------------------------------------------------------|---------|------------------|---------|---------|------------------|---------|--------------------------|--------------------------|

| Signal Standard                                      | Min (V) | Nom (V)          | Max (V) | Min (V) | Nom (V)          | Max (V) | Max (V)                  | Min (V)                  |

| GTL                                                  | -       | -                | -       | 0.74    | 0.8              | 0.86    | V <sub>REF</sub> - 0.05  | V <sub>REF</sub> + 0.05  |

| GTL_DCI <sup>(2)</sup>                               | -       | 1.2              | -       | 0.74    | 0.8              | 0.86    | V <sub>REF</sub> - 0.05  | V <sub>REF</sub> + 0.05  |

| GTLP                                                 | -       | -                | -       | 0.88    | 1                | 1.12    | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| GTLP_DCI <sup>(2)</sup>                              | -       | 1.5              | -       | 0.88    | 1                | 1.12    | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_I,<br>HSTL_I_DCI                                | 1.4     | 1.5              | 1.6     | 0.68    | 0.75             | 0.9     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_III,<br>HSTL_III_DCI                            | 1.4     | 1.5              | 1.6     | 0.68    | 0.9              | 0.9     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_I_18,<br>HSTL_I_DCI_18                          | 1.7     | 1.8              | 1.9     | -       | 0.9              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_II_18,<br>HSTL_II_DCI_18                        | 1.7     | 1.8              | 1.9     | -       | 0.9              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_III_18,<br>HSTL_III_DCI_18                      | 1.7     | 1.8              | 1.9     | -       | 1.1              | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| LVCMOS12 <sup>(3)</sup>                              | 1.14    | 1.2              | 1.3     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |

| LVCMOS15,<br>LVDCI_15 <sup>(3)</sup>                 | 1.4     | 1.5              | 1.6     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |

| LVCMOS18,<br>LVDCI_18 <sup>(3)</sup>                 | 1.7     | 1.8              | 1.9     | -       | -                | -       | 0.20V <sub>CCO</sub>     | 0.70V <sub>CCO</sub>     |

| LVCMOS25 <sup>(4)</sup> ,<br>LVDCI_25 <sup>(3)</sup> | 2.3     | 2.5              | 2.7     | -       | -                | -       | 0.7                      | 1.7                      |

| LVCMOS33,<br>LVDCI_33 <sup>(3)</sup>                 | 3.0     | 3.3              | 3.45    | -       | -                | -       | 0.8                      | 2.0                      |

| LVTTL                                                | 3.0     | 3.3              | 3.45    | -       | -                | -       | 0.8                      | 2.0                      |

| PCI33_3                                              | 3.0     | 3.0              | 3.0     | -       | -                | -       | 0.30V <sub>CCO</sub>     | 0.50V <sub>CCO</sub>     |

| SSTL18_I                                             | 1.65    | 1.8              | 1.95    | 0.825   | 0.9              | 0.975   | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 |

| SSTL2_I,<br>SSTL2_I_DCI                              | 2.3     | 2.5              | 2.7     | 1.15    | 1.25             | 1.35    | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  |

| SSTL2_II,<br>SSTL2_II_DCI                            | 2.3     | 2.5              | 2.7     | 1.15    | 1.25             | 1.35    | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  |

#### Notes:

Descriptions of the symbols used in this table are as follows: 1.

$V_{CCO}$  -- the supply voltage for the output drivers.  $V_{REF}$  -- the reference voltage for setting the input switching threshold.  $V_{IL}$  -- the input voltage that indicates a Low logic level

V<sub>IH</sub> -- the input voltage that indicates a High logic level

Because the GTL and GTLP standards employ open-drain output buffers, the  $V_{CCO}$  supply does not provide drive current. Nevertheless, the  $V_{CCO}$  level must always be at or above the termination voltage ( $V_{TT}$ ) and I/O pad voltages. 2.

3. There is approximately 100 mV of hysteresis on inputs using any LVCMOS standard.

In the standard case, all Dedicated pins (M0-M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, TMS) use the LVCMOS25 4. standard and are powered entirely by V<sub>CCAUX</sub>. The Dual-Purpose configuration pins (DIN/D0, D1-D7, CS\_B, RDWR\_B, BUSY/DOUT, and INIT\_B) use the LVCMOS25 standard during configuration. For information on how to program the FPGA using 3.3V signals and power, see the "3.3V-Tolerant Configuration Interface" section in Module 2. The recommended V<sub>CCO</sub> or V<sub>CCAUX</sub> levels must be applied to the Global Clock Inputs (GCLK0 - GCLK7) according to the signal standards assigned to them—the same as for User Inputs.

All parameters representing voltages are measured with respect to GND unless otherwise specified. 5.

|                                                      | Test C                  | Test Conditions         |                            | haracteristics             |

|------------------------------------------------------|-------------------------|-------------------------|----------------------------|----------------------------|

| Signal Standard                                      | l <sub>OL</sub><br>(mA) | I <sub>ОН</sub><br>(mA) | V <sub>OL</sub><br>Max (V) | V <sub>OH</sub><br>Min (V) |

| GTL, GTL_DCI                                         | 32                      | -                       | 0.4                        | -                          |

| GTLP, GTLP_DCI                                       | 36                      | -                       | 0.6                        | -                          |

| HSTL_I, HSTL_I_DCI                                   | 8                       | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |

| HSTL_III,<br>HSTL_III_DCI                            | 24                      | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |

| HSTL_I_18,<br>HSTL_I_DCI_18                          | 8                       | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |

| HSTL_II_18,<br>HSTL_II_DCI_18                        | 16                      | -16                     | 0.4                        | V <sub>CCO</sub> - 0.4     |

| HSTL_III_18,<br>HSTL_III_DCI_18                      | 24                      | -8                      | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVCMOS12                                             | 6                       | -6                      | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVCMOS15,<br>LVDCI_15                                | 12                      | -12                     | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVCMOS18,<br>LVDCI_18                                | 16                      | -16                     | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVCMOS25 <sup>(2)</sup> ,<br>LVDCI_25 <sup>(3)</sup> | 24                      | -24                     | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVCMOS33,<br>LVDCI_33                                | 24                      | -24                     | 0.4                        | V <sub>CCO</sub> - 0.4     |

| LVTTL                                                | 24                      | -24                     | 0.4                        | 2.4                        |

| PCI33_3                                              | Note 5                  | Note 5                  | 0.10V <sub>CCO</sub>       | 0.90V <sub>CCO</sub>       |

| SSTL18_I                                             | 6.7                     | -6.7                    | V <sub>TT</sub> - 0.475    | V <sub>TT</sub> + 0.475    |

| SSTL2_I,<br>SSTL2_I_DCI                              | 7.5                     | -7.5                    | V <sub>TT</sub> - 0.61     | V <sub>TT</sub> + 0.61     |

| SSTL2_II,<br>SSTL2_II_DCI                            | 15                      | -15                     | V <sub>TT</sub> - 0.80     | V <sub>TT</sub> + 0.80     |

Descriptions of the symbols used in this table are as follows: 1.

$I_{OL}$  -- the output current condition under which  $V_{OL}$  is tested

$V_{OL}$  -- the output current condition under which  $V_{OH}$  is tested  $V_{OL}$  -- the output current condition under which  $V_{OH}$  is tested  $V_{OL}$  -- the output voltage that indicates a Low logic level  $V_{OH}$  -- the output voltage that indicates a High logic level

$V_{IL}^{-}$  -- the input voltage that indicates a Low logic level  $V_{IH}^{-}$  -- the input voltage that indicates a High logic level

V<sub>CCO</sub> -- the supply voltage for the output drivers

V<sub>REF</sub> -- the reference voltage for setting the input switching threshold

V<sub>TT</sub> -- the termination voltage

In the standard case, all Dedicated pins (M0-M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, TMS) as well as the 2. Dual-Purpose configuration pins (DIN/D0, D1-D7, CS\_B, RDWR\_B, BUSY/DOUT, and INIT\_B) exhibit LVCMOS25 output characteristics. For information on how to program the FPGA using 3.3V signals and power, see the "3.3V-Tolerant Configuration Interface" section in Module 2

3. All parameters representing voltages are measured with respect to GND unless otherwise specified.

4. The numbers in this table are guaranteed over the conditions set forth in Table 4 and Table 7.

Tested according to relevant PCI specifications. 5.

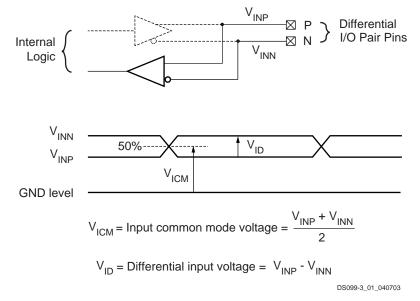

Figure 1: Differential Input Voltages

| Table 9: Recommended Operating Conditions for User I/Os Using Diffe | rential Signal Standards |

|---------------------------------------------------------------------|--------------------------|

|                               | V <sub>cco</sub> |         |         | V <sub>ID</sub> |             |          | V <sub>ICM</sub> |         |         |

|-------------------------------|------------------|---------|---------|-----------------|-------------|----------|------------------|---------|---------|

| Signal Standard               | Min (V)          | Nom (V) | Max (V) | Min (mV)        | Nom<br>(mV) | Max (mV) | Min (V)          | Nom (V) | Max (V) |

| LDT_25                        | 2.38             | 2.50    | 2.63    | 200             | 600         | 1000     | 0.44             | 0.60    | 0.78    |

| LVDS_25,<br>LVDS_25_DCI       | 2.38             | 2.50    | 2.63    | 100             | 350         | 600      | 0.30             | 1.25    | 2.20    |

| BLVDS_25                      | 2.38             | 2.50    | 2.63    | -               | 350         | -        | -                | 1.25    | -       |

| LVDSEXT_25,<br>LVDSEXT_25_DCI | 2.38             | 2.50    | 2.63    | 100             | 540         | 1000     | 0.30             | 1.20    | 2.20    |

| ULVDS_25                      | 2.38             | 2.50    | 2.63    | 200             | 600         | 1000     | 0.44             | 0.60    | 0.78    |

| RSDS_25                       | 2.38             | 2.50    | 2.63    | 100             | 200         | -        | -                | 1.30    | -       |

1. The V<sub>REF</sub> input is not used for any of the differential I/O standards.

Of the parameters shown, only V<sub>CCO</sub> represents a voltage measured with respect to GND. The remaining parameters are differential measurements. See Figure 1 for parameter definitions.

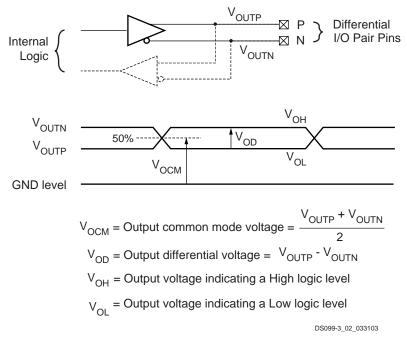

Figure 2: Differential Output Voltages

| Table 10: DC Characteristics of User I/Os Us | Ising Differential Signal Standards |

|----------------------------------------------|-------------------------------------|

|----------------------------------------------|-------------------------------------|

|                               |             | V <sub>OD</sub> |             | ΔV          | OD          |            | V <sub>OCM</sub> |            | Δ٧          | осм         | V          | он         | Va         | OL         |

|-------------------------------|-------------|-----------------|-------------|-------------|-------------|------------|------------------|------------|-------------|-------------|------------|------------|------------|------------|

| Signal Standard               | Min<br>(mV) | Typ<br>(mV)     | Max<br>(mV) | Min<br>(mV) | Max<br>(mV) | Min<br>(V) | Тур<br>(V)       | Max<br>(V) | Min<br>(mV) | Max<br>(mV) | Тур<br>(V) | Max<br>(V) | Min<br>(V) | Тур<br>(V) |

| LDT_25                        | 430         | 600             | 670         | -15         | 15          | 0.495      | 0.600            | 0.715      | -15         | 15          | -          | -          | -          | -          |

| LVDS_25,<br>LVDS_25_DCI       | 250         | 325             | 400         | -           | -           | 1.125      | 1.20             | 1.375      | -           | -           | -          | 1.475      | 0.925      | -          |

| BLVDS_25                      | 250         | 350             | 450         | -           | -           | -          | 1.20             | -          | -           | -           | -          | -          | -          | -          |

| LVDSEXT_25,<br>LVDSEXT_25_DCI | 330         | 540             | 700         | -           | -           | 1.125      | 1.20             | 1.375      | -           | -           | -          | 1.700      | 0.705      | -          |

| ULVDS_25                      | 430         | 600             | 670         | -           | -           | 0.495      | 0.600            | 0.715      | -           | -           | -          | -          | -          | -          |

| RSDS_25                       | 100         | 325             | 400         | -           | -           | 1.1        | 1.2              | 1.5        | -           | -           | -          | -          | -          | -          |

Of the parameters shown, only V<sub>OH</sub>, V<sub>OL</sub>, and V<sub>OCM</sub> represent voltages measured with respect to GND. The remaining parameters are differential measurements. See Figure 2 for parameter definitions.

2. Output voltage measurements for all differential standards are made with a termination resistor ( $R_T$ ) of 100 $\Omega$  across the N and P pins of the differential signal pair.

3. The numbers in this table are guaranteed over the conditions set forth in Table 4 and Table 9.

# **Switching Characteristics**

All Spartan-3 devices are available in two speed grades: -4 and -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production. Each category is defined as follows:

Advance: These speed files are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

**Preliminary**: These speed files are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

**Production**: These speed files are released once enough production silicon of a particular device family member has been characterized to provide full correlation between

speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

All specifications are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, values apply to all Spartan-3 devices.

Internal timing parameters are derived from measuring internal test patterns. Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. For more complete, more precise, and worst-case guaranteed data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotate to the simulation net list.

| Table | 11: | DLL | Timing |

|-------|-----|-----|--------|

|-------|-----|-----|--------|

|                                                                         |                            | Frequency<br>Mode                     |     |      |      |     |       |  |

|-------------------------------------------------------------------------|----------------------------|---------------------------------------|-----|------|------|-----|-------|--|

| Symbol                                                                  |                            |                                       | -5  |      | -4   |     |       |  |

|                                                                         | Description                |                                       | Min | Max  | Min  | Max | Units |  |

| Clock Out                                                               | puts                       | · · · · · · · · · · · · · · · · · · · |     | 1    | 1    |     |       |  |

| Frequency at the CLK0 and CLK180 pins                                   | High                       |                                       |     | 48   | 326  | MHz |       |  |

|                                                                         | CLK180 pins                | Low                                   |     |      | 25   | 180 | MHz   |  |

| Clock Inpu                                                              | its                        | I                                     |     | 1    | 1    | 1   | 1     |  |

| -                                                                       |                            | High                                  |     |      | 48   | 326 | MHz   |  |

| F <sub>CLKIN</sub>                                                      | Frequency at the CLKIN pin | Low                                   |     |      | 25   | 180 | MHz   |  |

| T <sub>CLKINJ</sub> Allowable cycle-to-cycle<br>jitter at the CLKIN pin | High                       |                                       |     | -100 | +100 | ps  |       |  |

|                                                                         |                            | Low                                   |     |      |      |     | ps    |  |

Notes:

1. For up-to-date information on DCM timing, see http://www.xilinx.com/bvdocs/publications/ds099-3.pdf.

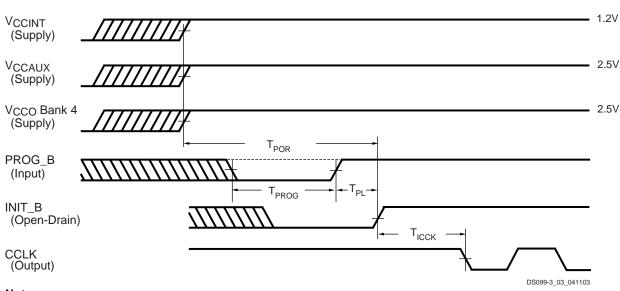

- The V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies may be applied in any order.

The Low-going pulse on PROG\_B is optional after power-on but necessary for reconfiguration without a power cycle.

- 3. The rising edge of INIT\_B samples the voltage levels applied to the mode pins (M0 - M2).

## Figure 3: Waveforms for Power-On and the Beginning of Configuration

| Table | 12: | Power-On | Timing | and the | Beginning | of ( | Configuration |

|-------|-----|----------|--------|---------|-----------|------|---------------|

|-------|-----|----------|--------|---------|-----------|------|---------------|

|                   |                                                                                                                                                 |          | All Spee |     |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----|-------|

| Symbol            | Description                                                                                                                                     | Device   | Min      | Max | Units |

| T <sub>POR</sub>  | The time from the application of V <sub>CCINT</sub> ,                                                                                           | XC3S50   | -        | 5   | ms    |

|                   | $V_{CCAUX}$ , and $V_{CCO}$ Bank 4 supply voltages                                                                                              | XC3S200  | -        | 5   | ms    |

|                   | (whichever occurs last) to the rising transition of the INIT_B pin <sup>(1)</sup>                                                               | XC3S400  | -        | 5   | ms    |

|                   |                                                                                                                                                 | XC3S1000 | -        | 5   | ms    |

|                   |                                                                                                                                                 | XC3S1500 | -        | 7   | ms    |

|                   |                                                                                                                                                 | XC3S2000 | -        | 7   | ms    |

|                   |                                                                                                                                                 | XC3S4000 | -        | 7   | ms    |

|                   |                                                                                                                                                 | XC3S5000 | -        | 7   | ms    |

| T <sub>PROG</sub> | The width of the low-going pulse on the PROG_B pin                                                                                              | All      | 0.3      | -   | μs    |

| T <sub>PL</sub>   | The time from the rising edge of the PROG_B pin to the rising transition on the INIT_B pin <sup>(1)</sup>                                       | XC3S50   | -        | 2   | ms    |

|                   |                                                                                                                                                 | XC3S200  | -        | 2   | ms    |

|                   |                                                                                                                                                 | XC3S400  | -        | 2   | ms    |

|                   |                                                                                                                                                 | XC3S1000 | -        | 2   | ms    |

|                   |                                                                                                                                                 | XC3S1500 | -        | 3   | ms    |

|                   |                                                                                                                                                 | XC3S2000 | -        | 3   | ms    |

|                   |                                                                                                                                                 | XC3S4000 | -        | 3   | ms    |

|                   |                                                                                                                                                 | XC3S5000 | -        | 3   | ms    |

| Т <sub>ІССК</sub> | The time from the rising edge of the INIT_B<br>pin to the generation of the configuration<br>clock signal at the CCLK output pin <sup>(2)</sup> | All      | 0.5      | 4.0 | μs    |

Notes:

Power-on reset and the clearing of configuration memory occurs during this period. 1

This specification applies only for the Master Serial and Master Parallel modes. 2.

1. The CS\_B, WRITE\_B, and BUSY signals are not used in the serial modes. Keep the CS\_B and WRITE\_B inputs inactive (i.e., both pins High).

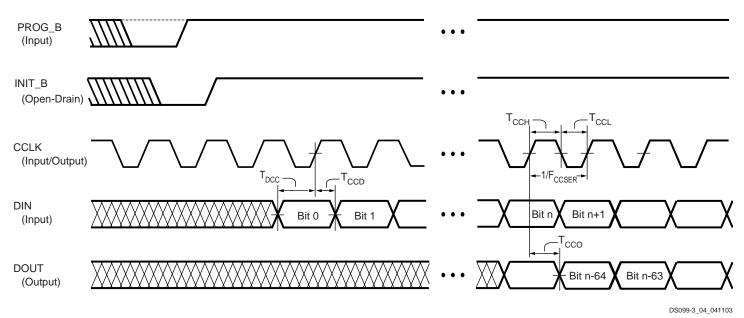

## Figure 4: Waveforms for Master and Slave Serial Configuration

| Table 13: | Timing for the | Master and Slave | Serial Configuration Modes |

|-----------|----------------|------------------|----------------------------|

|-----------|----------------|------------------|----------------------------|

|                    |                                                                                                        |              | All Spee |      |       |  |

|--------------------|--------------------------------------------------------------------------------------------------------|--------------|----------|------|-------|--|

| Symbol             | Description                                                                                            | Slave/Master | Min      | Max  | Units |  |

| Setup Times        |                                                                                                        |              |          |      |       |  |

| T <sub>DCC</sub>   | The time from the setup of data at the DIN pin to the rising transition at the CCLK pin                | Both         | -        | 5.0  | ns    |  |

| Hold Times         |                                                                                                        |              |          | 1    | 1     |  |

| T <sub>CCD</sub>   | The time from the rising transition at the CCLK pin to the point when data is last held at the DIN pin | Both         | -        | 0    | ns    |  |

| Clock-to-Output    | limes                                                                                                  | I I          |          | 1    | 1     |  |

| T <sub>CCO</sub>   | The time from the rising transition on the CCLK pin to data appearing at the DOUT pin                  | Both         | -        | 12.0 | ns    |  |

| Clock Timing       |                                                                                                        |              |          | 1    | 1     |  |

| T <sub>CCH</sub>   | The High pulse width at the CCLK input pin                                                             | Slave        | 5.0      | -    | ns    |  |

| T <sub>CCL</sub>   | The Low pulse width at the CCLK input pin                                                              | -            | 5.0      | -    | ns    |  |

| F <sub>CCSER</sub> | Frequency of the clock signal at the CCLK input pin                                                    | -            | -        | 66   | MHz   |  |

| $\Delta F_{CCSER}$ | Variation from the generated CCLK frequency set using the ConfigRate BitGen option                     | Master       | -50%     | +50% | -     |  |

1. In a given CCLK cycle, when RDWR\_B transitions High or Low while holding CS\_B Low, the next rising edge on the CCLK pin will abort configuration.

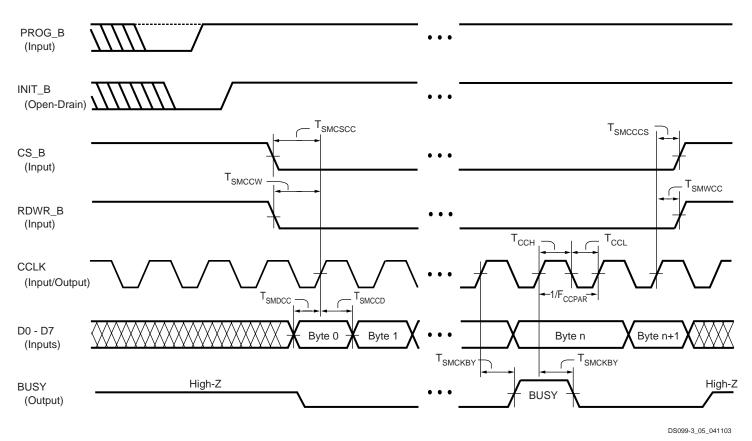

## Figure 5: Waveforms for Master and Slave Parallel Configuration

| <i>Table 14:</i> Timing for the Master and Slave Parallel Configuration Modes | Table | 14: | Timing f | or the | Master and | I Slave Pa | arallel Co | nfiguration Modes |

|-------------------------------------------------------------------------------|-------|-----|----------|--------|------------|------------|------------|-------------------|

|-------------------------------------------------------------------------------|-------|-----|----------|--------|------------|------------|------------|-------------------|

|                     |                                                                                                                                    |              | All Speed Grades |     |       |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|-----|-------|

| Symbol              | Description                                                                                                                        | Slave/Master | Min              | Max | Units |

| Setup Times         |                                                                                                                                    | 1            |                  |     |       |

| T <sub>SMDCC</sub>  | The time from the setup of data at the D0-D7 pins to the rising transition at the CCLK pin                                         | Both         | 5.0              | -   | ns    |

| T <sub>SMCSCC</sub> | The time from the setup of a logic level at the CS_B pin to the rising transition at the CCLK pin                                  | -            | 7.0              | -   | ns    |

| T <sub>SMCCW</sub>  | The time from the setup of a logic level at the RDWR_B pin to the rising transition at the CCLK pin <sup>(1)</sup>                 |              | 7.0              | -   | ns    |

| Hold Times          |                                                                                                                                    | I            | 1                | 1   |       |

| T <sub>SMCCD</sub>  | The time from the rising transition at the CCLK pin to the point when data is last held at the D0-D7 pins                          | Both         | 0                | -   | ns    |

| T <sub>SMCCCS</sub> | The time from the rising transition at the CCLK pin to the point when a logic level is last held at the CS_B pin                   |              | 0                | -   | ns    |

| T <sub>SMWCC</sub>  | The time from the rising transition at the CCLK $pin^{(1)}$ to the point when a logic level is last held at the RDWR_B $pin^{(1)}$ |              | 0                | -   | ns    |

|                     |                                                                |                                                                                       |              | All Speed Grades |      |       |

|---------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|------------------|------|-------|

| Symbol              | Descri                                                         | ption                                                                                 | Slave/Master | Min              | Max  | Units |

| Clock-to-Out        | put Times                                                      |                                                                                       |              |                  |      |       |

| T <sub>SMCKBY</sub> | The time from the rising transi signal transition at the BUSY  | e time from the rising transition on the CCLK pin to a nal transition at the BUSY pin |              |                  | 12.0 | ns    |

| <b>Clock Timing</b> |                                                                |                                                                                       | 1            | 1                | 1    | I     |

| Т <sub>ССН</sub>    | The High pulse width at the C                                  | CLK input pin                                                                         | Slave        | 5                | -    | ns    |

| T <sub>CCL</sub>    | The Low pulse width at the CO                                  | CLK input pin                                                                         |              | 5                | -    | ns    |

| F <sub>CCPAR</sub>  | Frequency of the clock signal                                  | Not using the BUSY pin <sup>(2)</sup>                                                 | -            | -                | 66   | MHz   |

|                     | at the CCLK input pin                                          | Using the BUSY pin                                                                    | -            | -                | 100  | MHz   |

| $\Delta F_{CCPAR}$  | Variation from the generated (<br>the BitGen option ConfigRate | Variation from the generated CCLK frequency set using                                 |              | -50%             | +50% | -     |

## Table 14: Timing for the Master and Slave Parallel Configuration Modes (Continued)

Notes:

1. RDWR\_B is synchronized to CCLK for the purpose of performing the Abort operation. The same pin asynchronously controls the driver impedance of the D0 - D7 pins. To avoid contention when writing configuration data to the D0 - D7 bus, do not bring RDWR\_B High when CS\_B is Low.

2. In the Slave Parallel mode, it is necessary to use the BUSY pin when the CCLK frequency exceeds this maximum specification.

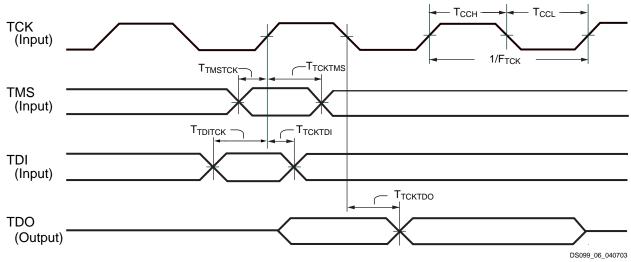

## Figure 6: JTAG Waveforms

|                     |                                                                                                       | All Spee |     |       |

|---------------------|-------------------------------------------------------------------------------------------------------|----------|-----|-------|

| Symbol              | Description                                                                                           | Min      | Max | Units |

| Setup Times         |                                                                                                       |          | •   |       |

| T <sub>TDITCK</sub> | The time from the setup of data at the TDI pin to the rising transition at the TCK pin                | 4.0      | -   | ns    |

| T <sub>TMSTCK</sub> | The time from the setup of a logic level at the TMS pin to the rising transition at the TCK pin       | 4.0      | -   | ns    |

| Hold Times          |                                                                                                       |          |     |       |

| Т <sub>ТСКТОІ</sub> | The time from the rising transition at the TCK pin to the point when data is last held at the TDI pin | 0        | -   | ns    |

# Table 15: Timing for the JTAG Port

|                     |                                                                                                                | All Spee |      |       |

|---------------------|----------------------------------------------------------------------------------------------------------------|----------|------|-------|

| Symbol              | Description                                                                                                    | Min      | Max  | Units |

| Т <sub>ТСКТМS</sub> | The time from the rising transition at the TCK pin to the point when a logic level is last held at the TMS pin | 0        | -    | ns    |

| Clock-to-Output T   | imes                                                                                                           |          |      |       |

| Т <sub>ТСКТDO</sub> | The time from the falling transition on the TCK pin to data appearing at the TDO pin                           | -        | 11.0 | ns    |

| Clock Timing        |                                                                                                                |          | 1    |       |

| Т <sub>ССН</sub>    | The High pulse width at the TCK pin                                                                            | 5.0      | -    | ns    |

| T <sub>CCL</sub>    | The Low pulse width at the TCK pin                                                                             | 5.0      | -    | ns    |

| F <sub>TCK</sub>    | Frequency of the clock signal at the TCK pin                                                                   | -        | 33   | MHz   |

# Table 15: Timing for the JTAG Port (Continued)

# **Revision History**

| Date     | Version No. | Description                                                                                                                                                   |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0         | Initial Xilinx release.                                                                                                                                       |

| 07/11/03 | 1.1         | Extended Absolute Maximum Rating for junction temperature in Table 1. Added numbers for typical quiescent supply current (Table 6) and DLL timing (Table 11). |

# **The Spartan-3 Family Data Sheet**

DS099-1, Spartan-3 1.2V FPGA Family: Introduction and Ordering Information (Module 1)

DS099-2, Spartan-3 1.2V FPGA Family: Functional Description (Module 2)

DS099-3, Spartan-3 1.2V FPGA Family: DC and Switching Characteristics (Module 3)

DS099-4, Spartan-3 1.2V FPGA Family: Pinout Tables (Module 4)