Platform Design Methods for Integrating Standard Processor Cores and Programmable Logic for Embedded Systems

IRM

caden

XILINX

Sustems ness

The Fallen

Celoxica

The MathWorks

#### **Presentation Content**

- Communications Platform Challenges

- Platform Design Criteria

- The Perfect Marriage

- Design Options Platform FPGA and Platform ASIC

- Two Examples: VPN Gateway and IP Phone

- Explore performance, function partitioning, simulation, emulation and software features

- Tips for Design for Portability

- Embedded FPGA Blocks in IBM 90nm

- Summary

- Contacts and References

#### Challenges

- New standards: 802.11g for wireless

- New interfaces: RapidIO, SPI4.X

- New applications: VPN, VoIP, WLAN

- Critical function and performance requirements

- High levels of integration, chip density, complexity

- System density & packaging versus power & thermal constraints

### **Platform Design Criteria**

- Logic Design Criteria

- Development cost

- Available skills

- Technology risks

- Standard architecture

- Tools availability

- Flexibility/reuse

- System Design Criteria

- Software base

- Legacy support

- Chassis & board space

- Power & thermal

- System performance

- BOM cost

- Building blocks

- Volume requirements

#### **A Perfect Marriage**

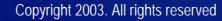

#### IBM – Xilinx Covers the Entire Design Spectrum

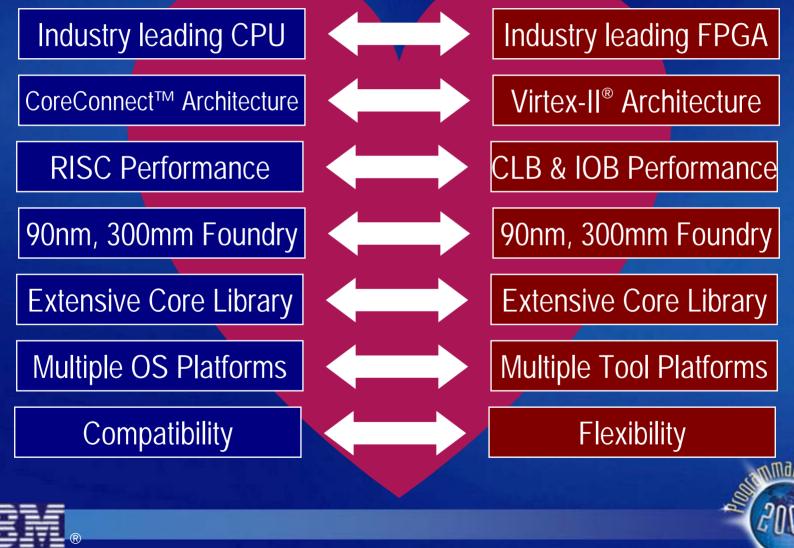

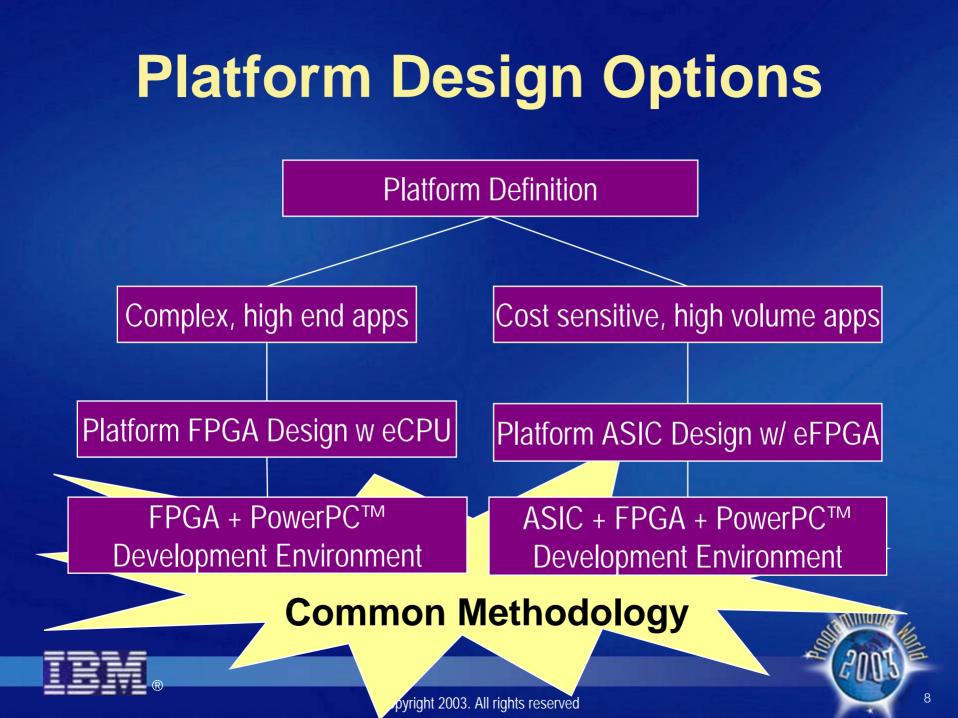

### **Platform Design Options**

Platform FPGA with embedded CPU

Fastest TTM, most flexibility

Platform ASIC with embedded FPGA

Dense integration for low cost, high volume applications

#### **PowerPC® + Virtex-II FPGA Value**

- Right the first time methodology

- Design flexibility; product flexibility

- Standard libraries, extensive support

- Pre-validated platform cores

- Best performance for software and hardware programmability

- Strong roadmaps with legacy protection

#### **Example Platforms**

- PowerPC<sup>®</sup> & Xilinx FPGA platforms covering the following design issues:

- Fast turn around and system enablement

- Standard product mixed with custom logic

- Integrated tools for simulation and emulation

- FPGA used to mitigate logic risk and add flexibility

- Support for performance expansion and product derivatives

- Available software

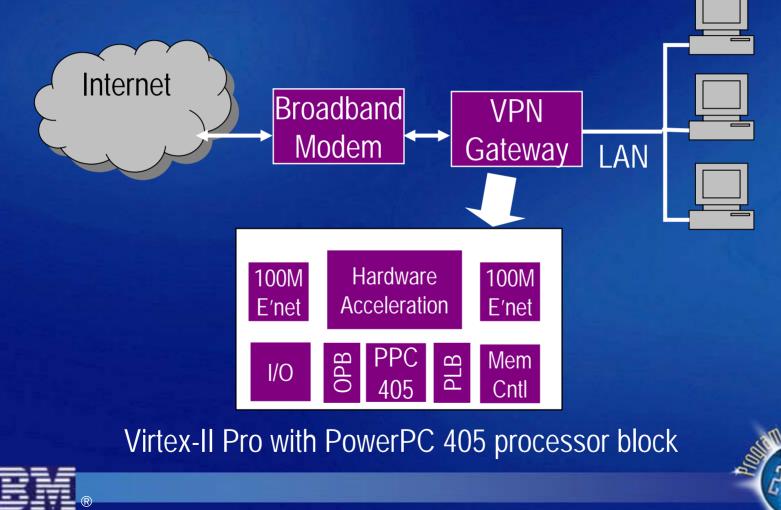

### **VPN Gateway Application**

Platform FPGA design using Virtex-II Pro®

#### **Performance Exercise**

- Control processing PowerPC® 405

- VPN session management

- **IPSEC protocol**

- User authentication

- Firewall function

- Data processing Programmable Logic

- Packet transfer

- Data encryption/decryption

#### **Performance Requirements**

| System Control                                                                                 | PPC405 processor block                                                                            |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| <ul><li>Embedded OS MV Linux/VxWorks</li><li>IP Firewall</li><li>VPN Session Manager</li></ul> | <ul> <li>- 333MHz, 500 MIPs</li> <li>- VPN performance 60Mbps<br/>(mixed packet sizes)</li> </ul> |

| - 30 VPN tunnels                                                                               |                                                                                                   |

| Hardware Accelerator<br>Functions<br>- 3DES, DES, AES, MD5, SHA                                | Xilinx High Speed<br>Encryptor/Decryptor<br>- App note XAPP270<br>- Approximately 5000 LUTs       |

| Network Connections                                                                            | WAN – 100 Mbit Ethernet<br>LAN – 100 Mbit Ethernet                                                |

|                                                                                                |                                                                                                   |

### **Partitioning Exercise**

- Balance function between CPU platform and programmable logic

- Separate low risk, standardized functions from high risk functions.

- Minimize design risk and maximize first-pass success

- Maximize enablement support

- Expansion and derivative plan

### **Function Partitioning**

| Module                   | Xilinx Virtex-II Pro®<br>FPGA development sfw & tools                                            | Standard part                               |

|--------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------|

| System Processor         | PPC405 processor block inside<br>Xilinx VirtexII Pro<br>PowerPC <sup>®</sup> support sfw & tools | Hard core w/<br>Core Connect<br>peripherals |

| Peripheral I/O           | 10/100 Mbps Ethernet MACs,<br>64MB RAM interface, 4MB<br>ROM interface                           | Xilinx library<br>cores                     |

| 3DES, DES<br>accelerator | Implement XAPP720 app note<br>- Approx 5040 LUTs                                                 | New logic                                   |

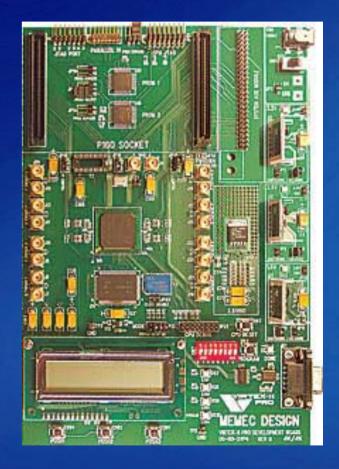

### **Design Emulation Option**

#### • Xilinx: Virtex-II Pro P4/7-FG456 evaluation kit

- Supports 2VP4 or 2VP7 Virtex-II

Pro FPGA

- Single embedded PowerPC 405

w/ Core Connect bus

- GNU based C compiler, assembler, linker and debugger

- 8 M x 32 SDRAM memory

- Expansion slot for user I/O

- Configuration through JTAG and ISP PROMs

- 2 x 16 character LCD

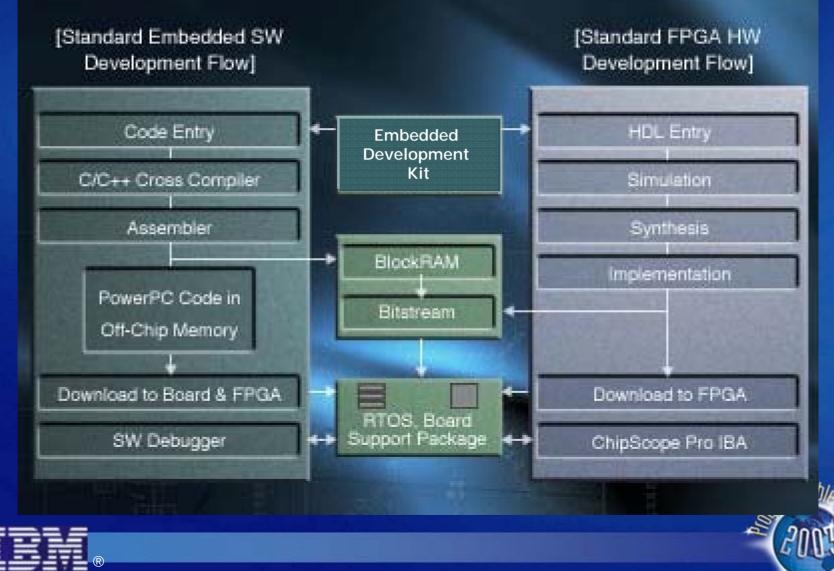

#### **Combined Tool Flow**

#### **Application Software Support**

#### Wind River Platform

- Tornado<sup>®</sup> and VxWorks<sup>®</sup> for IBM PowerPC<sup>®</sup>

- Wind®Net VPN protocol for VxWorks

- Ashley Laurent integrated security suite for VxWorks

- MontaVista™ Platform

- Embedded Linux<sup>®</sup> for IBM PowerPC

- MontaVista VPN and firewall ISV partners: Intoto, Inc., Artesyn Technologies, ipinfusion<sup>™</sup>, SSH<sup>®</sup>

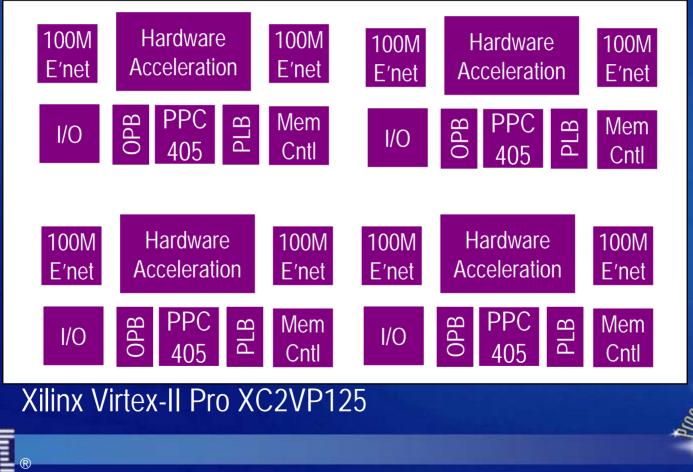

#### **Performance Expansion**

• A Virtex-II Pro with four PowerPC® 405 processor blocks can be used to produce a higher connectivity VPN solution

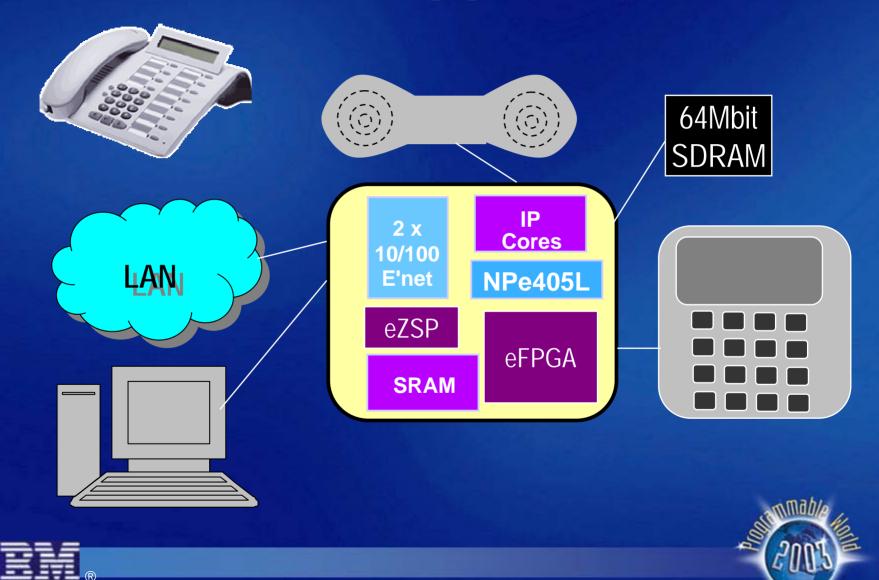

#### **Platform ASIC Example**

#### **IP Phone Application**

E

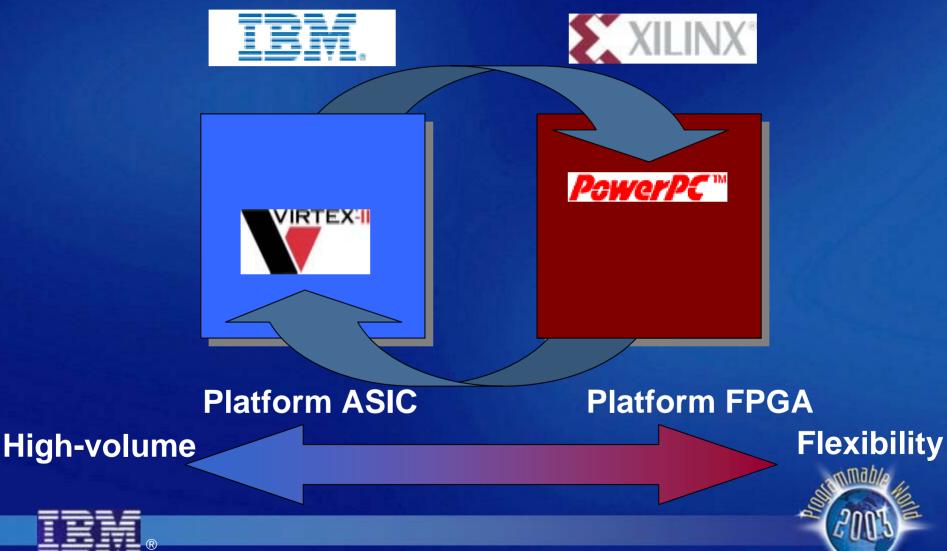

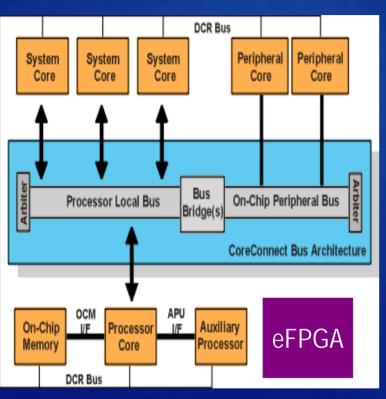

#### Platform ASIC with PowerPC® CoreConnect<sup>™</sup> and Embedded FPGA

**Processor Local Bus**

- Synchronous, 8 masters

- 32-, 64-, and 128-bit architecture

- Bus Pipelining, Split xactions

On-Chip Peripheral Bus

- Fully synchronous

- 32-bit address, 32-bit data bus

- Supports bus masters & slaves

- Bridge functions on PLB or OPB Add eFPGA cores to PLB or OPB

All cores designed to CoreConnect<sup>™</sup> specifications with timeconsuming performance, functional, and timing pattern issues resolved

#### **Performance Exercise**

#### Control processing

- Send and receive IP packets from LAN interfaces

- Switch packets between LAN, phone client and PC

- Process commands from phone pad interface

- Display status on LCD display

- Data processing

- Process G.729a, G.711 voice CODEC

- Process speakerphone, ADC/DAC

#### **Performance Requirements**

| ASIC Technology            | IBM 90nm                            |  |

|----------------------------|-------------------------------------|--|

| System Control             | 100 MHz, 150 MIPs NPe405L           |  |

| - Embedded OS              | 64Mb SDRAM, Boot ROM                |  |

| DSP Functions              |                                     |  |

| - G.729a G.711 Voice CODEC | 100 MHz, 400 MIPs, 200 MMACs ZSP400 |  |

| - H.323 Speakerphone       | 144 - 256KB eSRAM                   |  |

| - Stereo/Mono ADC, DAC     |                                     |  |

| Human Interfaces           |                                     |  |

| - LCD panal                | LCD interface, GPIO                 |  |

| - Phone pad                |                                     |  |

| - LED's & function buttons |                                     |  |

| Network Connection         | 2 x 100Mbit E'net                   |  |

|                            |                                     |  |

### **Function Partitioning**

| System Processor                   | Verified PPC405 core layout w/<br>SDRAM mem ctl, SRAM, DMA,<br>UART, GPIO, JTAG. Max<br>300MHz | Pre-validated<br>hard or soft<br>cores |

|------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------|

| Common I/O                         | 10/100 Mbps Ethernet MACs,<br>ROM interface                                                    | Soft cores                             |

| Codec, ADC/DAC<br>functions        | LSI ZSP400 tied to 405 PLB                                                                     | Hard core w/<br>software<br>library    |

| Custom LCD and phone pad interface | Programmable logic via internal eFPGA tied to OPB                                              | Hard core                              |

### **ASIC Development Tools**

- Design Entry

- Cadence Composer<sup>™</sup>, IBM Wizard<sup>™</sup>

- Simulation and Power Analysis

- Cadence, MTI ModelSIM<sup>™</sup>, Synopsys VSS<sup>™</sup>

- Synopsys DesignPower<sup>™</sup>, PowerCompiler<sup>™</sup>

- Logic/Physical Synthesis

- Cadence BuildGates<sup>™</sup>, IBM BooleDozer<sup>™</sup>

- Synopsys Design Compiler, Physical Compiler

- Test and Clock Synthesis

- Cadence DFTS, LogicVision ICBIST

- Static Timing Analysis

- IBM EinsTimer<sup>™</sup>, Synopsys PrimeTime<sup>™</sup>

- Post Layout Timing Analysis and Optimization

- IBM CMOSChks, ChipEdit, ALSIM, 3DNoise

# Swift Models and Software Simulation

- Based on Synopsys Smartmodel<sup>™</sup> functional simulation

- Created from Verilog RTL and netlist

- Use core level Swift model for SoC design

- PowerPC core customers can contact IBM Design Center for access.

- Simulator Configuration Guide for Synopsys Models, simcfg.pdf, at http://www.synopsys.com

### Power PC® 405EP Evaluation Platform

External Bus Connector for FPGA daughter board

#### Serial, Keyboard/Mouse, LAN

#### **RiscWatch trace tool connection**

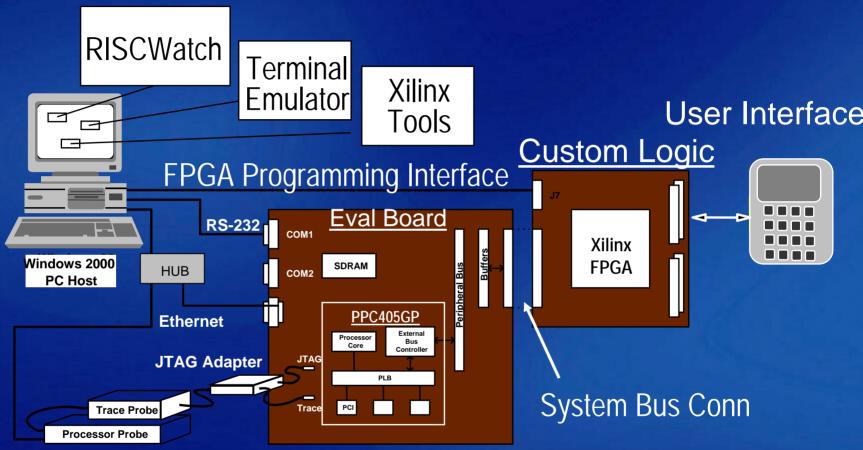

#### **Emulation System**

29

#### **Emulation System**

#### Eval Board

-PPC 405GP System-on-Chip

-COM I/O

-Ethernet port

-SDRAM

-PCI Slots

-ROM monitor ← RiscWatch

-OS Open

-Linux

#### **RISCWatch**

-GUI User Interface -User-Defined windows -Command files -JTAG interface to 405GP -Built in debug support

## Application Software Support

- Wind River Platform

- Tornado<sup>®</sup> and VxWorks<sup>®</sup> for IBM PowerPC<sup>®</sup>

- Windriver partner, Pingtel IP Phone Software

- Windriver partner, Micro PKI C Security Toolkit Designed for Embedded Devices

- MontaVista<sup>™</sup> Platform

- Embedded Linux for IBM PowerPC

- MontaVista ISV partner, Access Ltd Netfront<sup>®</sup> Information appliance software

#### **Portable Software Tips**

#### Category **Standard OS Open Source OS** API's Use standard API – **Application framework** software POSIX Open source drivers Drivers Device driver library and device driver development kit Make/Build **Application framework** Leverage porting and software and specific emulation kits conversion kits

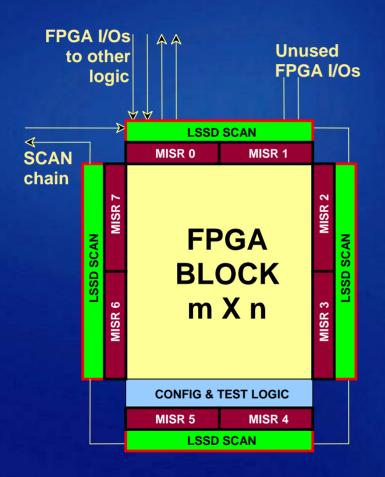

### More on Embedded FPGA's

- Collapse multiple designs into a single ASIC

- Families of chips w/ similar functions

- Design upgrades & added features post-tapeout

- Accommodate evolving industry standards

- Bug-fix capability for specific high-risk logic

- Control for dataflow

- New vs. reused logic

- Parallel design & verification

- Provide embedded debug & test circuitry on-demand

- Prototyping of design updates

- Customizing designs to unique customer requirements

#### **Embedded FPGA Block**

Cores are derivatives of Xilinx Virtex-II

architecture

- IBM methodology & toolset used for overall ASIC processing

- eFPGAs handled as custom hard cores

- Xilinx toolset used to configure, P&R, & time FPGA macros

- Xilinx basic FPGA fabric in IBM's 90nm

9SF fab process

- Virtex-II s/w base complete & in use

- Three sizes: 128, 256, 384 CLB's; 3, 5,

7 sq mm image

- Up to 400K programmable gates

### Summary

- IBM PowerPC<sup>™</sup> plus Xilinx Virtex-II<sup>®</sup> FPGA performance and flexibility

- Platform SoC or Platform FPGA options

- PowerPC Value

- Standard and open source OS platforms

- Compilers, simulation tools, development kits w/ real time debugging

- SoC peripheral cores via Core Connect architecture

- Xilinx FPGA Value

- Effective risk management for custom logic

- Large library of pre-validated core logic

- High speed, flexible interface support via RocketIO

- Integrated software development with real time logic development

- PowerPC + Virtex-II = Reduced design complexity and risk for faster TAT

**Agilent Technologies**

Altrum

# Thank You!

IBM

cadence

XILINX"

mable

The For The New Era P

Celóxica

The MathWorks

TF SUSTERIS BESS

TEXAS INSTRUMENTS

SYNOPSYS

NALLATECH

WIND RIVER

CMP

#### **Contacts and References**

(c) Copyright International Business Machines Corporation 2002 All Rights Reserved

#### Printed in the United States of America October 2002

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

PowerPC ®

PowerPC Architecture<sup>™</sup>

CoreConnect <sup>™</sup>

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

The IBM home page can be found at

http://www.ibm.com