#

# XC4000 Series Edge-Triggered and Dual-Port RAM Capability

XAPP 065 July 2,1996 (Version 1.0)

Application Note by S. K. Knapp

## Summary

The XC4000E and XC4000EX FPGA families provide distributed on-chip RAM. Select-RAM<sup>™</sup> memory can be configured as level-sensitive or edge-triggered, single-port or dual-port RAM. The edge-triggered capability simplifies system timing and provides better performance for RAM-based designs. The dual-port mode offers new capabilities and simplifies FIFO designs.

## Xilinx Family

XC4000E, XC4000L, XC4000EX, XC4000XL

#### The XC4000E FPGA family is a pin- and bitstream-compatible superset of the Xilinx XC4000 FPGA family. It provides increased performance, improved capabilities, and new features. The XC4000EX family of very large devices also includes all of the new features offered in the XC4000E.

Some of the more prominent new capabilities involve the distributed on-chip RAM found on XC4000-Series devices. Although XC4000E/EX FPGAs maintain all of the capabilities found on XC4000 devices, new capabilities include:

- Synchronous or edge-triggered RAM writing that simplifies timing and improves performance. Careful timing relationships between Address, Data, and Write-Enable are no longer required.

- Dual-port RAM mode that provides simultaneous read/ write capability. This mode is especially useful for building FIFOs and buffer memories. Dual-port RAM is always edge triggered.

- The ability to pre-initialize the contents of RAM on power-up. This simplifies the overall design in that RAM values are automatically defined. No additional logic is required to perform the initialization.

Table 1 describes the relative capabilities of the XC4000 and XC4000E/EX families.

## Table 1: RAM Capabilities of XC4000 and XC4000E/EX

| Feature                   | XC4000 | XC4000E/EX |

|---------------------------|--------|------------|

| On-chip RAM               | Х      | Х          |

| Level-sensitive RAM write | Х      | Х          |

| Single-port capability    | Х      | Х          |

| Dual-port capability      |        | Х          |

| Edge-triggered RAM write  |        | Х          |

| Initialized RAM data at   |        | X          |

| power-up                  |        |            |

## Demonstrates

Clocked or edge-triggered RAM Dual-port RAM

## Table 2: Storage Capacity for XC4000E/EX RAM Modes

| RAM Mode    | Capacity/CLB |

|-------------|--------------|

| Single Port | 32x1 or 16x2 |

| Dual Port   | 16x1         |

The dual-port capability comes at the price of decreased RAM capacity. Due to the way the dual-port RAM is implemented, and because only four address lines are available, dual-port mode has only half the effective storage capacity of single-port mode, as summarized in Table 2.

## XC4000-Series Conceptual Model

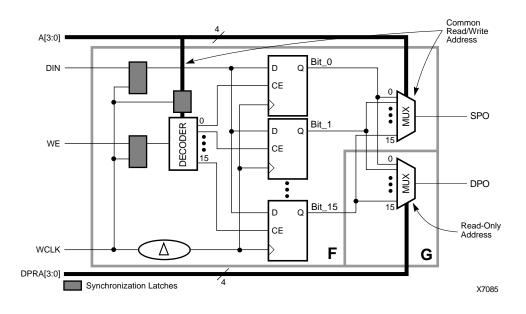

Figure 1 shows a conceptual model of the XC4000-Series RAM. This diagram will be used to describe the various edge-triggered and dual-port capabilities available within each logic block. In this example, the logic block is configured as a 16x1, dual-port, edge-triggered RAM.

This diagram is not intended to convey the actual circuit implementation, but rather to describe the functionality.

# **Edge-Triggered Write**

The XC4000 Series provides both level-sensitive and edge-triggered write capabilities. Both options are available for single-port mode, while dual-port mode is always edge-triggered. Most designers are familiar with level-sensitive RAM. This type of RAM is similar to most SRAM devices available on the market.

One disadvantage of level-sensitive RAM is that it requires a careful timing relationship between the Address, Data and Write-Enable signals. Maintaining such relationships inside an array-based device can be difficult, because the designer does not have direct control over the routing delays within the device.

## Figure 1: XC4000-Series Conceptual Model

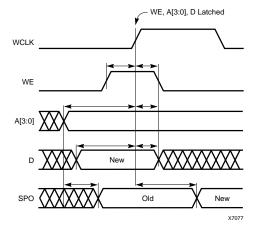

However, a better approach for system design is to use synchronous or edge-triggered RAM. Edge-triggered writing simplifies the RAM timing. Instead of a complex relationship between various timing parameters, XC4000-Series RAM timing operates like writing to a data register. Data and Address are presented. The register is enabled. Then a clock edge loads the Data into the register, as shown in Figure 2.

A write operation uses the signals described in Table 3. These signals are derived from Figure 1. The lower right corner of Figure 1—the shaded box labeled 'G'—should be ignored temporarily but is discussed later under "Dual-Port Mode."

During a Write operation, Data is presented on the D input. The write location is presented on the Address inputs, A[3:0]. The RAM block is enabled for writing by a logic High on the write-enable input, WE.

The Write Clock input, WCLK, can be configured as active on either the rising edge (default) or the falling edge. The rising edge will be used throughout these examples. On the rising edge of the Write Clock, the D, A[3:0], and WE inputs are captured, thereby synchronizing them to the clock.

A short delay, indicated by the delta symbol ( $_{\Delta}$ ) in Figure 1, allows the signals to propagate through the decoder logic that enables the appropriate flip-flop. The data is clocked

into the enabled flip-flop by the delayed clock edge. The new RAM data is available on the SPO output a short time later.

The Write Clock input to the logic block is the same input used to clock the CLB flip-flops, although it can be independently inverted. Consequently, the Write Clock input is best driven from one of the global clock buffers (BUFGP or BUFGS for the XC4000E, BUFGLS or BUFGE for the XC4000EX).

Figure 2: Edge-Triggered RAM Write Cycle

#### Table 3: Edge-triggered RAM Description

| Signal | I/O | Description                                                                                                                              |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| A[3:0] | I   | Address input for reading and writing<br>the RAM. The RAM data are available<br>on SPO.                                                  |

| D      | I   | RAM Data input.                                                                                                                          |

| WE     | I   | Write Enable input. When High, the RAM may be written with the data presented on the D input.                                            |

| WCLK   | I   | Write Clock input. Clocks the data into<br>the RAM when WE is High. Also cap-<br>tures and synchronizes the A[3:0], D,<br>and WE inputs. |

| SPO    | 0   | Single-port output from the RAM. The<br>RAM location is controlled by the<br>A[3:0] inputs. SPO is not controlled by<br>the WCLK input.  |

## **Dual-Port Mode**

Most RAMs have a single address port and a single output port. These are called single-port RAMs. However, some applications require more than one port. FIFOs are one example of an application that benefits from additional output and address ports.

In a FIFO, there are separate read and write addresses for the memory. A FIFO can be implemented using a singleport memory by multiplexing both the read and write addresses onto a single address port. This approach, however, prevents a simultaneous Read and Write operation. Either a Read or a Write operation can access the RAM at different times, but not both at the same time.

These extra multiplexers and their associated control logic add to the complexity of a RAM-based FIFO design. A dual-port RAM—one with two Address inputs and two outputs—would simplify a FIFO design.

Again, Figure 1 provides an example. The logic in the figure is configured as a 16x1 edge-triggered dual-port RAM. Data can be read and written using the A[3:0] address port and the RAM data appears on the SPO output, just as it would for a single-port RAM.

Simultaneously, data can be read—but not written—using the DPRA[3:0] address port and the RAM data appears on the DPO output. Operations with the DPRA[3:0] address port are independent of the A[3:0] address port. Consequently, a RAM location can be accessed simultaneously through two different locations using the two sets of address and data ports as described in Table 4.

## Table 4: Address Port Functionality

| Address Port | Operation      |

|--------------|----------------|

| A[3:0]       | Read and Write |

| DPRA[3:0]    | Read only      |

If both addresses point to the same location and a Write is performed using the A[3:0] inputs, data appears on SPO and then on DPO a short time later. The DPO output should be used as the primary data output for FIFO designs.

The dual-port mode signals include those shown in Table 3 plus a few additional signals described in Table 5.

# **Schematic Symbols**

Using the XC4000-Series edge-triggered and dual-port RAM capabilities requires special schematic symbols available within the XC4000E and XC4000EX libraries.

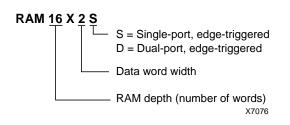

All edge-triggered RAMs have symbols that begin with 'RAM' and end with either 'S' or 'D'. Single-port edge-triggered RAMs end with 'S"; dual-port RAMs end with 'D'. If no letter is appended, the level-sensitive RAM is referenced. All dual-port RAMs are implicitly edge-triggered.

Figure 3 shows an example of RAM library symbol naming conventions.

## Table 5: Additional Signals for Dual-Port Mode

| Signal    | I/O                                                                                                                                     | Description                                                                                                 |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| DPRA[3:0] | I                                                                                                                                       | I Dual-Port Read Address (DPRA)<br>input for reading from the RAM.<br>The RAM data are available on<br>DPO. |  |

| DPO       | Output from the RAM. The RAM<br>read location is controlled by the<br>DPRA[3:0] input. DPRA[3:0] is<br>not controlled by the WCLK input |                                                                                                             |  |

## **Initializing RAMs**

The contents of an XC4000E RAM can be initialized at power-up. Initial contents are defined by attaching an 'INIT' attribute or property to the RAM symbol, as described in the schematic library guide.

If not defined, all XC4000-Series RAM contents are initialized to all zeros, by default.

**NOTE:** RAM initialization occurs *only* during configuration. The RAM contents are not affected by Global Reset.

## **Software Support**

The edge-triggered and dual-port capabilities are supported in XACT*step* version 5.2 or later. A software update may be required.

# **XILINX**<sup>®</sup> The Programmable Logic Company<sup>ss</sup>

#### Headquarters

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 U.S.A.

Tel: 1 (800) 255-7778 or 1 (408) 559-7778 Fax: 1 (800) 559-7114

Net: hotline@xilinx.com Web: http://www.xilinx.com

#### North America

Irvine, California (714) 727-0780

# Englewood, Colorado (303)220-7541

Sunnyvale, California (408) 245-9850

Schaumburg, Illinois (847) 605-1972

Nashua, New Hampshire (603) 891-1098

Raleigh, North Carolina (919) 846-3922

West Chester, Pennsylvania (610) 430-3300

Dallas, Texas (214) 960-1043

#### Europe

Xilinx Sarl Jouy en Josas, France Tel: (33) 1-34-63-01-01

Net: frhelp@xilinx.com Xilinx GmbH Aschheim, Germany Tel: (49) 89-99-1549-01

Net: dlhelp@xilinx.com Xilinx, Ltd. Byfleet, United Kingdom Tel: (44) 1-932-349401 Net: ukhelp@xilinx.com

#### Japan

Xilinx, K.K. Tokyo, Japan Tel: (03) 3297-9191

#### Asia Pacific

Xilinx Asia Pacific Hong Kong Tel: (852) 2424-5200 Net: hongkong@xilinx.com

© 1996 Xilinx, Inc. All rights reserved. The Xilinx name and the Xilinx logo are registered trademarks, all XC-designated products are trademarks, and the Programmable Logic Company is a service mark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patent, copyright or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. cannot assume responsibility for the use of any circuitry described other than circuitry entrely embodied in its products. Products are manufactured under one or more of the following U.S. Patents: (4,847,612; 5,012,135; 4,967,107; 5,023,606; 4,940,909; 5,028,821; 4,870,302; 4,706,216; 4,758,985; 4,642,487; 4,695,740; 4,713,557; 4,750,155; 4,821,233; 4,746,822; 4,820,937; 4,783,607; 4,855,669; 5,047,710; 5,068,603; 4,855,619; 4,835,418; and 4,902,910. Xilinx, Inc. cannot assume responsibility for any circuits shown nor represent that they are free from patent infringement or of any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made.