# **Tornado<sup>™</sup> BSP** Training Workshop

Wind River Systems, Inc. 1010 Atlantic Avenue Alameda, CA 94501

510-749-2148 FAX: 510-749-2378 training@wrs.com http://www.wrs.com/training

**ã** Wind River Systems, Inc. 1997 Copyright © Wind River Systems, Inc. 1986 - 1998 Version 1.0.2, April 1998

ALL RIGHTS RESERVED. No part of this publication may be reproduced in any form, by photocopy, microfilm, retrieval system, of by any other means now known or hereafter invented without the prior written permission of Wind River System, Inc.

This document is designed to support the Tornado BSP Training Workshop class. It is not designed as a stand-alone document, nor can it substitute for Wind River Systems BSP documentation. For information about the Wind River Systems training program, contact:

Training Department Wind River Systems, 1010 Atlantic Avenue Alameda, CA 94501 Wind River Systems S.A.R.L. Inc. 27, Avenue de la Baltique Bâtiment B4, LP739 91962 Les Ulis Cedex France

510-749-2148 (phone) 510-749-2378 (fax) EMAIL: training@wrs.com

33-1-69-07-78-78 (phone) 33-1-69-07-08-26 (fax)

Wind River Systems Japan/Asia-Pacific Pola Ebisu Bldg. 11F 3-9-19 Higashi Shibuya-ku Tokyo 150 Japan +81-03-5467-5900 (phone)

+81-03-5467-5877 (fax)

VxWorks<sup>®</sup> and Wind River Systems<sup>®</sup> are registered trademarks and Tornado, wind, windX, WindPower, WindNet, WindNet SNMP, WindView, VxGNU, VxGDB, VxSim, VxVMI, VxMP, and MicroWorks are trademarks of Wind River Systems, Inc. All other trademarks cited herein are the properties of their respective owners.

# **Course Prerequisites**

- General prerequisites:

- Solid knowledge of C programming, and familiarity with general assembly level programming principles.

- Experience writing device drivers using the C programming language.

- Basic understanding of standard embedded systems hardware.

- Basic understanding of VxWorks and debugging techniques.

- Basic understanding of makefiles and building executable images.

- Functional knowledge of host platform and Tornado tools:

- UNIX: user-level knowledge of make, csh, man, vi or emacs, etc.

- Windows NT: user-level knowledge of Windows NT graphical and command-line user interfaces, file systems, and standard Windows editor.

- Tornado tools: configuration of a target server to support various back end connection strategies, practical experience using CrossWind, and basic user-level knowledge of other Tornado tools.

# **Course Objectives**

- Overview of BSP responsibilities and integration issues.

- Choose a BSP development strategy.

- Manage a BSP development environment.

- Choose BSP development tools.

- Use WDB agent for BSP development.

- Perform pre-kernel initialization.

- Perform post-kernel initialization.

- WRS guidelines for device driver design.

- Manage interrupts in a BSP.

- Integrate timer drivers.

- Manage memory.

- Integrate serial communication controller for debugging.

- Build and support VxWorks images such as:

- Loadable images

- ROM-based images (compressed/uncompressed)

- ROM-resident images

- Writing and testing WRS a compliant BSP.

# What Course Does Not Cover

- Writing generic device drivers (network, SCC, SCSI, etc.). Material covered in Tornado Device Driver Workshop.

- Using Tornado tools and non-BSP VxWorks facilities. Material covered in Tornado Training Workshop.

- Architecture port issues.

- Specific vendor hardware:

- Target devices.

- Non-WRS development tools.

# **Table of Contents**

|                                                    | <u>Chapter</u> |

|----------------------------------------------------|----------------|

| Overview                                           | 1              |

| Integration Issues                                 |                |

| VxWorks Boot Sequence                              |                |

| Tornado Directory Structure                        |                |

| Conventions and Validation                         |                |

| System Hardware                                    | 2              |

| Overview                                           |                |

| Architecture Issues                                |                |

| Bus Systems                                        |                |

| Memory                                             |                |

| Devices                                            |                |

| BSP Development Issues                             |                |

| Development Cycle Overview                         |                |

| Development Environment                            |                |

| Strategies For Getting Started                     |                |

| <b>Pre-Kernel Initialization Overview</b>          | 4              |

| Pre-Kernel Initialization Sequence                 |                |

| BSP Files                                          |                |

| Building VxWorks Images                            |                |

| <b>Pre-Kernel Initialization - Boot Specific C</b> | Code5          |

| Boot Specific vs. Generic Code                     |                |

| romInit.s : romInit()                              |                |

| PIC and VxWorks                                    |                |

| <pre>bootInit.c : romStart()</pre>                 |                |

| <pre>sysALib.s : sysInit()</pre>                   |                |

|                                                    | - AWKndI       |

| 6                                                  |                |

CI

| Pre-Kernel Initialization - Generic Code6                  |

|------------------------------------------------------------|

| Generic Code Overview                                      |

| sysHwInit()                                                |

| Activating the Kernel                                      |

| <b>Pre-Kernel Initialization - Debugging With Tornado7</b> |

| Overview                                                   |

| Using the WDB Agent                                        |

| SCC Support For WDB Agent                                  |

| Debugging Techniques                                       |

| Memory                                                     |

| Overview                                                   |

| Configuring Memory                                         |

| MMU Issues                                                 |

| Cache Issues                                               |

| Memory Probes                                              |

| Managing Interrupts9                                       |

| Overview                                                   |

| Installing ISRs                                            |

| Supporting Interrupt Libraries                             |

| Initializing An Interrupt Controller                       |

| Optional Interrupt Support                                 |

| Timers                                                     |

| Overview                                                   |

| System Clock                                               |

| Auxiliary Clock                                            |

| Timestamp                                                  |

| Completing the BSP - Finishing the Port                    |

| Overview                                                   |

| Remaining BSP Routines                                     |

| Device Driver Issues                                       |

| Final BSP Files                                            |

| Validation Test Suite                                      |

| 7                                                          |

) |

........

# Chapter - 1

#### Overview

#### Overview

1.1 Integration Issues

VxWorks Boot Sequence

**Tornado Directory Structure**

Conventions and Validation

# What is a **BSP**?

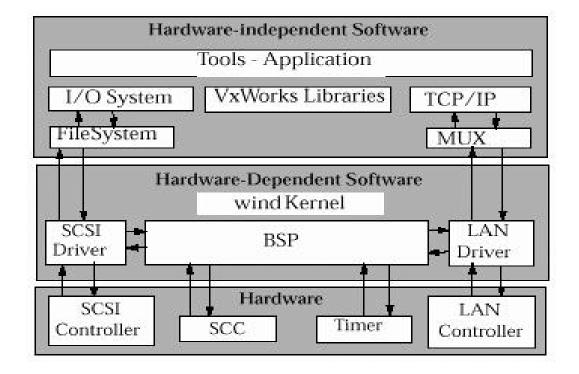

- Provides VxWorks with primary interface to hardware environment.

- BSP Responsibilities:

- Hardware initialization on power-up.

- Support for VxWorks access to hardware drivers.

- Integration of hardware-dependent and hardware-independent software in VxWorks.

- Components consist of:

- Source, include, and make files.

- Derived files.

- Binary driver modules.

- May be validated to be WRS compliant.

# What a BSP is Not

- A BSP is not a hardware driver:

- A hardware driver accesses hardware.

- Hardware drivers are classified as generic or BSP specific:

- Generic drivers manage devices which can be moved from one target environment to another (e.g. LAN chip).

- BSP drivers manage devices which are specific to the target environment (e.g. interrupt controller).

- BSP developer responsible for:

- Complete support for BSP specific drivers.

- Integration of generic device drivers.

#### **BSPs and VxWorks**

# BSP Responsibility: Hardware Initialization

- VxWorks boot sequence specifics will vary with processors and hardware environments.

- Common initialization requirements:

- Provide code at specific location in memory which processor will jump to on reset or power-up.

- Set processor in a specific state.

- Initialize memory and memory addressing.

- Disable interrupts.

- Pass control to additional bootstrapping code.

- Load required VxWorks segment(s) into RAM.

- Place hardware in quiescent state before initializing VxWorks kernel.

# BSP Responsibility: VxWorks Access To Hardware Drivers

- Some driver support is provided by BSP. Examples:

- Driver defines ISR(s), but BSP connects ISR(s) to interrupt vector table.

- BSP creates structures (objects) which are passed to driver for initialization.

- Offset constants and access macros for hardware registers provided by BSP and used by driver.

- Provides portability for hardware driver code.

- Device configuration management:

- Access to full range of device features (possibly at a later time).

- Separate development/production configurations.

# BSP Responsibility: Integration of Hardware Dependent Software

- Provides code flexibility and portability:

- Compile-time flexibility.

- Run-time portability.

- Compile-time flexibility:

- Uses preprocessor macros to customize system.

- Provides ability to produce optimized modules without changing source code.

- Run-time portability:

- Uses pointers to access routines.

- Provides portability for compiled object modules.

# **BSP Components: Primary Files**

- Primary BSP files:

- Source files.

- Include files.

- Make files.

- Source files:

- Generic code is written in C. Architecture specific and performance optimized code is assembly.

- Include files:

- All includes and definitions specific to a CPU board are localized in two files.

- Make file:

- Controls building of all images.

# **BSP Components: Derived Files**

- Derived BSP files are created using:

- Primary BSP files.

- Driver source files.

- Modules in VxWorks archive libraries.

- Derived BSP files are classified as:

- Hardware initialization object modules.

- VxWorks boot object modules.

- VxWorks images.

- VxWorks binary symbol table.

- A complete BSP port will generate all of these files.

- End users will recreate some of these files when configuring the system.

# **BSP Development**

- Development should occur in incremental steps:

- First set up development environment (down-load path(s), debug strategies, etc.).

- Write pre-kernel initialization code.

- Optionally activate WDB agent and Tornado tools using polled serial or ethernet interface.

- Start minimal VxWorks kernel adding support for a system clock, and install interrupts.

- Complete BSP providing all necessary support for hardware environment (full network support etc.).

- Clean-up, testing and documentation.

- Course material will be presented following this sequence as closely as possible.

## **BSP Development - cont.**

- Development time may be reduced by purchasing:

- The BSP Developer's Kit.

- Appropriate reference BSP.

- BSP Developers Kit provides:

- A Validation Test Suite (VTS).

- Template BSP (all architectures).

- Template device drivers.

- Purchasing a reference BSP which most closely matches target environment:

- Specific device drivers which are not part of reference BSP can also be purchased from WRS.

- Reference BSP obtained when Tornado is purchased.

# **BSP** Validation

- BSP validation:

- WRS validated.

- Non WRS validated.

- A WRS validated BSP:

- Classified as Tornado Certified, and may be distributed displaying this information.

- Contact WRS to obtain validation requirements.

- BSP validation uses a Validation Test Suite (VTS):

- Automated test suite which runs on host and target to exercise BSP and report defects.

- Included in BSP Developer's Kit.

- VTS distribution includes source to allow extension.

#### Overview

Integration Issues

1.2 VxWorks Boot Sequence

**Tornado Directory Structure**

Conventions and Validation

# VxWorks Image Types

- There are three classes of VxWorks images:

- Loadable images.

- ROM-based images compressed/uncompressed.

- ROM-Resident images.

- Loadable images are loaded into RAM by boot code.

- Boot code is "burned" into ROM or Flash.

- Boot code is a stand-alone VxWorks application.

- ROM-based images load themselves into RAM from ROM or Flash.

- ROM-resident images execute out of ROM or Flash.

- Only the data segment of the VxWorks image is loaded into RAM.

# Some Terminology

- VxWorks boot image A VxWorks image designed to load another VxWorks image containing application code (often referred to as "boot code").

- "Burned" into ROM or loaded into Flash.

- May execute in ROM/Flash (ROM-resident).

- May execute out of RAM.

- VxWorks image A VxWorks image containing "end-user" code. Sub-types:

- Loadable VxWorks image VxWorks images loaded by VxWorks boot image.

- VxWorks ROM image VxWorks image "burned" into ROM or loaded into Flash. May execute in ROM/Flash (ROM-resident) or RAM.

# **VxWorks Startup Sequence**

- The sequence of events which occur at power-up are a function of the type of VxWorks image which will run.

- The initial phase of the start-up sequence is the same across all VxWorks image types.

- Processor is "jumped" to the entry point of boot-strap code in ROM or Flash. This code:

- Disables interrupts (via the processor).

- Initializes target memory.

- Loads appropriate VxWorks image segments.

- Jumps to code to place target in a quiet state.

- Various startup sequences are discussed next.

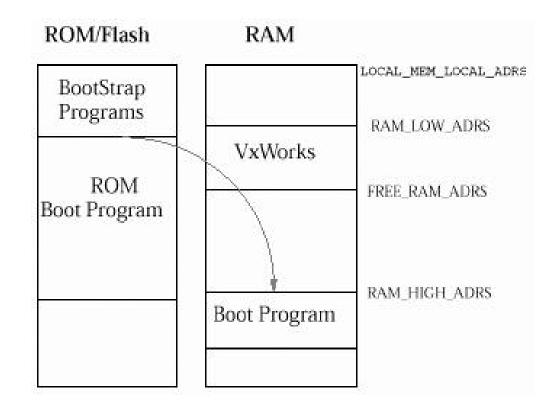

# Boot Sequence - Loadable VxWorks Image

• Bootstrap code executes and loads text and data segments of boot code (from ROM or Flash) into RAM.

Scenarios are:

- Boot code compressed Decompression during copy

- Boot code uncompressed Copy

- Boot code is ROM-resident Copy data segment only

- Boot program executes and loads VxWorks image into RAM. Jumps to VxWorks load point.

- System initialization code statically linked into loaded VxWorks image executes and completes initialization.

#### Loadable VxWorks Image

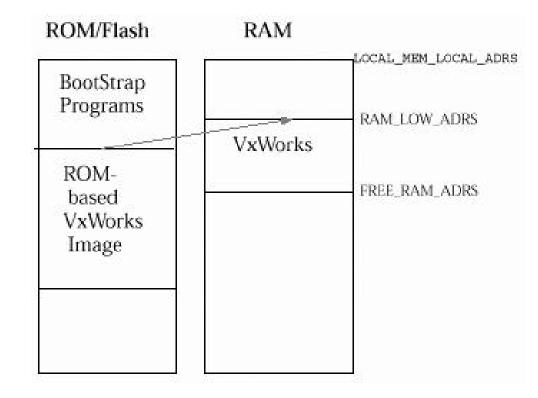

# Startup Sequence - ROM-based VxWorks Image

• Bootstrap code executes and loads text and data segments of VxWorks (from ROM or Flash) into RAM.

Scenarios are:

- VxWorks compressed Decompression during copy

- VxWorks uncompressed Copy

- Control transfers to VxWorks initialization code in RAM.

- System initialization code statically linked into VxWorks image executes (in RAM) and completes initialization.

#### **ROM-based VxWorks Image**

# Startup Sequence - ROM-resident VxWorks Image

- Bootstrap code executes and loads data segment of VxWorks image (from ROM or Flash) into RAM.

- Control branches to VxWorks initialization code in ROM or Flash.

- System initialization code statically linked into VxWorks image executes (in ROM or Flash) and completes initialization.

#### **ROM-resident VxWorks Image**

# Startup Sequence - VxWorks Initialization

- After ("end-user") VxWorks segment(s) are loaded into RAM, system initialization code statically linked into VxWorks image executes to complete the boot sequence.

- This code will:

- Place hardware environment in a quiet state.

- Initialize and start the wind kernel.

- Spawn a task to complete system initialization.

- System initialization task will initialize support for end-user specified facilities, and start the end-user's application.

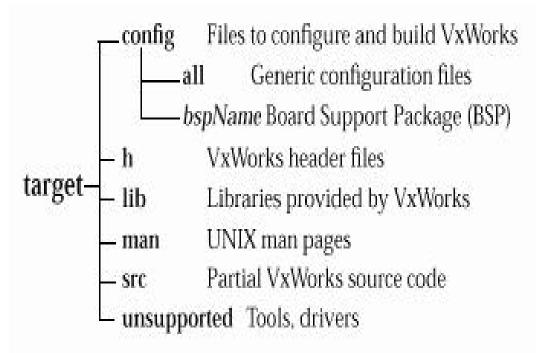

# **Overview Integration Issues** VxWorks Boot Sequence 1.3 Tornado Directory Structure Conventions and Validation

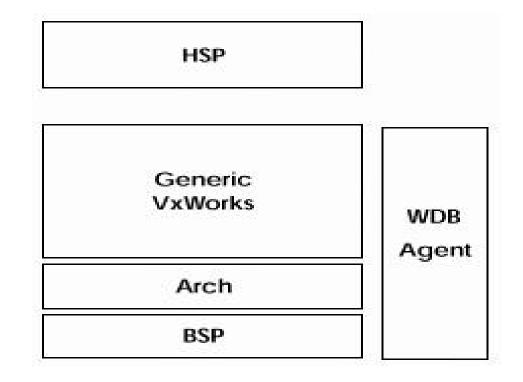

# **Tornado Modularity**

- Tornado is composed of a set of modular components.

- Modularity aids in portability, flexibility of use, and maintenance.

- Tornado modules are:

- Host Support Package (HSP).

- Generic (target independent) VxWorks.

- Architecture Module.

- Board Support Package.

- Wind Debug Agent (WDB Agent).

- Tornado modules have been designed to minimize interdependence.

#### **Tornado Modularity**

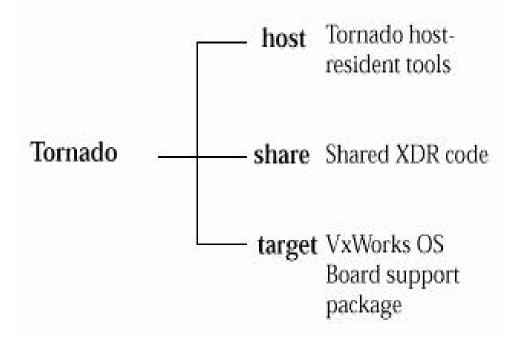

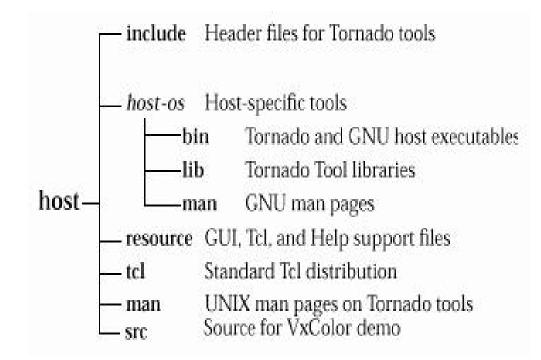

# Tornado Modularity and the Tornado Directory Tree

- Files which make up Tornado are organized to reflect Tornado's component modularity.

- At the highest level files (relevant for BSP development) are separated into host and target directories.

- All BSP specific files are in the target directory. However, many tools useful in developing a BSP are in the host directory.

- Files which will be modified in developing a BSP are in a configuration sub-directory of the target directory.

#### **Tornado Directory Tree**

#### **Host Directory Tree**

#### **Target Directory Tree**

### **BSP Relevant Files**

- All code which executes at power-up is in files within the config directory.

- BSP code vs. generic driver code:

- Generic device driver code is designed to be usable with multiple BSPs (network drivers, serial drivers, etc.).

- BSP (device driver) code is tightly coupled to the target environment and is not designed to be used with other BSPs.

- BSP specific code will always reside in ../<bspName>.

- Generic device driver code not supplied by WRS will reside in the <br/> <br/> spName> directory or a subdirectory of <br/> <br/> spName>.

#### Overview

**Integration Issues**

VxWorks Boot Sequence

**Tornado Directory Structure**

1.4 Conventions and Validation

### **BSP Conventions and Validation**

- BSP conventions and validation procedures are designed to help guarantee integrity of BSP.

- BSP conventions fall into categories:

- Coding conventions

- Documentation guidelines.

- BSP packaging.

- Driver guidelines.

- Validation test:

- Package validation.

- Installation test.

- Functional test (VTS).

- Code review process and WRS validation process.

### Summary

- BSP responsible for supporting system hardware environment:

- Initialization of hardware environment.

- VxWorks/application access to hardware drivers.

- Hardware/software integration.

- Provides VxWorks with primary interface to hardware environment.

- Components consist of:

- Source, include, and make files.

- Derived files.

- May be validated to be WRS compliant.

# Chapter - 2

#### System Hardware

#### **System Hardware**

2.1 Overview

Architecture Issues

Bus Systems

Memory

Devices

#### Overview

- BSPs have responsibilities for all components in the hardware environment.

- Embedded hardware categories:

- Architecture specific (caches, MMUs, interrupt controllers, and floating point hardware).

- Bus specific (Bus controllers, and bus bridges).

- Memory specific (memory controllers, and chips).

- Devices (architecture/bus/memory independent).

- Support issues:

- Initialization.

- Access.

#### **System Hardware**

Overview

2.2 Architecture Issues

Bus Systems

Memory

Devices

### **BSPs and CPUs**

- Libraries for managing CPUs are part of the Tornado architecture module.

- Some CPU specifics will be relevant for BSP development:

- MMU Support

- Cache Issues

- Interrupt Handling

- Floating-Point Support

- Many of these specifics will be important during the initialization phase of booting a VxWorks image.

## MMUs

- Memory Management Units control memory access for:

- Allocating/de-allocating memory.

- Resolving cache coherency issues.

- Write protecting memory.

- Virtual memory swapping.

- Paging and segmentation.

- Garbage collection.

- Requires RAM resident translation tables which map physical memory into a virtual memory address space.

- May be inappropriate for real-time applications due to latency increases and memory consumption.

- Unit is often on the same ASIC as the CPU.

## **MMU Support**

- Booting VxWorks:

- MMU disabled until the wind kernel is activated.

- Build translation tables.

- Enable MMU.

- In VxWorks a task does not include a translation table as part of its context:

- Tasks do not reside in virtual memory.

- Default virtual memory maps are global and flat.

- MMU may be managed dynamically with:

- Bundled MMU library.

- Optional virtual memory management product (provides programmatic access to MMU).

## Caches

- Fast memory interface between CPU and main memory.

- Reduces read/write access time for CPU and local bus activity.

- Most modern processors support separate data and instruction caches.

- Cache is accessed in quantized units called cache lines.

- Cache modes:

- Write through Data written to cache by processor flushed to main memory.

- Copyback Writes only to cache, conserves processor bandwidth.

#### **Caches - continued**

- Cache is located:

- On the same ASIC as the CPU L1 cache

- External to the CPU ASIC L2 cache

- Backside L2 cache External L1 cache (with special bus to processor).

- Some architectures provide cache management instructions, others bundle cache management with virtual memory support facilities.

- If cache is enabled, it is examined by the CPU for each memory access:

- If data is there cache hit.

- If data is not there, access main memory- cache miss.

#### **Cache Issues**

- Cache coherency:

- Ideally cached information mirrors main memory.

- Bus master or device with DMA support may update main memory without updating cache.

- CPU may update cache without updating main memory, making information in main memory stale.

- To maintain cache coherency:

- Cache needs to be flushed when updated by CPU.

- Cache needs to be invalidated (and updated) when main memory is modified by bus master or DMA transfer.

- Snooping circuitry.

- Copyback with snooping is fastest configuration.

## **Cache Support**

- Booting VxWorks:

- Cache(s) disabled until the hardware environment is placed in a quiet state.

- Invalidate and configure cache mode.

- Enable cache(s) (before wind kernel is activated).

- Provide cache coherency for VxWorks:

- Data cache / RAM Bus master and DMA access to RAM.

- Instruction cache / data cache Loader, debugger, and ISR connection routines.

- Shared cache lines Multiple task access to cache.

- When MMU is enabled, cache management and mode control are supplied by an MMU library.

#### **Cache Support - continued**

- Cache coherency is maintained:

- Map off-board addresses as non-cacheable.

- MMU enabled Routine to allocate cache aligned memory marked as non-cacheable (returned cacheable).

- MMU not enabled Cache library support to flush and invalidate cache when necessary.

- Architecture may have more than one cache implementation. Hardware environment could then support multiple cache systems.

- BSP must supply support for selecting the appropriate cache libraries.

- Linker must include needed cache library modules.

## **Interrupt Handling**

- Hardware interrupt request and acknowledgment transactions are specific to:

- Hardware requesting interrupt service.

- CPU.

- System bus protocol(s).

- Hardware device will:

- Determine which interrupt service is requested.

- Terminate device interrupt request upon IACK or device access.

- CPU will determine number of external interrupts and interrupt levels supported using external interrupt lines and/or interrupt controller.

#### **Interrupt Handling - continued**

- IACK cycles are a function of local bus protocol:

- Vectored Automatic acknowledgment.

- Autovectored Acknowledgment done in software.

- CPU will determine which ISR to execute based on:

- External interrupt line activated.

- Interrupt select register of interrupt controller.

- Interrupt select register on device.

- Combinations, often requiring interrupt service de-multiplexing in software.

- CPU will reset interrupt status info after ISR completes:

- Bits in a CPU status register.

- Interrupt mask on external interrupt controller.

## Interrupt Handling Issues

- Designing interrupt scheme for hardware environment:

- Interrupt priority levels.

- Association of interrupts with devices and/or device service requests.

- Number of ISRs De-multiplex services in single ISR.

- Hardware support facilities:

- CPU (and interrupt controller when present).

- Device specific (enable/disable, IACKs, etc.).

- Interrupt service routines:

- Latency.

- Interrupt context and hardware negotiation.

- Connecting.

## **Interrupt Circuitry Guidelines**

- To minimize latency in handling interrupts, design efficient interrupt circuitry.

- Choose devices which provide interrupt vectors, with different vectors for each requested service. If not possible, one vector for device.

- Ability to enable/disable each interrupt source separately.

- Device interrupt control register.

- Interrupt controller.

- Well documented and diagramed interrupt vector scheme.

### **Interrupt Handling Support**

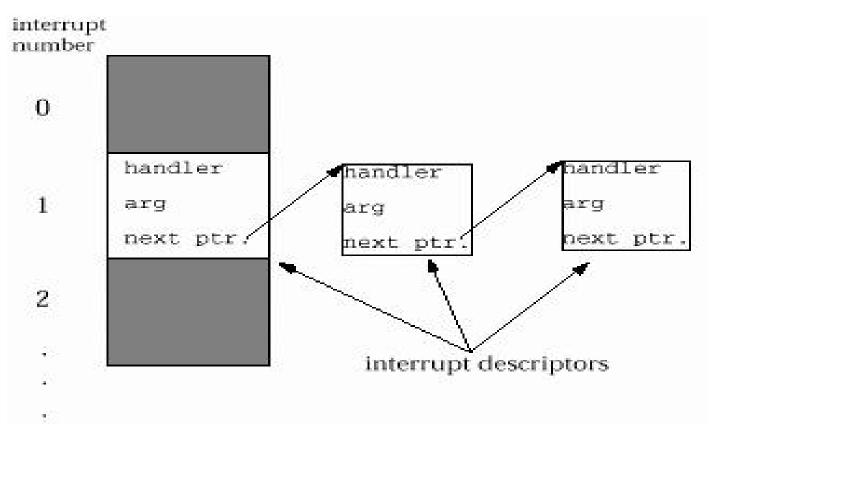

- VxWorks uses an interrupt table:

- ISRs must be connected to unique interrupt vectors after wind kernel is started.

- Table contains addresses for interrupt handlers.

- VxWorks is interrupt aware, preventing the OS from providing blocking services at interrupt time.

- Device interrupts must be disabled before kernel is activated, and enabled after ISRs are connected.

- Architecture and device driver libraries:

- Provide ISR code.

- Provide hardware interrupt management code.

### **Interrupt Handling Support -continued**

- A BSP:

- Disables device interrupts at system start-up.

- Connects ISRs to interrupt table.

- Supplies interrupt level/vector bindings to devices.

- Supplies addresses and control values associated with hardware interrupt status and control registers.

- Supplies routine which transfers control to boot code if an ISR throws an exception.

- BSP interrupt support should make device drivers as flexible as possible so they can be reused in hardware environments with different interrupt structures.

## **Floating Point Support**

- Support for floating-point operations:

- Floating-point/math co-processor(s).

- Software emulation.

- VxWorks contexts do not save/restore floating-point registers by default:

- Tasks allow an optional context extension which will include floating point registers.

- ISRs and exception handlers use bundled routine to programmatically manage floating-point registers.

- Architecture is responsible for floating-point support.

- Some BSPs will have configuration macros for FPU or software floating-point emulation.

### Additional Architecture Considerations

- Additional architecture issues which may impact a BSP:

- Big-endian/little-endian byte ordering.

- Processor specific initialization.

- Register and memory alignment.

- Addressing mode constraints.

- TAS operations and external bus access.

- Any of these issues may require BSP configuration macros to be defined.

#### **System Hardware**

Overview

Architecture Issues

2.3 Bus Systems

Memory

Devices

### **Bus Systems**

- Buses are classified relative to the processor:

- Local bus (processor bus).

- External buses (all others).

- Hardware environment may have:

- Multiple external bus systems.

- No external bus system.

- Bus system characteristics:

- Cycles ((a)synchronous, multiplexed, etc.).

- Arbitration (bus-locking, priority levels, etc.).

- Data transfers (memory-mapped, I/O mapped, etc.).

- Data properties (width, big/little endian, etc.).

- Interrupt policies (generation, IACK, routing, etc.).

### **Bus System Issues**

- BSP developer will need to be aware of bus protocols:

- Data transfer rates and formats.

- Bus requirements for DMA transfers.

- Interrupt protocols.

- For hardware environments with multiple buses, bridge chips may connect the busses, and provide an interface for inter-operability:

- Data transfer.

- Interrupt services.

- Bus system initialization:

- Minimum initialization to boot VxWorks.

- Complete initialization to support application.

### **Bus System Support**

- Bus systems and bus bridges have device drivers.

- Generic device drivers should be decoupled from bus specific issues.

- A BSP provides configuration and access support for:

- Bus drivers.

- Bus bridge drivers.

- Generic drivers for bus resident devices.

- A BSP is responsible for bus initialization:

- Bootstrap code identifies local bus speed, initializes local CPU bus, and necessary bus bridges.

- Boot code/VxWorks completes initialization, paricularly support for external buses.

#### **System Hardware**

Overview

Architecture Issues

**Bus Systems**

2.4 Memory

Devices

### **Memory Types**

- Memory types traditionally supported by embedded systems:

- RAM Random Access Memory

- ROM Read Only Memory

- Non-Volatile memory NVRAM and Flash.

- Memory types represent different technologies with different access characteristics, capabilities, and costs.

- Each memory type itself has multiple sub-types.

- Embedded systems will typically use some or all of these memory types.

#### **Memory Access**

- Memory is accessed via uniquely addressed locations (which may be mapped to a separate address space).

- A memory controller provides hardware support allowing the CPU to access memory. Provides:

- Address decode logic.

- Timing control.

- Memory bus interface support.

- Control of memory mapped devices.

- To access memory mapped addresses in a different physical address space, the hardware environment may have a separate memory controller ASIC.

- Hardware environment may have multiple maps.

### **Memory Access Issues**

- Memory access issues:

- Initialize memory hardware.

- Provide support for software access.

- Initializing memory hardware:

- Enable memory controller.

- Enable memory chips.

- Enable bridge/memory controller(s).

- Check integrity of memory.

- Supporting software access:

- Initialize dynamic memory management facilities.

- Maintain integrity of system/application memory pools.

### **Memory Access Support**

- Memory access:

- Hardware support.

- Software support.

- Hardware support:

- Initialization to load ROM code into RAM performed at powerup.

- Remainder of memory hardware initialized by pre-kernel initialization code in VxWorks.

- Software support:

- Management of virtual memory maps.

- Initialize partition library after kernel is activated.

- Enable and initialize MMU after kernel is activated.

## RAM

- Random Access Memory:

- Dynamic RAM (DRAM)

- Static RAM (SRAM)

- DRAM

- Primary storage technology.

- Store/hold capacitor technology.

- Limited read/write cycle times.

- Refresh cycles required.

- SRAM

- Most often used for cache storage, often on CPU chip

- Flip-flop technology, fast read/write cycle times.

- No refresh cycles.

# **RAM Support**

- RAM configuration:

- Main memory.

- Cache memory.

- Main memory RAM configuration:

- Zeroed at power-up for cold-boot to prevent parity errors.

- Configured and enabled by ROM code at system power-up.

- Cache memory RAM configuration:

- Usually disabled at power-up, enabled by VxWorks pre-kernel initialization code.

- Provide cache management libraries.

# ROM

- Read Only Memory types:

- Programmable ROM (PROM).

- Erasable Programmable ROM (EPROM).

- Electrically Erasable PROM (EEPROM).

- ROM properties:

- Non-volatile. Modified using a ROM programmer.

- Usually longer access times than DRAM/SRAM.

- Memory controller interfaces ROM to CPU.

- Non-volatile property allows:

- System boot code storage.

- Hardware environment configured to jump to a ROM address at power-up.

# Flash

- Flash is non-volatile memory which can be modified programmatically.

- Used as a "silicon" hard disk:

- System boot code storage.

- Hardware environment configured to jump to a flash address at power-up.

- Maintaining data integrity during power-outs.

- Access times slightly slower than DRAM but faster than ROM.

- Flash memory cells have a finite number of erase/ program cycles (~10,000 100,000).

#### Flash vs. PROM

- Flash and ROM use similar memory cell technology:

- Storage transistor employs transistor tunnelling.

- No battery to provide non-volatility.

- Access times are roughly the same.

- Flash technology requires lower voltage to erase/ program than PROM.

- Flash power supply unit allows flash to be modified without being removed from hardware environment.

- Contents may be modified over a network interface.

- Contents may be modified by application code.

- Many flash chips support configurable write protection.

# Flash/PROM Support

- Flash/PROM support facilities:

- At system start-up.

- For application code.

- System start-up support:

- Code executing out of flash/PROM in Tornado tree.

- Makefile support to build boot code.

- Flash file system to load VxWorks from flash.

- Minimum capacity PROM.

- Application code support:

- Code (driver/file system) to uniformly access flash.

- Large capacity PROM for ROM-resident and un-compressed VxWorks/boot code images.

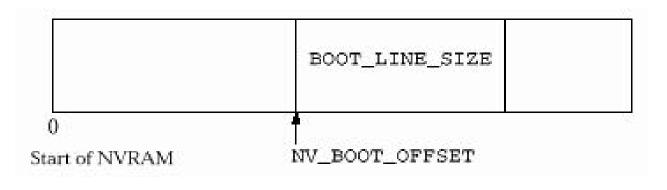

# NVRAM

- Non-volatile RAM:

- Non-volatility usually provided by battery.

- May be implemented using CMOS RAM, battery-backed SRAM, or flash.

- Units may contain a programmable time-of-day (TOD) clock:

- TOD information is stored in NVRAM.

- Used to store boot parameters for VxWorks image:

- VxWorks boot parameters may use up 255 bytes.

- If a hardware environment does not have NVRAM, boot parameters are statically linked into boot code.

#### **System Hardware**

Overview

Architecture Issues

**Bus Systems**

Memory

2.5 Devices

# **Embedded System Devices**

- Generic devices are independent of architecture, buses, and memory hardware.

- Typical devices:

- Timers.

- Serial Communication Controllers (SCC).

- Network interfaces.

- SCSI controllers.

- Custom ASICs (DSP chips, etc.)

- Devices should support:

- Read/write access.

- Any mandatory access timing requirements.

# Timers

- Hardware timers are used for:

- System clock interrupt (mandatory).

- Auxiliary clock for high speed polling.

- Timestamp for WindView.

- TOD clocks ("Real Time Clocks" RTCs).

- Timers operate in one of three modes:

- Periodic interrupt.

- One-shot interrupt.

- Timestamp.

- Timer use dictated by mode(s) supported by hardware.

- Timers are initialized after the kernel is activated.

#### Timers - cont.

- The three modes for timer operation are:

- Periodic interrupt Counts up/down to programmed terminal count, generates interrupt, resets counter.

- One-shot interrupt Counts up/down to programmed terminal count, generates interrupt, disables counter.

- Timestamp Counts up/down to maximum count, generates interrupt to log counter rollover, restarts count. Unlike periodic interrupt, counter is polled to obtain high-fidelity timestamp, interrupt is only used to mark counter rollover.

- TOD clocks will also contain date information.

# **Serial Communication Controllers**

- SCCs used as:

- Download/debug path during BSP/application development.

- Communication channel for application.

- Support for interrupt and polled mode operation:

- System level debugging (pre/post kernel).

- Task level debugging (post kernel).

- Dual level debugging (post kernel).

- In polled mode, serial interface can be used for system level debugging prior to kernel activation.

- For pre-kernel system level debugging serial port is accessed by WDB agent.

#### **Network Interfaces**

- Provides support for:

- Application development using Tornado.

- Distributed applications.

- VxWorks supports two network stacks:

- 4.3 BSD TCP/IP stack.

- SENS Scalable Enhanced Network Stack.

- SENS supports:

- 4.4 BSD TCP/IP stack.

- A proprietary MUX interface between the link and protocol layers.

- END Enhanced Network driver which decouples network driver from network protocols.

# **SCSI Controllers**

- Used to provide access to hard disks, tape drives, etc.:

- For booting VxWorks.

- Application data storage/retrieval.

- VxWorks supports SCSI-2 systems. Support consist of:

- Architecture independent libraries.

- Architecture specific controller driver.

- Board specific device initialization code.

- Devices accessed by application through:

- File system (DOS or RAW) for block devices.

- Tape file system for sequential devices.

- Customized SCSI commands for unsupported device classes.

# Summary

- A BSP will provide support for several hardware categories.

- Architecture specific:

- Caches.

- MMUs.

- Interrupt controllers.

- Floating point hardware.

- Bus specific:

- Bus controllers.

- Bus bridges.

# Summary

- Memory specific:

- Memory controllers.

- Memory chips.

- Devices:

- Timers.

- Serial Communication Controllers.

- Network interfaces.

- SCSI controllers.

- Custom ASICs.

- Support issues involve initialization and hardware access by application code.

# Chapter - 3

# BSP Development Issues

#### **BSP Development Issues**

3.1 Development Cycle Overview

**Development Environment**

Strategies For Getting Started

#### **Development Cycle Overview**

- Development of BSP proceeds in stages, with each stage depending on developments from previous stages:

- Obtain appropriate reference BSP and template code.

- Prepare the development environment.

- Write the VxWorks pre-kernel initialization code.

- Optionally supply support for Tornado access using a polled serial driver.

- Once kernel is activated, connect system interrupts.

- Enable the system clock.

- Complete BSP by supporting desired features.

- Test and document BSP following WRS standards.

- Details will depend on development environment and desired BSP features.

#### **Reference BSP**

- Choosing an appropriate reference BSP involves obtaining maximum coverage for desired target features, and reducing development time.

- Must obtain Tornado package for correct development platform and target architecture.

- Give priority to matching system features over generic (BSP independent) devices:

- Local and external bus support.

- Target bridges and controllers.

- May be able to obtain drivers for generic devices (e.g. serial, LAN, SCSI, etc.) separately from WRS or third party.

### **BSP Template**

- BSP template files are obtained when BSP developers purchase the BSP developer's kit.

- Includes all architectures.

- This should be the starting point for all code development:

- Do not "hack" reference BSP files, unless development consists of simply adding generic drivers.

- Examine and analyze reference BSP code, but build BSP using template files.

- The template BSP will compile, but most optional features have been disabled.

#### **Development Environment**

- Primary components of development environment:

- Technique for downloading code to target.

- Technique(s) for testing and debugging code.

- Appropriate and available development tools are dependent on development stage:

- Early pre-kernel initialization phase requires BSP developer to define development environment.

- Post-kernel initialization phase will have access to Tornado tools.

- Early pre-kernel development environment needs to provide download path and mechanism to jump to code entry points and execute code successfully.

### Pre-Kernel Development Environment

- Common download paths:

- Target vendor's debug ROM.

- ROM emulator.

- In-Circuit Emulator (ICE).

- Common debug tools:

- Target vendor's debug ROM.

- ICE.

- Logic analyzer.

- Target features such as LEDs.

- Tornado toolset.

#### **BSP Development Issues**

Development Cycle Overview

3.2 Development Environment

Strategies For Getting Started

#### Development Environment Requirements

- Developer must define pre-kernel development environment, often the same tool will provide download mechanism and debug facilities:

- ICE.

- Target vendor's debug ROM (if available).

- Sometimes a combination of tools will be required.

- For a ROM emulator, debug tools will need to be supplied separately.

- A download path will be needed for some debug tools:

- Logic analyzer.

- Target status indicators.

#### **In-Circuit Emulation**

- Processor replaced by probe with cables connected to emulation unit:

- Specific architecture is emulated.

- Emulation unit contains copy of processor being emulated.

- Technique allows access to processor bus to monitor or inject signals into system via:

- Emulator processor.

- Emulator circuitry.

- Emulator processor allows code to execute at full CPU speed providing timing information and allowing race conditions to be caught.

#### In-Circuit Emulation - cont.

- Emulator circuitry provides debug capabilities:

- Source level debugging.

- Halt emulation (breakpoint) on events not supported by software debuggers (trap code insertion).

- ICE debug extended feature examples:

- Breakpoints in ROM or RAM.

- Hardware breakpoints (watched points).

- Breakpoints on "don't care" addresses and data (e.g. 0x0247XXXX).

- Breakpoints on certain bus events.

- Breakpoints on processor cycles (interrupt acknowledge, cache writeback, etc.)

- Code fetches with specific data patterns.

# **In-Circuit Emulators**

- Primary issues:

- Must have correct emulator for target architecture.

- Cost.

- ICE systems usually come with support for code downloads via serial or network interface:

- To RAM (loadable VxWorks image).

- To Flash (ROM-based and ROM-resident images).

- Most emulators contain memory for code storage:

- Allows re-mapping of target memory regions to emulator (e.g. mapping ROM to emulator RAM).

- Off-loads system software from host, reducing host load while using ICE.

#### In-Circuit Emulators - cont.

- Often ICE will bundle enhanced facilities:

- Logic state analyzer.

- Logic timing analyzer.

- Pulse and pattern generator.

- Multiple trace capability.

- User-friendly GUI.

- Integrated debugger.

- Expansion busses for additional hardware access.

- Event ID and isolation capability.

- Real-time trace and filter.

- If target server backend is developed for an ICE, it can be used with Tornado tools.

# **Tornado / ICE Integration**

- Two ICEs which can be used with Tornado:

- visionICE

- TRACE 32 ICE

- Both products provide ethernet download capability, support for several popular architectures, and many enhanced features for real-time systems.

- Target server backend for these ICEs have been developed:

- Provides access to Tornado tools prior to kernel activation.

- Contact WRS for more information concerning ICEs which can be integrated with Tornado.

#### **ROM Emulators**

- ROM emulator gives host machine access to target via ROM socket:

- Target ROM chip is removed and emulator pods are plugged into (standard) ROM socket.

- Pods are connected to emulator, which in turn connects to host machine via serial or network link.

- ROM emulators not architecture dependent, can be used with any target which has ROM socket.

- ROM emulator unit contains memory which replaces target ROM:

- Code downloaded from host to emulator memory.

- Emulator memory appears as part of target memory.

#### **ROM Emulators - cont.**

- VxWorks can be executed:

- Out of emulator memory (ROM-resident image).

- Out of target memory (ROM-based image).

- ROM emulator provides download path, but not debug tools. Debug tools obtained via:

- Logic analyzer.

- Debug agent linked with software loaded to emulator memory.

- Most ROM emulators provide communication path and protocol to pass debug messages from target to host.

- If target server backend is developed for a ROM emulator it can be used with Tornado tools.

# NetROM

- One ROM emulator which can be used with Tornado tools is NetROM:

- Converts target with ROM socket to network node.

- 1 MB of emulation memory.

- Ethernet downloads via tftp or TCP.

- 2 KB of dual ported RAM for debug communication.

- NetROM target server backend option bundled with Tornado:

- Provides access to Tornado tools prior to kernel activation.

- See Tornado User's Guide for more information on configuring and using NetROM.

# Vendor Debug ROM

- Vendor native debug ROM (when available) comes with target board.

- Development software burned into ROM on target:

- Dynamic loader.

- Supported download path.

- Ability to jump to address and begin execution.

- Debug tools.

- Diagnostics.

- Target environment may have jumper allowing board to boot from ROM or some non-volatile RAM.

- After development can be replaced by ROM containing VxWorks image.

# Vendor Debug ROM - cont.

- Downloading code:

- Serial or network interface.

- Download path to RAM (VxWorks loadable image).

- Often download paths to Flash (ROM-based or

- ROM-resident images).

- Debug ROM code supplies device driver for communication interface port (serial or network).

- Example debug/diagnostic facilities (support varies):

- Set breakpoints and step code.

- Examine and modify memory.

- Set environmental parameters (bus clock speed, etc.).

- Self-test to verify integrity of target.

# Logic Analyzer

- Provides tool to monitor processor's address, data, control, and status lines:

- Connects to processor pins via multiple probes.

- Contains memory for data capture.

- Provides pre-kernel development services such as:

- Tracing on clock cycle or bus pattern triggers to monitor device responses.

- Locate hardware interrupt sources.

- Monitor address access to check memory mapping.

- Processor state evolution to monitor code execution sequences.

- Bundled with many ICEs.

# **Target Feature Debug Tools**

- Native target environment may provide several features which can be used as diagnostic/debug tools:

- Accessible memory mapped LEDs.

- Local or off board persistent memory.

- Serial port.

- Write library to manage target feature to be used as diagnostic/debug tool:

- Flash LEDs N times to mark code sequence events.

- Write state information to persistent memory for analysis after system reboot.

- Polled serial driver to send character(s) to host to mark code sequence events.

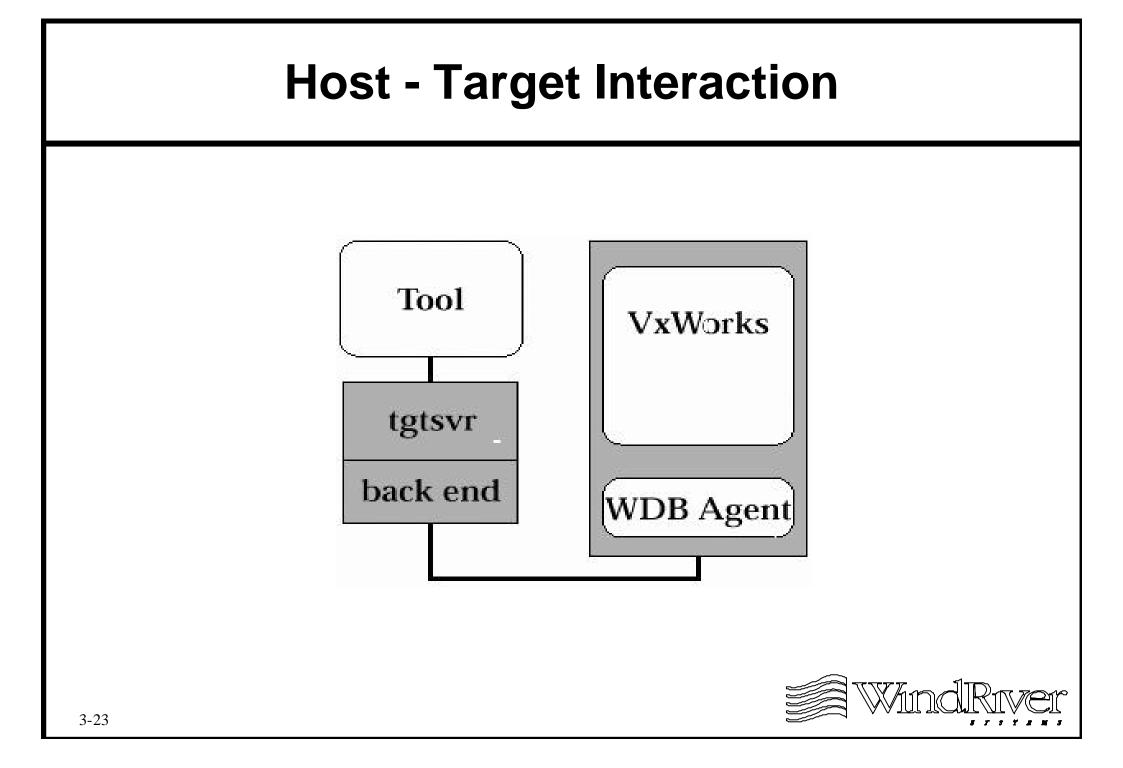

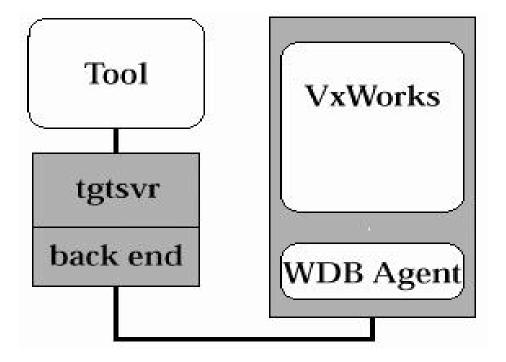

# WDB Agent And Tornado Tools

- Wind DeBug (WDB) agent is statically linked with VxWorks image. Provides advantages over traditional ROM monitor:

- One set of initialization code for agent and OS.

- Reduced size as agent shares libraries with OS.

- Provides access to full featured debug environment,

- Can run in system or task mode (post-kernel).

- Requires target server backend support to access Tornado tools. For pre-kernel development:

- NetROM (bundled).

- Serial line (bundled).

- Some ICEs (vendor or third party supplied).

#### **BSP Development Issues**

Development Cycle Overview

**Development Environment**

3.3 Strategies For Getting Started

# **Getting Started**

- Obtain appropriate reference BSP, Tornado BSP Developer's Kit for VxWorks, and device drivers.

- Once WRS software is provided but before starting development code:

- Determine development environment and obtain appropriate hardware.

- Configure target hardware based on documentation and development strategy.

- Choose appropriate development image type.

- Identify and configure required software tools.

- Once Tornado access has been achieved, development environment and strategy may be changed.

### **Development Environment**

- Will need to determine:

- Development tools.

- Target download path.

- For ICE or ROM emulator:

- Download tools provided.

- Determine to execute image in emulator memory or target memory (ROM-resident or ROM-based development image).

- Will need to provide debug tools for ROM emulator.

- For ROM monitor:

- Download and debug tools supplied.

- Development image may be loadable or ROM.

### **Development Environment - cont.**

- For vendor debug ROM:

- Download and debug tools provided.

- Load image to Flash (ROM-resident or ROM-based).

- Load image to RAM (can use loadable VxWorks image if ROM debug code initializes RAM).

- For tools without download facilities (logic analyzer and target features):

- Use with tools suppling download path.

- Burn development image into ROM.

- Target environment may need hardware configuration boot from Flash or ROM, external bus status, activation of download port, ROM swap, etc.

# Loadable vs. ROM images

- Difference between ROM and loadable image is loadable image does not initialize RAM.

- If development image is a loadable image RAM will need to be initialized by some other facility:

- If RAM initialization facility is not be present in production environment, start with ROM image.

- If loadable image is only option for development environment, and RAM initialization facility will not be available in production environment:

- Will need alternative environment to develop and test VxWorks RAM initialization code.

- Course will assume development image is ROM image.

# **Code Preparation**

- Development modules must be fully linked:

- Set appropriate cross-compiler, assembler, and linker flags.

- Linker must produce image with appropriate format for download methodology.

- WRS provides cross-development tools:

- Appropriate cross-compiler, assembler, and linker.

- Architecture specific nmX command to dump object module symbol table.

- Architecture specific objdumpX command to compare host assembly code with assembly code loaded to target.

- Routines to convert various object modules to hex (with appropriate S-record format).

# **Code Preparation - cont.**

- VxWorks image code is built using makefiles. Macros provided to specify build details:

- Cross-compiler and linker flags.

- Module components linked with image.

- Image types.

- For code not linked into a VxWorks image, developer will need to create makefile(s) to produce fully linked object module(s) which can be downloaded:

- Use WRS supplied cross-development tools.

- May need different cross-compiler and linker options during different phases of development.

- Build libraries an place them outside of Tornado directory structure.

# **Code Preparation Example**

- A routine to establish initial contact with target:

- Blinks target LED on 68k board.

- Loaded via serial line from UNIX host.

- Target RAM previously initialized.

- Routine in file talkToTarget.c:

- /\* talkToTarget.c \*/

- /\* Routines to blink lights on target board. \*/

- #define WAIT\_CNT 100000 /\* Loop count for delay. \*/

- /\* Forward declarations. \*/

- void lightBlink (void);

- void wait (void);

#### **Code Preparation Example - cont.**

```

void lightBlink (void)

int * pBrdLight= (int *) 0xFFF40060;

for(;;)

*pBrdLight = 0x4300000; /* Turn light on. */

wait ();

*pBrdLight = 0x4100000; /* Turn light off. */

wait ();

return;

void wait (void)

int i;

for(i=0;i<WAIT_CNT;i++)

```

#### **Code Preparation Example - cont.**

- First talkToTarget.c is cross-compiled using WRS cross-compiler: cc68k -c -DCPU=MC68040 - FLAGS talkToTarget.c

- Produces relocatable object module talkToTarget.o. Symbol table dumped with nm68k: 00000000 T \_lightBlink 00000028 T \_wait 00000000 t gcc2\_compiled.

- Convert to fully linked module with desired download address (0x100000) using WRS link-load tool: ld68k -Ttext 100000 talkToTarget.o

### **Code Preparation Example - cont.**

• Produces a.out file, dumping symbol table with nm68k:

00000000 A \_\_\_\_\_\_DYNAMIC

00120000 B \_\_\_end

00120000 D \_edata

00120000 B \_end

00120000 T \_etext

00100000 T \_lightBlink

00100028 T \_wait

00100000 t gcc2\_compiled.

00100000 t talkToTarget.o

- Convert to S-record format for serial line download using WRS tool: hex a.out > talkToTarget.hex

- This file may now be downloaded to target RAM.

# Summary

- First stage of BSP development involves:

- Obtaining appropriate reference BSP, template code, and device drivers.

- Define pre-kernel development environment.

- Pre-kernel development environment will specify:

- Target download mechanism.

- Diagnostic and debug tools.

- Appropriate VxWorks development image.

- WRS cross-development tools will be useful for preparing code not statically linked with VxWorks.

- Post-kernel development may employ a different development environment using Tornado tools.

# Chapter - 4

Pre-Kernel Initialization Overview

### **Pre-Kernel Initialization Overview**

4.1 Pre-Kernel Initialization Sequence

**BSP** Files

Building VxWorks Images

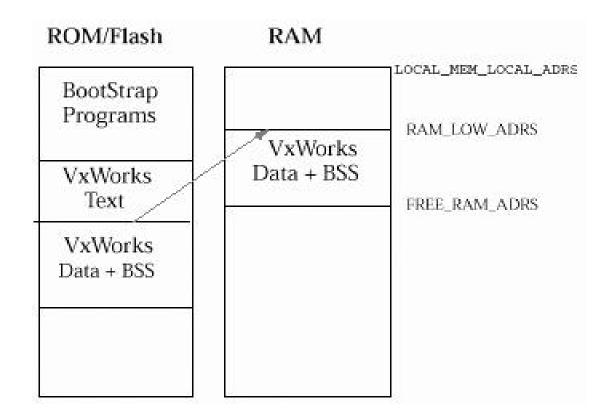

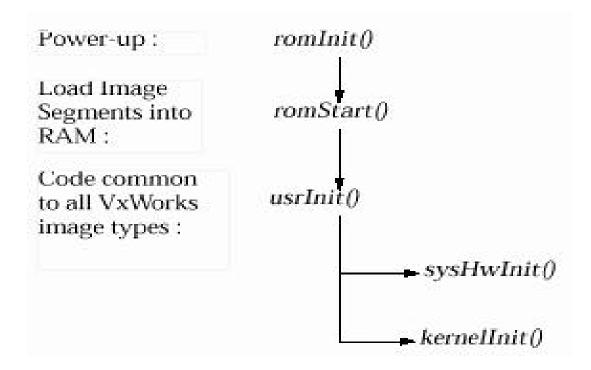

### VxWorks Boot and ROM Images

- As outlined in the Overview chapter, on power-up bootstrap code executes:

- The processor is "jumped" to a routine romInit() in ROM/Flash.

- romInit() resets processor, initializes memory system, and performs any other required hardware initialization.

- romInit() branches to romStart() which loads the ROM image (boot or VxWorks) into RAM.

- Processor jumps to pre-kernel initialization code statically linked into VxWorks image (usrInit()).

- For ROM-resident images:

- romStart() only loads data segment of image into RAM.

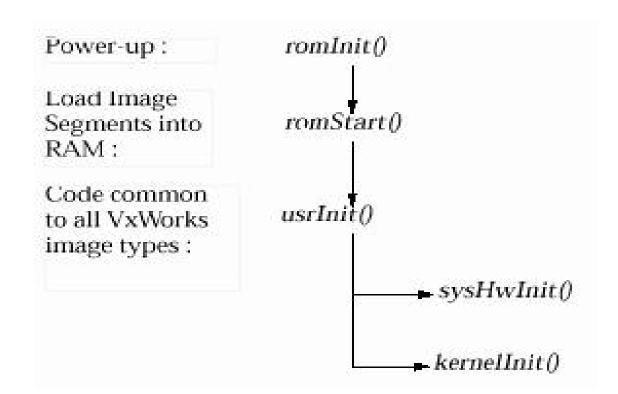

### VxWorks Loadable Images

- After "end-user" VxWorks image is loaded in RAM, the processor is "jumped" to the VxWorks load address.

- A routine sysInit() resides at this address. This routine resets the processor, and performs other hardware initialization if required.

- sysInit() branches to usrInit() which completes the pre-kernel initialization.

- Both of these routines are statically linked into a loadable VxWorks image.

- sysInit() is functionally similar to romInit(). The difference is that romInit() initializes memory and sysInit() does not. (DRAM and memory controller usually need to be initialized once.)

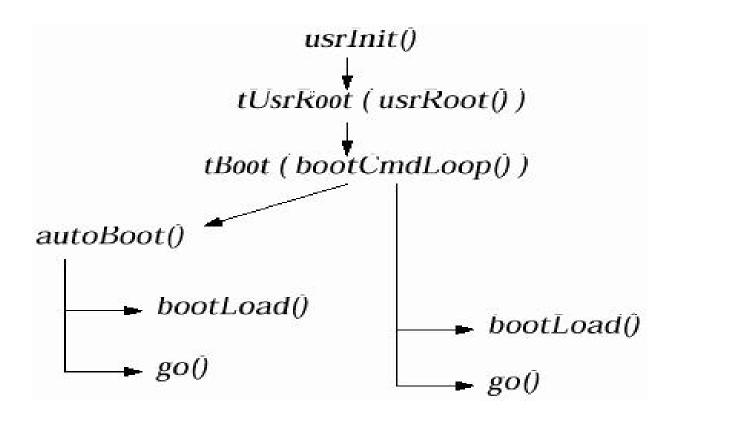

### **Generic Pre-Kernel Initialization**

- The routine usrInit() is a generic routine:

- Statically linked into all VxWorks image types.

- Calls routine which activates VxWorks kernel.

- Primary responsibility to place hardware in a quiet state so kernel can be activated:

- Disable all hardware interrupts.

- Initialize hardware to a known quiescent state.

- romInit()/sysInit() perform the minimal initialization necessary to allow usrInit() to execute.

- "VxWorks" provides the remainder of the hardware initialization via usrInit().

### **Generic Pre-Kernel Initialization - cont.**

- The routine which places hardware in the initial quiet state prior to activating the kernel is sysHwInit().

- The routine which activates the VxWorks kernel is kernelInit().

- kernelInit() activates the multitasking environment and spawns a task which:

- Installs drivers and creates devices.

- Initializes VxWorks library facilities.

- Calls application start-up code.

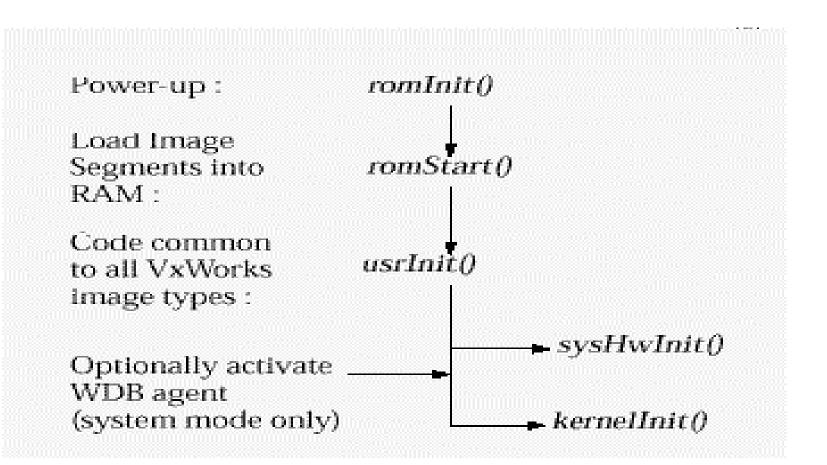

# Pre-Kernel Initialization Sequence VxWorks Boot and ROM Images

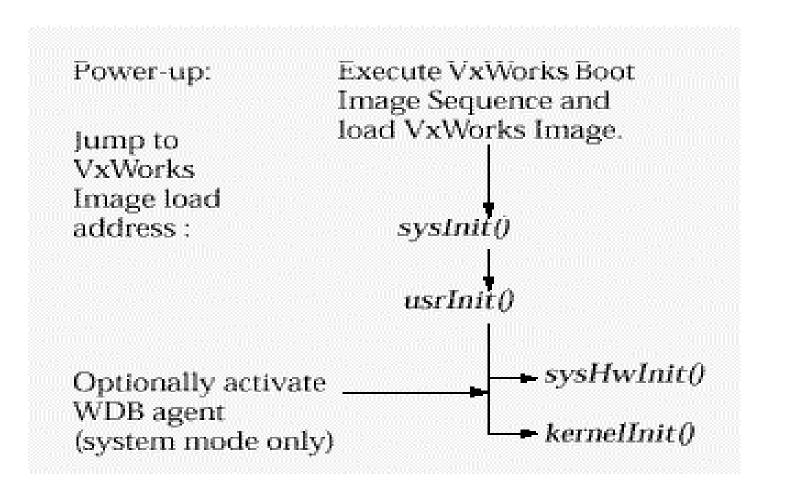

# Pre-Kernel Initialization Sequence Loadable VxWorks Image

### What Executes Where?

- romInit() always executes in ROM/Flash, and jumps to romStart() in ROM/Flash.

- romStart() always begins execution in ROM/Flash.

- ROM-resident images load data segment to RAM and continue to execute in ROM.

- Images which are not ROM-resident copy start-up code to a RAM address, and then jump to that RAM address.

- usrInit() executes out of RAM except for ROM-resident boot and ROM-resident VxWorks images.

- sysInit() always executes out of RAM.

#### **Pre-Kernel Initialization Overview**

**Pre-Kernel Initialization Sequence**

4.2 BSP Files

Building VxWorks Images

### **BSP Files - Overview**

- BSP component files are located in:

- ../config/<bspName>

- Directories containing BSP related files are:

- ../config/all

- ../h/make

- Related directories providing support for device drivers will also be referenced during BSP development:

- ../src/drv

- ../h/drv

- BSP development will focus on BSP files. All files which must be customized are in ../config/<bspName>.

### **BSP Files - Overview**

- Files in the ../config/all directory are delivered as part of the Tornado distribution. These files should not be modified.

- Files in the ../config/<bspName> directory are not delivered as part of the Tornado distribution:

- BSP is a separate product (sales and installation).

- All VxWorks image type builds are controlled by the Makefile in the ../config/<bspName> directory.

- Support makefiles containing rules and dependencies are located in ../h/make. Modifications will be needed in the primary Makefile as part of BSP development.

### **BSP Files - Overview**

- The components of a BSP are:

- Source files.

- Include files.

- Makefiles.

- Derived files.

- Document files.

- BSP, and BSP related files will be presented as follows:

- Source files in the ../config directories.

- Include files in the ../config directories.

- Makefiles in ../config/<bspName> and ../h/make.

- Derived files in ../config/<bspName>.

- Document files in ../config/<bspName>.

#### **BSP Related Files - Source Files**

- BSP related source files in ../config/all:

- bootConfig.c The primary initialization file for VxWorks boot images. Contains the routine usrInit().

- usrConfig.c The primary initialization file for VxWorks images. Contains the routine usrInit().

- bootInit.c Consists of the routine romStart() and two support routines which romStart() calls.

- dataSegPad.c Insures that text and data segments of VxWorks images do not share a MMU page when using VxVMI. Not used in the pre-kernel initialization sequence.

#### **BSP Files - Source Files**

- BSP source files in ../config/<bspName>:

- romInit.s Assembly language source for romInit().

- sysALib.s Assembly language source for sysInit().

- sysLib.c File containing routines providing board-level access in a generic fashion. It #includes all driver modules (or causes them to be linked into VxWorks images). Contains the routines sysHwInit(), sysHwInit2(), as well as many other routines which must be provided as part of a BSP. Primary BSP source file.

### **BSP Files - Source Files**

- Optional BSP source files in ../config/<bspName>:

- sysSerial.c File containing routines to provide initialization for serial I/O devices. Some routines in this file are called via sysHwInit() as part of pre-kernel initialization. Not required if serial I/O interface is not used.

- sysScsi.c File containing SCSI configuration routines. These routines execute after the kernel is activated. Not required if SCSI support not needed.

- sysNet.c File containing routines for initialization and configuration of network interface devices. Not required if LAN interface is not present.

- If the BSP requires any unique drivers they should be located in ../config/<bspName> (not ../src/drv).

### **BSP Files - Include Files**

- BSP related include files in ../config/all:

- configAll.h This file establishes the default configuration for VxWorks. It should not be modified.

- BSP include files in ../config/<bspName>:

- config.h This file is used to modify VxWorks and BSP hardware configurations. This file will be modified as BSP development evolves.

- <bsp>.h This file contains fixed hardware values (hardware addresses, hardware interrupt levels, etc.). Should not be modified unless hardware environment is modified.

### **BSP Files - Makefiles**

- BSP makefile in ../config/<bspName>:

- Makefile Controls building of all VxWorks image types. Probably will need to be modified as part of the pre-kernel code development.

- BSP related sub-makefiles in ../h/make:

- rules.bsp Contains the rules for building the various VxWorks image types, as well as the rules for BSP object modules which are used in VxWorks builds.

- defs.bsp Contains definitions of BSP build control macros for compilation and linking.

- Other sub-makefiles in ../h/make control host and architecture specific build parameters.

### **BSP Files - Derived Files**

- BSP derived files in ../config/<bspName>:

- VxWorks images.

- VxWorks boot images.

- Object modules generated when source files in the ../ config directories are compiled (bootConfig.o, usrConfig.o, bootInit.o, romInit.o, sysALib.o, and sysLib.o).

- depend.<br/>bspName> Make will generate this dependencies file when a VxWorks build is done.

- C files and associated object module files for a target resident symbol table (symTbl.c and symTbl.o) and C++ constructors/destructors (ctdt.c and ctdt.o).

- VxWorks image types will be discussed in greater detail later.

### **BSP Files - Document Files**

- BSP documentation files in ../config/<bspName>:

- target.nr File containing board specific information necessary to execute VxWorks image types. File is nroff format and divided into sections involving supported/unsupported features, instructions for using boot ROMs, summary of hardware devices, target environment layout, and description of board jumpers.

- target.txt ASCII version of target.nr.

- README File contains BSP release record. This information is a version number/revision number.

- A BSP version number identifies the BSP's generation, a BSP revision number incrementally identifies a release within a BSP generation.

#### **Pre-Kernel Initialization Overview**

**Pre-Kernel Initialization Sequence**

**BSP** Files

4.3 Building VxWorks Images

### **VxWorks Builds**

- VxWorks builds are controlled by the Makefile in the ../ config/<bspName> directory.

- The type of VxWorks image which will be built is specified by the object type name specified. These "target" names appear in the file ../h/make/rules.bsp.

- VxWorks image types can be divided into:

- VxWorks images Loadable, ROMable, and ROM-resident.

- VxWorks boot images ROMable and ROM-resident.

- All ROMable (non-ROM-resident) images can be sub-divided as compressed or uncompressed.

## VxWorks Image Types

- The build rules for VxWorks will produce images for the following object type names:

- vxWorks Loadable binary VxWorks image. (Also builds a separate vxWorks.sym symbol table file).

- vxWorks\_rom Uncompressed ROMable binary VxWorks image.

- vxWorks.st Stand-alone loadable binary VxWorks image. Symbol table linked in.

- vxWorks.st\_rom Compressed ROMable version of vxWorks.st.

- vxWorks.res\_rom Uncompressed ROM-resident version of vxWorks.st.

- vxWorks.res\_rom\_nosym ROM-resident version of vxWorks.st without symbol table.

## **VxWorks Image Types - continued**

- bootrom Compressed ROMable binary VxWorks boot image.

- bootrom\_uncmp Uncompressed rommable binary VxWorks boot image.

- bootrom\_res ROM-resident binary VxWorks boot image.

- S-record formatted versions for all rommable and ROM-resident images can be built by using the object type name show here and adding a ".hex" extension.

- Note, uncompressed ROMable images may require extra capacity ROMs.

- All ROMable and ROM-resident images can be configured to be "burned" into Flash or PROM.

### The VxWorks Makefile

- The file Makefile in the ../config/<bspName> directory controls all VxWorks builds. It contains:

- Required BSP specific macros.

- Additional (non-required) support macros.

- Includes of support makefiles in ../h/make.

- Some macros defined in Makefile are also defined in ../config/<bspName>/config.h. Definitions must be identical.

- Compilation rules, linking rules and support macro definitions for building images are in ../h/make.

### **VxWorks Makefile Macros**

- The BSP developer is responsible for defining the following required BSP specific macros in ../config/ <bspName>/Makefile:

- CPU Target CPU.

- TOOL Host tool chain (e.g., gnu)

- TGT\_DIR By default set to \$(WIND\_BASE)/target.

- TARGET\_DIR BSP directory name.

- VENDOR Board manufacturer's name

- BOARD Name of board.

- ROM\_TEXT\_ADRS Boot ROM entry address in hexadecimal. Will be a Flash address if processor is "jumped" to Flash on power-up.

#### **VxWorks Makefile Macros -continued**

- ROM\_SIZE Size of ROM area in hexadecimal.

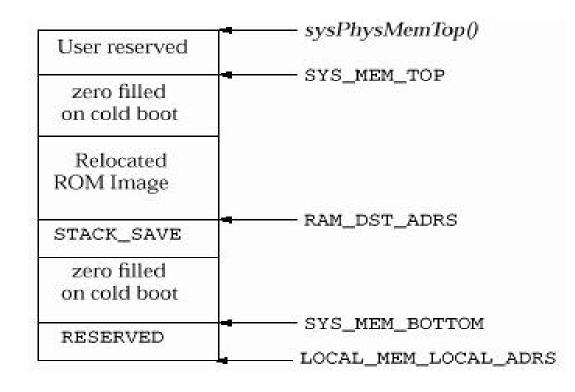

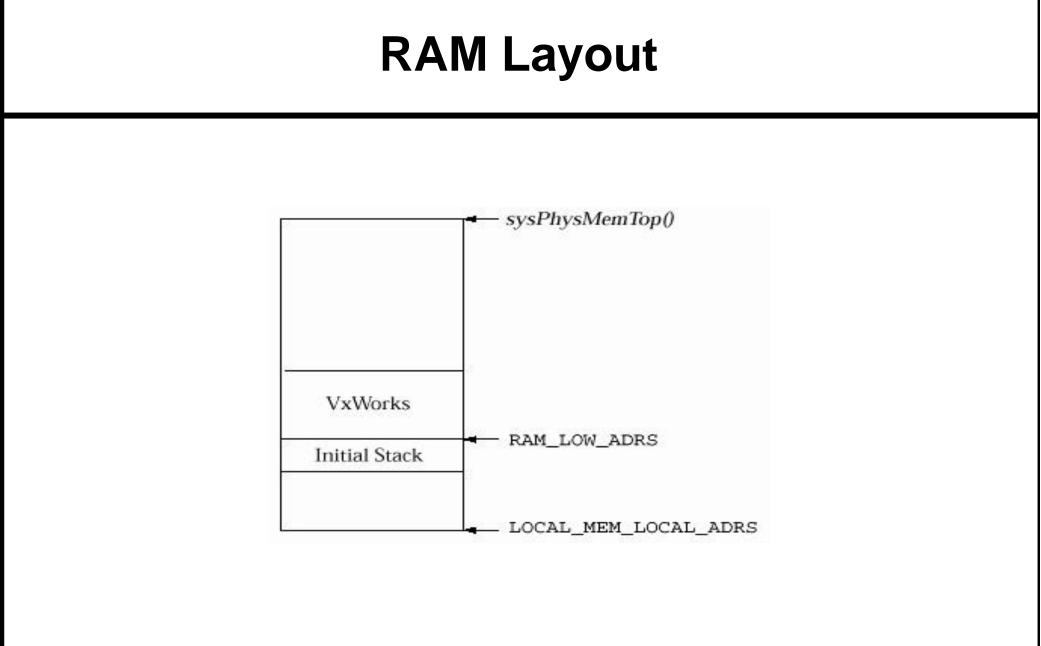

- RAM\_LOW\_ADRS Address at which non-ROM-resident application VxWorks images begin. (It is also the initial load address for compressed VxWorks boot images. This will be discussed in the next chapter.)

- RAM\_HIGH\_ADRS Destination address for non-ROM- resident VxWorks boot images. (Also initial load address for non-ROM- resident compressed VxWorks ROM images.)

- HEX\_FLAGS Architecture specific flags for building S-record formatted versions of images.

- MACH\_EXTRA Extra machine-dependent files to be linked. Initialize as empty declaration.

### **VxWorks Makefile Macros -continued**

- The following macros must be identically defined in ../h/<bspName>/config.h:

- ROM\_TEXT\_ADRS

- ROM\_SIZE

- RAM\_LOW\_ADRS

- RAM\_HIGH\_ADRS

- There may also be some architecture specific macros required in the Makefile file. (Example, the i960 CPU needs to know where to link the Initial Boot Record.)

- Hexadecimal addresses used in macro definitions should not have a leading 0x in Makefile.

## VxWorks Makefile Macros For Customized Builds

- Additional (non-required) macros to customize VxWorks builds fall into two categories:

- Those used by application developers.

- Those used by BSP developers.

- Macros for application developers contain ADDED in their name. These macros allow the user to specify compile time options.

- Macros for BSP developers contain EXTRA in their name. These macros allow additional object modules to be compiled and linked with VxWorks.

### The Makefile and Sub-makefiles

- The Makefile file contains includes of sub-makefiles containing definitions and rules necessary for VxWorks builds. These sub-makefiles are in ../h/make:

- defs.bsp File containing default make definitions. These definitions can be customized in Makefile.

- make.\$(CPU)\$(TOOL) File contains CPU specific macros for a specific tool chain.

- defs.\$(WIND\_HOST\_TYPE) File where host specific macros are defined.

- rules.bsp File containing rules for VxWorks builds.

- rules.\$(WIND\_HOST\_TYPE) Files contains host specific build rules.

## Summary

- Pre-kernel initialization code is responsible for placing the hardware environment in a state which allows the VxWorks kernel to be activated.

- Pre-kernel initialization code is specific to boot strategy and statically linked into the appropriate VxWorks image type:

- Loadable image Contains application code.

- ROM image May contain application or boot code.

- ROM-resident image May contain application or boot code.

- VxWorks builds controlled by Makefile file which uses submakefiles containing make definitions and rules.

# Chapter - 5

## Pre - Kernel Initialization - Boot Specific Code

### Pre-Kernel Initialization - Boot Specific Code

5.1 Boot Specific vs. Generic Code

romInit.s : romInit()

PIC and VxWorks

bootInit.c : romStart()

sysALib.s : sysInit()

### VxWorks Image Types and Generic Code

- Details of pre-kernel initialization depend on VxWorks image type characteristics:

- ROM image Boot or "end-user" image.

- a. compressed

- b. uncompressed

- ROM-resident image Boot or "end-user" image.

- Loadable image "End-user" image.

- Generic pre-kernel code common to all image types is usrInit() and the routines it calls. These will be discussed in the next chapter.

## Boot Specific Pre-kernel Initialization Code

- VxWorks image type specific code:

- romInit()

- romStart()

- sysInit()

- romInit() and romStart() execute for all images "burned" into ROM.

- sysInit() only executes for all loadable VxWorks images.

- romInit() and sysInit() are similar routines except romInit() initializes memory and sysInit() does not (this is done by romInit() in the boot image).

## **Choice of First Image**

- Which type of image is developed first depends on download path:

- Download to RAM Use vxWorks.

- Download to ROM Use vxWorks\_rom or vxWorks.res\_rom\_nosym.

- The initial image should not be compressed or contain a symbol table. These features can be added later.

- The first image for a download path to ROM:

- vxWorks\_rom Allows software breakpoints for code which executes in RAM.

- vxWorks.res\_rom\_nosym Provides a smaller RAM footprint (and possibly reduced start-up time).

### Pre-Kernel Initialization - Boot Specific Code

Boot Specific vs. Generic Code

5.2 romInit.s : romInit()

PIC and VxWorks

bootInit.c : romStart()

sysALib.s : sysInit()

## romInit() Basics

- First code to execute on power-up. Entry point for all VxWorks ROM images.

- Performs minimum required setup to execute romStart(). The remainder of hardware initialization is performed by generic prekernel code.

- Routine must:

- Mask processor interrupts and reset processor.

- Initialize the memory system.

- Initialize stack pointer and other registers to begin executing romStart() and passing the boot type.

- Routine is written is assembly language and resides in file romInit.s.

### **Architecture vs. BSP Specific Issues**

- Much of what romInit() needs to do is processor specific and can be copied from the reference BSP:

- Masking processor interrupts.

- Initializing on-processor caches.

- Initializing the stack pointer.

- Non-processor specific initialization involves DRAM and will be specific to the hardware environment.

- Wait states.

- Refresh rates.

- Chip selects (bridge/bus/memory controllers, etc.)

- Disabling of L2 caches (if necessary).

## Cold vs. Warm Boots

- Two boot types:

- Cold boot Power-up of hardware environment.

- Warm boot Call to reboot(), ^X, or exception at interrupt level. The routine which passes control to the ROM monitor is sysToMonitor() in sysLib.c.

- Where romInit() begins execution is a function of the boot type:

- Cold boot Execution begins at the entry point romInit(). Boot type is forced to be BOOT\_COLD.

- Warm boot Execution begins at romInit() plus a small offset (usually 4 bytes). Boot type is saved.

- Boot type (cold/warm) is stored in an architecture specific register and passed to romStart().

### **Stack Pointer Initialization**

- Macro which configures beginning of stack is STACK\_ADRS in configAll.h.

- For ROM-resident images the stack will begin:

- In RAM at the start of the VxWorks data segment for stacks which grow down.

- In RAM at the start of the VxWorks data segment less the size of the stack for stacks which grow up.

- For non-ROM-resident images the stack will begin:

- In RAM at the start of the text segment of the VxWorks image for stacks which grow down.

- In RAM at the start of the text segment of the VxWorks image less the size of the stack for stacks which grow up.

## romInit() - PIC

- romInit(), which runs in ROM/Flash, must be written as Position Independent Code (PIC) to support the various boot strategies for VxWorks images.

- PIC code is program counter (PC) relative.

- If a ROM address cannot be made program counter relative then it must be recomputed by:

- Subtracting \_romInit (The entry point for romInit().)

- Adding ROM\_TEXT\_ADRS (Boot ROM/Flash entry address. Where ROM code is "burned".)

- This algorithm ensures that a ROM address is expressed relative to the PC value for romInit() regardless of the address assigned to romInit() by the compiler/linker.

## romInit() - Some do's and don'ts

- Perform minimum necessary initialization. Leave most hardware initialization to generic routine sysHwInit().

- Do not call out to other modules or routines:

- May cause linking problems for compressed images.

- Call outs to C routines may use absolute not PC relative addressing.

- Make sure romInit() is the first routine in romInit.s.

- Start with romInit() from reference BSP.

- Make sure macros in Makefile and config.h are correct:

- ROM\_TEXT\_ADRS

- ROM\_SIZE

### Pre-Kernel Initialization - Boot Specific Code

Boot Specific vs. Generic Code

romInit.s : romInit()

5.3 PIC and VxWorks

bootInit.c : romStart()

sysALib.s : sysInit()

## **PIC and VxWorks Builds**

- romInit() which executes in ROM needs to be PIC to support various VxWorks image types.

- This is because romInit() is linked into all non-loadable VxWorks images, all of which do not execute in ROM.

- To understand how romInit() (as well as other routines) are linked into VxWorks images the build rules in ../h/ make/rules.bsp must be examined.

- Examine the link instructions for vxWorks\_rom:

- Uncompressed rommable binary image.

- Begins execution in ROM.

- Transfers execution to RAM in romStart().

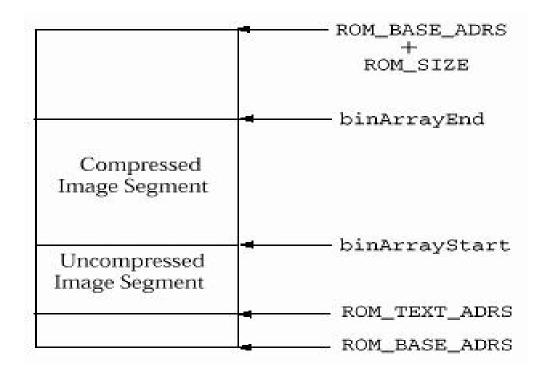

## vxWorks\_rom Build