2001년 12월

# 저가형 광가입자 장비 기술 개발

Development of the Low-cost Optical Access Equipment Technology

# 인 사 말 씀

21 세기는 지식과 정보가 컴퓨터나 통신기능과 결합해 훨씬 높은 효율로 활용되는 지식 기반 사회가 될 것입니다. 지난 수년간 가입자망의 급속한 환경 변화는 일반인들에게 생활 가까이에서 인터넷을 사용하고 느끼게 하는 계기가 되었습니다. 이제는 연구 현장에서 뿐만 아니라 일반인들의 생활에서도 인터넷을 떼어놓고는 생활하기가 불편한 시대가 되었습니다. 이러한 급속한 환경 변화는 곧 새로운 사회적 요구와 사용자의 욕구에 의해 더욱 다양하고 본격적인 정보 통신 환경의 변화를 유발하고 있습니다.

우선 첫째 더욱 광범위한 초고속 가입자망의 보급입니다. 그러기 위해서는 인터넷에서 소외되는 지역, 계층이 없도록 경제적이면서 다양한 환경에 적응될 수 있는 초고속 가입자망 장치가 절실히 요구됩니다, 두 번째는 인터넷의 생산적 활용입니다. 많은 사람들이 인터넷을 접하게 됨으로써 인터넷의 새로운 가치가 끊임없이 발견되고 있으며, 그에 따른 새로운 응용이 계속되고 있습니다. 새로운 응용이 안정적으로 이루어질 수 있도록 고품질, 고 신뢰성의 통신 서비스를 제공하는 것이 중요한 과제가 되고 있습니다. 세 번째는 더욱 큰 대역폭요구에 대한 대처입니다. 현재의 인터넷이 텍스트 품질에 기반 한 인터넷인 반면 향후의 인터넷은 고품질의 영상, 음향 기반의 멀티미디어 인터넷이 될 것입니다. 현재 시작되고 있는다양한 품질의 디지털 영상 신호의 활용이 이러한 예측을 뒷받침해 주고 있습니다. 이를 위해서는 현재의 초고속 가입자망보다 10배-100배 빠른 속도의 데이터를 저비용으로 제공하는 초고속 가입자망 기술이 필요합니다.

본 연구에서는 말씀드린 새로운 정보 통신 환경 변화 요구에 부응할 수 있는 광가입자 장비를 저가로 개발하는 것을 연구 목표로 하였습니다. 광가입자 장치는 무한대의 대역폭을 갖는 광섬유를 가입자 댁내 혹은 인근까지 설치하는 궁극적인 형태의 초고속 가입자망이지만 광 특유의 고비용 문제 때문에 본격 적용이 지연되고 있습니다. 따라서, 본 연구에서는 장치의 개발뿐만 아니라 주요 핵심부품의 개발에 역점을 두어서 장치의 저가화에 많은 노력을 하였습니다. 20Km 에 달하는 전송 거리, 소규모 주거지역에도 경제적으로 적용, 수 Mb/s-100Mb/s 까지 융통성 있는 대역폭 제공 등의 특성을 갖는 ATM-PON 광가입자 장비는 현재 초고속 가입자 장치의 단점을 보완하고, 나아가서 차세대 초고속 가입자 장치로 활용할 수 있을 것으로 크게 기대됩니다.

끝으로 본 연구 과제를 위하여 협조해주신 정보통신부와 정보통신진흥원의관계자 여러분께 깊은 감사를 드리며, 연구 업무에 참여한 연구원들의 노고를 치하하는 바입니다.

2001. 12. 한국전자통신연구원 원장 오 길 록

# 제 출 문

#### 정보통신부장관 귀하

본 보고서를 "저가형 광가입자 장비 기술 개발에 관한 연구"의 최종 연구개발결과보고서로 제출합니다.

#### 2001년 12월 31일

주관연구기관 : 한국전자통신연구원

참여연구기관 : 한국통신

: 삼우통신공업(주): 두일 전자통신(주): (주)엔디에스: 서두인칩(주)

: (주)한화정보통신

연구책임자 : 책임연구원 유 태환(광가입자팀장)

책임연구원 김 재근(광통신연구부장)<sup>(1)</sup>

참여연구원 : 책임연구원 이 종현(광통신연구부장)(2)

책임연구원 김 대웅(네트워크서비스연구부장)<sup>(3)</sup> 책임연구원 고 제수(전송핵심 모듈팀장)<sup>(4)</sup> 책임연구원 허 재두(광전송S/W팀장)<sup>(5)</sup> 책임연구원 강 성수(고속모뎀팀 )<sup>(6)</sup> 책임연구원 전 경규(고속모뎀팀 )<sup>(7)</sup> 책임연구원 김 홍주(PON기술팀 )<sup>(8)</sup>

선임연구원 문 필주(광루프전송팀장)<sup>(9)</sup> 선임연구원 장 윤선(광가입자팀) 선임연구원 노 지명(광가입자팀) 선임연구원 김 승환(전송핵심모듈팀)

강 호용(전송핵심모듈 팀 )<sup>(10)</sup> 선임연구원 선임연구원 김 찬(전송핵심모듈팀) 선임연구원 김 영화(광전송S/W팀) 선임연구원 심 재찬(광전송S/W팀) 선임연구원 최 수일(광전송S/W팀) 이 유태(광전송S/W팀 )<sup>(11)</sup> 선임연구원 김 효중(광루프전송팀 )(12) 선임연구원 이 동춘(PON기술팀 )<sup>(13)</sup> 선임연구원

선임연구원 최 강일(PON기술팀 )<sup>(14)</sup> 연 구 원 김 정학(광가입자팀) 연 구 원 최 현균(광가입자팀)

한 경수 (광 가입자 팀) 연 구 원 연 구 원 훈 (전송핵심모듈팀) 연 구 원 임 정묵 (광 전 송 S/W 팀 ) 연 구 원 유 윤식 (광 전 송 S/W 팀 ) 위촉연구원 전 덕영 (광가입자 팀) 위촉연구원 정 병익 (광 전 송 S/W 팀 )(15) 연구책임자 김 운하 (한국통신)('01.01.~'01.12.) 책임연구원 유 건일 (한국통신)('01.01.~'01.12.) 책임연구원 고 상호 (한국통신)('01.01.~'01.12.) 선임연구원 임 채운 (한국통신)('01.01.~'01.12.) 선임연구원 김 진희 (한국통신)('01.01.~'01.12.) 김 종안 (한국통신)('01.01.~'01.12.) 선임연구원 선임연구원 강 대경 (한국통신)('01.01.~'01.12.) 선임연구원 김 홍석 (한국통신)('01.01.~'01.12.) 박 용석 (삼우통신)(99.12.~'01.12.) 연구책임자 선임연구원 강 명진 (삼우통신)(99.12.~'01.12.) 전임연구원 임 은성 (삼우통신)('00.03.~'01.12.) 주임연구원 고 준원 (삼우통신)('00.03.~'01.12.) 김 주임연구원 현 (삼우통신)('00.03.~'01.12.) 연 구 원 상 명희 (삼우통신)('00.05.~'01.12.) 연구책임자 이 영희 (두일 전자)('99.12.~'0.1.12.) 양 문석 (두일전자)('00.03.~'01.12.) 책임연구원 선임연구원 김 인원 (두일전자)('00.08.~'01.12.) 선임연구원 한 상준 (두일전자)('00.03.~ '01.12.) 연 구 원 임 형표 (두일전자)('00.06.~ '01.12.) 주임연구원 김 민규 (두일전자)('00.03.~'01.12.) 연 구 원 한 만재 (두일전자)('00.03.~'01.12.) 연 구 원 김 용문 (두일전자)('00.05.~'01.12.) 연구책임자 구 현모 (엔디에스) ('99.12.~ '01.12.) 수석연구원 한 광열 (엔디에스) ('00.05.~'01.06) 책임연구원 장 세봉 (엔디에스) ('00.06.~'01.12.) 전임연구원 김 재경 (엔디에스) (00.09.~'01.12.) 연 구 원 김 진억 (엔디에스) ('01.02.~'01.12.) 연 구 원 정 병익 (엔디에스) (01.01.~'01.09.) 구 연 원 박 정훈 (엔디에스) ('01.04.~ '01.12.) 연 구 원 배 현종 (엔디에스) ('01.04.~'01.12.) 과장 강 인기 (엔디에스) ('01.06.~'01.12.) 강 길순 (서두인칩) ('99.08.~ '01.12.) 연구책임자 선임연구원 정 홍구 (서두인칩) ('99.08.~ '01.12.) 서 지승 (서두인칩) ('99.08.~ '01.12.) 선임연구원

연구책임자 김 중응 (한화정보) ('99.12.~ '00.12.) 책임연구원 박 성우 (한화정보) ('99.12.~ '00.12.) 선임연구원 최 용묵 (한화정보) (00.03.~ '01.12.) 선임연구원 정 재일 (한화정보) (00.03.~ '01.12.) 주임연구원 정 병용 (한화정보) (00.03.~ '01.12.)

- (1) 1998.12.부터 1999..12.까지 참여

- (2) 2000.01.01.부터 참여

- (3) 2001.01.01.부터 참여

- (4) 2001.01.01.부터 참여

- (5) 2001.01.01.부터 참여

- (6) 1998.12.부터 1999..12.까지 참여

- (7) 1998.12.부터 1999..12.까지 참여

- (8) 1998.12.부터 1999..12.까지 참여

- (9) 2001.02.10.까지 참여

- (10) 2000.07.01.부터 참여

- (11) 2001.02.20.까지 참여

- (12) 1998.12.부터 1999..06.까지 참여

- (13) 1998.12.부터 1999..12.까지 참여

- (14) 1998.12.부터 1999..06.까지 참여

- (15) 2001.10.01.부터 참여

# 요 약 문

#### 1.제목

저가형 광가입자 장비 기술 개발

# 2. 연구개발의 목적 및 중요성

### 가. 연구의 목적

본 연구는 기존 동선 전화선 구축비용 수준으로 가입자 댁내 흑은 가입자 근처까지 광 선로를 설치하기 위한 경제적 광가입자망의 구현을 최종 목표로 한다. 이를 위해 최대 64분기를 갖는 PON(Passive Optical Network) 기술, 622Mb/s 단위의 32x32 ATM 스위치 기능을 갖는 OLT(Optical Line Termination), 전주 형 및 Desktop형 ONU(Optical Network Unit), 기존 전화선을 활용하기 위한 고속 디지털 모뎀 등을 각각 저가로 개발하고, 음성 및 광 대역 멀티미디어 등 다양한 서비스를 수용하기 위한가입자와 서비스 노드 접속기술을 개발하다.

#### 나. 연구의 중요성

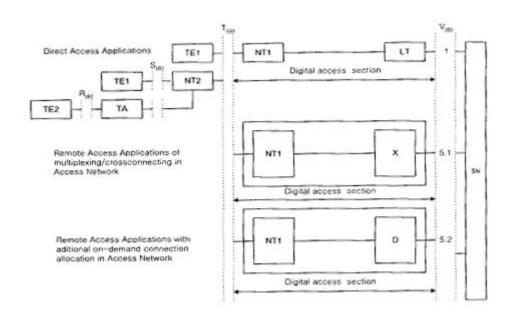

초고속 가입자망은 기존 가입자망 기반 시설을 그대로 활용하는 xDSL, 광 선로 기술을 기반으로 하는 FITL(Fiber In The Loop), 무선기술의 RITL(Radio In The Loop),위성 등 다양한 방안이 있다. 이중에 xDSL 은 3.6km 까지 최대 6Mb/s의 데이터 서비스를 제공할 수있는 ADSL,이 대량으로 보급되어 있고, RITL로는 광 대역 무선LAN이 가입자망 영역으로 확장되고 있는 추세이다. FITL 의 일종인 HFC는 1990년대 후반 케이블모뎀을 이용한 초고속 서비스를 위해 동축케이블 분배 망을 개선하는 방안으로 적용되었다. 이와 같이 1990년대 후반부터 xDSL과 FITL 방식의 초고속 가입자망이 다양한 형태로 개발, 적용되어 왔으나, 다음의 몇 가지 현안을 가지고 있다.

첫째는 현재의 초고속 가입자망은 대역폭이 수Mb/s 이하로 제한되고, 차별화된 고품질 서비스를 제공하지 않는다는 것이다.

음성서비스가 쇠퇴하고 데이터가 주요 트래픽을 차지하고 있는 상황에서 음성 서비스와 같은 규모의 매출을 보장하는 새로운 서비스의 창출이 필요한 시점이다. 새로운 서비스에서는 대역폭의 확대,Qos 기반의 서비스, 보안성 확보 등이 고품질의 네트워킹기술이 요구된다. 두 번째는 초고속 서비스로부터 소외된 지역에 경제적으로 적용할 수 있는 초고속 가입자망의 개발이다. 현재 집단 주거지 중심으로 보급된 xDSL, 기반 초고속서비스는 농어촌, 일반주택지 등에는 적용하기가 어렵다.

상기 문제를 해결하는 방안으로 광 선로를 좀더 가입자에 접근시키기 위한 FTTC, FTTN, FTTH 광 가입자 시스템 이 개발되고 있다. FTTC/FTTN/TTH를 경제적으로 구현하는 방식으로는 수동광분기기를 기반으로 하는 PON(Passive Optical Network)이 유력한 방식으로 인식되고 있으며, 북미, 일본, 유럽 등을 중심으로 관련기술의 표준화, 시스템 개발 및 사업 적용이 진행되고 있다.

본 연구 개발은 수 Mb/s에서 수백 Mb/s 범위의 대용량 대역폭을 가입자 요구에 따라 융통성 있게 제공하고, 광선로를 가입자 댁내 혹은 인근에 설치하는 FTTC/N/H 광가입자망을 저가로 구축할 수 있는 기술을 개발하는 것을 목표로 하였다. 저가 구현을 위해 한 개의 광섬유를 여러 가입자가 공유하는 PON 방식을 가입자 분배망으로 선택하였다. 또한 QoS 보장과 보안성 확보를 위해 ATM을 데이터 링크 프로토콜로 사용하였고, 주요 핵심 기능인 ATM 계층처리 칩 및 스위치 칩을 자체개발, 적용하여 저가화 할 수 있도록 하였다.

PON 방식을 이용할 경우 ONU의 가입자 수용 규모를 FTTH 경우는 단일 가입자, FTTC/N 경우는  $10\sim30$  가입자 규모로 줄일 수 있고, 전송 거리도 최대 20km에 이르기 때문에 농어촌, 일반주택지, 소규모 다세대 주택 등에 경제적으로 적용하기에 적합하다. 또한 망 단국에서 가입자 방향인 하향으로는 622Mb/s, 그 반대 방향인 상향으로는 155Mb/s의 광 전송 속도를 가지며, 32개의 ONU가 한 광 선로를 공유할 경우 ONU 당 평균 하향 20Mb/s 상향 5Mb/s의 대역폭 제공이 가능하다. 또한, PON 방식의 고유 특성으로서, 가입자가 요구할 경우 순간적으로 광 선로 전체 속도, 즉155Mb/s 혹은 622Mb/s 까지 한 ONU가 사용할 수 있도록 동적으로 대역폭을 할당할 수 있다.

이러한 특성을 고려해 볼 때 본 연구 개발에서 주진한 ATM-PON 가입자망은 전술한 현재의 초고속 가입자망 문제점을 해결하는 방안이며, 나아가서 궁극적인FTTH 망을 구축하는 유력한 방식이 될 것이다. 최근 1-2년 사이 FTTH망의 보급에 큰 장애가 되어 왔던 광송수신 부품 가격이 급격히 하락하고 있어 FTTH망의 본격적이 적용 전망을 더욱 밝게 해주고 있다.

### 3. 연구개발의 내용 및 범위

#### 가. 최종 연구 목표

기존 동선 전화선 구축 비용 수준으로 가입자 댁내 혹은 가입자 근처까지 광선로를 설치하기 위한 경제적 광가입자망의 구현을 최종 목표로 한다. 이를 위해 최대 64분기를 갖는 PON(Passive Optical Network) 기술, 622Mb/s 단위의 32x32ATM 스위치 기능을 갖는 OLT(Optical Line Termination), 전주 형 및 Desktop형 ONU(Optical Network Unit), 기존 전화선을 활용하기 위한 고속 디지털 모뎀 등을 각각 저가로 개발하고, 음성 및 광대역 멀티미디어 등 다양한 서비스를 수용하기 위한가입자와 서비스 노드 접속기술을 개발한다.

#### 나. 연구 개발 내용

- □ PON 기반의 저가형 OLT/ONU 시스템 개발

- o 망 형태 : ATM 또는 IP 기반의 PDS(Passive Double Star)형

- o OLT용량: 128 x 128 x 155Mbps(20Gb/s 분배스위칭)

- o ONU종류 : 전주 및 Desk-Top설치 형 (아파트/벽면형은 산업체 개발)

- o 가입자 접속대역 : 공유 형(전주, 평균10Mb/s), 개별 형(Desk-top, 30Mb/s)

- o 광전송 속도 : ITU-T 표준규격 수용(비대칭:622Mb/s하향,155Mb/s상향, 대칭 : 상하향 155Mb/s)

- o PON 분기율: ITU-T 권고수용(기본 분기율: 32분기, 최대 분기 율: 64분기)

- o 수용 ONU수 : 최대 1,024 개 수용

- o 수용서비스: POTS, VDSL,기반 광 대역 멀티미디어 서비스

- o 집적회로: ATM/IP스위치 칩, PON MAC칩 등 개발

- \* 전주형 ONU 제원 및 경쟁력

- 서비스:POTS, Power DSL기반 멀티서비스

- 전송속도: 하향 622Mbps, 상향 155Mb/s, 혹은 상·하향 대칭 155Mb/s

- 액세스 망 정보전달방식 : ATM 프로토콜

- 수용가입자 수 : 8-12가입자/ONU (목표 가입자 수는 경제성, 가입자 상화에 따라 최적화 고려)

- 가입자당 대역 : 1Mbps~10Mb/s

- 무게 : 8가입자 전주형 기준 15Kg

- 크기 : 8가입자 전주 형 기준 600 x 300 x 300 (DxWxH : mm)

- ※ 댁내 Desk-Top 설치 형 ONU는 전주 설치형 개발과 함께 응용 설계

- □ ONU 및 STB 탑재용 고속모뎀칩 개발

- o 변·복조 방식: ITU-T에 제안되는 VDSL 표준 방식 수용

- o 전송매체: 기존 전화선

- o 전송거리 : 최대 7km이내 전송속도 대비 전송거리 자동적응

- o 전송속도 : 하향 1.5Mbps-52Mbps(26Mb/s 이상은 경제성을 고려, 유보할 수 있음.

ITU-T권고), 상향 64Kbps-13Mbps

- o 소비전력 : 최대 1W이내, 1.5V 동작(국내 공정 기술 수준에 따라 변경)

- o 반도체설계 기술: CMOS,0.25µm(국내 공정 기술 수준에 따라 변경)

- o 목표가격(칩 당): 상하향 일체형(1종 80만 게이트 추정)으로 \$30(양산가격)

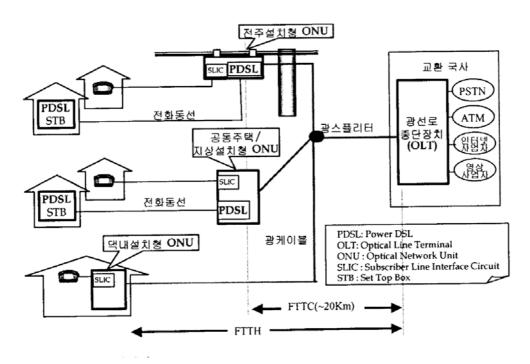

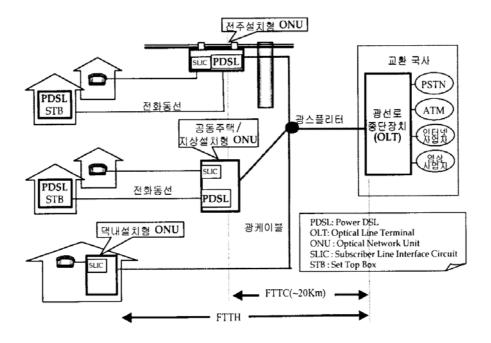

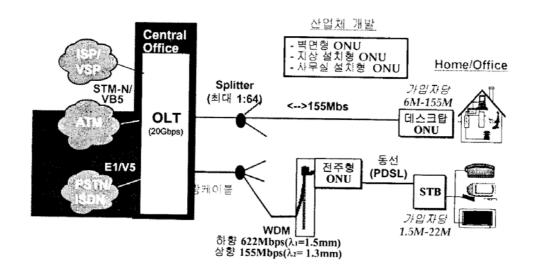

#### 다. 목표망 및 기술 개발 범위

- ※ PDSL은 VDSL 모뎀을 의미함

- ※ 어두운 영역은 기술 개발 범위를 표시함

# 4. 연구개발 결과

본 사업 1차 년도인 1999년도는 ATM-PON OLT/ONU의 기능 규격 작성과 관련핵심 기술을 개발하였고, 2000년은 1차 년도에 수행한 시스템 설계 내용을 기반으로 ATM-PON 시스템 시작품 개발하였고, 1차년도에 이어 계속하여 핵심 기술의 개발을 추진하였다. 최종년도인 2001년에는 ATM-PON 시스템 실용제품을 개발하였고, 핵심 칩셋 개발을 완료하였다. 그 주요 연구개발 결과는 다음과 같다.

## 가. ATM-PON 시스템

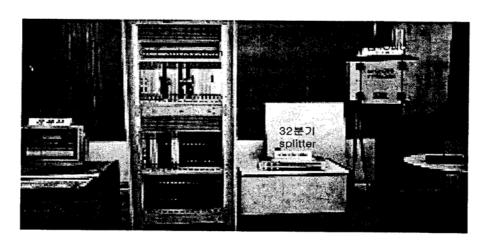

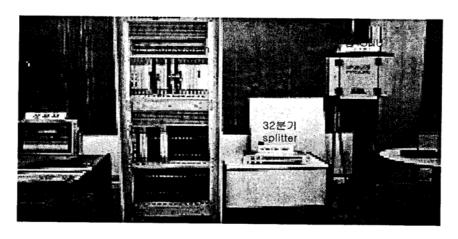

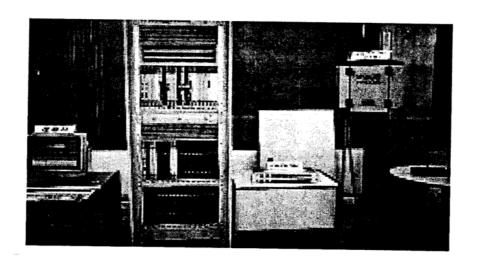

# (ATM-PON 실용 시스템 사진)

| 항목        |                    |                                                                                                  |  |

|-----------|--------------------|--------------------------------------------------------------------------------------------------|--|

| 서브시<br>스템 | 기능부                | 제원                                                                                               |  |

|           | 서비스노드<br>접속        | - ATM/STM1, ATM/STM4c, ATM VP/VC PVC 연결<br>- 100BASE-T 접속<br>- V.52 PSTN 접속<br>- nx64 TDM 전용선 접속 |  |

|           | 용량                 | - 622Mb/s 32x32 ATM 셀 스위치 (20Gb/s 용량)                                                            |  |

| OLT       | 가입자망<br>정합         | - ATM-PON 정합 Master 기능<br>비대칭: 하향 622Mbys, 상향 155Mb/s<br>대칭 : 하향 155Mb/s, 상향 155Mb/s             |  |

|           | 보호 절체              | - 1:1 보호 절체(스위치, 프로세서, 정합유니트)                                                                    |  |

|           | 집선율<br>ATM채널운<br>영 | - 1:1 ~ 28:1 범위 운영<br>(28:1 경우 622Mb/s PON 28 포트 설치 가능)                                          |  |

|           |                    | - VP, VP√VC 스위치(총 65K 연결 지원)<br>- CBR, VBR、ABR, UBR 지원<br>- UPC 기능(PCR, SCR, MBS)                |  |

| 누                   | 7             |                                          |  |

|---------------------|---------------|------------------------------------------|--|

| 항목                  |               | 제원                                       |  |

| 서브시스템               | 기능 부          | 세번                                       |  |

|                     | •             | - 최대 132분기                               |  |

| 분배                  | 망             | - full duplex protection지원               |  |

|                     |               | - 최대전송거리 20Km                            |  |

|                     | 가입자망          | - ATM-PON 정합 slave 기능                    |  |

|                     | 정합            | 지원속도: OLT 와 동일한 대칭/비대칭                   |  |

| 옥외ONU(              |               | 2 등급 priority에 따른 DBA 운영                 |  |

| FTTC/xD             | ATM           | - VP, VP/VC 운영                           |  |

| SL)                 | 채널            | UPC 기능(PCR, SCR, MBS)                    |  |

| SL)                 | 가입자정<br>합     | - 광대역: VDSL,(VDSL)etc - 협대역: PSTN, SHDSL |  |

|                     |               | - 설치 위치: 전주, 벽면 등 20~30 가입자 규모           |  |

|                     | 日             | 무게20Kg, 부피 42x42x21 cm <sup>3</sup>      |  |

|                     | 가입자망          | - ATM-PON 정합 slave 기능                    |  |

| 옥내<br>ONU<br>(FTTH) | / 1십시 경<br>정합 | 지원속도 OLT 와 동일한 대칭/비대칭                    |  |

|                     | (3) 百         | 2 등급 priority에 따른 DBA 운영                 |  |

|                     | 댁내 망<br>정합    | - ATM 25Mbps 정합,10/100BASE-T 정합          |  |

# 나. 광가입자 가입자당 채널 단가

| 최종 목표            |          | 개발 결과                   |

|------------------|----------|-------------------------|

| 기존 전화선           | FTTC/VDS | 217,000 원               |

| 초고속가입자망 수준의      | L        | (가입자 댁내 모뎀은 단가 계산에서 제외) |

| 비용('99년 당시 36만원) | FTTH     | 597,000원                |

<sup>※</sup> 상기 가격은 실용모델 시스템 제작에 투입된 비용을 기반으로 주정된 양산 단가임 선로 설치비용은 포함하지 않았음

# 다. 핵심 기술 및 핵심 칩 개발 결과물

| 칩명                       | 주요 기능 및 제원                                                        |

|--------------------------|-------------------------------------------------------------------|

| ATM-PON Master 칩         | 표준 ATM-PON Master 처리기능, PON-MAC/DBA 기능, 최대 64분기 지원                |

| ATM-PON Slave 칩          | 표준 ATM-PON Slave 처리기능, TDMA 제어                                    |

| 10Gb/s 가변 길이 패킷<br>스위치 칩 | 622Mb/s 16x16 스위 칭), ATM 셀 및 IP 패킷 처리,<br>출력버퍼 공유메모리 스위치, 8등급 Qos |

| ATM 계층 처리칩               | 622Mb/s ATM 셀 양방향 처리, UPC, 실시간 OAM처리, Qos 버퍼 링                    |

| VDSL 모뎀 칩                | 국제 표준규격 만족 QAM 변복조 방식, 비대칭 하향<br>26Mb/s 및 상향 13Mb/s, 대칭 13Mb/s    |

| ONU 통합 기능칩               | ATM-PON slave 및 ATM 계층처리 기능 통합                                    |

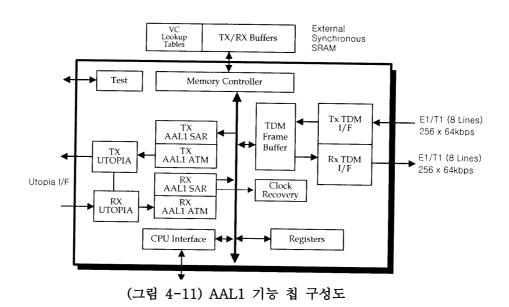

| ATM Circuit Emulation    | AAL1 SDT/DBCES 처리, 8 TDM 채널지원, 256VCC<br>지원 설계 완료 후 IP 화          |

## 5. 활용에 대한 건의

무한대의 대역폭 특성을 갖는 광섬유를 가입자망에 적용하여 가입자망의 병목현상을 근본적으로 해결하려는 노력이 1990년대 초반 이후 계속되어 왔다. 그러나, 기 설치된 전화선을 그대로 이용하는 xDSL 초고속 가입자망에 비하여 월등히 높은 비용 때문에 현재까지도 본 격적인 서비스 적용이 이루어지지 않고 있다. 본 사업에서는 현재의 xDSL, 기반의 초고속 가입자망의 단점을 보완하고, 나아가서 xDSL 의 다음 단계를 위한 초고속 가입자망으로서 ATM-PON 광가입자 시스템을 개발하였다. 특히 광가입자 장치의 본격 적용에 장애가 되고 있는 고비용 문제를 해결하는데 연구 개발의 초점이 맞추어졌다.

저가화를 달성하는 첫 번째 방안은 시스템의 주요 기능부를 단일 칩으로 구현하고, 비용 절 감의 효과가 극대화되는 규모로 시스템 용량을 증가시키며, 핵심 칩을 자체 개발하는 것이다. 이를 위해 본 사업에서는 ONU MAC slave 기능과 ATM 계층처리 기능이 통합된 칩과 ATM-PON MAC master 칩을 자체 개발하였고, 세계적으로도 아직 상용화 초기 단계인 10Gb/s 용량의 ATM, IP 겸용 스위치 칩을 국제 공동연구를 통하여 개발하였다. 또한, FTTC/VDSL 구성의 핵심 칩인 VDSL 모뎀칩을 자체 개발하였다. VDSL 모뎀 칩은 1TU-T에 제안되고 있는 4-band QAM 방식을 구현한 최초의 VDSL 모뎀 칩이다. ADSL 핵심 부품의 외산 도입으로 초고속 가입자망의 구축과정에서 많은 국부를 유출했던 상황을 생각해볼 때 VDSL 십의 자체 개발은 큰 의미를 갖는다.

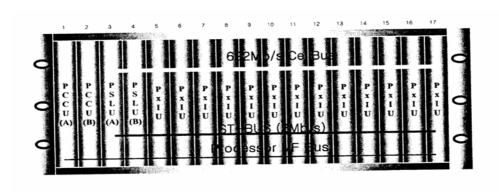

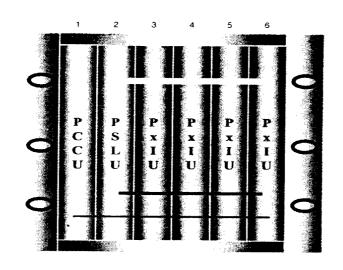

두 번째는 ONU 의 저가화이다. 옥외 ONU는 ONU 공통부에서 발생하는 비용 때문에 ONU에서 수용하는 가입자 수가 줄어듦에 따라 가입자당 단가는 상승한다. 본 사업에서는 제공서비스에 따라 융통성 있게 공통 부를 구성할 수 있도록 하여 ONU를 저가화할 수 있도록하였다. ONU에 사용되는 구성 유니트는 600Mb/s Backplane Cell Bus 접속 용량을 갖도록 설계되었기 때문에 100 가입자 규모의 ONU 셀프에도 적용할 수 있다. 또한 FTTH에적용되는 Desktop ONU는 저가의 상용 communication processor를 채용하고, ATM-POM Slave 구동 기능을 Communication processor에 탑재함으로써 저가화를 이루었다.

마지막으로 광송수신모듈의 저가화 이다. 본 사업에서는 광 송수신 모듈을 자체 개발하지는 않았지만, Lucent 의 전자부품과 국내 업체의 광부품을 사용하여 광모듈을 시험 제작함으로써 국내 자체 개발 및 저가화 가능성을 확인하였다. 그 결과 주요 광부품은 국내 산업체 개발이 가능한 것으로 분석되었다. 또한 가격면에서는 2001년 광송수신 모듈 가격의 급격한 하락으로 광송수신 모듈의 저가화는 자연스럽게 이루어지고 있다.

이러한 연구 길과 deep fiber access(FTTH, FTTC)를 구현하는 광가입자망을 당초의 목표 가격을 만족할 수 있는 수준으로 개발할 수 있었다. 향후 본 장비의 성공적인 상용화가 이루어질 것으로 기대되며, 본 가입자 장비를 활용할 수 있는 분야를 정리하면 다음과 같다.

- O FTTC/VDSL 광 가입자망

- 옥외 ONU에 VDSL 혹은 ADSL, 가입자 정합 장치를 구성하여 최종 가입자 인입구간 (lkm 이내)에서 기존의 전화선을 사용함으로써 20Mb/s 의 높은 대역폭을 경제적인 비용으로 제공함.

- 기존 ADSL에 의한 서비스가 곤란한 농어촌, 일반 주택지, 소규모 다세대 주택에 적합함.

- O FTTH/FTTB 광가입자망

- 가입자 댁내, SOHO 사무실내 혹은 소규모 빌딩 내까지 광섬유를 설치하여 궁극적인 광 가입자망 구축

- 신축 주거 지역, 중소사업자 등이 주 대상임.

- O 통합 서비스 액세스 platform으로 활용

- 협대역 광대역 통합 서비스가 가능함.

- 유선, 무선 통합을 위한 액세스 platform으로 활용 가능함.

- 새로운 파장을 통한 유선 방송 서비스 가능

## 6. 기 대 효 과

본 ATM-PON 시스템의 개발 결과와 확보된 핵심 기술은 경제성 있는 ATM-PON 광가입자 시스템을 성공적으로 상용화하는 데 크게 기여를 할 것이며, 예상되는 기대효과는 다음과 같다.

O 기존 전화용 동선과 새로운 광선로의 결합을 통해서 기존 전화 가입자에게 최대 52Mb/s 급까지의 초고속 정보통신서비스를 보다 경제적으로 제공함으로써 MIC에서 추진중인 초고 속정보통신망 구축사업을 보다 원활하게 추진할 수 있는 기반 제공

- O PON은 동선에 의한 관로 포화율을 줄이고, 최소 20Km이상의 전송거리를 확보함으로써 전송거리가 5km내외인 기존 동선루프의 한계를 극복하는 최적의 대안으로 부상될 것이며, 로컬국사(Central Office)의 수를 축소시킴으로써 가입자망 구축비용의 절감효과를 통해 치국계획의 전환을 이룰 수 있음

- O TDMA-PON/FTTH 기반의 FITL은 국내에서 2002년이 '시범사업의 해'이며, 2003년이 '상용서비스의 해'로 기록될 전망이며, 2005년 이후에는 본격적으로 적용될 전망임.

- O 북미에서 PON 시장은 2004년 20억불 가량의 시장을 형성할 것으로 예측되고 있으며 (RHK 자료), 그 이후 급속한 보급이 이루어져 2006년경에는 PON을 포함한 FTTH 가입자수가 265만 가구에 이를 것으로 예측하고 있음.(KMI Corp. 자료)

## SUMMARY

#### 1. Subject

A study on the development of low-cost access equipment technology

## 2. Purpose and significance of the project

#### A. Purpose

The purpose of this project is to implement a low-cost optical access network in which the optical cable can be extended directly into the customer's premise or to the neighbor of the customer place with a cost comparable to that of the xDSL system utilizing the existing copper cable. The scope of the project includes the development of ATM-PON (Passive Optical Network) technology with splitting ratio of 64, OLT(Optical Line termination) with a switching capacity of 622Mb/s 32x32, Pole and Desk-top ONUs, and VDSL modern chip to transmit more than 20Mb/s over the existing telephone line. It also includes development of access and service node interface technology to provide various services such as voice and broadband multimedia, and so on.

#### B. Significance of the project

The broadband access network are being deployed in various schemes, namely xDSL utilizing the existing access infra structure, FITL(Fiber In The Loop) using optical fibers, RITL(Radio In The Loop) using wireless radio channel, and satellite, etc. The access network has been undergone a drastic change in recent few years with the wide deployment of xDSL and HFC. It was very successful in providing a high-speed internet access. It, however, has several problems described in the following.

First, the current ADSL network has a limitation in bandwidth and does not provide the differentiated services. The communication service provider needs to create new services compensating the revenue decline expected in the voice service. The new services is surely realized on the high quality network in which the differentiated services are provided, the communication security is guaranteed, and the wide range of bandwidth is available to meet the ever increasing bandwidth demand from the user. The second problem is the so-called "digital divide" problem. The ADSL is deployed only in the highly populated area such as the apartment complex. The way of living, the culture, or even the competitiveness of the people tends to be determined by the accessibility to the high-speed network. The ADSL cannot, however, effectively be deployed in the rural area, the suburban, the single-family residential area, or the other remote area,

The optical access networks deeply deployed into the access network – namely, FTTH, FTTC, FTTN – are being considered the solution to overcome the limitation of the current high-speed access network. Especially, the PON(Passive Optical Network) is recognized as the cost effective optical access scheme and therefore there has been a lot of activities on the standardization, system developments, and field trials for the PON access networks in the North America, Europe, and Japan. This project aims to realize a FTTC/N/H optical access network providing the bandwidth ranged from a few Mb/s to hundreds Mb/s in a cost-effective way. To achieve the goal of low-cost, we chose PON scheme in which multiple customers can share a single optical fiber through a passive optical splitter. ATM was chosen as the data link protocol for QoS and the communication security. Most of the core technologies have been developed in the project and they include lOGb/s ATM/IP switch, ATM layer processor, ATM-PON MAC, and ONU intgrated function chip, and VDSL modem chip. The object of the low-cost has successfully been achieved as the result of all this effort.

The capacity of ONU was reduced to a single user in the case of FTTH and to  $10 \sim 30$  users in the case of FTTC/N. The coverage of PON is up to  $20 \rm Km$  and therefore users living in the remote place can access the network with a bandwidth over  $10 \rm Mb/s$ . The another feature of PON is the dynamic bandwidth allocation. The whole bandwidth of PON link can be temporary allocated to a single user on demand bases.

Consequently, the ATM-PON access network is considered a solution to compensate the demerit of the current ADSL network and also regarded as an effective scheme for the FTTH network expected to corne after xDSL. In recent few years, the cost of the optical transceiver has been drastically reduced and therefore the biggest barrier against FTTH are disappearing. It make the prospect of wide-scale FTTH deployment even more bright.

## 3. Contents and scope

#### A. The final goal of the project

The goal is to implement a low-cost optical access network in which the optical cable can be extended directly into the customer's premise or to the neighbor of the customer place with a cost comparable to that of the xDSL system utilizing the existing copper cable. The scope of the project includes the development of ATM-PON (Passive Optical Network) technology with splitting ratio of 64, OLT(Optical Line termination) with a switching capacity of 622Mb/s 32x32, Pole and Desk-top ONUs, and VDSL modem chip to transmit more than 20Mb/s over the existing telephone line. It also includes development of access and service node interface technology to provide various services such as voice and broadband multimedia, and so on.

## B. The scope and contents of the scope

- ♦ Development of a low-cost OLT/ONU system based on PON

- o Network architecture: ATM or IP based PDS(Passive Double Star) network

- o Capacity of OLT: 128x128 155Mb/s switching capacity (20Gb/s)

- o ONUs: Electric pole type(FTTC) and desktop type(FTTH) ONUs

- o Subscriber bandwidth: FTTC type(I0Mb/s), FTTH type(30Mb/s)

- o PON link transmission speed: ITU-T recommendation are supported, (symmetric type: 155Mb/s both for up and down stream, asymmetric type: 622Mb/s down and 155Mb/s up.)

- o PON splitting ratio: 32 (up to 64 in the maximum)

- o The number of ONU: 1024

- o Services: POTS, VDSL-based broadband multimedia services

- o ICs: ATM/IP switch IC, PON MAC chip

- Electric pole-type ONU features

- Services: POTS, VDSL(PowerDSL)-based multimedia

- Data rate: PON link transmission rate

- Data link protocol: ATM

- The number of subscribers: 8~12 subscribers

-Bandwidth per subscriber: 1~10 Mb/s

-Weight: 15kg for 8 subscribers

-Dimension: 600x300x300 mm<sup>3</sup> for 8 subscribers

♦ Development of a VDSL modem chip

o Modulation scheme: ITU-T proposal is supported

o Transmission media: telephone cable

o Transmission distance: up to 7km with a rate-adaptive feature

- o Transmission rate :  $1.5\sim52$ Mb/s in the down stream(could reserve the requirement of over 26Mb/s in consideration of the cost)

- o Power consumption: less than I Watts with 1,5 V voltage supply(could be changed according to the status of the available domestic foundry.)

- o Semiconductor technology: 0.25um CMOS (could be changed according to the status of the available domestic foundry.)

- o The price goal: unit price \$30

### C. Target Network Diagram

- \* PDSL means a VDSL

- \* The shadowed elements are included m the scope of the project

### 4. Results

In 1999, the first year of the project, the core technology development and system design for ATM-PON ONU/OLT were conducted. In 2000, the prototype for the ATM-PON system was designed, fabricated and tested. The development of the core technology has been performed following the first year. In final year, a commercial model for ATM-PON system was developed and the development for core chipset was completed. The major results for research and development activities are as follows.

# A. ATM-PON system

(Photograph of the whole ATM-PON system)

| intems         |                            |                                                                                                                                                   |

|----------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| sub-<br>system | function block             | Features                                                                                                                                          |

|                | Service node interface     | - ATM/STM1, ATM/STM4c, ATM VP/VC PVC - I00BASE-T interface - V5.2 PSTN interface - nx64 TDM leased line interface - 622Mb/s 32x32 ATM cell switch |

|                | Сараспу                    | (20Gb/s capacity)                                                                                                                                 |

| OLT            | Access<br>interface        | - ATM-PON MAC Master function<br>Asymmetric: 622Mb/s down, 155Mb/s<br>tip Symmetric: 155Mb/s both for down<br>and up                              |

|                | Protection                 | - 1:1 protection(switch, processor, interface plug-in unit)                                                                                       |

|                | Concentration              | - conentration ratio variable in the range of 1:1 28:1 (622Mb/s PON 28 port -> 1:28 concentration ratio)                                          |

|                | ATM<br>layer<br>processing | <ul><li>VP, VP/VC switch (65K connection)</li><li>Support CBR. VBR. ABR, UBR</li><li>UPC function(PCR, SCR, MBS)</li></ul>                        |

| Items                |                         |                                         |  |

|----------------------|-------------------------|-----------------------------------------|--|

| sub-system           | Function<br>Block       | Features                                |  |

| Access               |                         | -Maximum 1:32 split                     |  |

| Distrib              | oution                  | -support full duplex protection         |  |

| Netw                 | york                    | -maximu transmission distance : 20km    |  |

|                      | Access                  | -ATM-PON MAC slave function             |  |

|                      | Network                 | sspeed : the same as that of OLT        |  |

|                      | Interface               | -2 level priority DBA                   |  |

| Out door             | ATM Channel             | -VP,VP/VC operation                     |  |

| ONU                  |                         | - UPC function(PCR, SCR, MBS)           |  |

| (FTTC/xDSL)          | Subscriber<br>Interface | -Broadband : VDSL,(ADSL)etc.            |  |

| (I'II'C/XDSL)        |                         | - Narrow band :PSTN, SHDSL              |  |

|                      |                         | -Installation : electric pole, wall to. |  |

|                      |                         | cover 20~30 subscribers weight.         |  |

|                      |                         | 20kg, Dimension 40x50x20 cm             |  |

|                      | Access                  | -ATM-PON MAC slave function             |  |

| Indoor ONII          | Network                 | sspeed : the same as that of OLT        |  |

| Indoor ONU<br>(FTTH) | Interface               | -2 level priority DBA                   |  |

| (1, 1, 1, 11)        | Home                    | - ATM 25Mbps ,10/100BASE-T              |  |

|                      | network                 | ATM 20M0ps ,10/100DASE-1                |  |

# B. Equipment cost per subscriber

| Final goal                                                  |           | Result                            |

|-------------------------------------------------------------|-----------|-----------------------------------|

| Comparable to the cost of ADSL technology (\$300as of 1999) | FTTC/VDSL | \$ 180<br>(excluded user's modem) |

|                                                             | FTTH      | \$ 500                            |

<sup>\*</sup>The cable installation cost was not included in the price estimation

# C. Core technology and ICs developed in the project

| IC name             | Function and Feature                         |  |

|---------------------|----------------------------------------------|--|

| ATM-PON Master IC   | ATM-PON Master PON-MAC/DBA function,         |  |

| ATM TON Master IC   | Support of 64 splitting ratio                |  |

| ATM-PON Slave IC    | ATM-PON Slave function, TDMA MAC             |  |

| 10Gb/s variable     | 622Mb/s 16x16 switch, ATM cell IP packet     |  |

| packets witch       | switch Output buffer shared memory switch, 8 |  |

| packets witch       | level QoS.                                   |  |

| ATM lover processor | 622Mb/s ATM Cell layer processing, LPC, real |  |

| ATM layer processor | time OAM, QoS buffering                      |  |

|                     | Support ITU-T Standard, QAM modulation,      |  |

| VDSL modern chip    | asymmetric 26Mb/s in ds and 13Mb/s in us,    |  |

|                     | symmetric 13Mb/s                             |  |

| ONU function IC     | ATM-PON slave and ATM layer processing       |  |

| ATM Circuit         | AALI CDT/DDCDC 0 TDM 1 1 05C VCC             |  |

| Emulation           | AAL1 SDT/DBCES, 8 TDM channel, 256 VCC       |  |

### 5. Applications of the results

The FTTC or FTTH based optical access network can be built in a cost-effective way with ATM-PON system. The possible optical access network configurations are as follows:

#### O FTTC/VDSL Network

- -Provides more than 20Mb/s high-speed service by installing ONU near to the subscriber's place and using the existing telephone copper line in the final drop section to the subscriber.

- -Major application area is the rural area and the single-family residence area.

- O FTTH/FTTB Network

- Installing optical fiber to subscriber premises or business offices for unlimited bandwidth provision.

- O Integrated Access Platform

- Integrated services for narrow band and broadband

#### 6. Expected effects

The commercial model system of ATM-PON and the related core technologies are planned to be transferred to the manufacturers and expected to finally be commercialized. The expected effects are as follows:

- O It can provide high-speed information communication service up to 52Mb/s to the existing telephone subscribe1 by combining the existing copper wire and new optical fiber in FTTC network.

- O ATM-PON technology based on the low-cost passive optical devices will significantly reduce the initial fiber, deployment cost which is considered as the major obstacle in the way to the full optical network,

O Core chipsets such as ATM/IP switch, revised ASAH-L4, APMC, APSC, ONUC, VDSL modern chip, etc. will be used for the low-cost and moderate speed multimedia access.

O The TDMA-PON/FTTH will be in superior competition with the current copper subscriber network in terms of the channel cost per subscriber and the performance.

# CONTENTS

| Section 2. Scope of the Project                      |

|------------------------------------------------------|

| Section 3. Research Methodology                      |

|                                                      |

| Chapter 2. Development of ATM-PON System             |

| Section 1. System Design                             |

| Section 2. Core Technology                           |

| Chapter 3. Implementation and Test of Practice Model |

| Section 1. OLT                                       |

| Section 2. ONU                                       |

| Section 3. Web-based System OAM                      |

| section 4. System Integration Test                   |

| Chapter 4. Development of Core Chipset for ATM-PON   |

| Section 1. Overview                                  |

| Section 2. Implementation of Core Chipset            |

| Chapter 5. Conclusion                                |

| Abbreviations                                        |

| Appendix                                             |

Chapter 1. Introduction Section 1. Objectives

# 목 차

# 제 1 장 서 론

- 제 1 절 연구의 목적 및 필요성

- 제 2 절 연구의 내용 및 범위

- 제 3 절 연구수행방법 및 보고서 체계

# 제 2 장 ATM-PON 시스템 개발

- 제 1 절 시스템 설계

- 1. ATM-PON 고려사항

- 2. 시스템 기능 및 구조

- 3. 시스템 제원

- 제 2 절 핵심기술

- 1.버스트모드 광트랜시버

- 2. PON MAC/DBA

- 3. ATM/IP 고속 스위치

- 4. 고속신호 백플레인 전송

- 5. QAM-VDSL 모뎀 기술

## 제 3 장 실용모델 제작 및 시험

- 제 1 절 OLT

- 1. 개요

- 2. 광대역 셀프

- 3. 협대역 셀프

- 제 2 절 ONU

- 1. 개요

- 2. 전주형 ONU

- 3. 데스크탑 ONU

- 제 3 절 웹 기반시스템운용관리

- 1. 개요

- 2. EMS구조

- 3. 운용관리 방법

- 4. 감시제어 및 서비스 정합

# 제 4 절 시스템 통합시험

- 1. 시험시스템구성

- 2. 시험항목

- 3. 시험결과 및 분석

# 제 4 장 ATM-PON용 핵심 칩셋 개발

- 제 1 절 개요

- 제 2 절 핵심 칩셋 구현

- 1. ATM/IP 패킷 스위치

- 2, ATM-PON Master Controller (APMC)

- 3. ATM-PON Slave Controller (APSC)

- 4. ATM 계층처리 기능칩 (ASAH-L4)

- 5. QAM-VDSL 모뎀 칩

- 6. AAL1 SDT/DBCES 기능

제 5 장 결론

영문약어표

부록

# 표 목 차

- <표 2-1> 제공 서비스

- <표 2-2> ATM-PON 시스템의 주요제원

- <표 2-3> 시험 결과 요약

- <표 3-1> 시스템 시험 항목

- <표 4-1> ATM-PON 용 칩셋의 주요 제원

- <표 4-2> QAM-VDSL 모뎀의 성능 실험 결과

- <표 5-1> 연차별 연구 개발 내용

# 그림 목차

- (그림 1-1) 목표 망 구성도

- (그림 2-1) ATM-PON 시스템의 기능구성도

- (그림 2-2) ATM-PON 시스템 구조

- (그림 2-3) ATM-PON 시스템

- (그림 2-4) TDMA 기반의 상/하향 데이터 전송

- (그림 2-5) OLT 와 ONU 의 기능 블록

- (그림 3-1) ATM-PON OLT (POLS) 랙 구성도

- (그림 3-2) ATM-PON OLT (POLS) BB-Shelf의 유니트 실장도

- (그림 3-3) ATM-PON OLT (POLS) TPLB의 유니트 실장도

- (그림 3-4) TBIU 유니트 구성도

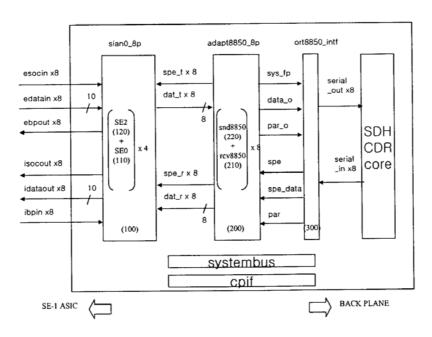

- (그림 3-5) TPOU 유니트 구성도

- (그림 3-6) 백 플레인 셀 포맷

- (그림 3-7) 두 개의 SE-1 칩을 사용한 20Gbps 스위칭

- (그림 3-8) SEO/SE2 FPGA 구조

- (그림 3-9) TMCU 프로세서 보드 전체의 불록도

- (그림 3-10) TEIU 구성도

- (그림 3-11) TBPU 구조

- (그림 3-12) TPLB 블록도

- (그림 3-13) Timing for High Speed Serial Interface (8.192Mbps)

- (그림 3-14) 19인치 함체용 ONU 형상

- (그림 3-15) 옥외 함체용 전주 형 ONU

- (그림 3-16) 전주형 ONU 전체 기능 블록

- (그림 3-17) PCCU 보드(MPC860 보드) 전체 블록도

- (그림 3-18) 데스크탑 ONU의 외관

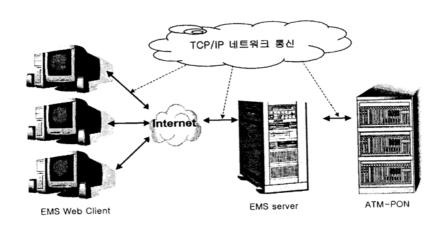

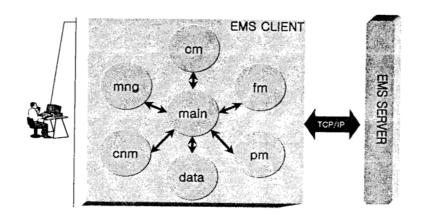

- (그림 3-19) ATM-PON EMS 구성도

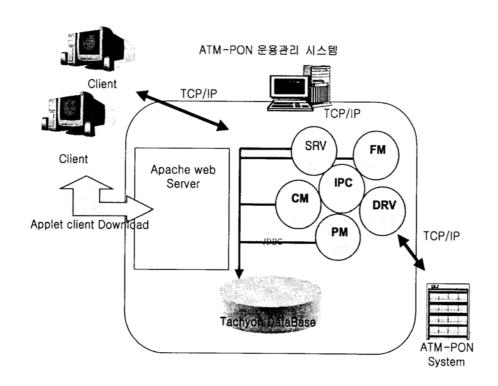

- (그림 3-20) ATM-PON EMS 서버 구조

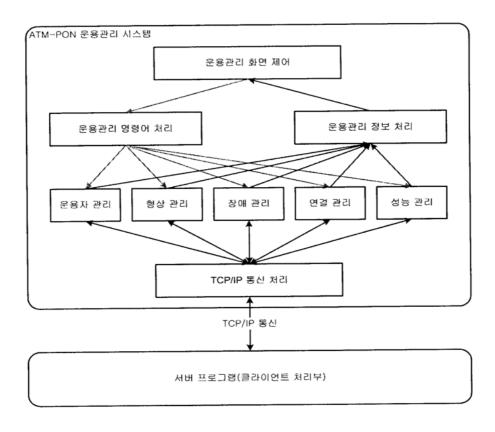

- (그림 3-21) ATM-PON EMS 클라이언트 기능 블록

- (그림 3-22) ATM-PON EMS 클라이언트 구조

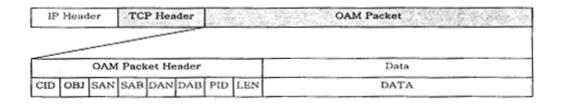

- (그림 3-23) EMS 서버-클라이언트간 운용관리 정보 패킷 구조

- (그림 3-24) EMS 서버-운용관리 불록 간 운용관리 정보 패킷 구조

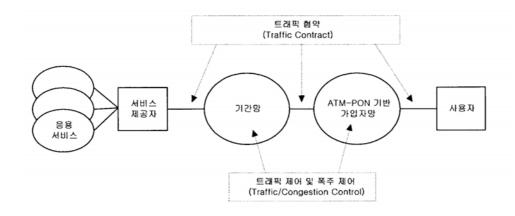

- (그림 3-25) ATM-PON 시스템 트래픽 제어 및 폭주제어 기능 구조

- (그림 3-26) 감시제어 구성도

- (그림 3-27) 서비스노드 인터페이스 유형

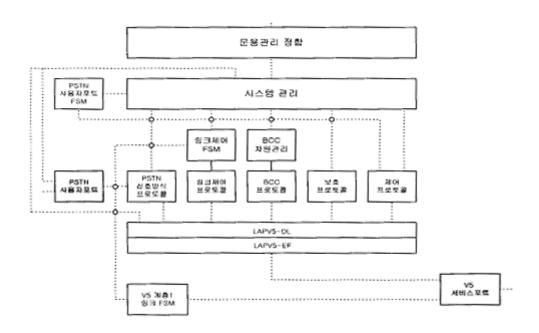

- (그림 3-28) V5 기반 서비스정합 기능구조

- (그림 3-29) VB5 기반 서비스 정합 기능구조

- (그럼 3-30) ATM-PON 시험 시스템 구성도

- (그림 4-1) ATM-PON 시스템의 핵심칩셋 구성도

- (그림 4-2) ATM/IP 패킷 스위치 칩 외관

- (그림 4-3) 스위치 입출력 데이터 포맷

- (그림 4-4) 스위치 칩 블록도

- (그림 4-5) APMC 주요 블록도

- (그림 4-6) APSC 칩의 블록도

- (그림 4-7) ASAH-L4 칩 기능 구성도

- (그림 4-8) QAM-VDSL 모뎀의 기능블록도

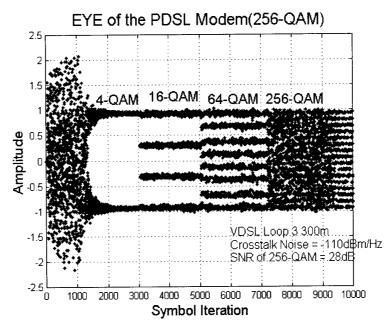

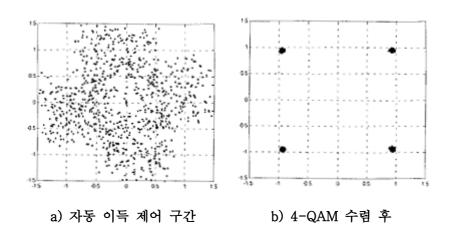

- (그림 4-9) 블라인드 등화기를 이용하여 왜곡 보상된 수신 신호의 EYE

- (그림 4-10) 블라인드 등화기를 이용하여 왜곡 보상된 수신 신호의 신호성상도

- (그림 4-11) AAL1 기능 칩 구성도

# 제 1 장 서 론

# 제 1 장 서 론

# 제 1 절 연구의 목적 및 필요성

정보화 사회를 지향하는 사회적 요구와 사용자 욕구에 부응하기 위해 정보통신 산업은 다각적인 방면에서 급속한 변화가 이루어지고 있다. 특히 액세스망 분야에서는 기존 동선 전화선을 이용하여 수 Mb/s 급의 고속 데이터를 전송하는 ADSL(Asymmetric Digital Subscriber Line)이 1998년 이후 급격히 보급되어 2001년11월 현재 가입자가 4백만에 이르고 있다. 케이블모뎀, LAN 방식, 위성 등 기타 다른 방식으로 접속하고 있는 가입자를 포함하면 총 7백만 가입자가 Mb/s 급 초고속서비스를 받고 있다. 이제는 대부분의 일반인들이 인터넷을 통하여 생활 정보를 얻고 있고, 인터넷이 보편화되지 않았던 시대로 돌아가는 것은 상상할 수도 없게 되었다. 가히 초고속 정보 통신이 생활화된 시대에 살고 있다 하겠다.

그러나, 급속히 보급된 현재의 초고속 통신망은 풀어야할 몇 가지 과제를 안고 있다. 우선 통신사업자가 가지고 있는 문제로서 현재의 음성서비스, 전용선 서비스에 필적할 수 있는 새로운 서비스의 창출이다. 새로운 서비스는 기존의 음성급 서비스, 인터넷 이외에도 텍스트, 화상, 영상이 복합화 된 다양한 응용서비스와 유선, 무선 등 다양한 접속 형태를 가지며. QoS(Quality of Service)와 통신보안을 보장하는 고품질, 고 신뢰성 서비스를 경제적으로 제공할 것을 요구하고 있다. 통신 사업자들은 이를 위해 현재 가입자당 평균 30kbps 의트패 픽 발생을 가정하여 설계된 통신망을 가입자당 수 Mbps의 평균 트래픽이 발생하는 경우를 수용할 수 있도록 통신망 개선을 추진하고 있다. 이러한 새로운 수요에 대처하기 위해 초고속 가입자망은 현재의수 Mb/s에서 10Mb/s 이상으로 대역폭을 확대할 것이 필요하며, 동시에 QoS가 보장되는 차별화된 접속 기능을 갖도록 개선할 것이 요구된다.

두 번째 문제는 현재 초고속 가입자망이 아파트 등 집단 주거지 위주로 구축되어 있다는 것이다. 농어촌, 일반 주택, 소규모 다세대 주택 등에 ADSL 등 현재의초고속 가입자망을 설치하기에는 성능과 경제성 문제로 보급이 지연되고 있다. 초고속 서비스를 받지 못하는 지역은 문화적으로도 소외되는 소위 "digital divide" 가 사회적 문제로 제기되고 있는 상황이다. 이를 해결하기 위해서는 가입자까지의 거리, 가입자 주거 형태에 관계없이 경제적이며 안정적 품질을 갖는 가입자망을 제공할 수 있는 기술의 개발이 요구된다.

초고속 가입자망은 기존 가입자망 기반 시설을 그대로 활용하는 xDSL, 광 선로 기술을 기반으로 하는 FITL(Fiber In The Loop), 무선기술의 RITL(Radio In The Loop), 위성 등다양한 방안이 있다.

xDSL 은 3.6km 까지 최대 6Mb/s의 데이터 서비스를 제공할 수 있는 ADSL이 대량으로 보급되어 있고, RITL로는 광대역 무선 LAN이 가입자망 영역으로 확장되고 있는 추세이다. FITL은 망사업자의 단국에서가입자까지에 이르는 피더선, 분배선, 인입선으로 구성된 가입자 선로의 일부 혹은 전부를 광으로 대체하는 방식이다. 광이 종단된 위치에 따라 FTT Cab(Cabinet),FTTC(Curb), FTTN(Neighbor), FTTO(Office), FTTB(Building) 등의 방식과 궁극적으로 가입자 댁내까지 광선로를 설치하는 FTTH(Home), 그리고 기존의 CATV의 동축 케이블 분배 망 일부를 광 선로로 교체한 HFC(Hybrid Fiber Coax)방식이 있다. 국내에서는 대형 빌딩에 대한 FTTB망이 1990년대 후반 집중적으로 설치되었으며, 현재는 규모가 작은 빌딩으로 보급이 확대되고 있다. HFC도 1990년대 후반 케이블모뎀을 이용한 초고속 서비스를 위해 동축케이블 분배 망을 개선하는 방안으로 적용되었다. 이와 같이 1990년대 후반부터 FITL 방식이 다양한 형태로 개발, 적용되어 왔으며, 현재는 광 선로를 좀더가입자에 접근시키기 위한 FTTC,FTTN,FTTH 광가입자 시스템이 개발되고 있다. FTTC/FTTN/FTTH를 경제적으로 구현하는 방식으로는 수동광분기기를 기반으로 하는 PON(Passive Optical Network) 이 유력한 방식으로 인식되고 있으며, 북미, 일본, 유럽 등을 중심으로 관련 기술의 표준화, 시스템 개발 및 사업 적용이 진행되고 있다.

본 연구 개발은 수 Mb/s에서 수백 Mb/s 범위의 대용량 대역폭을 가입자 요구에 따라 융통성 있게 제공하고, 광선로를 가입자 댁내 혹은 인근에 설치하는 FTTC/N/H 광 가입자망을 저가로 구축할 수 있는 기술을 개발하는 것을 목표로 하였다. 개발된 광가입자망은 「OLT-가입자 분배 망-ONU」로 구성된다. 가입자 분배망은 망 단국에 설치되는 OLT와 가입자 댁내 혹은 가입자 인근 지역에 설치되는 ONU 사이를 연결하는 광선로를 의미한다. 저가 구현을 위해 한 개의 광섬유를 여러 가입자가 공유하는 PON 방식을 가입자 분배 망으로 선택하였다. 그리고, 가입자규모가 적은 경우에도 초기 투자 부담이 적도록 시스템 용량, 구조 설계에 고려하였으며, 가입자 채널당 비용 구성비가 높은 ONU의 저가 화에 많은 노력을 하였다. 또한 ONU, OLT의 주요 기능부들은 각각 단일 칩으로 구현하여 시스템 저가 화를 이룰 수 있도록 하였다. QoS 의 보장과 보안성 확보를 위해 ATM을 데이터 링크프로토콜로 사용하였고, 주요 핵심 기능인 ATM 계층처리칩 및 스위치칩을 자체 개발하여 적용하였다.

PON 방식을 이용할 경우 ONU의 가입자 수용 규모를 FTTH 경우는 단일 가입자, FTTC/N 경우는  $10\sim30$  가입자 규모로 줄일 수 있고, 전송 거리도 최대 20km에 이르기때문에 농어촌, 일반주택지, 소규모 다세대 주택 등에 경제적으로 적용하기에 적합하다. 또한 망 단국에서 가입자 방향인 하향으로는 622Mb/s, 그 반대 방향인 상향으로는 155Mb/s의 광전송 속도를 가지며, 32개의 ONU가 한 광 선로를 공유할 경우 ONU당 평균 하향 20Mb/s 상향 5Mb/s의 대역폭 제공이 가능하다. 또한, PON 방식의 고유 특성으로서, 가입자가 요구할 경우 순간적으로 광선로 전체 속도, 즉 155Mb/s 혹은 622Mb/s 까지 한 ONU가 사용할 수 있도록 동적으로 대역폭을 할당할 수 있다.

이러한 특성을 고려해 볼 때 본 연구 개발에서 추진한 ATM-PON 가입자 망은 전술한 현재의 초고속 가입자망의 현안을 해결하는 방안이며, 나아가서 궁극적인 FTTH 망을 구축하는 유력한 방식이 될 것이다. 최근 1-2년 사이 FTTH망의 보급에 큰 장애가 되어 왔던 광송수신부품 가격이 급격히 하락하고 있어 FTTH망의 본격적이 적용 전망을 더욱 밝게 해주고 있다.

# 제 2 절 연구의 내용 및 범위

#### 1. 최종 연구목표

기존 동선 전화선 수준의 비용으로 가입자 댁내, 혹은 가입자 근처까지 대용량 광케이블을 설치하기 위한 경제적 광가입자망의 구현을 최종 목표로 하며, 이를 위해 최대 64분기를 갖는 ATM-PON(Passive Optical Network) 기술, 622Mb/s단위로 32x32 ATM 스위치 기능을 갖는 OLT, 전주 형 및 Desk-top형 ONU, 기존전화선을 활용하기 위한 고속 디지털 모뎀 등을 각각 저가, 상용화 수준으로 개발하고, 전화, 광 대역 멀티미디어 서비스 등 다양한 통신 및 영상 서비스를 수용하기위하여 가입자와 서비스 노드에 협대역 및 광대역의 다양한 접속 기능을 제공하는 기술을 최종적으로 개발한다.

(그림 1-1) 목표 망 구성도

### 2. 연차별 연구내용 및 범위

#### 가.1차년도 (1999): 핵심 기술 설계/개발, 시스템 설계

- 1) 시스템 엔지니어링

- o PON 시스템 벤치마킹

- PON/VDSL 사용자/시스템 요구사항 정의

- o PON 시스템 설계 및 기능규격서 작성

- ㅇ PDS(Passive Double Star) 네트워크 보호복구방식연구

- 2) OLT/ONU 소요 핵심기술 개발

- OLT 설계 및 핵심기술 개발

- o 저가형 ONU/STB 설계 및 핵심기술 개발

- 3) Power DSL 핵심기능 설계 및 시뮬레이션

- ㅇ PDSL, 기능 규격 정의 및 표준화 활동

- ㅇ 변복조 알고리즘 개발

- o Software 탑재 방식으로 복수의 변 복조 방식을 수용하는 PDSL 모뎀 Platform 보드설계 및 제작.

- ㅇ 기타 모뎀 물리 계층 부가 기능 설계

## 나.2차년도 (2000) : 시스템 시작품 제작/시험

- 1) 시스템 엔지니어링

- o 시스템 벤치마킹 계속

- ㅇ 사용자 요구사항 / 시스템요구사항 보완

- TDMA 기반 ATM-PON 시작품 시스템 설계, 제작 및 시험

- 2) ATM/IP기반 OLT장치 시작품 개발

- ㅇ 622Mb/s급 32x32 ATM/IP Switch Fabric 설계 및 실험

- 32분기 하향 622Mbps. 상향 155Mb/s ATM-PON 실용 개발

- ㅇ 대용량 처리 backplane 인터페이스 기술 개발

- ㅇ ITU-T표준 하향 622Mb/s, 상향 155Mb/s급 PON-MAC master ASIC 칩 설계

- 10Gb/s급 ATM/IP겸용 패킷 스위치 칩 설계

- ㅇ 고밀도 광 선로 종단/분배/시험 모듈 제작 및 실험

- TDMA기반 ATM-PON 감시제어 및 유지보수 기능 개발

- o TDMA기반 가입자 대역 할당 알고리즘 및 연결 관리 기능 개발

- o TMN기반 광가입자 액세스 망 통합관리 Agent

- 3) 저가형 ONU/STB 시작품 개발

- ㅇ 하향 622Mb/s, 상향 155Mb/s급 PON-MAC slave 칩 ASIC 안정화 보완

- 저가형 155Mbps 버스트모드 광 송신기 개발

- ㅇ 멀티미디어 정합 기능 개발

- 집선 및 다중화 ASIC 칩 설계

- 고밀도 PON기반 광가입자망 유지보수, 감시제어 기능 개발

- ㅇ 급전 기능 설계 및 실험

- 4) Power DSL 모뎀 칩 설계

- ㅇ QAM-Power DSL 모뎀 규격 정의

- o 고속 QAM 변 복조 알고리즘 설계 및 최적화

- 고성능 전송거리 확장(RS 부호화 및 인터리빙) 상세 설계

- QAM 방식 PDSL 모뎀 Platform 보드(PDSL 모뎀 시작품)를 이용한 알고리즘 검증

- o QAM 방식 PDSL 모뎀 칩 구현을 위한 핵심 core 개발: equalizer, clock/timing recovery

- PDSL 모뎀 칩 설계 (0.25um 혹은 0.18um CMOS 적용)

#### 다. 3차년도 (2001) : 실용모델 시스템 개발

- 1) 시스템 엔지니어링

- ATM-PON 실용 모델 시스템 규격 작성 및 시스템 시험 평가

- o ATM-PON 시스템 요구사항 작성

- ATM-PON 광가입자 사업화 방안 모색

- 실용모델 시험 및 산업체 제품 제작지원

- 2) ATM-PON OLT/ONU 실용모델 시스템 개발

- PON 광선로 종단/분배/시험 모들 안정화 보완

- OLT 기능 개선, 안정화, 보완 개발·

- OLT 시스템 연결 관리, 감시제어, 운용관리부 안정화 보완

- o 전주형/ Dcsk-Top형 ONU 기능의 저가화, 안정화 보완 개발

- o ONU 장치 감시제어, 운용관리부 안정화 보완

- ㅇ 광가입자 액세스망 통합 관리 시스템 개발

- 3) ATM-PON 핵심 기술 개발

- ATM/IP 패킷 스위치칩 제작 및 20Gb/s ATM 스위치 패브릭 구성

- PDSL 모뎀 칩 설계 및 시스템 적용

- ATM-PON MAC 2차 버전 칩 설계 및 시스템 적용

- o 소형 ONU 통합 기능 칩 설계

# 3. 최종 연구 결과 요약

# 가. ATM-PON 실용 모델 시스템 개발 완료

# 1) 시스템 제원

| 항목                       |             |                                                                                                      |

|--------------------------|-------------|------------------------------------------------------------------------------------------------------|

| 서브시스<br>템                | 기능부         | 제원                                                                                                   |

|                          | 서비스노드<br>접속 | - ATM/STM1, ATM/STM4c, ATM VP/VC PVC 연<br>결<br>- 100BASE-T 접속<br>- V52 PSTN 접속·<br>- nx64 TDM 전용선 접속 |

|                          | 용량          | - 622Mb/s 32x32 ATM 셀 스위치 (20Gb/s 용량)                                                                |

| OLT                      | 가입자망<br>정합  | - ATM-PON 정합 Master 기능<br>비대칭: 하향 622Mb/s, 상향 155Mb/s<br>대칭 : 하향 155Mb/s, 상향 155Mb/s                 |

|                          | 보호 절체       | - 1:1 보호 절체(스위치, 프로세서, 정합유니트)                                                                        |

|                          | 접선율         | - 1:1 ~ 28:1 범위 운영<br>(28:1 경우 622Mb/s PON 28 포트 설치 가능)                                              |

|                          | ATM채널운<br>영 | - VP, VP/VC 스위치(총 65K 연결 지원)<br>- CBR, VBR, ABR, UBR 지원<br>- UPC 기능(PCR, SCR, MBS)                   |

| 분배망                      |             | - 최대 1:32분기<br>- full duplex protection지원<br>- 최대 전송 거리20Km                                          |

| 옥외ONU(<br>FTTC/xD<br>SL) | 가입자망<br>정합  | - ATM-PON 정합 slave 기능<br>- 지원속도 OLT 와 동일한 대칭/비대칭<br>2 등급 priority에 따른 DBA 운영                         |

|                          | ATM 채널      | - VP, VP/VC 운영<br>- UPC 기능(PCR, SCR, MBS)                                                            |

|                          | 가입자정합       | - 광대역: VDSL,(VDSL)etc - 협대역: PSTN,<br>SHDSL<br>- 설치위치: 전주, 벽면 등 20~30 가입자 규모                         |

| 옥내<br>ONU<br>(FTTH)      | 가입자망<br>정합  | - ATM-PON 정합 slave 기능<br>지원속도: OLT 와 동일한 대칭/비대칭<br>2 등급 priority에 따른 DBA 운영                          |

| (1 1 111)                | 댁내망 정합      | - ATM 25Mbps 정합, 10/100BASE-T 정합                                                                     |

# 2) 시스템 구성

# □ 전체 시스템

# □ OLT

| 항목      | 설명                 |  |  |

|---------|--------------------|--|--|

|         | - 가입자망정합,          |  |  |

| 키노      | 서비스노드조합            |  |  |

| 기능      | - ATM 채널 다중 및 교차연결 |  |  |

|         | - ATM 트래픽 관리       |  |  |

|         | - TPOU 등 총 9종 유니트  |  |  |

| 구성      | - 2.5Gb/s 용량/유니트   |  |  |

|         | - 유니트간 1+1 보호 절체   |  |  |

| 후면판     | - 1Gb/s 고속 데이터선    |  |  |

| 구인헌<br> | - 40Gb/s 용량        |  |  |

| 운영관리    | - 장치 관리자 접속 RS232  |  |  |

|         | - 운영관리시스템접속 TCP/IP |  |  |

# □ PON 분배장치

| 항목      | 설명                 |  |

|---------|--------------------|--|

| 기능      | - 광수동 분배           |  |

| /10     | - 광선로 보호 절체        |  |

|         | - 8분기              |  |

| 손실      | - 16분기             |  |

|         | - 32분기             |  |

| ນະໂດໄະໂ | OLT, ONU 사이 옥외 광선로 |  |

| 설치위치    | 구간                 |  |

# □ 전주 설치형 ONU(FTTC-ONU)

| 항목   | 설명                      |  |

|------|-------------------------|--|

|      | - PON 가입자망 정합           |  |

| 기능   | - 가입자 정합                |  |

| /10  | - ATM 채널 다중             |  |

|      | - ATM 트래픽 관리            |  |

| 구성   | - PSLU 등 총 3종           |  |

| 후면판  | - 600Mb/s cellbus(ATM용) |  |

| 수인판  | - 8Mb/s ST-Bus(TDM용)    |  |

|      | - 장치 관리자 접속 RS232       |  |

| 운영관리 | - ATM 채널을 통한 OLT 와      |  |

|      | OAM 접속                  |  |

## □ 옥내형 ONU (FTTH-ONU)

| _  |                         |  |

|----|-------------------------|--|

| 항목 | 설명                      |  |

|    | - PON 가입자망정합, 댁내망정합     |  |

|    | - Bridge, IP routing    |  |

| 기능 | - IPoA 혹은 Ethernet over |  |

|    | ATM                     |  |

|    | - DHCP server 혹은 NAT    |  |

|    | - 댁내망접속: ATM25, 10/100  |  |

| 구성 | Ethernet                |  |

|    | - PON 가입자망 접속           |  |

# □ ATM-PON 운영관리 시스템

| 항목   | 설명                 |  |  |

|------|--------------------|--|--|

|      | - 가입자망정합, 서비스노드정합  |  |  |

| 기능   | - ATM 채널 다중 및 교차연결 |  |  |

|      | - ATM 트래픽 관리       |  |  |

|      | - TPOU 등 총 9종 유니트  |  |  |

| 구성   | - 2.5Gb/s 용량/유니트   |  |  |

|      | - 유니트간 1+1 보호 절체   |  |  |

| 저소   | - 1Gb/s 고속 데이터선    |  |  |

| 접속   | - 40Gb/s 용량        |  |  |

| 운영관리 | - 장치 관리자 접속 RS232  |  |  |

|      | - 운영관리시스템접속 TCP/IP |  |  |

#### 나. ATM-PON 실용 모델 시스템 단가

본 연구에서는 전화선 모뎀 수준으로 광가입자 장치의 가격을 낮추는 것을 주요 목표로 하였고, 그 가격 수준은 사업 제안 시기인 1999년 현재 가격으로 가입자 채널당 300불 수준이었다. 본 항에서는 실용시스템을 양산하였을 경우 가입자 채널 당 재료비/제작비를 계산하였다. ONU가 가입자 채널당 가격에 많은 영향을 주고 있고, 특히 PON용 광 송수신기모듈의 가격이 채널 단가에 크게 영향을 주는 것으로 분석되었다.

본 연구에서는 광송수신기 모듈의 개발이 연구 목표에서 제외 되었지만, 향후 국내 개발 가능성 타진과 양산 가격의 추정을 위해서 PON 모듈의 시험 제작을 추진하였다. 시험 제작은 국내 업체로부터 BIDI 모듈은 제공받고, Lucent 로부터 Burst-mode 전치증폭기, AGC 주증폭기, 클럭 추출 IC 등을 제공받아 모듈을 구성하였다. BIDI(Bidirectional) 모듈은 두 개의 서로 다른 파장을 사용하여 한 광섬유로 송신과 수신을 동시에 할 수 있도록 한 LD, PD, WDM 분기/결합기로 구성된 광 부품이다. PON용 광 송수신 모듈의 특성을 좌우하며, 가격의 대부분을 차지한다. 본 연구에서는 PON 광 송수신모듈의 시험 제작을 통해 국내 기술로 충분히 개발 할 수 있는 것으로 파악하였고, 향후 양산 시 가격을 예측할 수 있었으며, 본 가격 분석은 이러한 연구 결과에 기초한 것이다.

155Mb/s 상 하향 전송하는 PON 광 송수신기는 현재 OLT 용은 2500불, ONU 용은 850불 수준이다. 이러한 가격으로는 xDSL 등 다른 초고속망 대안과 가격 경쟁력을 갖지 못하며, PON 광가입자망을 본격적으로 적용하지 못한 가장 큰 이유가 되고 있다. 여기에는 BID1 모듈의 고성능화 및 저가화가 중요한 기술적, 경제적 문제로 분석되고 있다. ATM-PON 시스템 기능 및 구조를 규정하는ITU-T G.983.1 에서는 BIDI 모듈의 배제를 위해 두 가닥의 광섬유를 사용하여 송신과 수신을 별도의 광섬유를 통하여 하는 것도 허용하고 있다. 따라서. BIDI 모듈을 구비한 PON 광 송수신 모듈은 양산 적용할 경우에는 일반 광송수신기 모듈과 비교되는 가격을 형성해야 될 것이며, 현재 국내외 다수의 업체에서 저가, 고성능BIDI 모듈을 개발하고 있으므로, 곧 일반 광송수신기와 유사한 가격을 형성할 것으로 판단된다.

한편 2001년을 기점으로 155Mb/s 용 광송수신기 가격이 급격히 하락하여 9만 원대를 형성하고 있으며, 2002년에는 5~6만 원대로 하락할 것으로 관련 업계에서 전망하고 있다. 본 시스템 가격 분석에서는 이러한 점들을 고려하여 OLT용 155Mb/s PON 광 송수신모듈은 160만원, ONU용 광 송수신 모듈은 11만원으로 양산 가격을 추정하였다.

# 1) FTTC/VDSL 경우 VDSL, 가입자당 채널 단가

| 항<br>목      | 설명                                                                                                      | 가격(원)      | 구성비 |

|-------------|---------------------------------------------------------------------------------------------------------|------------|-----|

| А           | OLT 공통부: - rack & power(3 셀프 실장,1/3 가격만<br>계산) - 각 Shelf 내 공통 부는 프로세서 유니트,<br>클럭유니트, 스위치 유니트 각 2매씩으로 구성 | 15,760,000 | 2%  |

| В           | OLT 망정합부(1:1 접선 고려)                                                                                     | 2,303,000  | 1%  |

| С           | OLT 가입자 정합 부(PON 2포트7, 광모듈<br>제외)                                                                       | 2,020,000  | 1%  |

| D           | OLT 가입자 정합 부 광모듈(PON 2 포트)                                                                              | 3,250,000  | 1%  |

| Е           | 1:32 수도 -광분배기(PON 2 포트 지원->2조)                                                                          | 3,000,000  | 1%  |

| F           | ONU 18 VDSL 가입자(광모 듈 제외)                                                                                | 3,510,000  | 91% |

| G           | ONU 광모 듈                                                                                                | 110,000    | 3%  |

| 가입:<br>(A/4 | 자 채널당 가격.<br>+ B+ C+ D+ E+ 64x(F+ G))/(2x32x18)                                                         | 214,000    | 원   |

<sup>(</sup>주) 1. 가입자 댁내에 설치하는 VDSL 모뎀은 가격 계산에서 제외되었음

## 2. PON 분기 율은 32분기

# 2) FTTH 경우 (32분기 PON에 대해서)

| 항<br>목                                             | 설명                                                                                                | 가격(원)      | 구성비 |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------|------------|-----|

| A                                                  | OLT 공통 부: - raCk & power(3 셀프 실장,1/3 가격만 계산) - 각 Shelf 내 공통부는 프로세서 유니트, 클럭유니트, 스위치 유니트 각 2매씩으로 구성 | 15,760,000 | 10% |

| В                                                  | OLT 망정합부(1:1 접선 고려)                                                                               | 2,303,000  | 6%  |

| С                                                  | OLT 가입자 정합부(PON 2포트, 광모듈 제외)                                                                      | 2,020,000  | 6%  |

| D                                                  | OLT 가입자 정합부 광모듈(PON 2 포트)                                                                         | 3,250,000  | 8%  |

| Е                                                  | 1:32 수도 광분배기(PON 2 포트 지원->2조)                                                                     | 3,000,000  | 8%  |

| F                                                  | DesktopONU (광모듈 제외)                                                                               | 260,000    | 44% |

| G                                                  | DesktopONU 광모듈                                                                                    | 110,000    | 18% |

| 가입자 채널당 가격. (A/4+B+C+D+E+64x(F+G))/(2x32) 597,000원 |                                                                                                   |            | 원   |

# 다. 핵심 칩 개발 결과물

| 칩명                       | 주요 기능 및 제원                                                       |

|--------------------------|------------------------------------------------------------------|

| ATM-PON Master 칩         | 표준 ATM-PON Master 처리기능, PON-MAC/DBA<br>기능, 최대 64분기 지원            |

| ATM-PON Slave 칩          | 표준 ATM-PON Slave 처리기능, TDMA 제어                                   |

| 10Gb/s 가변 길이 패킷<br>스위치 칩 | 622Mb/s 16x16 스위 칭, ATM 셀 및 IP 패킷 처리,<br>출력버퍼 공유메모리 스위치, 8등급 Qos |

| ATM 계층 처리칩               | 622Mb/s ATM 셀 양방향 처리, UPC, 실시간<br>OAM처리, Qos 버퍼 링                |

| VDSL 모뎀 칩                | 국제 표준규격 만족, QAM 변복조 방식, 비대칭 하향<br>26Mb/s 및 상향 13Mb/s, 대칭 13Mb/s  |

| ONU 통합 기능 칩              | ATM-PON slave 및 ATM 계층처리 기능 통합                                   |

| ATM Circuit              | AAL1 SDT/DBCES 처리, 8 TDM 채널지원,2                                  |

| Emulation                | 56VCC 지원                                                         |

# 라. 기타 연구 결과물

| 항목    | 연구 결과물                                   |

|-------|------------------------------------------|

| 기술 문서 | TDP(시스템 개발 문서) : 196편<br>TM(기술 메모): 158편 |

| 특허    | 국제특허 : 출원 13건<br>국내특허 : 등록 2건, 출원 7건     |

| 논문    | 국제발표 : 12편<br>국내발표 : 35편                 |

| 프로그램  | 28건                                      |

## 마. 연구 협력 활동

| 항목     | 협력 기관                  | 협력 내용                                                                                               |

|--------|------------------------|-----------------------------------------------------------------------------------------------------|

| 국제공동연구 | Erlang System          | 10Gb/s 가변길이 패킷 스위치 칩 개발<br>-ETRI칩 기능 및 규격, ASIC 구현, 시험 및<br>시스템 적용<br>- Erlang 칩 구조 설계, ASIC 구현, 제작 |

| 국내공동연구 | KT, 삼우통신,<br>두일전자, NDS | ATM-PON 시스템 개발 - ETRI: 기능규격, 설계, 제작, 시험 - KT: 기능 규격, 망 적용 계획 - 삼우통신, 두일 전자, NDS: 시스템 개발,<br>상용화     |

|        | 서두인칩                   | VDSL 모뎀 개발<br>- ETRI : 기능 규격, 설계, 시험 및 적용<br>- 서두인칩 : 설계, 제작                                        |

|        | A-PACK                 | ONU 함체개발<br>- ETRI: 기능 규격<br>- A-PACK : 설계, 제작 및 시험                                                 |

| 위탁/용역  | ICU                    | ATM-PON 인터넷 적용 기술<br>- 적용시나리오 연구<br>- MPLS 기능 개발                                                    |

|        | 전북대                    | VDSL 모뎀 설계                                                                                          |

|        | 경북대                    | AAL2를 이용한 음성/데이터 동시 전송 방안                                                                           |

|        | 항공대                    | Ethernet - PON 기술 조사                                                                                |

# 제 3 절 연구수행방법 및 보고서 체계

#### 1. 연구수행방법 및 연구체계

저가형 광가입자 장비 기술 개발은 HAN/B-ISDN 사업, MAIN 사업 등 타 국책과제를 통하여 기 확보된 기술과 관련 산업체의 보유 기술을 최대한 활용하였으며, 연구개발 수행은 연구기관, 반도체 및 시스템업체, 통신사업자간 공동 분담 연구개발로 기술개발 역량 결집할수 있도록 하였다. 핵심 기술의 자체 개발을 통한 시스템경쟁력 확보를 위하여 ATM\_PON 주요 핵심 기술(ATM-PON MAC, ATM 스위치,VDSL 모뎀칩 등)의 자체 개발을 추진하였다. 또한 사업추진 관련 업무협의회를 최대한 가동하고 연구원은 연구시제품 개발 시 최대한 공동연구 산업체의 상용화 요구조건을 수용하여 연구시제품의 상용제품화를 손쉽게 추진하도록 하였다.

본 연구 개발이 진행되는 동안 국내 통신장비 제조업의 시장 상황이 극도로 악화되어서 공동연구 참여 업체의 원할한 연구 참여에는 많은 어려움이 있었다. 당초 4개 업체가 본 연구에 참여하였으나, 1개 업체가 시장 악화로 최종연도에 참여하지 못하였다. 그러나 최종연도에 KT가 본 사업에 공동연구업체로 참여하였고 나머지 3개 업체가 계속 공동연구를 추진하여 성공적으로 연구 목표를 달성할 수 있었다.

본 연구를 통하여 광 가입자망 기술의 세계적 추세의 지속적 파악을 통해 경쟁력 있는 핵심 기술을 개발하고, 가입자망 진화전략에 따른 소요 시스템 규격 및 기반기술을 개발하여 중. 장기적인 관점에서 경쟁력이 확보되도록 하였다. 개발제품의 국제 경쟁력 확보를 위하여 본 시스템의 핵심 기술인 10G 용량의 ATM/IP 패킷 스위치 칩, ATM-PON MAC master 및 slave 칩, VDSL 모뎀 칩, 소형 ONU 통합기능칩 등을 자체 개발하여 상용모델에 조기 적용될 수 있도록 하였다.

본 연구에서 ETRI는 주관연구기관으로서 전체 기술개발을 총괄하고 시스템기술과 핵심기술 개발을 주도하였으며, 참여 기업체는 시스템 개발 구현 및 상용화 추진을 담당하였으며, 통신사업자는 사용자 요구사항, 시스템 기술 규격 작성, 광 가입자망 시범 서비스 제안 등의역할을 담당하였다. 그리고 연구수행을 효율적으로 추진하기 위하여 각 기관별 사업 책임자들로 구성된 총괄실무협의회를 운영하였으며, 각 과제 실무책임자 및 담당자들로 구성된 H/W 실무협의회 및 S/W 실무협의회를 두고 필요시 협의회를 개최하여 원활한 연구개발이수행되도록 하였다.

#### 2. 보고서 체계

본 보고서는 '1998.12.~ 2001.12.'기간에 수행된 "저가형 광가입자 장비 기술개발" 사업의 최종 연구개발 내용과 결과를 기술한 것으로서 본 서론에 이어 제2장에서는 ATM-PON 시스템 및 핵심기술에 대해 기술하고, 제3장에서는 최종연도에 수행된 실용모델 제작 및 시험에 대해 기술하고, 제4장에서는 기업체 상용모델에 적용하게 될 핵심 칩셋 개발에 대해 기술한다. 마지막으로 제5장에서는 결론으로서 본 연구개발 결과에 대한 활용과 기대효과에 대해 기술한다.

# 제 2 장 ATM-PON 시스템 개발

# 제 2 장 ATM-PON 시스템 개발

## 제 1 절 시스템 설계

## 1.ATM-PON 고려사항

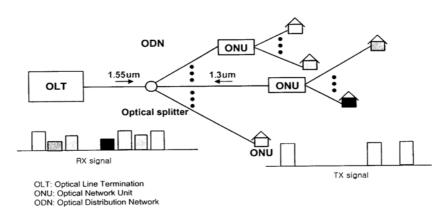

ATM-PON은 망 측에서 가입자 방향으로 「OLT-ODN-ONU」로 구성된다. ODN은 국사에 위치한 OLT 와 가입자 댁내 혹은 가입자 인근에 위치한 ONU 사이에 구성된 광분배 망을 의미한다. 광분배 망은 수동광분기기를 이용하여 OLT의 한 가닥 광섬유를 복수의 ONU와 연결하는 PON을 사용한다. 다수의 ONU가 한 광섬유를 통하여 OLT와 통신채널을 구성하기 위한 다중접속 방식은 하향으로는 TDM(Time Division Multiplex), 상향으로는 TDMA(Time Division Multiple Access) 방식을 사용한다. TDMA 방식은 상향 채널을 다수의 시간영역으로 할당하고, ONU는 지정된 특정 시간영역을 통해 데이터를 보내는 방범을 사용한다. 이때, OLT에서 ONU까지의 광선로 길이는 ONU마다 다르기 때문에 광선로 길이를 측정하여 선로 전달지연 시간만큼 각 ONU가 시간을 보정할 수 있도록 하기 위한 ranging 기능이 필요하다.

PON 의 물리적인 구성은 송수신 신호를 같은 광섬유를 통하여 전달하는 단일광섬유 PON 방식과, 송수신 신호를 각각 별도의 광섬유를 통하여 전달하는 이중광섬유 PON 이 있다, 단일광섬유 PON에서는 서로 다른 파장을 사용하여 송수신을 하기 때문에 광 모듈 출력 단에 파장에 따라 신호를 분리 결합하는 WDM 분기결합기가 추가로 구성되어야 한다. ITU-T G.983.1 에서는 단일광섬유 PON 경우에 하향은 1550nm, 상향은 1310nm를 사용할 것을 권고한다. 최근, WDM을 이용하여 CATV 신호를 방송하는 것을 제안하고 있는 G.983.3에서는 하향 파장을 1550nm에서 1490nm로 이동할 것을 권고하고 있다. 전송 속도는 하향 622Mb/s, 상향155Mb/s 인 비대칭속도와 상하향이 모두 155Mb/s 인 대칭속도를 모두 규정하고 있다.

이러한 ATM-PON 시스템의 설계 방향과 이를 위해 ATM-PON 시스템 설계 시 고려한 내용들은 다음과 같다.

- O 신뢰도가 높은 개방형 광 가입자망 플랫폼으로 개발

- 개방형 SNI(Service Node Interface) 및 ANI(Access Node Interface) 채택으로 멀티벤더 인터페이스(multi-vendor interface)를 제공

- Universal slot 구소의 OLT 설계를 통해 망 및 가입자 측 선로접속의 유연 성을 확보함으로써 망 사업자 및 서비스 제공자의 요구에 경제적이면서 융통성 있게 대처

- 자체 망 복구가 가능한 광분배망 구조를 지원하여 분기율 확장시 루프망 가용도 (99.999%) 만족

- O 망구축의 유연성과 가격 경쟁력 확보를 위한 초저가형 장치 실현

- 장치의 하드웨어 가격이 시스템 가격을 좌우하므로 소요 회로의 대규모 ASIC화 적극 추진, 망 및 장치구조를 단순화 하여 동선 대비 경제적 비교우위 실현

- ATM-PON 관련 장치 비용 가운데 가장 큰 가격점유비중을 갖는 ONU 에 대해서 ONU 자체의 저가화에 최우선을 둠은 물론 운용유지보수 비용이 저렴한 망 구조에 기반을 둔 ONU개발 추구

- O 초기 수요를 유인할 수 있도록 도시 지역에 적합한 시스템 설계

- 국내의 가입자선로 광케이블화 우선 지역인 가입자 밀집지역에 설치, 운용 및 유지보수가 용이하고 저비용을 실현할 수 있도록 고려

- POTS, E1 전용회선, Nx64Kbps, USB, 25Mbps ATM, 10/100Mbps, VDSL등 가입자 요구에 따라 구성이 가능한 ONU 구조 반영

- 가입자 분포/구조에 따른 ONU적용상의 융통성을 실현하기 위해서 다양한 용량 및 역할을 갖도록 ONU 다양화 추진 (SOHO용, 전주설치형, 벽면설치 형, 빌딩설치용 등)

- O 풀서비스(POTS, VOD, 고속 인터넷) 제공에 기반을 둔 시스템 설계

- POTS 서비스의 ATM 액세스 및 전송로 제공

- 고속/초고속 인터네트 제공자(ISP)와 사용자간의 병목 없는 가입자망 제공

- O 다양한 적용 형태의 ONU 설계

- 신규 주거지역에 적합한 댁내 설치형 ONU

- 일반주거용의 전주 설치 형 ONU

- 중소사업자용의 사무실내/건물내 설치 ONU

## 2. 시스템 기능 및 구조

#### 가. 시스템 기능

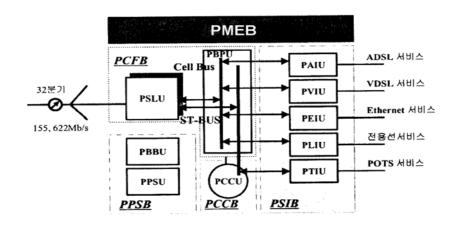

ATM-PON 시스템은 주거용 및 소규모 가입자에게 음성전화(이하 POTS : Plain Old Telephone Service), xDSL 서비스, 고속 인터넷(High-speed Internet), 전용선 서비스 (T1/El) 등, 다양한 서비스를 ATM 기반의 PON을 통하여 제공하기 위해 OLT, ODN, ONU 등으로 구성되는 광가입자 전송시스템으로 다음과 같은 기능으로 이루어진다.

- 서비스노드정합 기능 (광 대역/협대역)

- ATM 다중/분배 기능

- ATM 신호처리 기능

- PON Master/Slave 기능

- PON/ODN 정합기능

- ODN 기능

- 가입자 정합 기능 (VDSL/전용선/POTS)

- 클럭 동기 기능

- OLT/ONU 운용관리 기능

- 데스크탑 ONU 기능

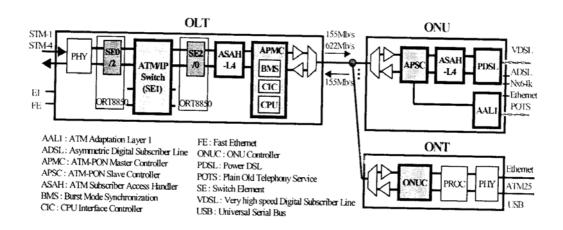

(그림 2-1) ATM-PON 시스템의 기능구성도

## 나. 제공 서비스

전용

VDSL

영상

ATM-PON 시스템에서 제공되는 서비스와 이를 수용하기 위해서 각 ONU, ONT, 및 OLT 에서 필요한 접속 기능은 <표 2-1>과 같다.

| 수용 서비스 |           | ONU                                | ONT                     | OLT                     |

|--------|-----------|------------------------------------|-------------------------|-------------------------|

| 음성     |           | AAL1                               | AAL1                    | V52 (AALI)<br>DS3/STM-1 |

| 전·     | 용선        | T1/E1/n x 64k:<br>SHDSL(AAL1)      | T1/E1/n x 64k<br>(AAL1) | T1/E1                   |

| 데이터    | 인터넷<br>접속 | ADSL, VDSL,<br>SHDSL,<br>10/100B-T | 10/100B-TM25            | STM-1/STM-4             |

|        | 인터넷       | SHDSL                              |                         | STM-1/STM-4             |

ATM25

STM-1/STM-4

<표 2-1> 제공 서비스

## 다. 시스템 구조

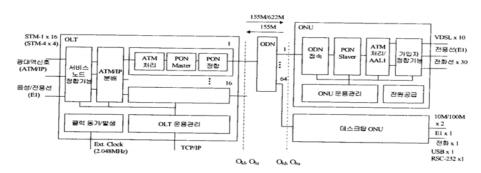

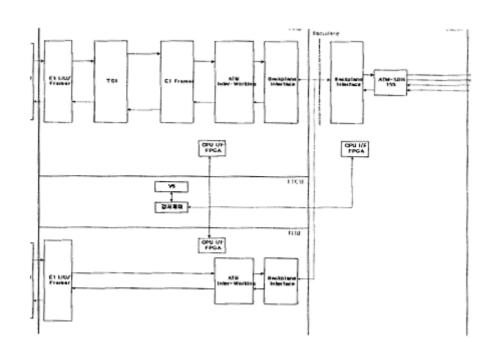

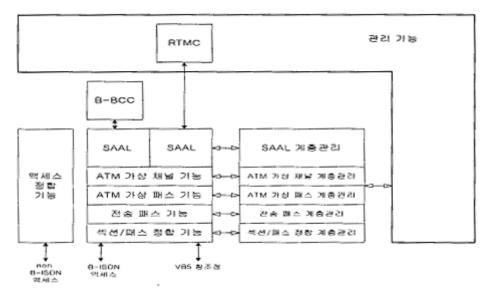

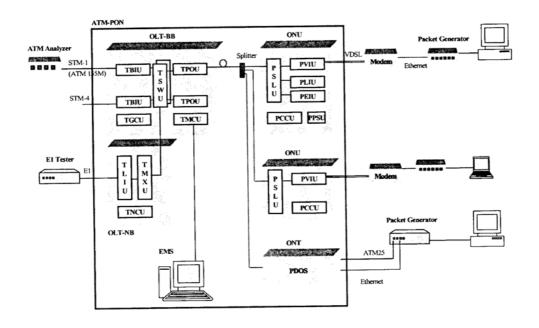

ATM-PON 시스템은 ATM-PON 기반의 가입자망 구조를 가지며 고속 인터넷접속, POTS, 및 고속 멀티서비스 접속 능력을 지원하는 ATM-PON OLT 서브시스템(ATM-PON OLT Subsystem: 이하 POLS이라 칭함), 가입자측 광선로 종단기능을 수행하는 ATM-PON Desktop ONU 서브시스템(ATM-PON Desktop ONU Subsystem:이하 PDOS이라 칭함), ATM-PON Pole ONU 서브시스템(ATM-PON Pole ONU Subsystem: 이하 PPOS이라 칭함), OLT와 ONU 사이의 분배망 역할을 수행하는 ATM-PON ODN서브시스템(ATM-PON ODN Subsystem: 이하 PODS이라 칭함) 등의 구성요소를 포함한다.

(그림 2-2) ATM-PON 시스템 구조

# 3. 시스템 제원

ATM-PON 시스템의 주요 제원을 보면 다음 <표 2-2>와 같다.

<표 2-2> ATM-PON 시스템의 주요 제원

| 항목            | 구분                           | 제원                                                                                                                               |  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 시스템 용량        | 최대 접속 용량                     | 28 PON/OLT<br>32 ONU/PON -> 896 ONU/OLT                                                                                          |  |

| 시스템 중앙        | 스위칭 용량                       | 20Gb/s (622Mb/s 16 x 16)                                                                                                         |  |

|               | ATM 접속 용량                    | PVC: 65,000 connection                                                                                                           |  |

| OLT 인터페이<br>스 | PON 정합<br>(ITU-T<br>G.983.1) | 대칭 : 상향 및 하향 155Mbps<br>비대칭 : 하향 622Mbps/상향<br>155Mbps<br>0~20km 전송거리<br>32 ONUs/PON (64 까지 확장<br>가능)<br>ITU-T G.983.4 DBA 규격 만족 |  |

|               | 망/서비스 정합                     | Broadband : ATM/SDH(STM-1,<br>STM-4),<br>Ethernet Bridge (FE, GE*)<br>Narrowband : V5.2, TDM<br>전용선(T1/El, STM-1)                |  |

| ONU 인터페이      | FTTC (ONU)                   | VDSL, ADSL*,SHDSL*,<br>10/100Base-T, E1 CES, POTS                                                                                |  |

| 스             | FTTB/H (ONT)                 | ATM25M,10/100Base-T,<br>El CES, POTS* USB*                                                                                       |  |

| 트래픽 관리        | Qos                          | CBR, rt-VBR, nrt-VBR, UBR                                                                                                        |  |

| (ITU-T I.371) | UPC                          | PCR, SCR, MBS                                                                                                                    |  |

| OAM 기능        | 감시제어 (1.610)<br>운영관리         | 경보, 장애, 시험, 성능 관리<br>EMS를 통한 웹 기반 운영관리                                                                                           |  |

| 보호 절체         | 유니트 이중화                      | ATM 스위치, 시스템클럭, OLT<br>메인 프로세서                                                                                                   |  |

| 기수 기표 기 기수    | PON 선로 절체                    | full duplex 방식                                                                                                                   |  |

<sup>\*</sup>상용제품에 적용

## 제2절 핵심기술 개발

#### 1. 버스트모드. 광트랜시버

#### 가. 개요

ATM-PON 가입자망은 (그림 2-3)과 같이, 망 측의 1개의 광섬유가 수동 광분기기를 통하여 최대 32 개의 광섬유로 분기되고, 분기된 각 광섬유 끝에는 각각 한 개의 ONU가 설치되는 구조를 갖는다. 따라서, 물리적으로 망 측의 가입자 정합부와 ONU는 1:N 의 연결 구조를 갖고, 다수의 ONU는 시분할다중접속(TDMA: Time Division Multiple Access)방식으로 망측의 가입자 정합부와 논리적인 1:1 연결 구조를 구성한다. 여기에서 망측에서 가입자측으로는 즉, 하향으로는 155Mb/s, 혹은622Mb/s 전송 속도를 갖는 연속적인 비트열 신호를 전송하고, 그 반대 방향인 상향으로는 각 ONU가 자신에게 할당된 시간 구역내에서 신호를 전송하고 그 외의시간에는 신호를 송신하지 않는 버스트 모드 신호를 155Mb/s 속도로 전송한다. 연속 비트열 신호는 대용량 광전송 장치의 개발에 따라 현재 10Gb/s까지는 상용화되어 있고, 40Gb/s 광 송수신 기술이 개발되고 있는 상황이다. 따라서, 광 가입자망에 적용되는 622Mb/s의 광송수신기는 일반화 되어 있다. 그러나, 상향 전송 채널에 적용되는 155Mb/s의 버스트 모드 광 송수신기는 ATM-PON 가입자망에 상용 적용될 수준으로 개발되어 있지 않다.

(그림 2-3) ATM-PON 시스템

본 과제에서는 OCP, NEL, HITACHI, 및 AGERE사에서 개발 단계에 있는 버스트 모드용 광 송수신기를 입수하여 테스트해 보았으며 이 결과들을 각 개발사에 전달하여 후속 개발에 반영하도록 유도하였다. 또한, ETRI에서도 독자적인 버스트모드용 광송수신기를 개발하여 테스트 중에 있다. 이러한 작업들은 궁극적으로 버스트 모드용 광송수신기가 적기에 낮은 가격으로 본 사업에 적용될 수 있도록 하고자 하는 노력이었다. 현재 개발된 시스템에는 HITACHI사의 ATM-PON 광트랜시버를 적용하였다.

### 나. 버스트 모드 광 송수신기의 해결 과제

- 1) 버스트 모드 광송신기

- \* 출력광 파워 제어 : 버스트 모드는 전송할 신호가 없는 구간이 많으므로 최고치 검출에 의한 제어와 같은 방법으로 광 출력을 제어하여야 한다.

- \* <u>Turn-on 지연 보상</u>: 레이저가 꺼진 상태에서 켜질 때에는 빛이 나오기까지 어느 정도의 시간 지연이 발생되며 이것은 신호 펄스폭의 왜곡을 초래하게 된다. 그러므로, first bit predistortion 방법이 필요하며, 셀 전송 영역에서는 turn-on 지연이 없도록 레이저의 바이 어스 전류를 임계치 이상으로 조정하는 기능이 필요하다.

- \*레이저 OFF기능 : 레이저가 완전히 꺼지지 않은 상태에서는 신호가 없더라도 어느 정도의 빛이 나오게 된다. 이것은 다른 ONU 신호들에게 잡음신호로 작용하므로 신호가 없을 때에는 레이저를 완전히 꺼야한다.

- 2) 버스트 모드 광수신기

- \* <u>각기 다른 파워의 신호 검출</u> :광가입자망의 구조상 서로 다른 거리의 ONU들로부터 수신 된 신호들은 각기 다른 파워를 가지게 된다. 그러므로, 같은 파워 레벨로 신호들을 증폭하 여 맞추거나 신호의 decision level을 각기 다르게 조정하거나 해야 한다

- \* 신호위상 검출: 서로 다른 전송 거리를 갖는 신호들은 도착시 위상이 서로 다르다. 따라서, 각 신호를 기준 시스템 클럭에 동기 시키는 과정이 필요하다,

- \* <u>거리 계산</u>: 서로 다른 거리의 ONU들로부터 전송된 신호들 간에 충돌을 방지하기 위해서 미리 거리를 계산하여 수신 시에 충돌이 없도록 각 ONU는 주어진 지연 시간 후에 신호를 보내도록 미리 약속하는 과정이 필요하다.

## 다. 결과 요약

ITU-T G.983의 주요 요구사항을 기준으로 시험결과를 정리하면 다음과 같다.

<표 2-3> 버스트 송수신 시험 결과 요약

|    |                   |        | OCP       | NEL   | НІТАСНІ | AGERE |

|----|-------------------|--------|-----------|-------|---------|-------|

| 송신 | 전송 속도             |        | 155Mb/s   |       |         |       |

|    | 파장                |        | ~ 1310 nm |       |         |       |

|    | 출력 파워 (dBm)       |        |           | + 1   | + 0.5   | _     |

|    | 소광비 (dB)          |        |           | >10   | >10     | _     |

|    | 레이저 OFF 기능        |        |           | 0     | 0       | _     |

| 수신 | BER               |        | >10       |       |         |       |

|    | Sensitivity (dBm) | 연속 신호  | -31       | -33   | -34     | -29   |

|    |                   | 버스트 신호 |           | -21   | -34     | -28   |

|    |                   | 송수신 동시 |           | -13   | -34     | -28   |

|    | Overload (dBm)    |        | -6        |       | -6      | -7    |

|    | 허용되는 연속적인 동일 비트 수 |        | >72       | CDR없음 | CDR없음   | >72   |

|    | Reset 신호          |        | 불필요       | 필요    | 필요      |       |

- \* OCP : 버스트 모드 광수신기와 CDR 칩을 입수하여 테스트 결과, 연속 신호에서만 dynamic range가 측정되었고, 버스트 모드에서는 동작 안됨. CDR 칩은 클릭 복구는 잘 되었으나 신호가 없는 부분에 큰 펄스가 나옴. Scramble 신호의 경우에는 큰 문제가 없음.

- \* NEL : ONU, OLT ATM-PON 트랜시버를 입수하여 테스트 결과, 버스트 신호 송신기는 적합하나, 버스트 신호 수신에 대해서는 적용 불가능.

- \* HITACHI: ONU, OLT ATM-PON 트랜시버를 입수하여 테스트 결과, 광 송신기의 파워가 조금 약하나 대체적으로 버스트 모드 광송수신기로 적합.

- \* AGERE :버스트 모드 광수신 모듈을 입수하여 테스트 결과, 성능이 좀 떨어지므로 추후 개발이 필요. 아직 트랜시버로 개발되지 않고 수신부로만 개발되어있으므로 Single-fiber ATM-PON 시스템에는 적용이 힘듬.

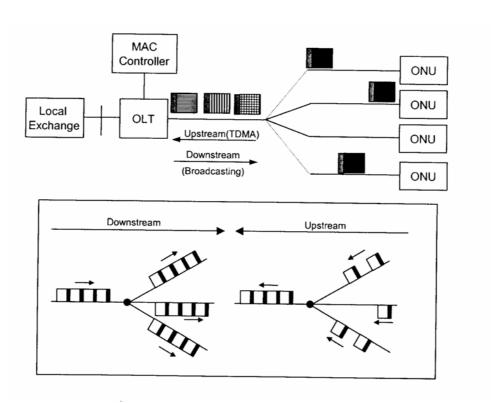

#### 2. PON MAC/DBA

## 가. MAC/DBA 의 필요성

ATM-PON에서 하향은 TDM, 상향은 TDMA 방식으로 OLT와 다수의 ONU 간의 통신 채널이 구성된다. 하향으로는 OLT 의 신호가 모든 ONU 에 방송되기 때문에 ONU는 단순히모든 데이터를 수신하고 자기에 해당하는 셀일 경우 받아들인다. 반면 가입자로부터 망측으로 데이터를 보내는 상향 채널은 다수의 ONU 가 데이터를 보내기 때문에 OLT 측에서 데이터의 충돌이 발생하지 않도록 ONU의 셀 전송을 중재한다. 하향의 경우는 ATM 셀을 그대로 전송하지만 상향의 경우에는 PON 오버헤드 정보를 ATM 셀 앞에 덧붙여서 보낸다. 오버헤드는 패킷 단위로 위상 재정렬이 이루어질 수 있도록 guard bits, preamble bits, cell start delimiter 등의 신호로 구성된다.

하향 채널은 OLT가 보내는 모든 데이터를 ONU 가 수신할 수 있기 때문에 보안의 문제가 발생할 수 있다. 따라서, 각 ATM cell을 목적지 ONU 만이 해석할 수 있도록 암호화 해서 보낸다. 암호 키는 ONU에 의해서 초 단위로 변경된다.

(그림 2-4) TDMA 기반의 상/하향 데이터 전송

상향 채널에 사용되는 TDMA는 ONU의 요구에 의해서 OLT가 time slot을 할당하고, ONU는 할당된 time slot을 통해서 ATM cell을 전송하는 방법이다. time slot을 할당하는 방법은 고정적으로 할당하는 방법과 동적으로 할당하는 방법이 있다. 고정 time slot 할당은 ONU가 항상 일정한 속도의 데이터를 상향으로 보내는 경우 사용한다. 해당 ONU가 할당된 time slot에 유효데이터를 보내지 않는 경우에도 지정된 time slot을 다른 ONU가 사용할수 없기 때문에 PON 링크 전체적으로 볼 때 대역폭 사용 효율이 떨어지는 문제가 있다. 동적 대역폭 할당 방식(DBA: Dynamic Bandwidth Allocation)은 PON 링크 대역폭을 효율적으로 활용하기 위한 방안이다. 상기한 고정적으로 할당 되고 남은 time slot은 ONU의 요구에 따라 매 프레임 단위로 time slot 할당을 다르게 할수 있다. ONU의 할당 요구가사용가능한 time slot 보다 많을 경우에는 ONU에서 보내려고 하는 데이터의 우선순위, ONU 버퍼의 상태를 고려하여 time slot을 할당 한다. 따라서, 동적 대역폭 할당 알고리즘은 제공하는 채널의 성능에 영향을 최소화하며, PON링크에서 제공하는 대역폭을 효율적으로 활용할수 있도록 구현되어야 한다.

## 나. ATM-PON 시스템에서 OLT 와 ONU 의 DBA 기능 블록 구성

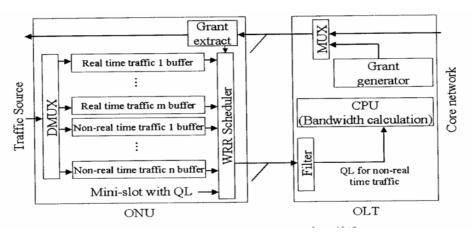

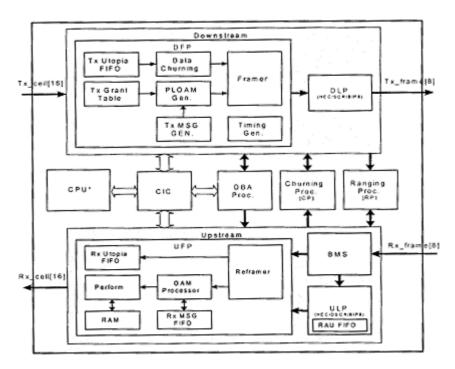

(그림 2-5) OLT 와 ONU 의 DBA 기능 블록

DBA 를 지원하는 OLT 와 ONU 의 기능 블록은 그림2와 같다. 각 ONU 는 여러 개의 QoS sub-queue 를 갖는다. ONU 는 비실시간 연결로부터 발생된 셀을 수용하는 버퍼의 대기열의 길이를 감시하여, 그 대기열의 길이의 합을 mini-slot 을 통하여 OLT 로 전달한다.

OLT 는 ONU 에 설정된 연결들의 ATC/QoS 와 mini-slot 을 통해 전달 받은 비실시간 셀의 수를 참조하여, 각 ONU 에 할당할 대역을 계산하고, 계산된 대역에 해당하는 만큼의 데이터 grant 를 해당 ONU 에 할당한다. 데이터 grant를 수신한 ONU 는 WRR (Weighted Round Robin) 스케줄러를 통하여 하나의 QoS sub-queue 를 선택하고 그 sub-queue 에 있는 하나의 셀을 해당 슬롯에 OLT로 전송한다.

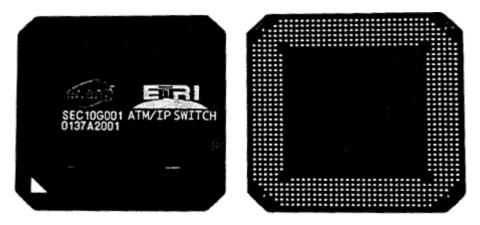

#### 3. 20Gb/s ATM/IP 고속 스위치

20Gb/s급 ATM 분배 스위칭 기능을 ATM/IP 패킷 스위치 칩을 이용하여 one board 로 구현하였다. ATM/IP 패킷 스위치 칩은 10Gb/s (622Mb/s x 16) 처리용량의 ATM/IP 패킷 스위치 ASIC 칩으로 싱글스위치 칩당 10Gbps 스위치 용량 (16x16622Mbps)을 가지며, 채널 그룹 평(멀티채널 스위 칭)에 의해 622Mb/s 및 2.5Gb/s 라인속도 지원이 가능하며 8 등급의 QoS 버퍼 링 및 스케쥴링 기술과 512 ATM 셀 공유메모리를 갖고 있다. 상세한 구현 내용은 제3장의 TSWU-E 유니트와 제4장의ATM/IP 패킷 스위치 부분에서 기술한다.

#### 4. 고속신호 백 플레인 전송

OLT의 백 플레인 (OLT Back Plane Unit, 이하 TBPU)에는 총 21장의 유닛이 실장 될 수 있는데, 이 중에서 광대역 서비스 및 PON 정합을 위해 스위치보드 2장과라인카드 8장이 실장 된다. 스위치보드는 622Mb/s 32 포트를 갖는 20Gb/s 용량이고, 보호 절체를 위해 Active, Stand-by로 구성된다.

본 시스템에서는 622Mb/s 32포트를 갖는 20Gb/s 용량의 스위치보드와 라인 카드들 간의 데이터 전송을 위해 1Gb/s 직렬 전송라인을 사용한다. 직렬 전송 라인은 라인카드와 스위치 유니트간에 점대점 연결을 구성하며 working, protection을 포함해서 모두 64개의 직렬 전송선이 백플레인 상에 구성되어 있다. LVDS 신호를 사용하여 안정적인 직렬 전송라인을 구성하였고, 구현된 직렬 전송선을 SCFL 신호를 발생하는 BERT로 측정한 결과 4Gb/s 까지 무 에러 전송이 가능하였다. 고신뢰 직렬전송선을 사용함으로써 백플레인 상에서 전송신뢰성을 높일 수 있었고, 그 결과 저가격으로 대용량, 고신뢰, 소형의 시스템을 성공적으로 구현할 수 있었다.

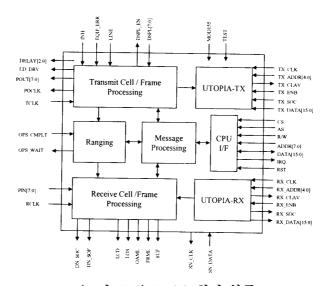

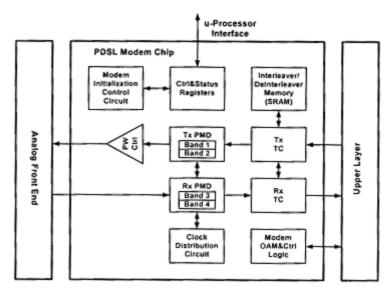

#### 5. QAM-VDSL 모뎀 기술

QAM-VDSL 모뎀 기술은 QAM(Quadrature Amplitude Modulation) 변복조 방식을 사용하는 VDSL(Very high-rate Digital Subscriber Line) 모뎀 칩, 모뎀 테스트 보드 및 구동 프로그램으로 구성된다. VDSL 모뎀은 ONU(Optical Network Unit)와 댁내 단말기에 각각위치하여, 기손 포설된 저급 전화선을 전송 매체로 하여, FDD(Frequency Division Duplexing) 방식으로 최대 비대칭 하향 26Mbps/상향 13Mbps, 대칭 13Mbps의 고속 데이터를 전송한다. 본 과제에서 개발하는 QAM-VDSL 모뎀 칩은 특히 ITU-T, ANSI TIEl.4, ETSITM6등의 국제 표준 규격을 만족하도록 설계 되었으며, 상향 및 하향 전송에 각각 2개씩 전송 대역을 할당하는 4-band 방식을 최초로 적용하여 고속 대칭 데이터 서비스가 원활하게 이루어지도록 하였다. 주요 기능을 요약하면 다음과 같다.

- · ITU-T, ANSI TIEI.4 및 ETSI TM6 표준 규격 만족

- · ONU 및 댁내 단말기에 모두 적용 가능

- · 최대 비대칭 하향 26Mbps/상향 13Mbps, 대칭 13Mbps의 고속 데이터 전송

- 전송 거리에 따른 데이터 속도 조절 기능

- · On-chip 클럭 복원회로

- 상향 및 하향 데이터 전송에 각각 2개의 독립적인 전송 밴드 채용

- · UTOPIA leve1-2 및 E1 데이터 인터페이스 지원

- · ATM 셀 처리 기능(HEC 생성/검증, 셀 혼화/역 혼화, 셀 경계 식별)

- · Dual Latency 제공(인터리버 선택적 사용 및 depth 조절 기능)

- · 최대 500us의 버스트 노이즈를 처리 가능한 인터리버 내장

- · Forward Error Correction (RS code, t=8) 내장

- · OAM 채널을 통한 모뎀 칩 configuration 및 상태정보 교환 기능

- · Link Activation/De-activation 제어회로 내장

- 외부 프로세서를 이용한 모뎀 제어 및 상태 모니터링 기능

- 각 전송 밴드별로 독립적인 초기 설정 및 제어 가능

- 67.5kbauds 단위로 심볼율 가변 기능

- · 135kbps 단위로 데이터 전송 율 가변 기능

- · 1Hz 단위로 중심주파수 가변 기능

- · Scalable QAM 인코딩/디코딩(4,16,32,64,128,256-QAM)

- 블라인드 등화 방식의 결정 궤환 등화기(DFE) 채용

- · 상향전송 출력의 PBO(Power Back-Off 기능

- 자동 이득 제어장치 내장

- · JTAG 내장

# 제 3 장 실용모델 제작 및 시험

# 제 3 장 실용모델 제작 및 시험

## 제 1 절 OLT

실장 될 수 있다

#### 1. 개요

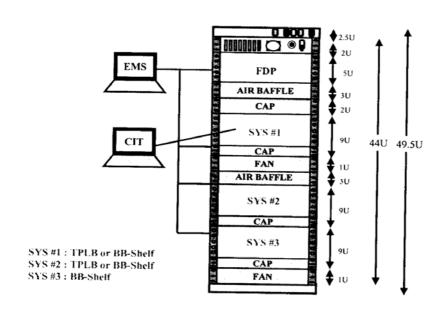

ATM-PON 하드웨어 중 OLT (POLS; ATM-PON OLT Subsystem)는 광대역 서비스용/공통 셀프와 협 대역 서비스용 셀프로 구분하며, 광 대역 서비스용/공통 셀프에서는 ATM Switch 유니트가 실장되고 서비스 정합 유니트와 PON 정합 유니트가 최대 용량 범위 내에서 슬롯 구분없이 자유롭게 실장 가능하다. 하나의 POLS 랙은 3개의 셀프로 구성된다. 스위치 유니트와 서비스정합 및 PON정합 유니트는 1Gb/s 직렬신호로 백플레인을 통해 연결된다. 스위치 용량은 최대 20Gbps로 622Mbps단위로 스위칭 된다. 한편, 협대역 서비스 정합 블록(TPLB)은 동일한 광 대역 서비스/공통 셀프 또는 별도의 협대역 서비스용 셀프에

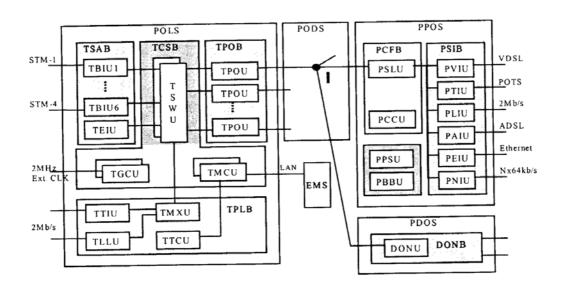

ATM-PON 하드웨어의 형상 및 구성을 보면 POLS 의 경우 (그림 3-1)과 같이 23인치 랙에 3개의 시스템 셀프를 실장하며, 광 대역 서비스/공통 셀프(BB-Shelf는(그림 3-2)와 같이 유니트를 구성하고, 협대역용 셀프(TPLB)는 (그림 3-3)과 같이 구성한다.

(그림 3-1) ATM-PON OLT (POLS) 랙 구성도

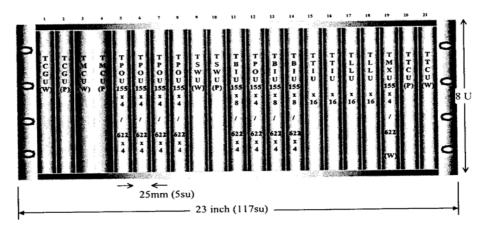

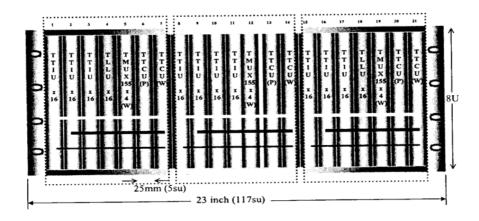

(그림 3-2) ATM-PON OLT (POLS) BB-Shelf의 유니트 실장도

(그림 3-3) ATM-PON OLT (POLS) TPLB의 유니트 실장도

## 2. 광대역 셀프

#### 가.TBIU

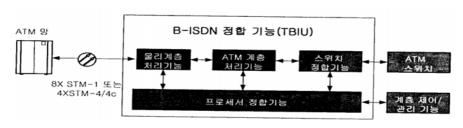

TBIU는 ATM-PON 기반의 저가형 광 가입자 시스템의 서브시스템인 POLS의 서비스노드 정합 블럭 TSAB(OLT SNI Adaptation Block)에서 B-ISDN 서비스 정합 기능을 담당한 유니트이며, 망 측으로는 ATM 교환기와 접속하고, 가입자 측으로는ATM 스위치에 접속된 다. 따라서, 하향으로 수신된 데이터는 ATM 스위치에서 수용 가능한 형태로 변환되고, 상향으로 수신된 데이터는 SDH 프레임구조에 맞게 변환되어 전송된다. TBIU는 SDH 계위 STM-1급 단일모드 광 선로 8포트를 지원하여 1.25Gbps의 처리용량을 가지는 TBIUI과 STM-4/4c급 단일모드 광 선로 4포트를 지원하여 2.5Gbps의 처리용량을 가지는 TBIU6의 두 가지 모델이 있으며, (그림 3-4)는B-ISDN정합 기능 구조를 나다낸 것이다.

- 1) 주요 기능

- 가) 622Mb/s STM-4/4c 4포트 광 송수신 기능(TBIU6)

- 나) 155Mb/s STM-1 8포트 광 송수신 기능(TBIUI)

- 다) SDH 계위 물리 계층 처리 기능: Fl, F2 및 F3 1eve1의 OAM 채널 처리 기능

- 라) ATM 계층처리 기능: VP, VC 변환, F4/F5 OAM 채널 처리 기능

- 마) ATM Traffic Management : CBR, rt-VBR, nrt-VBR, ABR, UBR 등 class 별 트래픽 관리 및 UPC 기능

- 바) TSWU-ASX 또는 TSWU-SIAN 과의 스위치 인터페이스 기능

- 사) 850Mbps의 serial backplane 2포트(TBIU1) 및 4포트(TBIU6) 접속 기능

- 아) MPC 750 모듈을 채용한 TMCU 프로세서 보드와의 인터페이스 기능

(그림 3-4) TBIU 유니트 구성도

## 나. TPOU

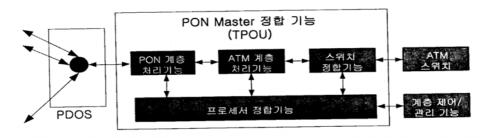

TPOU는 ATM-PON 기반의 저가형 광 가입자 시스템의 하부 시스템인 POLS의서비스노드 정합 블럭 TPOB(OLT PON Master Block)에서 ATM-PON 링크 정합 기능을 담당한 유니트이며, 가입자 측으로는 G.983.1을 지원하는 ATM-PON 링그와 접속하고, 망 측으로는 ATM 스위치에 접속된다. 따라서, 상향으로 수신된 데이터는 ATM 스위치에서 수용 가능한 형대로 변환되고, 하향으로 수신된 데이터는 PON 링크 프레임 구조에 맞게 변환되어 전송된다. (그림 3-5)은 TPOU의 기능 구조를 나타낸 것이다.

- 1) 주요 기능

- 가) 622Mb/s continuous-mode 광 송신 및 155Mb/s burst-mode 광 수신 기능(선택)

- 나) 155Mb/s continuous-mode 광 송신 및 155Mb/s burst-mode 광 수신 기능(선택)

- 다) PON MAC Master 기능(G.983.1): APON-20G OLT PON MAC Slave 기능과 연동하여 Ranging, TDMA 상향 채널 접속, 동적 대역폭 할당, 하향 채널 암호키 상호 인증 및 해독 등의 기능을 한다.

- 라) ATM 계층처리 기능: VP, VC 변환, F4/F5 OAM 채널 처리

- 마) ATM Traffic Management : CBR, rt-VBR, nrt-VBR, ABR, UBR 등 class 별 트래픽 관리 및 UPC 기능

- 바) TSWU-ASX 또는 TSWU-SIAN 과의 스위치 인터페이스 기능

- 사) 850Mbps Serial Backplane 2포트 접속 기능

- 아) MPC 750 모듈을 채용한 TMCU 프로세서 보드와의 인터페이스 기능

(그림 3-5) TPOU 유니트 구성도

#### 다. TSWU

#### 1) 개요

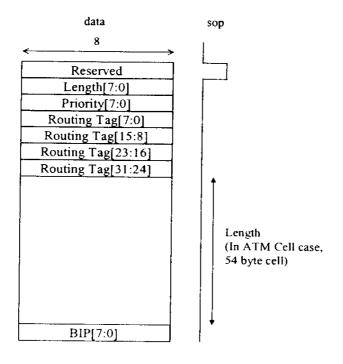

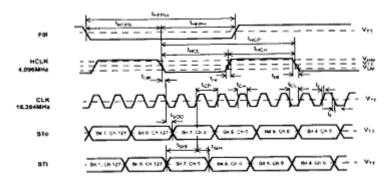

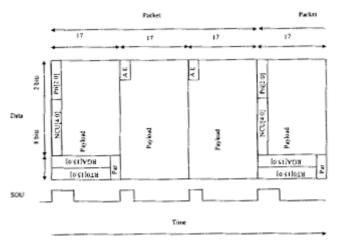

본 스위치보드는 600Mbps의 속도를 갖는 32개의 포트에 대해 스위칭을 처리해 주며 20Gbps의 처리 용량을 가지고, ATM 셀과 함께 IP 등 가변길이 패킷도 동일한 방식으로 처리한다. 스위치보드로 입출력되는 데이터는 850Mbps의 직렬 인터페이스를 사용하여 pseudo-SDH 신호에 전달되며, SPE 구간에서는 (그림 3-6)과 같은 백플레인 포맷을 따른다.

(그림 3-6) 백 플레인 셀 포맷

Length[7:0]은 Routing Tag와 BIP(Parity)사이에 위치하는 패킷의 길이를 나타내며 Routing Tag[31:0]은 0에서 31번 시스템 포트 중에서 해당 패킷이 전달되어야 할 포트를 비트맵으로 나타낸다. Routing Tag에 두 비트 이상 1이 있는 경우 해당 포트로 동시에 패킷이 전달되어야 함을 뜻한다. 또한 Priority는 해당 패킷의 우선순위를 나타내는데 스위치칩 내부에서 스케쥴 링 우선순위로 사용된다.

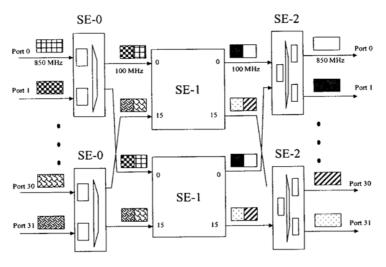

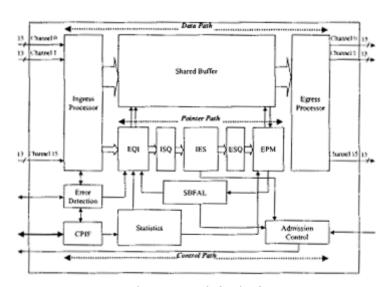

스위칭은 3단계로 처리되는데 첫 번째 단계인 SE-0에서는 각 포트별 입력 데이터의 16비트 변환과 버퍼링, 2개의 포드에 대해 버퍼링 된 데이터의 다중화, 그리고 병렬처리를 위한 상하 바이트로의 분리 및 SE-1 칩에서 사용하는 포맷으로의 변환을 담당한다. 두 번째 단계는 두 개의 SE-1 ASIC에 의해 병렬로 처리되는데, 입력된 유효한 유닛 데이터마다 공유메모리 번지를 할당하여 저장하고, 포인터 정보를 입력큐에 저장했다가 출력포트 및 우선순위에 따라 출력 linked list subqueue에 옮기고, 각 포트에 대해 우선순위에 따라 스케쥴링을 하여 공유메모리에서 패킷을 읽어 출력하는 기능을 담당한다. 세 번째 단계인 SE-2에서는 스위칭되어 두 개의 SE-1 칩으로부터 입력되는 데이터를 병렬로 묶어서 해당하는 라우팅 태그에 따라 해당 출력 FIFO에 16비트 형태로 저장하면서 두 번째 단계를 위해 삽입되었던 오버헤드를 제거하고, 이후에 패킷 데이터를 읽어 백플레인 형식에 맞추어 전송한다. 두 포트를 처리하는 SE-0와 두 포트를 처리하는 SE-2가 모여서 두 포트를 처리하는 회로가 되고, 이러한 회로가 네 개가 하나의 ORT8850 FPSC에 구현되었다. 따라서 하나의 FPGA(FPSC)는 8개의 포트를 담당한다. 각 FPGA 내부에는 또한 FPSC가 내장하고 있는 직렬 백플레인 인터페이스 코어와의 접속을 담당하는 adapt8850회로를 가지고 있다.

두개의 SE-1 칩을 병렬로 사용하여 622Mbps의 포트 32개에 대해서 스위칭을 하는 방법을 나타내면 (그림 3-7)과 같다.

(그림 3-7) 두 개의 SE-1 칩을 사용한 20Gbps 스위칭

FPGA는 (그림 3-8)과 같은 구조를 가지는데 TSWU-E 보드에는 네 개의 FPGA와 두개의 스위치 ASIC을 가지고 있다.

(그림 3-8) SEO/SE2 FPGA 구조

#### 라. TCGU

TCGU(OLT Clock Generation Unit)는 망으로부터 공급되거나 추출할 수 있는 타이밍 정보를 이용하여 동기식스위칭 시스템에 필요한 클럭을 생성하여 각 해당 유닛에 공급하는 기능을 수행한다. 본 유닛은 POLS(ATM-PON OLT Subsystem)에서 필요로 하는 시스템 클럭의 생성뿐만 아니라, 유도된 DS-IE 클럭 신호를 외부에 공급할 수도 있어야 한다, 이를 위한 기준 클럭의 선택은 자동적으로 수행되거나, TMCU (OLT Master Control Unit)의 제어에 의해 매뉴얼로 선택할 수도 있다. 또한, TCGU의 신뢰성을 향상시키기 위해 이중화기능이 구현되어야 한다.

#### 1) 클럭 생성 기능

본 POLS 시스템은 ATM-교환기, POTS교환기 및 IP Router등에 접속을 지원해주는 Access node로써 POLS의 시스템 클럭을 망에 동기 된 클럭으로 사용해야 한다. POLS 시스템에 사용할 시스템 클럭의 생성을 위해 TCGU는 같은 세 가지 글럭 생성 모드를 지원한다.

- 가) 외부 동기 모드 : 외부 동기 모드는 2.048 MHz의 DOTS 신호를 수신하여 이를 클럭 동기 원으로 삼는 모드이다.

- 나) 수신 종속 동기 모드 : 수신 종속 동기는 교환기 또는 망의 동기 계층에 종속 동기 되어 운용되는 모드로 수신된 채널로부터 복원된 클럭에 POLS시스템을 동기 시기는 모드이다

- 다) 국부 동기 모드 : 수신종속 또는 외부 동기원의 단절 시에도 POLS 시스템은 독립된 국부 동기 클럭 원에 의한 비 동기 운용이 가능해야 하며, 이를 국부 동기 모드라 한다.

- 2) 기준 클럭의 절제 기능

모든 기준 클럭은 자체 장애 상태를 검출할 수 있어야 하며 장애 상태 검출 시 절제되어 기준 클럭으로 선택되지 않아야 한다. 기준 클럭의 장애 검출은 TBIU에서 재생 분주된 8KHz 선로 클럭과 함께 L,OS 검출회로에 의한 신호로서 판단한다.

3) 유도 클럭 생성 기능

다중화 장치의 유도 클럭은 수신 STM-1 선로 신호에 동기 된 2개의 DS-IE신호 형태로 생성되어야 한다.

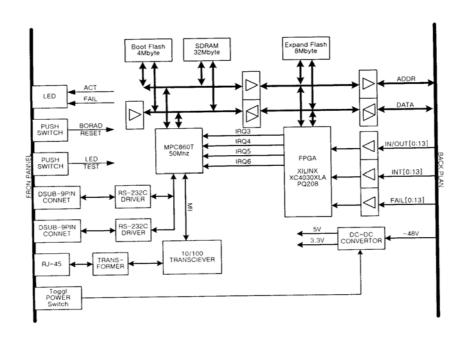

## 마. TMCU

TMCU (OLT Master Control Processor Unit) 유닛은 ATM-PON 시스템의 OLT 서브시스템(POLS)의 제어 프로세서 보드로서, POLS 시스템을 제어 및 관리 기능을 수행한다.

### 1) 기능구현

TMCU 유니트는 서비스 정보 보드, PON 정합 보드, 클럭보드 및 스위치 보드를 제어하며, 감시제어, 운용관리 및 VB5 제어를 담당하는 상위 프로그램들이 실행되는 유니트 이다. 이와 같은 상위 프로그램들이 실행되기 때문에 충분한 성능을 보장해야 하기 때문에 고성능의 PPC750 프로세서를 사용하여 구현되었다. 또한 시스템 백업을 위한 비휘발성 메모리를 포함하고 있다.

## 2) 구성 블록 및 기능

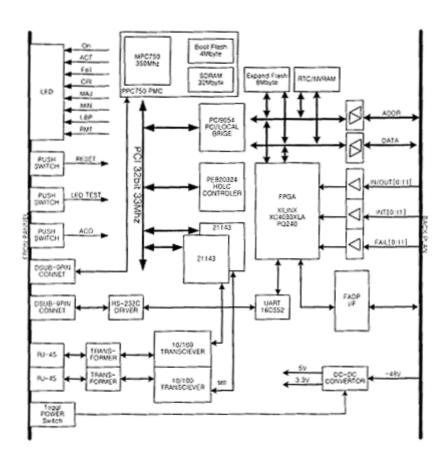

(그림 3-9) TMCU 프로세서 보드 전체의 블록도

TMCU 프로세서 보드는 Power PC 750 CPU를 탑재한 PPMC750 모듈을 사용하여 주변 칩과 로직을 access한다. 프로세서 보드 전체의 블록도는 (그림 3-9)와 같다. PPMC750 프로세서 모듈은 다음과 같은 핵심 모듈을 포함한다.

\* 16Mbyte,32bit 13bit Boot Flash Memory On Module

#### \* 128Mbyte, 64bit SDRAM On Module

TMCU 프로세서 보드는 MPC750 프로세서 모듈, DS12887 RTC, XC4020XLFPGA, DEC21143 Ethernet Controller, NVRAM 들로 구성된다. 통신 및 MMI를 위한 Ethernet por와 Serial port는 2개씩 제공한다. MPC750 프로세서의 동작 주파수는 최대400MHz이고 대략 733MIPS 정도의 처리를 할 수 있다. 그리고 DEC21143 Ethernet Controller는 10/100Base-Tx모두를 지원하며, PCI 브릿지를 통하여access한다. 동작주파수는 66.7MHz가 최대 값이다. Boot ROM은 8Mbyte를 사용하며, 제어 및 운용관리프로그램이 포함되어사용된다. DS12887 RTC는 Real Time Clock을 제공하며, XilinxFPGA를 통해서 값을 읽고 쓴다. CPU는 XC4020XL FPGA는 통해서 RTC, Flash Memory, NVRAM을 access한다. Xilinx FPGA는 address와 chip select 신호를 내보낸다. Chip select 신호를 받은 칩은 Chip Select 신호를 이용해서 값을 읽고 쓴다, 그리고, CPU가 Linecard를 access할 매필요한 제어 신호를 Xilinx FPGA가 처리한다.

TMCU 보드내의 FPGA는 PCI 버스상의 PCI 9054 LOCAL to PCI Brige 칩의 Local BUS를 통해 16bit 데이터 버스로 액세스 되며 내부에 16bit 레지스터 16개를 가지고 있다. FPGA는 백플랜을 통해 연결된 각각의 보드에 대한 실/탈장 정보, 장애 상태정보, 인터럽트 요구 정보와 프로세서 자체의 장애 정보를 모니터 하여 레지스터에 관리하고 각 정보의 상대에 변화가 발생시 프로세서에게 인터럽트를 발생 시키고 프로세서는 이를 정해진 인터럽트 서비스 루틴을 통해 처리해 주어야 한다. FPGA는address와 chip select 신호를 내보내며, Chip select 신호를 받은 칩은 Chip Select 신호를 이용해서 값을 읽고 쓴다, 그리고, 프로세서가 Linecard를 access할 때 필-요-한 제어신호를 Xilinx FPGA가 처리한다.

TMCU 보드는 INTEL DEC21143 Ethernet Controller를 이용해서 Remote Host와 통신을 한다. Flash Memo다는 E28F320 8Mbyte Flash Memory를 2개 사용하여 16Mbyte Flash Memor를 제공한다. 이 메모리는 운용관리 프로그램과 VB5 제어 프로그램이 올라간다. NVRAM은 2Mbyte를 사용하며, TMCU 에서 시스템 형상이나 연결 정보등 중요한정보를 저장하기 위해서 사용하다.

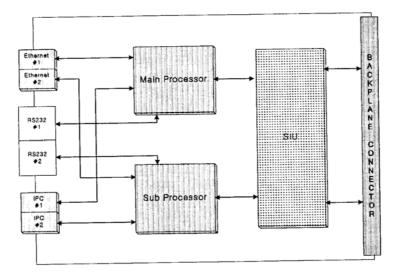

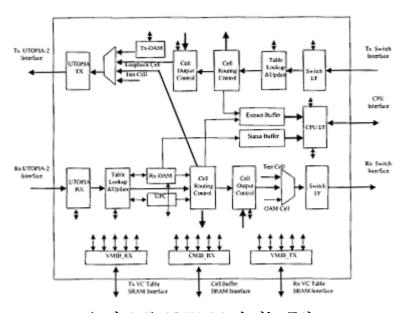

#### 바.TEIU

TEIU는 POLS에서 Ethernet network와 접속을 담당하며, Fast Ethernet 2포트를 지원한다. Ethernet network으로부터 패킷을 수신하여 IPOA 프로토콜 기능을 수행 후 TSWU로 ATM 셀을 송신하며, TSWU 로부터 ATM 셀을 수신하여 IPOA 프로토콜 기능을 수행 후 Ethernet network로 패킷을 송신한다.(그림 3-10)은 TEIU 구성도이다.

(그림 3-10) TEIU 구성도

Main processor 블록은 이더넷 1번 포트로부터 데이터를 수신하여 IPOA 기능을 수행 후 내부 셀 포맷으로 변경하여 UTOPIA I 인터페이스를 통하여 SIU로 데이터를 송신하며,IPC 1번 포트를 통하여 상위 프로세서와 통신하고, 또한 RS232 1번 포트를 통하여 외부 콘솔과 통신한다.

Sub processor 블록은 이더넷 2번 포트로부터 데이터를 수신하여 IPOA 기능을 수행 후 내부 셀 포맷으로 변경하여 UTOPIA I 인터페이스를 통하여 SIU로 데이터를 송신하며, IPC 2번 포트를 통하여 상위 프로세서와 통신하고, 또한 RS232 2번 포트를 통하여 외부 콘솔과 통신한다.

SIU 블록은 Main processor UTOPIA I 인터페이스와 Sub Processor UTOPIA I인터페이스를 통하여 셀의 송수신을 담당하는 FPGA 블록과 백플레인을 통하여 각각의 스위치 포트로 시리얼 데이터를 송수신하는 FPSC 블록으로 나누어진다.

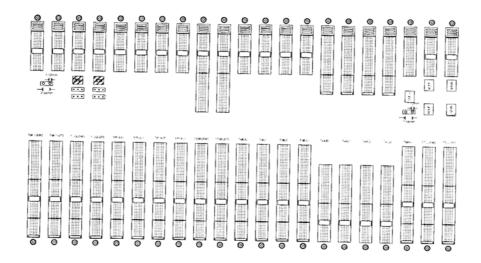

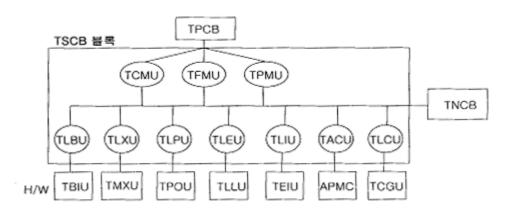

## 사. TBPU

OLT의 백플레인 (OLT BackPlane Unit, 이하 TBPU)은 일반 및 스위치 블록(OIT Common & Switch Block, 이하 TCSB)의 구성 유닛과 협대역 서비스 정합 블록(OLT POTS & Leased Line Block, 이하 TPLB)의 구성 유닛이 실장된다. TBPU는 TCSB의 구성 유닛으로써 TMCU, TCGU, TBIU, TPOU, TSWU, TEIU 등의 TCSB 구성 유닛들과, TPLB의 구성 유닛인 TTCU, TVIU, TMXU, TTIU, TLIU 등이 함께 실장된다.

TBPU에는 층 21장의 유닛이 실장 될 수 있는데, 이 중에서 광 대역 서비스 및 PON 정합을 위해 스위치보드 2장과 라인카드 8장이 실장 되고, 스위치보드는622Mb/s 32 포트를 갖는 20Gb/s 용량이고, 보호 절체를 위해 Active, Stand-by로 구성된다.