# System Management Bus (SMBus) Specification

Version 2.0

August 3, 2000

#### **SBS Implementers Forum**

Copyright © 1994, 1995, 1998, 2000

Duracell, Inc., Energizer Power Systems, Inc., Fujitsu, Ltd., Intel Corporation, Linear Technology Inc., Maxim Integrated Products, Mitsubishi Electric Semiconductor Company, PowerSmart, Inc., Toshiba Battery Co. Ltd., Unitrode Corporation, USAR Systems, Inc. All rights reserved.

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT OR FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

IN NO EVENT WILL ANY SPECIFICATION CO-OWNER BE LIABLE TO ANY OTHER PARTY FOR ANY LOSS OF PROFITS, LOSS OF USE, INCIDENTAL, CONSEQUENTIAL, INDIRECT OR SPECIAL DAMAGES ARISING OUT OF THIS SPECIFICATION, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES. FURTHER, NO WARRANTY OR REPRESENTATION IS MADE OR IMPLIED RELATIVE TO FREEDOM FROM INFRINGEMENT OF ANY THIRD PARTY PATENTS WHEN PRACTICING THE SPECIFICATION.

\* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owner's benefit, without intent to infringe.

| Revision No. | Date     | Notes               |

|--------------|----------|---------------------|

| 1.0          | 2/15/95  | General Release     |

| 1.1          | 12/11/98 | Version 1.1 Release |

| 2.0          | 8/3/00   | Version 2.0 Release |

Questions and comments regarding this specification may be forwarded to: <a href="mailto:questions@sbs-forum.org">questions@sbs-forum.org</a>

For additional information on Smart Battery System Specifications, visit the SBS Implementer's Forum (SBS-IF) at: www.sbs-forum.org

# **Table of Contents**

| 1.   | INTRODUCTION                                                      | 5  |

|------|-------------------------------------------------------------------|----|

| 1.1. | Overview                                                          | 5  |

| 1.2. | Audience                                                          | 5  |

| 1.3. | Scope                                                             | 5  |

| 1.4. | Organization of this document                                     | 5  |

| 1.5. | Supporting documents                                              |    |

| 1.6. | Definitions of terms                                              |    |

| 1.7. | Conventions                                                       |    |

| 2.   | GENERAL CHARACTERISTICS                                           | g  |

| 3.   | LAYER 1 – THE PHYSICAL LAYER                                      | 11 |

| 3.1. | Electrical characteristics of SMBus devices – two discrete worlds |    |

|      | 1.2. Low-power DC specifications                                  |    |

|      | 1.3. High-Power DC specifications                                 |    |

| 3.1  |                                                                   |    |

| 4.   | LAYER 2 – THE DATA LINK LAYER                                     | 18 |

| 4.1. | Bit transfers                                                     | 18 |

|      | 1.1. Data validity                                                |    |

| 4.1  | 1.2. START and STOP conditions                                    |    |

| 4.1  | 1.3. Bus idle condition                                           |    |

| 4.2. | Data transfers on SMBus                                           | 19 |

| 4.3. | Clock generation and arbitration                                  |    |

|      | 3.1. Synchronization                                              |    |

|      | 3.2. Arbitration                                                  |    |

| 4.3  | 3.3. Clock low extending                                          | 22 |

| 4.4. | Data transfer formats                                             | 23 |

| 5.   | LAYER 3 – NETWORK LAYER                                           | 24 |

| 5.1. | Usage model                                                       | 24 |

| 5.2. | Device identification – slave address                             |    |

| 5.2  | 2.1. SMBus address types                                          | 25 |

| 5.3. | Using a device                                                    | 26 |

| 5.4. Pa   | cket error checking                                         | 26 |

|-----------|-------------------------------------------------------------|----|

| 5.4.1.    | Packet error checking implementation                        | 26 |

| 5.5. Bu   | s Protocols                                                 | 27 |

| 5.5.1.    | Quick command                                               |    |

| 5.5.2.    | Send byte                                                   |    |

| 5.5.3.    | Receive byte                                                |    |

| 5.5.4.    | Write byte/word                                             |    |

| 5.5.5.    | Read byte/word                                              |    |

| 5.5.6.    | Process call                                                |    |

| 5.5.7.    | Block write/read                                            | 31 |

| 5.5.8.    | Block write-block read process call                         | 32 |

| 5.5.9     | SMBus host notify protocol                                  |    |

| 5.6. SN   | ABus Address resolution protocol                            | 34 |

| 5.6.1.    | Unique Device Identifier (UDID)                             |    |

| 5.6.2.    | Power-on reset                                              |    |

| 5.6.3.    | ARP commands                                                | 38 |

|           |                                                             |    |

| APPEND    | IX A – OPTIONAL SMBUS SIGNALS                               | 54 |

| SMBSUS    | #                                                           | 54 |

| SMBALE    | CRT#                                                        | 55 |

| APPEND    | IX B – DIFFERENCES BETWEEN SMBUS AND I <sup>2</sup> C       | 57 |

| DC specif | ications for SMBus and I2C                                  | 57 |

| Timing sp | pecification differences between SMBus and I <sup>2</sup> C | 58 |

| Other dif | ferences                                                    | 58 |

| APPEND    | IX C – SMBUS DEVICE ADDRESS ASSIGNMENTS                     | 59 |

#### 1. Introduction

#### 1.1. Overview

The System Management Bus (SMBus) is a two-wire interface through which various system component chips can communicate with each other and with the rest of the system. It is based on the principles of operation of  $I^2C^*$ .

SMBus provides a control bus for system and power management related tasks. A system may use SMBus to pass messages to and from devices instead of tripping individual control lines. Removing the individual control lines reduces pin count. Accepting messages ensures future expandability.

With System Management Bus, a device can provide manufacturer information, tell the system what its model/part number is, save its state for a suspend event, report different types of errors, accept control parameters, and return its status.

#### 1.2. Audience

The target audience for this document includes but is not limited to:

- System designers implementing the System Management Bus Specification in their systems

- VLSI engineers designing chips to connect to the System Management Bus

- Software engineers writing support code for System Management Bus chips

#### 1.3. Scope

This document describes the electrical characteristics, network control conventions and communications protocols used by SMBus devices. These can be thought as existing at the first three layers of the seven-layer OSI network model, that is, the physical, data link and network layers. Functions normally implemented at higher layers of the OSI model are beyond the scope of this document.

The original purpose of the SMBus was to define the communication link between an intelligent battery, a charger for the battery and a microcontroller that communicates with the rest of the system. However, SMBus can also be used to connect a wide variety of devices including power-related devices, system sensors, inventory EEPROMs communications devices and more.

This version of the specification is a superset of previous versions, 1.0 and 1.1. All devices compliant with these previous versions are compliant with this version. Those features new to SMBus with this version of the spec are optional and are appropriate to the new environments enabled by those features. However, if implemented, these new features must be implemented in a manner compliant with this specification.

# 1.4. Organization of this document

This document is organized to first give the reader an overview of the SMBus and then to delve deeper into its actual working. The major technical discussion appears in three sections that treat the various aspects of the SMBus as they would appear in the first three layers of the OSI reference network model, the physical layer the data link layer and the network layer.

The section on the physical layer sets out SMBus electrical characteristics. The section on the data link layer specifies bit transfers, byte data transfers, arbitration and clock signals. The section on the link layer deals with the general usage model, the concept of addresses in SMBus, the Address Resolution Protocol and the bus data transfer protocol. All aspects of the SMBus proper may be described within the scope of the first three OSI layers.

The SMBus is a multiple attachment bus with no routing capability. Most communication occurs between and involves only two nodes, a master and a slave. Exceptions to this rule occur during and apply to devices that implement the Address Resolution Protocol as well as the Alert Response Address.

Appendixes at the end of this document contain additional information and guides to implementation that the reader may find useful.

# 1.5. Supporting documents

This specification assumes that the reader is familiar with or has access to the following documents:

- The I<sup>2</sup>C-bus and how to use it, Philips Semiconductors document #98-8080-575-01.

- *ACPI Specification*, Version 1.0b, Intel Corporation, Microsoft Corporation, Toshiba Corp., February 2, 1999 (http://www.teleport.com/~acpi)

- PCI Local Bus Specification, revision 2.2, December 18, 1998, (http://www.pcisig.com)

- SMBus Control Method Interface Specification, Version 1.0, Smart Battery System Implementers Forum, December 1999

#### 1.6. Definitions of terms

The following terms are defined with respect to this specification and may have other meanings in other contexts. Some of these terms are used throughout the specification while others have meaning only within limited portions. They are defined here so that the reader may be able to find their definitions in one place.

| <b>Address Resolution Protocol</b> | A protocol by which SMBus devices with assignable addresses on the bus are enumerated and assigned non-conflicting slave addresses.                                                                                                                                                                                  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Resolved flag (AR)         | A flag bit or state internal to a device that indicates whether or not the device's slave address has been resolved by the ARP Master.                                                                                                                                                                               |

| Address Valid flag (AV)            | A flag bit or state internal to a device that indicates whether or not the device's slave address is valid. This bit must be non-volatile for devices that support the Persistent Slave Address.                                                                                                                     |

| ARP                                | Address Resolution Protocol                                                                                                                                                                                                                                                                                          |

| SMBus ARP Enumerator               | An SMBus master that uses a subset of the ARP for the purpose of discovering ARP-capable slave devices and their assigned slave addresses.                                                                                                                                                                           |

| ARP Master                         | The SMBus master (hardware, software or a combination) responsible for executing the ARP and assigning addresses to ARP-capable slave devices. The SMBus Host will usually be the ARP Master but under some circumstances another SMBus master may assume the role. There is only one active ARP Master at any time. |

| Assigned Slave Address             | The address assigned to a slave device by the ARP Master. This address is then used for accesses to the device's core function. Legal values are in the range 0010 000 to 1111 110 with some exceptions (associated with reserved addresses and those consumed by Fixed Slave Address devices).                      |

| Bus Master                         | Any device that initiates SMBus transactions and drives the clock.                                                                                                                                                                                                                                                   |

| <b>Bus Slave</b>                   | Target of an SMBus transaction which is driven by some master.                                                                                                                                                                                                                                                       |

| Fixed Slave Address                | A slave address that cannot be changed. Non-ARP-capable SMBus                                                                                                                                                                                                                                                        |

devices fall into this category. The ARP Master must not assign a used

(i.e. device is present on the bus) Fixed Slave Address to an ARP-capable device.

Master-receiver A bus master in an SMBus transaction while it is receiving data from a

bus slave during an SMBus transaction

Master-transmitter A bus master in an SMBus transaction while it is transmitting data onto

the bus during an SMBus transaction.

PEC Packet Error Code

Persistent Slave Address (PSA)

Reserved

An assigned slave address that is retained through loss of device power.

Reserved fields and bits within any of the data structures in this document and in the SMBus ARP data structures in particular are expected to be unused and ignored by software. Reserved bits must written as 0 and read at 0 unless otherwise specified. These bits and fields are reserved for future use and may not be used by OEMs or

IHVs.

**Repeated Start** A repeated START is a START condition on the SMBus used to switch

from write mode to read mode in a combined format protocol (e.g. Byte Read). The repeated START always follows an Acknowledge, and it

always indicates that an address phase is beginning.

**Self-powered device** A self-powered device is a device powered either by a battery or an

external power source, but not by the system of which it is a part and not

in any way by the SMBus.

**Slave-receiver** A Slave-receiver is a device that acts as a bus slave in an SMBus

transaction while it is receiving address, command or other data from a

device acting as a bus master in the transaction.

**Slave-transmitter** A Slave-transmitter is a device acting as a bus slave in an SMBus

transaction while it is transmitting data on the bus in response to a bus

master's request

**SMBus Device Default**

Address

The address all ARP-capable slave devices must respond to. After a slave address has been assigned a device must still respond to

commands at the SMBus Device Default Address for ARP management.

This address is fixed at 1100 001.

**SMBus Host Address** The address to which a host must always respond. This address is used

by ARP-capable devices to address the host notify command. This

address is fixed at 0001 000.

**UDID** Unique Device Identifier. A 128-bit value that a device uses during the

ARP process to uniquely identify itself.

**Used Address Pool**The list of slave addresses known by the ARP Master that are either:

Reserved

• Used by non-ARP-capable devices (Fixed Slave Addresses)

Already assigned to ARP-capable devices

The ARP Master must not assign addresses from the first two categories

to ARP-capable devices.

#### 1.7. Conventions

Throughout this document, SMBus addresses are given in binary format. SMBus addresses are 7 binary bits long and are conventionally expressed as 4 bits followed by 3 bits followed by the letter 'b', for example, 0001 110b. These addresses occupy the high seven bits of an eight-bit field on the bus. The low bit of this field, however, has other semantic meaning that is not part of an SMBus address.

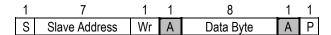

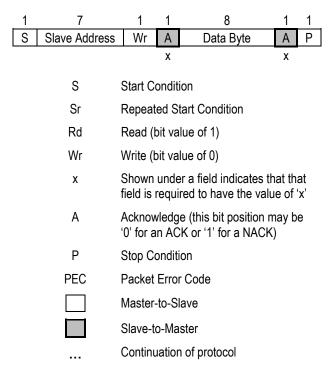

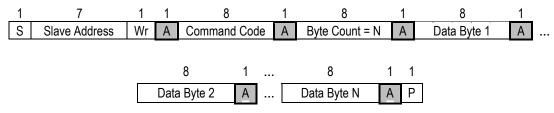

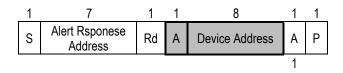

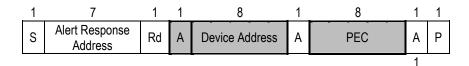

Diagrams of SMBus transaction data structures as they appear on the bus are of the form:

Figure 1-1: generic transaction diagram

In these diagrams, the un-shaded portions are supplied by the bus master of the bus transaction and the shaded portions are driven by the bus slave. The numbers across the top of the transaction diagram indicate the bit widths of each field. In some cases, values will be found below a field in a transaction diagram. When present, this indicates the actual value of the field. The semantics of the various sections of this example transaction are explained in the relevant part of this specification.

The specific SMBus START and STOP conditions, defined in section 4.1.2, are referred to in capital letters.

# 2. General Characteristics

SMBus is a two-wire bus. Multiple devices, both bus masters and bus slaves, may be connected to an SMBus segment. Generally, a bus master device initiates a bus transfer between it and a single bus slave and provides the clock signals. The one exception to this rule, detailed later, is during initial bus setup when a single master may initiate transactions with multiple slaves simultaneously. A bus slave device can receive data provided by the master or it can provide data to the master.

Only one device may master the bus at any time. Since more than one device may attempt to take control of the bus as a master, SMBus provides an arbitration mechanism that relies on the wired-AND connection of all SMBus device interfaces to the SMBus.

This specification defines two classes of electrical characteristics, low power and high power. The first class, originally defined in the SMBus 1.0 and 1.1 specifications, was designed primarily with Smart Batteries in mind, but could be used with other low-power devices. This version of the specification introduces an alternative higher power set of electrical characteristics. This class is appropriate for use when higher drive capability is required, for example with SMBus devices on PCI add-in cards and for connecting such cards across the PCI connector between each other and to SMBus devices on the system board.

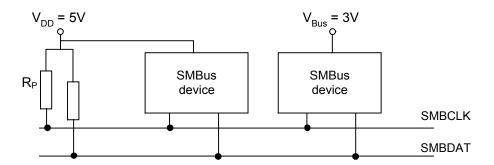

Devices may be powered by the bus  $V_{DD}$  or by another power source,  $V_{Bus}$ , (as with, for example, Smart Batteries) and will inter-operate as long as they adhere to the SMBus electrical specifications for their class.

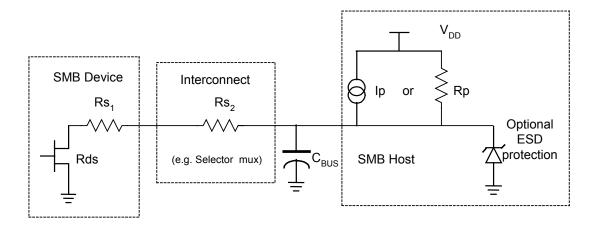

The following diagram shows an example implementation of a 5 volt SMBus with devices powered by the bus  $V_{DD}$  inter-operating with self-powered devices.

Figure 2-1: SMBus Topology

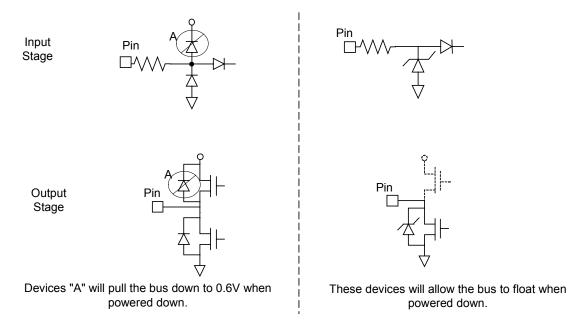

$V_{\rm DD}$  may be 3 to 5 volts +/- 10% and there may be SMBus devices powered directly by the bus  $V_{\rm DD}$ . Both SMBCLK and SMBDAT lines are bi-directional, connected to a positive supply voltage through a pull-up resistor or a current source or other similar circuit. When the bus is free, both lines are high. The output stages of the devices connected to the bus must have an open drain or open collector in order to perform the wired-AND function. Care should be taken in the design of both the input and output stages of SMBus devices, in order not to load the bus when their power plane is turned off, i.e. powered-down devices must provide no leakage path to ground.

Figure 2-2: Example input and output stages of SMBus devices

A device that wants to place a 'zero' on the bus must drive the bus line to the defined logic low voltage level. In order to place a logic 'one' on the bus the device should release the bus line letting it be pulled high by the bus pull-up circuitry.

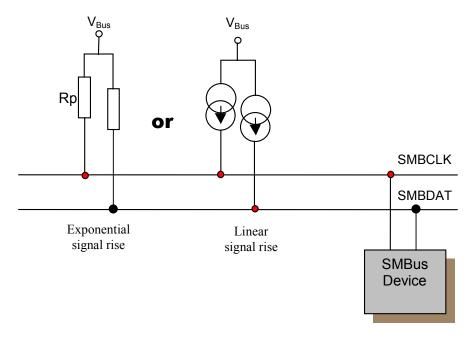

The bus lines may be pulled high by a pull-up resistor or by a current source. In cases that involve higher bus capacitance, a more sophisticated circuit may be used that can limit the pull-down sink current while also providing enough current during the low-to-high transition to maintain the rise time specifications of the SMBus.

Figure 2-3: SMBus pull-up circuitry

# 3. Layer 1 - the Physical layer

#### 3.1. Electrical characteristics of SMBus devices – two discrete worlds

SMBus 2.0 is expected to operate in at least two different mutually exclusive environments that have different electrical requirements. In one case, SMBus must operate reliably in the traditional low-power environment of the battery devices that are at its roots. It must also operate reliably in the higher-noise environment of the PCI connector and PCI add-in cards. This specification meets these needs by providing two classes of electrical characteristics as called out below. Most of these specifications deal with voltage levels, noise margins, etc. Of course, many specific items, including general AC specifications, are the same in both environments.

A low-power and a high-power bus may not be directly connected to each other. Low-power devices should not be expected to work on a high-power bus if the device's current sink capability is smaller than 4mA. However, it is possible to combine a low-power bus segment and a high-power bus segment by connecting the two bus segments through a suitable bridge device.

See Appendix B for ways in which SMBus deviates from I<sup>2</sup>C electricals.

#### 3.1.1. SMBus common AC specifications

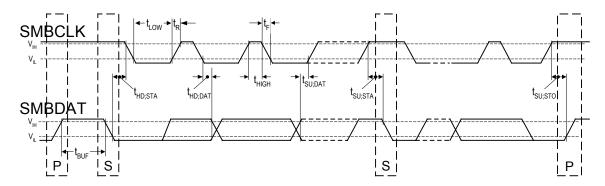

Both high-power and low-power SMBus electricals share a common set of AC specifications. The diagram below illustrates the various SMBus timings and sets the context for the specifications to follow.

Figure 3-1: SMBus timing measurements

The table below applies to both high and low-power classes of electrical specifications.

| Symbol   | Parameter                                                                                    | Limits |     | Units | Comments   |

|----------|----------------------------------------------------------------------------------------------|--------|-----|-------|------------|

|          |                                                                                              | Min    | Max |       |            |

| FSMB     | SMBus Operating Frequency                                                                    | 10     | 100 | KHz   | See note 1 |

| TBUF     | Bus free time between Stop and Start Condition                                               |        | -   | μs    |            |

| THD:STA  | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. |        | -   | μs    |            |

| Tsu:sta  | TSU:STA Repeated Start Condition setup time                                                  |        | -   | μs    |            |

| Tsu:sto  | Stop Condition setup time                                                                    | 4.0    | -   | μs    |            |

| THD:DAT  | Data hold time                                                                               | 300    | -   | ns    |            |

| Tsu:dat  | DAT Data setup time                                                                          |        | -   | ns    |            |

| TTIMEOUT | TIMEOUT Detect clock low timeout                                                             |        | 35  | ms    | See note 2 |

| TLOW     | Clock low period                                                                             | 4.7    | -   | μs    |            |

| THIGH    | Clock high period                                                                            | 4.0    | 50  | μs    | See note 3 |

| Symbol     | Parameter                                                       | Lin | nits | Units | Comments            |  |

|------------|-----------------------------------------------------------------|-----|------|-------|---------------------|--|

| _          |                                                                 | Min | Max  |       |                     |  |

| TLOW: SEXT | Cumulative clock low extend time (slave device)                 | -   | 25   | ms    | See note 4          |  |

| TLOW: MEXT | Cumulative clock low extend time (master device)                |     | 10   | ms    | See note 5          |  |

| TF         | Clock/Data Fall Time                                            |     | 300  | ns    | See note 6          |  |

| Tr         | Clock/Data Rise Time                                            |     | 1000 | ns    | See note 6          |  |

| TPOR       | Time in which a device must be operational after power-on reset |     | 500  | ms    | See section 3.1.4.2 |  |

Table 1: SMBus AC specifications

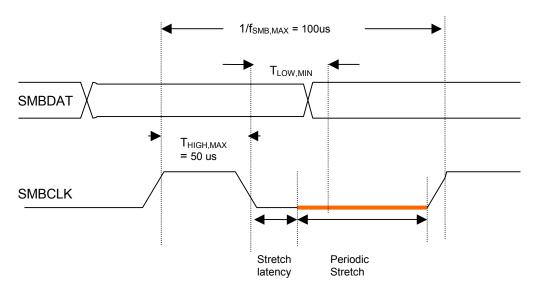

**Note 1:** The minimum frequency for synchronizing device clocks is defined in section 4.3.3. A master shall not drive the clock at a frequency below the minimum FSMB. Further, the operating clock frequency shall not be reduced below the minimum value of FSMB due to periodic clock extending by slave devices as defined in section 4.3.3. This limit does not apply to the bus idle condition, and this limit is independent from the TLOW: SEXT and TLOW: MEXT limits.

For example, if the SMBCLK is high for THIGH,MAX, the clock must not be periodically stretched longer than 1/FSMB,MIN – THIGH,MAX. This requirement does not pertain to a device that extends the SMBCLK low for data processing of a received byte, data buffering and so forth for longer than 100us in a non-periodic way.

**Note 2:** Devices participating in a transfer can abort the transfer in progress and release the bus when any single clock low interval exceeds the value of TTIMEOUT,MIN. After the master in a transaction detects this condition, it must generate a stop condition within or after the current data byte in the transfer process. Devices that have detected this condition must reset their communication and be able to receive a new START condition no later than TTIMEOUT,MAX. Typical device examples include the host controller, and embedded controller and most devices that can master the SMBus. Some simple devices do not contain a clock low drive circuit; this simple kind of device typically may reset its communications port after a start or a stop condition.

A timeout condition can only be ensured if the device that is forcing the timeout holds the SMBCLK low for TTIMEOUT, MAX or longer.

**Note 3:** THIGH,MAX provides a simple guaranteed method for masters to detect bus idle conditions. A master can assume that the bus is free if it detects that the clock and data signals have been high for greater than THIGH,MAX.

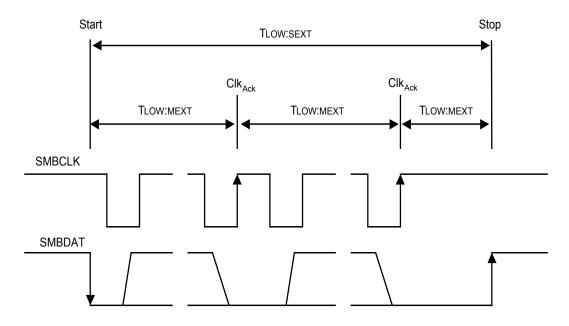

**Note 4:** TLOW:SEXT is the cumulative time a given slave device is allowed to extend the clock cycles in one message from the initial START to the STOP. It is possible that, another slave device or the master will also extend the clock causing the combined clock low extend time to be greater than TLOW:SEXT. Therefore, this parameter is measured with the slave device as the sole target of a full-speed master.

**Note 5:** TLOW:MEXT is the cumulative time a master device is allowed to extend its clock cycles within *each byte* of a message as defined from START-to-ACK, ACK-to-ACK, or ACK-to-STOP. It is possible that a slave device or another master will also extend the clock causing the combined clock low time to be greater than TLOW:MEXT on a given byte. Therefore, this parameter is measured with a full speed slave device as the sole target of the master.

Note 6: Rise and fall time is defined as follows:

TR = (VILMAX - 0.15) to (VIHMIN + 0.15)

TF = (VIHMIN + 0.15)to (VILMAX - 0.15)

#### 3.1.1.1. General Timing Conditions

The SMBus is designed to provide a predictable communications link between a system and its devices. However some devices, such as a Smart Battery using a microcontroller to support bus transactions and to maintain battery data, may require more time than might normally be expected. These specifications take such devices into account while maintaining relatively predictable communications. The following are general comments on the SMBus' timing:

- The bus is at 0 KHz when idle. The FSMB,MIN specification is intended to dissuade components from taking too long to complete a transaction.

- Every device must be able to recognize and react to a START condition at the fastest timings in Table

1: SMBus AC specifications, above.

#### 3.1.1.2. Timeouts

Figure 3-2: Timeout measurement intervals illustrates the definition of the timeout intervals, TLOW:SEXT and TLOW:MEXT.

Figure 3-2: Timeout measurement intervals

#### 3.1.1.3. Slave device timeout definitions and conditions

The TTIMEOUT,MIN parameter allows a master or slave to conclude that a defective device is holding the clock low indefinitely or a master is intentionally trying to drive devices off the bus. It is highly recommended that a slave device release the bus (stop driving the bus and let SMBCLK and SMBDAT float high) when it detects any single clock held low longer than TTIMEOUT,MIN. Devices that have detected this condition must reset their communication and be able to receive a new START condition in no later than TTIMEOUT,MAX.

Slave devices that violate TLOW:SEXT are not conformant with this specification. A Master is allowed to abort the transaction in progress to any slave that violates the TLOW:SEXT or TTIMEOUT,MIN specifications

#### 3.1.1.4. Master device timeout definitions and conditions

TLOW: MEXT is defined as the cumulative time a master device is allowed to extend its clock cycles within one byte in a message as measured from:

START to ACK ACK to ACK ACK to STOP.

A system host may not violate TLOW:MEXT except when caused by the combination of its clock extension with the clock extension from a slave device or another master.

A Master is allowed to abort the transaction in progress to any slave that violates the TLOW:SEXT or TTIMEOUT, MIN specifications. This can be accomplished by the Master issuing a STOP condition at the conclusion of the byte transfer in progress.<sup>1</sup>

#### 3.1.2. Low-power DC specifications

#### 3.1.2.1. DC parameters

The System Management Bus is designed to operate over a range of voltages between 3 and 5 Volts +/-10% (2.7 V to 5.5 V).

| Symbol                            | Parameter                                                                       | Limits |     | Units | Comments        |

|-----------------------------------|---------------------------------------------------------------------------------|--------|-----|-------|-----------------|

| _                                 |                                                                                 |        | Max |       |                 |

| Vı∟ Data, Clock Input Low Voltage |                                                                                 | -      | 0.8 | V     |                 |

| ViH                               | V <sub>I</sub> H Data, Clock Input High Voltage                                 |        | VDD | V     |                 |

| Vol                               | Vol. Data, Clock Output Low Voltage                                             |        | 0.4 | V     | at Ipullup, Max |

| ILEAK                             | ILEAK Input Leakage  IPULLUP Current through pull-up resistor or current source |        | ±5  | μΑ    | Note 1          |

| IPULLUP                           |                                                                                 |        | 350 | μА    | Note 2          |

| VDD                               | Nominal bus voltage                                                             | 2.7    | 5.5 | V     | 3V to 5V ±10%   |

Table 2: Low power SMBus DC specification

Note 1: Devices must meet this specification whether powered or unpowered. However, a microcontroller acting as an SMBus host may exceed ILEAK by no more than 10  $\mu$ A.

Note 2: The IPULLUP, MAX specification is determined primarily by the need to accommodate a maximum of 1.1K equivalent series resistor of removable SMBus devices, such as the Smart Battery, while maintaining the VOL, MAX of the bus.

Because of the relatively low pull-up current, the system designer must ensure that the loading on the bus remains within acceptable limits. Additionally, to prevent bus loading, any devices that remain connected to the active bus while unpowered (that is, their Vcc lowered to zero), must also meet the leakage current specification.

<sup>&</sup>lt;sup>1</sup> A Master should take care when evaluating TLOW:SEXT violation during arbitration since the clock may be held low by multiple slave devices simultaneously. The arbitration interval may be extended for several bytes in the case of devices that respond to commands to the SMBus ARP address. If timeouts are handled at the driver level, the software may need to allow timeouts to be configured or disabled by applications that use the driver in order to support older devices that do not fully meet the SMBus timeout specifications. Devices that implement 'shared' slave addresses may also violate this specification due to combined clock stretching by the different devices sharing the address. TTIMEOUT,MIN, however, does not increase due to combined clock stretching. Therefore, this is a safer timeout parameter for a Master to use when it knows it"s accessing SMBus 2.0 devices.

Systems can be designed today using CMOS components, such as microcontrollers. It is the responsibility of the system designer to ensure that all SMBus components comply with the SMBus timing requirements, and are able to operate within the voltage requirements of the specific system.

Components attached to SMBus may operate at different voltages. Therefore the SMBus cannot assume that all devices will share a common  $V_{DD}$ , hence fixed voltage logic levels.

#### 3.1.2.2. SMBus branch circuit model

The following diagram shows the electrical model of the SMBus. A series protection resistor can be used for ESD protection of components that can be hot-plugged to the system, such as a Smart Battery. The Equivalent Series Resistor (ESR) of the device and interconnect must not exceed 1.1K in order to maintain the  $V_{\text{OL,MAX}}$  of the SMBus low-power specification. This circuit model is equally valid for high-power components discussed in the next section. Due to significantly different bus loading, individual component values will change.

Figure 3-3: SMBus circuit model

The value of the pull-up resistors (Rp) will vary depending on the system's  $V_{DD}$  and the bus' actual capacitance. Current sources (Ip) offer better performance but with increased cost.

The optional diode shown in the diagram above is for ESD protection. It may be necessary in systems where a removable SMBus device such as a Smart Battery is used. However, circuits as actually implemented must comply with the previously stated unpowered leakage current specification.

# V<sub>DD</sub> SMBus device SMBus device SMBus device SMBDAT SMBCLK

## 3.1.3. High-Power DC specifications

Figure 3-4: SMBus branch with multiple devices attached

\* All R<sub>s</sub> are optional

High-power SMBus is specified below. These higher power specifications provide the robustness necessary, for example, to allow SMBus to cross the PCI connector, thus allowing SMBus devices on PCI add-in cards to communicate with other devices on both the system board and other PCI add-in cards in the same system. These higher power electrical specifications are an alternative to the lower power specifications stated above and may be used in environments where necessary. Some parameters are explained further in the sections below.

| Symbol                | Parameter                                           | Lin | nits     | Units  | Comments                                                     |

|-----------------------|-----------------------------------------------------|-----|----------|--------|--------------------------------------------------------------|

|                       |                                                     | Min | Max      |        |                                                              |

| $V_{IL}$              | V <sub>IL</sub> SMBus signal Input low voltage      |     |          | V      |                                                              |

| $V_{IH}$              | SMBus signal Input high voltage                     | 2.1 | $V_{DD}$ | V      |                                                              |

| V <sub>OL</sub>       |                                                     |     | 0.4      | V      | @ IPULLUP                                                    |

| I <sub>LEAK-BUS</sub> | I <sub>LEAK-BUS</sub> Input Leakage per bus segment |     | ±200     | uA     |                                                              |

| I <sub>LEAK-PIN</sub> | I <sub>LEAK-PIN</sub> Input Leakage per device pin  |     | ±10      | uA     |                                                              |

| Vdd                   | Nominal bus voltage                                 | 2.7 | 5.5      | V      | 3V to 5V ±10%                                                |

| I <sub>PULLUP</sub>   | Current sinking, VOL = 0.4V                         | 4   |          | mA     |                                                              |

| $C_{BUS}$             |                                                     |     | 400      | pF     |                                                              |

| Cı                    | CI Capacitance for SMBDAT or SMBCLK pin             |     | 10       | pF     | Recommended                                                  |

| V <sub>NOISE</sub>    |                                                     |     | -        | mV p-p | This AC item applies to the high-power DC specification only |

Table 3: High-power SMBus DC specification

#### 3.1.3.1. Capacitive load of high-power SMBus lines

Capacitive load for each bus line includes all pin, wire and connector capacitances. The maximum capacitive load affects the selection of the  $R_P$  pull-up resistor or the current source in order to meet the rise time specifications of SMBus.

Pin capacitance (CI) is defined as the total capacitive load of one SMBus device as seen in a typical manufacturer's data sheet. The value is a recommended guideline so that two such devices may, for example, be populated on an add-in card.

#### 3.1.3.2. Minimum current sinking requirements for SMBus devices

While SMBus devices used in low-power segments have practically no minimum current sinking requirements due to the low pull-up current specified for low-power segments, devices in high-power segments are required to sink a minimum current of 4 mA while maintaining the  $V_{OL,MAX}$  of 0.4 Volts. The requirement for 4 mA sink current determines the minimum value of the pull-up resistor  $R_P$  that can be used in SMBus systems.

#### 3.1.4 Additional common low and high-power specifications

#### 3.1.4.1 SMBus 'back powering' considerations

Unpowered devices connected to either a low-power or high-power SMBus segment must provide, either within the device or through the interface circuitry, protection against "back powering" the SMBus. Unpowered devices connected to high-power segments must meet leakage specifications in section 3.1.2.1.

#### 3.1.4.2 Power-on reset

SMBus devices detect a power-on event in one of three ways:

- By detecting that power is being applied to the device,

- By an external reset signal that is being asserted or

- For self-powered or always powered devices, by detecting that the SMBus is active (clock and data lines have gone high after being low for more than 2 1/2 seconds).

An SMBus device must respond to a power-on event by bringing the device into an operational state within TPOR, defined in Table 1, after the device has been supplied power that is within the device's normal operating range. Self-powered or always-powered devices, such as Smart Batteries, are not required to do a complete power-on reset but must be in an operational state within 500 milliseconds after the SMBus becomes active.

# 4. Layer 2 - the Data Link layer

#### 4.1. Bit transfers

SMBus uses fixed voltage levels to define the logic "ZERO" and logic "ONE" on the bus respectively.

#### 4.1.1. Data validity

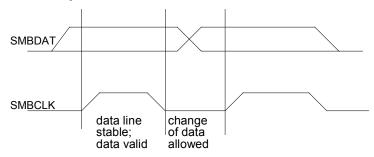

Figure 4-1: Data validity

The data on SMBDAT must be stable during the "HIGH" period of the clock. Data can change state only when SMBCLK is low. Figure 4-1 illustrates the relationships. See figure 3-1 and table 1 for actual specifications.

#### 4.1.2. START and STOP conditions

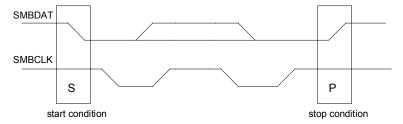

Figure 4-2: START and STOP conditions

Two unique bus situations define a message START and STOP condition.

- A HIGH to LOW transition of the SMBDAT line while SMBCLK is HIGH indicates a message START condition.

- A LOW to HIGH transition of the SMBDAT line while SMBCLK is HIGH defines a message STOP condition. START and STOP conditions are always generated by the bus master. After a START condition the bus is considered to be busy. The bus becomes idle again after certain time following a STOP condition or after both the SMBCLK and SMBDAT lines remain high for more than THIGH:MAX.

#### 4.1.3. Bus idle condition

Bus idle is the conditon during which the SMBCLK and SMBDAT lines are both high, without any state transitions, for a time period specified as the minimum of the following:

- TBUF  $(4.7 \mu S)$  from the last detected STOP condition, or

- THIGH:MAX (50 μS)

The latter timing parameter covers the condition where a master has been dynamically added to the bus and may not have detected a state transition on the SMBCLK or SMBDAT lines. In this case, the master must wait long enough to ensure that a transfer is not currently in progress.

#### 4.2. Data transfers on SMBus

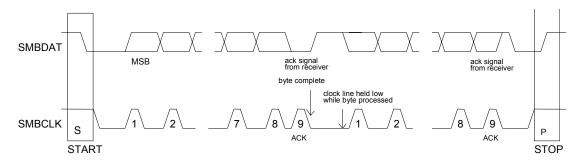

Figure 4-3: SMBus byte format

Every byte consists of 8 bits. Each byte transferred on the bus must be followed by an acknowledge bit. Bytes are transferred with the most significant bit (MSB) first.

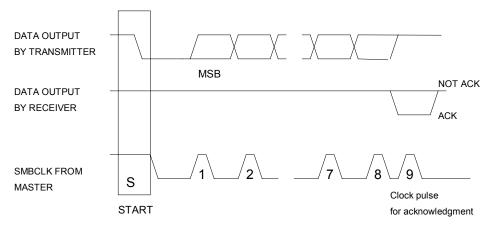

The diagram below, figure 4-4 illustrates the positioning of acknowledge (ACK) and not acknowledge (NACK) pulses relative to other data

Figure 4-4: ACK and NACK signaling of SMBus

The acknowledge-related clock pulse is generated by the master. The transmitter, master or slave, releases the SMBDAT line (HIGH) during the acknowledge clock cycle. In order to acknowledge a byte, the receiver must pull the SMBDAT line LOW during the HIGH period of the clock pulse according to the SMBus timing specifications. A receiver that wishes to NACK a byte must let the SMBDAT line remain HIGH during the acknowledge clock pulse.

An SMBus device must always acknowledge (ACK) its own address. SMBus uses this signaling to detect the presence of detachable devices on the bus.

An SMBus slave device may decide to NACK a byte other than the address byte in the following situations:

• The slave device is busy performing a real time task, or data requested are not available. The master upon detection of the NACK condition must generate a STOP condition to abort the transfer. Note

that as an alternative, the slave device can extend the clock LOW period within the limits of this specification in order to complete its tasks and continue the transfer.

- The slave device detects an invalid command or invalid data. In this case the slave device must NACK

the received byte. The master upon detection of this condition must generate a STOP condition and

retry the transaction.

- If a master-receiver is involved in the transaction it must signal the end of data to the slave-transmitter by generating an NACK on the last byte that was clocked out by the slave. The slave-transmitter must release the data line to allow the master to generate a STOP condition.

The latter mechanism is one way for a device to detect whether a slave transmitter implements Packet Error Checking. See section 5.4 for more information on Packet Error Checking.

# 4.3. Clock generation and arbitration

#### 4.3.1. Synchronization

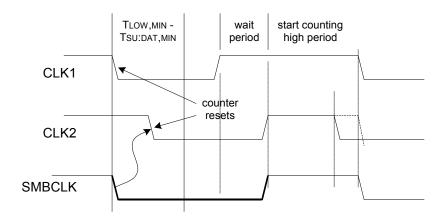

A situation may occur in which more than one master is trying to place clock signals on the bus at the same time. The resulting bus signal will be the wired AND of all the clock signals provided by the masters.

It is important for the bus integrity that there is a clear definition of the clock, bit by bit for all masters involved during an arbitration process.

A high-to-low transition on the SMBCLK line will cause all devices involved to start counting off their LOW period and start driving SMBCLK low if the device is a master. As soon as a device finishes counting its LOW period it will release the SMBCLK line. Nevertheless, the actual signal on the SMBCLK may not transition to the HIGH state if another master with longer LOW period keeps the SMBCLK line LOW. In this situation the master that released the SMBCLK line will enter the SMBCLK HIGH wait period. When all devices have counted off their LOW period, the SMBCLK line will be released and go HIGH. All devices concerned at this point will start counting their HIGH periods. The first device that completes its HIGH period count will pull the SMBCLK line LOW and the cycle will start again.

Figure 4-5: SMBus clock synchronization

In Figure 4-5, the interval between the first high-to-low transition of CLK1 and CLK2 must be less than (TLOW:MIN – TSU:DAT). This way, a synchronized clock is provided for all devices, where the SMBCLK

LOW period is determined by the slowest device and the SMBCLK HIGH period is determined by the fastest device.

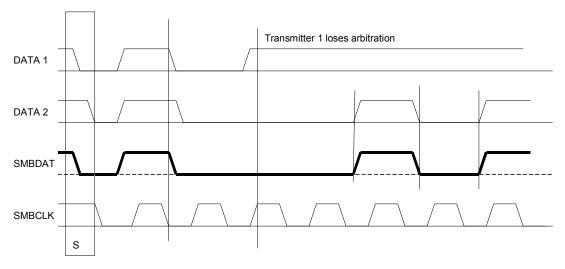

#### 4.3.2. Arbitration

A master may start a transfer only if the bus is idle. One or more devices may generate a START condition within the minimum hold time ( $t_{HOLD:STA}$ ) resulting in a defined START condition on the bus.

Since the devices that generated the START condition may not be aware that other masters are contending for the bus, arbitration takes place on the SMBDAT line while the SMBCLK is HIGH. A master that transmits a HIGH level, while the other(s) master is transmitting a LOW level on the SMBDAT line loses control of the bus in the arbitration cycle.

The master that lost the arbitration may continue to provide clock pulses until the completion of the byte on which it lost the arbitration. Arbitration in the case of two masters trying to access the same device may continue past the address byte. In this case arbitration will continue with the remaining transfer data. In the event that two masters are arbitrating and the first master wants to put a repeated START on the bus while the second master wants to put a ZERO data bit on the bus, the first master must recognize that it cannot cause the start and lose arbitration. If the first master wants to put a repeated START on the bus while the second master wants to put a ONE data bit on the bus, the second master will see the repeated start and lose arbitration. If both masters put a repeated START on the bus in the same bit position, arbitration should continue at each data bit.

This mechanism requires that SMBus master devices participating in an arbitration cycle monitor the actual state of the SMBDAT line during arbitration.

If a master also incorporates a slave function and loses control of the bus in the arbitration cycle during the address stage, it must check the actual address placed on the bus in order to determine whether another master is trying to access it. In this case the master that lost the arbitration must switch immediately to its slave receiver mode in order to receive the rest of the message.

Figure 4-6: SMBus arbitration

During each bus transaction masters are still required to be able to recognize a repeated START condition on the bus. A device that detects a repeated START condition that it didn't generate must quit the transfer.

Once a master has won arbitration, arbitration is disallowed until the bus is again idle.

#### 4.3.3. Clock low extending

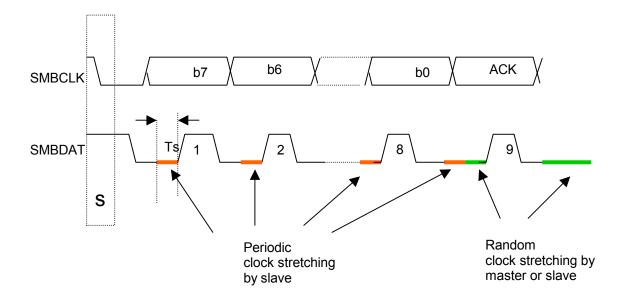

SMBus provides a clock synchronization mechanism to allow devices of different speeds to co-exist on the bus. In addition to the bus arbitration procedure the clock synchronization mechanism can be used during a bit or a byte transfer in order to allow slower slave devices to cope with faster masters.

At the bit level, a device may slow down the bus by periodically extending the clock low interval.

Devices are allowed to stretch the clock during the transfer of one message up to the maximum limits described in the AC specifications of this document. Nevertheless, devices designed to stretch every clock cycle periodically must maintain the  $f_{SMB,MIN}$  frequency of 10 KHz ( $f_{SMB,MIN}^{-1}=100\mu s$ ) in order to preserve the SMBus bandwidth.

Figure 4-7: Periodic clock stretching by a slave SMBus device

Clock LOW extension, or stretching , if necessary, must start after the SMBCLK high-to-low transition within a  $T_{LOW:MIN-}$  TSU:DAT interval. Devices designed to stretch the clock on every bit transfer must maintain the minimum bus frequency  $f_{SMB,MIN}$  of 10 KHz. A slave device may opt to stretch the clock line during a specific bit transfer in order to process a real time task or check the validity of a byte. In this case the slave device must adhere to the  $T_{TIMEOUT}$  and  $T_{LOW:SEXT}$  specifications. Clock LOW extension may occur during any bit transfer including the clock provided prior to the ACK clock pulse.

A slave device may select to stretch the clock LOW period between byte transfers on the bus, in order to process received data or prepare data for transmission. In this case the slave device will hold the clock line LOW after the reception and acknowledgement of a byte. Again the slave device is responsible for not violating the  $T_{\text{LOW:SEXT}}$  specification of SMBus.

During a bus transaction the master also can select to extend the clock LOW period between bytes or at any point in the byte transfer, including the clock LOW period after the byte transfer and before the acknowledgement clock. The master may need to extend the clock LOW period selectively in order to process data or serve a real time task. In doing so, the master must not exceed the  $T_{LOW:MEXT}$  specification.

Figure 4-8: Periodic and random clock stretching

Both master and slave devices must adhere to the SMBus  $T_{\text{TIMEOUT}}$  specification in order to maintain bus bandwidth and recovery from fatal bus conditions.

#### 4.4. Data transfer formats

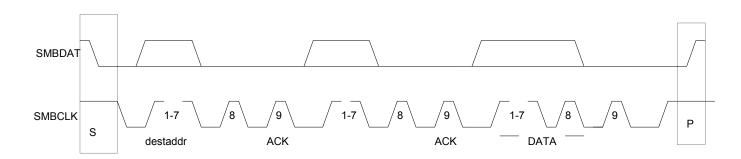

SMBus data transfers follow the format shown in the following figure.

Figure 4-9: Data transfer over SMBus

After the START condition, **S**, the master places the 7-bit address of the slave device it wants to address on the bus. The address is 7 bits long followed by an eighth bit indicating the direction of the data transfer (R/W#); a ZERO indicates a transmission (WRITE) while a ONE indicates a request for data (READ). A data transfer is always terminated by a STOP (P) condition generated by the master.

Specific SMBus protocols require the master to generate a repeated START condition followed by the slave device address without first generating a STOP condition.

# 5. Layer 3 - Network layer

# 5.1. Usage model

The System Management Bus Specification refers to three types of devices. A *slave* is a device that is receiving or responding to a command. A *master* is a device that issues commands, generates the clocks, and terminates the transfer. A *host* is a specialized master that provides the main interface to the system's CPU. A host must be a master-slave and must support the SMBus host notify protocol. There may be at most one host in a system. One example of a hostless system is a simple battery charging station. The station might sit plugged into a wall waiting to charge a smart battery.

A device may be designed so that it is never a master and always a slave. A device may act as a slave most of the time, but in special instances it may become a master. A device can also be designed to be a master only. A system host is an example of a device that acts as a host most of the time but that includes some slave behavior..

#### 5.2. Device identification – slave address

Any device that exists on the System Management Bus as a slave has a unique address called the *Slave Address*. For reference, the following addresses are reserved and must not be used by or assigned to any SMBus slave device unless otherwise detailed by this specification.

| Slave Address<br>Bits 7-1 | R/W# bit<br>Bit 0 | Comment                                   |  |

|---------------------------|-------------------|-------------------------------------------|--|

| 0000 000                  | 0                 | General Call Address                      |  |

| 0000 000                  | 1                 | START byte                                |  |

| 0000 001                  | X                 | CBUS address                              |  |

| 0000 010                  | X                 | Address reserved for different bus format |  |

| 0000 011                  | X                 | Reserved for future use                   |  |

| 0000 1XX                  | X                 | Reserved for future use                   |  |

| 0101 000                  | X                 | Reserved for ACCESS.bus host              |  |

| 0110 111                  | X                 | Reserved for ACCESS.bus default address   |  |

| 1111 0XX                  | X                 | 10-bit slave addressing                   |  |

| 1111 1XX                  | X                 | Reserved for future use                   |  |

| 0001 000                  | X                 | SMBus Host                                |  |

| 0001 100                  | X                 | SMBus Alert Response Address              |  |

| 1100 001                  | X                 | SMBus Device Default Address              |  |

**Table 4: Reserved SMBus Addresses**

All other addresses are available for address assignment for dynamic address devices and/or for miscellaneous devices. Miscellaneous device addresses are discussed in Section 5.2.1.4.

The SMBus Alert Response Address (0001 100) can be a substitute for device master capability. See Appendix A for details.

The SMBus Device Default Address is reserved for use by the SMBus Address Resolution Protocol, which allows addresses to be assigned dynamically. See section 5.6 for details

Addresses not specified here or within the appendices are reserved for future use. All 10-bit slave addresses are reserved for future use and are outside the scope of this specification.

The host has the lowest legitimate address so that messages going to the host have the highest priority with respect to bus arbitration.

#### 5.2.1. SMBus address types

Several SMBus devices can be used simultaneously in an actual system. In case of device address contention the designer may use either programmable features implemented in SMBus devices to resolve such contention or/and multiple SMBus branches within the same system to spread devices that use the same address.

There are several type of addresses currently in use in actual SMBus systems.

#### 5.2.1.1. Reserved addresses

SMBus, Access.bus and I<sup>2</sup>C reserve several addresses for specific bus functions as defined in Table 4.

# 5.2.1.2. Purpose-assigned addresses

These addresses are assigned by the SMBus Working Group to specific types of devices. Each device type that obtains an assigned address has to have an SMBus specification associated with it. Some systems using SMBus assume that if a device exists at a purpose-assigned address then the device complies with the associated specifications for that address. For example, SMBus application to Smart Battery implementations assume that Smart Battery devices and controllers are at their purpose-assigned addresses. Thus, devices that do not meet the purpose-assigned address specifications for Smart Battery devices cannot be used in Smart Battery applications.

Other SMBus implementations do not rely solely on the device address to identify a device's functionality. In these applications, devices may have addresses that overlap with the purpose-assigned addresses.

The device manufacturer is forewarned that this may preclude use of that device in other applications. In general, purpose-assigned addresses should be avoided except for devices that are intended to meet the specification for the corresponding address(es). The device manufacturer should consult the SMBus WG to get the latest information on purpose-assigned addresses as a guide to whether their address assignment is disallowed in certain SMBus applications.

#### 5.2.1.3. Prototype Addresses

| Slave Address | Description         |

|---------------|---------------------|

| 1001 0XX      | Prototype Addresses |

**Table 5: Prototype addresses**

The Prototype addresses (1001 0XX) are reserved for device prototyping and experimenting in applications that utilize purpose-assigned addresses. They are not intended for production parts and should never be assigned to any device.

#### 5.2.1.4. Miscellaneous device addresses

Manufacturers have produced and may continue producing SMBus compatible devices for specific system purposes, for which they do not need to implement the complete SMBus specification, or for which they do not require explicit support from the OS. Such devices, for example, may be port expanders, D/A circuits, etc. The SMBus web site (http://www.smbus.org) includes a page where SBS-IF member companies can share address information for such devices. This page may aid manufacturers to avoid address conflicts with devices likely to co-exist on the same SMBus segment.

#### 5.2.1.5. Dynamically assigned addresses

Version 2.0 introduces the concept of dynamically assigned addresses. This is detailed in section 5.6.

# 5.3. Using a device

A typical SMBus device will have a set of commands by which data can be read and written. All commands are 8 bits (1 byte) long. Command arguments and return values can vary in length. Accessing a command that does not exist or is not supported may cause an error condition. In accordance with this specification, the Most Significant Bit is transferred first.

There are eleven possible command protocols for any given device. A slave device may use any or all of the eleven protocols to communicate. The protocols are Quick Command, Send Byte, Receive Byte, Write Byte, Write Word, Read Byte, Read Word, Process Call, Block Read, Block Write and Block Write-Block Read Process Call.

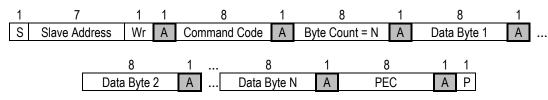

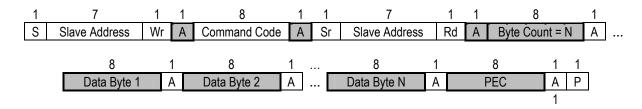

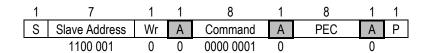

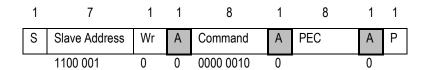

# 5.4. Packet error checking

Version 1.1 of SMBus introduced a Packet Error Checking mechanism to improve reliability and communication robustness. Implementation of Packet Error Checking by SMBus devices is optional for SMBus devices but is required for devices participating in and only during the ARP process. SMBus devices that implement Packet Error Checking must be capable to communicate with the host and other devices that do not implement the Packet Error Checking mechanism.

Packet Error Checking, whenever applicable, is implemented by appending a Packet Error Code (PEC) at the end of each message transfer. Each protocol (except for Quick Commandand the host notify protocol described in a later Section) has two variants: one with the Packet Error Code (PEC) byte and one without. The PEC is a CRC-8 error-checking byte, calculated on all the message bytes (including addresses and read/write bits). The PEC is appended to the message by the device that supplied the last data byte.

#### 5.4.1. Packet error checking implementation

The SMBus must accommodate any mixture of devices that support Packet Error Checking and devices that do not. A device that acts as a slave and supports the PEC must always be prepared to perform the slave transfer with or without a PEC, verify the correctness of the PEC if present, and only process the message if the PEC is correct. Implementations are encouraged to issue a NACK if the PEC is present but not correct.

#### 5.4.1.1. ACK/NACK and Packet Error Checking

The ACK/NACK bit in an SMBus byte is as susceptible to corruption as any other bit in an SMBus packet. Hence, an ACK at the end of a PEC is not a guarantee that the PEC is correct. A master-transmitter receiving an ACK at the end of a write should not necessarily assume that the write was successfully carried out at the slave-receiver of the write, although it is highly likely that it was.

A NACK received after a PEC by a master-transmitter indicates that the link layer of the slave-receiver became aware of an error with the transmission in time to supply a NACK at the end of the PEC byte. This may be due to an incorrect PEC or any other error. Errors discovered above the data link layer may also be indicated with a NACK if the device is fast enough to discover and indicate the error when the NACK is due.

An ACK received after a PEC by a master-transmitter means that no error could be determined by the link layer in the slave-receiver in time to supply a NACK. This might be because the receiver is not able to check the validity of the PEC in real time.

If a master transmitter wants to be sure that a write-operation is performed correctly at the target device, it must use some higher-layer mechanism to verify this. This might take the form of a read-with-PEC of the data; receipt of a correct PEC would reliably indicate that that the original write occurred without error.

When a master-receiver reads data from a slave-transmitter, the ACK/NACK supplied by the master-receiver at the end of the transaction has little meaning other than to mark the end of the last byte. The slave-transmitter is supplying the data, and if the PEC supplied by the slave-transmitter is correct, the master-receiver may assume that the data was received as the slave transmitted it. If not, it is up to the master-receiver to take any appropriate remedial action.

#### 5.4.1.2. Master implementation

A master may use PEC on any transaction. It is required that the master have either a priori knowledge of whether or not the target slave supports PEC or a way to determine whether the target slave supports PEC. The use of PEC is governed by upper layer protocols (e.g. device drivers), specifications (e.g. requirements of the SMBus ARP protocol) or detection algorithms for a given class of devices (e.g. smart batteries).

#### 5.4.1.3. Slave implementation

A slave device that implements Packet Error Checking must be prepared to receive and transmit data with or without a PEC. During a slave receive transfer, after the device has identified the protocol and command must accept and check the additional PEC for validity.

During a slave transmit transfer, the slave transmitter must respond to additional clocks after the last byte transfer and furnish a PEC to the master receiver requesting it.

Each bus transaction requires a Packet Error Code (PEC) calculation by both the transmitter and receiver within each packet. The PEC uses an 8-bit cyclic redundancy check (CRC-8) of each read or write bus transaction to calculate a Packet Error Code (PEC). The PEC may be calculated in any way that conforms to a CRC-8 represented by the polynomial,  $C(x) = x^8 + x^2 + x^1 + 1$  and must be calculated in the order of the bits as received.

Calculating the PEC for transmission or reception is implemented in a method chosen by the device manufacturer. It is possible to perform the check with low-cost hardware or firmware algorithm that could process the message bit-by-bit or with a byte-wise look-up table. The SMBus web page provides some example CRC-8 methods.

The PEC is appended to the message as dictated by the protocols in section 5.5. The PEC calculation includes all bytes in the transmission, including address, command and data. The PEC calculation does not include ACK, NACK, START, STOP nor Repeated START bits. This means that the PEC is computed over the entire message from the first START condition.

Whether a device implements packet error checking may be determined by the specification revision code that is present in the SpecificationInfo() command for a Smart Battery, Smart Battery Charger or Smart Battery Selector. See these individual specifications for exact revision coding identities. It may also be discovered in the UDID, defined in section 5.6.1, for other devices.

#### 5.5. Bus Protocols

Following is a description of the various SMBus protocols with and without a Packet Error Code. Compliant devices need not support all the protocols defined in this section. The results returned by such a device to a protocol it does not support are undefined.

Below is a key to the protocol diagrams in this section. Not all protocol elements will be present in every command. For instance, not all packets are required to include the Packet Error Code.

Figure 5-1: SMBus packet protocol diagram element key

A value shown below a field in the following diagrams is a mandatory value for that field.

The data formats implemented by SMBus are:

- Master-transmitter transmits to slave-receiver: The transfer direction in this case is not changed.

- Master reads slave immediately after the first byte: At the moment of the first acknowledgment (provided by the slave-receiver) the master-transmitter becomes a master-receiver and the slave-receiver becomes a slave-transmitter.

- Combined format: During a change of direction within a transfer, the master repeats both a START condition and the slave address but with the R/W# bit reversed. In this case the master receiver terminates the transfer by generating a NACK on the last byte of the transfer and a STOP condition.

Examples of these formats will be seen in the SMBus protocols below.

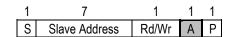

#### 5.5.1. Quick command

Here, part of the slave address denotes the command – the R/W# bit. The R/W# bit may be used to simply turn a device function on or off, or enable/disable a low-power standby mode. There is no data sent or received.

The quick command implementation is good for very small devices that have limited support for the SMBus specification. It also limits data on the bus for simple devices.

Figure 5-2: Quick command protocol

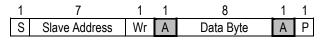

#### 5.5.2. Send byte

A simple device may recognize its own slave address and accept up to 256 possible encoded commands in the form of a byte that follows the slave address.

All or parts of the Send Byte may contribute to the command. For example, the highest 7 bits of the command code might specify an access to a feature, while the least significant bit would tell the device to turn the feature on or off. Or, a device may set the "volume" of its output based on the value it received from the Send Byte protocol.

Figure 5-3: Send byte protocol

Figure 5-4: Send byte protocol with PEC

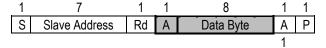

#### 5.5.3. Receive byte

The Receive Byte is similar to a Send Byte, the only difference being the direction of data transfer. A simple device may have information that the host needs. It can do so with the Receive Byte protocol. The same device may accept both Send Byte and Receive Byte protocols. A NACK (a '1' in the ACK bit position) signifies the end of a read transfer.

Figure 5-5: Receive byte protocol

Figure 5-6: Receive byte protocol with PEC

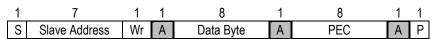

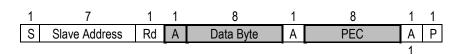

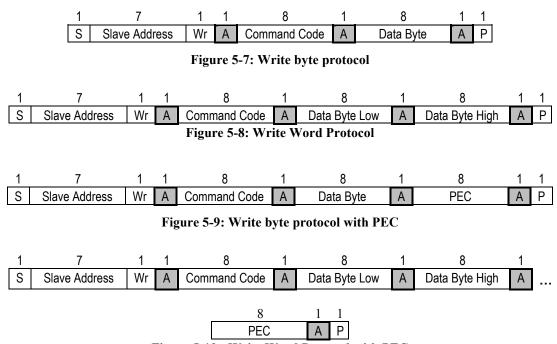

#### 5.5.4. Write byte/word

The first byte of a Write Byte/Word access is the command code. The next one or two bytes, respectively, are the data to be written. In this example the master asserts the slave device address followed by the write bit. The device acknowledges and the master delivers the command code. The slave again acknowledges before the master sends the data byte or word (low byte first). The slave acknowledges each byte, and the entire transaction is finished with a STOP condition.

Figure 5-10: Write Word Protocol with PEC

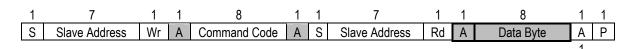

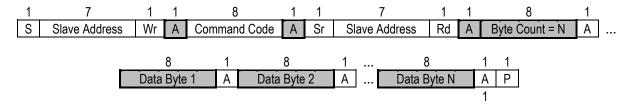

#### 5.5.5. Read byte/word

Reading data is slightly more complicated than writing data. First the host must write a command to the slave device. Then it must follow that command with a repeated START condition to denote a read from that device's address. The slave then returns one or two bytes of data.

Note that there is no STOP condition before the repeated START condition, and that a NACK signifies the end of the read transfer.

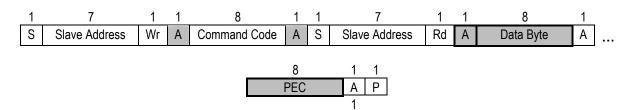

Figure 5-11: Read Byte Protocol

Figure 5-12: Read byte protocol with PEC

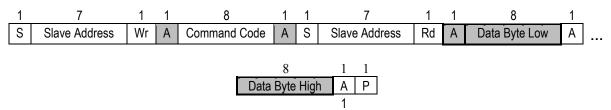

Figure 5-13: Read word protocol

Figure 5-14: Read word protocol with PEC

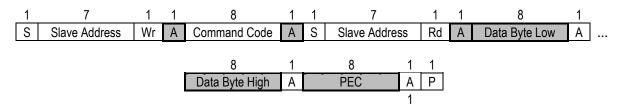

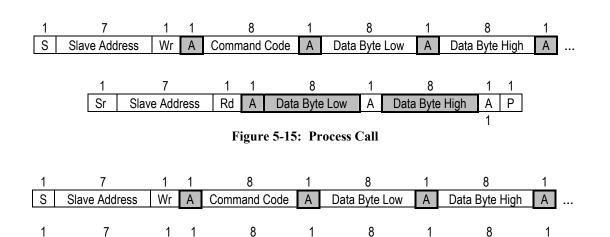

#### 5.5.6. Process call

The process call is so named because a command sends data and waits for the slave to return a value dependent on that data. The protocol is simply a Write Word followed by a Read Word without the Read-Word command field and the Write-Word STOP bit.

Note that there is no STOP condition before the repeated START condition, and that a NACK signifies the end of the read transfer.

Figure 5-16: Process Call with PEC

Α

Data Byte HIgh

Data Byte Low

#### 5.5.7. Block write/read

Rd A

The Block Write begins with a slave address and a write condition. After the command code the host issues a byte count which describes how many more bytes will follow in the message. If a slave has 20 bytes to send, the byte count field will have the value 20 (14h), followed by the 20 bytes of data. The byte

Slave Address

Sr

PEC

Α

Α

count does not include the PEC byte. The byte count may not be 0. A Block Read or Write is allowed to transfer a maximum of 32 data bytes.

Figure 5-17: Block Write

Figure 5-18: Block Write with PEC

A Block Read differs from a block write in that the repeated START condition exists to satisfy the requirement for a change in the transfer direction. A NACK immediately preceding the STOP condition signifies the end of the read transfer.

Figure 5-19: Block Read

Figure 5-20: Block Read with PEC

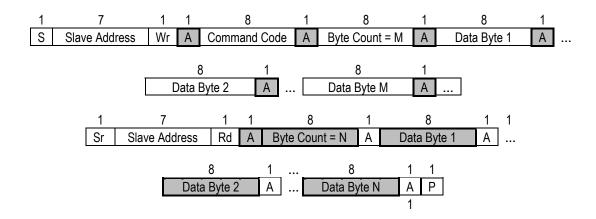

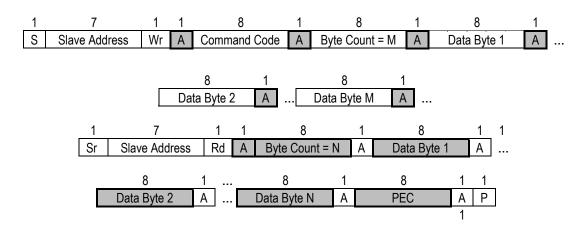

#### 5.5.8. Block write-block read process call

The block write-block read process call is a two-part message. The call begins with a slave address and a write condition. After the command code the host issues a write byte count (M) that describes how many more bytes will be written in the first part of the message. If a master has 6 bytes to send, the byte count

field will have the value 6 (0000 0110b), followed by the 6 bytes of data. The write byte count (M) cannot be zero.

The second part of the message is a block of read data beginning with a repeated start condition followed by the slave address and a Read bit. The next byte is the read byte count (N), which may differ from the write byte count (M). The read byte count (N) cannot be zero.

The combined data payload must not exceed 32 bytes. The byte length restrictions of this process call are summarized as follows:

- $M \ge 1$  byte

- $N \ge 1$  byte

- $M + N \le 32$  bytes

The read byte count does not include the PEC byte. The PEC is computed on the total message beginning with the first slave address and using the normal PEC computational rules. It is highly recommended that a PEC byte be used with the Block Write-Block Read Process Call.

Note that there is no STOP condition before the repeated START condition, and that a NACK signifies the end of the read transfer.

Figure 5-21: Block Write - Block Read Process Call

Figure 5-22: Block Write - Block Read Process Call with PEC

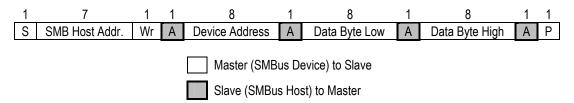

#### 5.5.9 SMBus host notify protocol

To prevent messages coming to the SMBus host controller from unknown devices in unknown formats only one method of communication is allowed, a modified form of the Write Word protocol. The standard Write Word protocol is modified by replacing the command code with the alerting device's address. This protocol MUST be used when an SMBus device becomes a **master** in order to communicate with the SMBus host acting as a **slave**.

Communication from SMBus Device to SMBus Host begins with the SMBus Host address (0001 000b). The message's Command Code is the initiating SMBus device's address. From this, the SMBus Host knows the origin of the following 16 bits of device status. The contents of the status are device specific.

Figure 5-23: 7-bit Addressable Device to Host Communication

SMBus hosts must support the host notify protocol. Hosts may implement the optional #SMBALERT line if devices in the system use it.

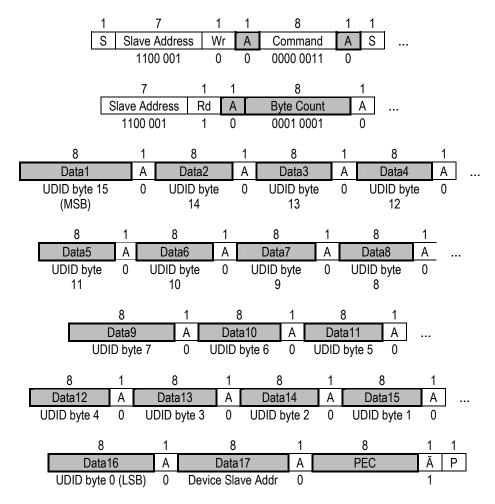

# 5.6. SMBus Address resolution protocol

SMBus slave address conflicts can be resolved by dynamically assigning a new unique address to each slave device. The Address Resolution Protocol (ARP) possesses the following attributes:

- Address assignment utilizes the standard SMBus physical layer arbitration mechanism

- Assigned addresses remain constant while device power is applied; address retention through device power loss is also allowed

- No additional SMBus packet overhead is incurred after address assignment. (i.e. subsequent accesses to assigned slave addresses have the same overhead as accesses to fixed address devices.)

- Any SMBus master can enumerate the bus

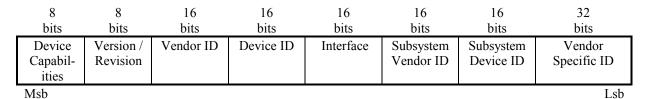

#### 5.6.1. Unique Device Identifier (UDID)

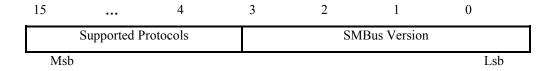

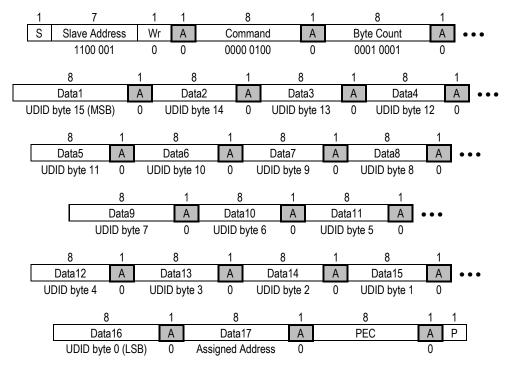

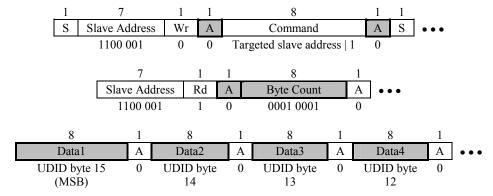

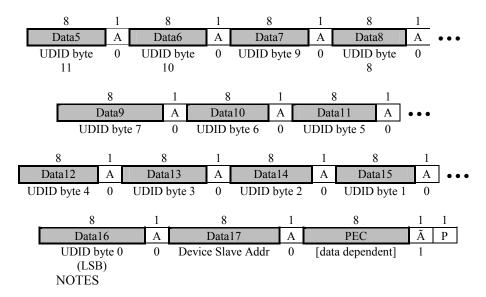

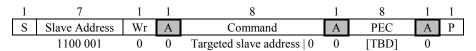

In order to provide a mechanism to isolate each device for the purpose of address assignment each device must implement a unique device identifier (UDID). This 128-bit number is comprised of the following fields:

Figure 5-24: UDID

**Device Capabilities** Describes the device's capabilities. See detail below.

**Version / Revision** UDID version number, and a silicon revision identification. See detail below.

**Vendor ID** The device manufacturer's ID as assigned by the SBS Implementers' Forum or the

PCI SIG.

**Device ID** The device ID as assigned by the device manufacturer (identified by the Vendor ID

field).

**Interface** Identifies the protocol layer interfaces supported over the SMBus connection by the

device. For example, ASF and IPMI.

**Subsystem Vendor ID** This field may hold a value derived from any of several sources:

• The device manufacturer's ID as assigned by the SBS Implementers' Forum or the PCI SIG.

The device OEM's ID as assigned by the SBS Implementers' Forum or the PCI SIG

A value that, in combination with the Subsystem Device ID, can be used to identify an organization or industry group that has defined a particular common device interface specification.

**Subsystem Device ID** The subsystem ID identifies a specific interface, implementation, or device. The

Subsystem ID is defined by the party identified by the Subsystem Vendor ID field.

**Vendor-specific ID** A unique number per device. See detail below.

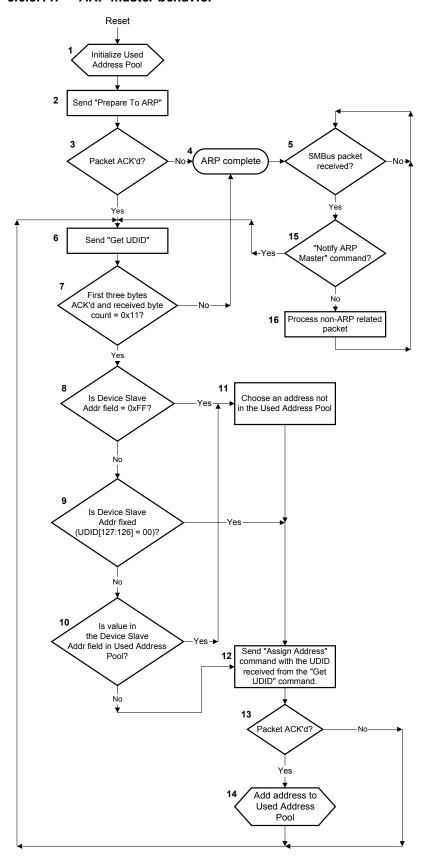

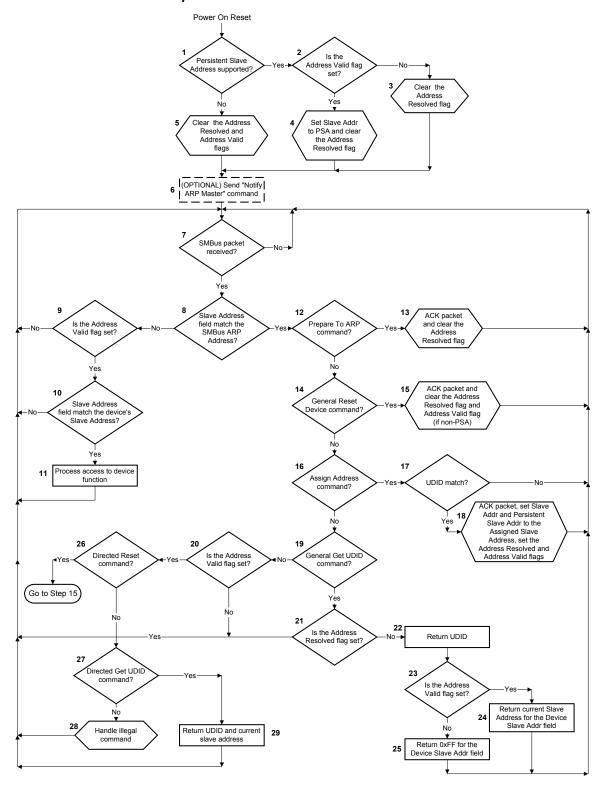

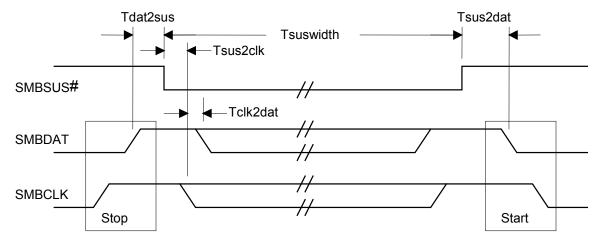

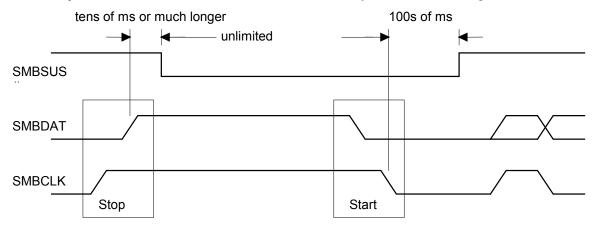

#### 5.6.1.1. Device capabilities field

The Device Capabilities field serves multiple purposes:

1. Reports generic SMBus capabilities.

- 2. Guarantees order of ARP resolution. Because a 'zero' bit wins arbitration over a '1' bit, and the Address Type bits are the first two bits presented when a device presents its UDID, all fixed address devices on the bus are detected during ARP first, followed by devices with dynamic and persistent addresses, and so on. The bits in the brackets below show the highest two bits, the address type field, within the Device Capabilities field:

- [00] Fixed Address devices are identified first.

- [01] Dynamic and Persistent Address devices are identified next.

- [10] Dynamic and Volatile Address devices are identified next.

- [11] Random Number devices are identified last.

| 7     | 6       | 5            | 4            | 3            | 2            | 1            | 0                |

|-------|---------|--------------|--------------|--------------|--------------|--------------|------------------|

| Addre | ss Type | Reserved (0) | PEC<br>Supported |