# Verilog Coding for Logic Synthesis

Weng Fook Lee

Verilog Coding for Logic Synthesis

## Verilog Coding for Logic Synthesis

WENG FOOK LEE

Copyright © 2003 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400, fax 978-750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, e-mail: permreq@wiley.com.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services please contact our Customer Care Department within the U.S. at 877-762-2974, outside the U.S. at 317-572-3993 or fax 317-572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print, however, may not be available in electronic format.

#### Library of Congress Cataloging-in-Publication Data:

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

Dedicated to my mother for all her sacrifices.

### Contents

| Та              | ble o            | f Figures                                         | xi    |

|-----------------|------------------|---------------------------------------------------|-------|

| Та              | able of Examples |                                                   | xvii  |

| Lis             | List of Tables   |                                                   | xxi   |

| Pr              | eface            |                                                   | xxiii |

| Acknowledgments |                  |                                                   |       |

| AC              | KHOW             | heugments                                         | XXV   |

| Tra             | adem             | arks                                              | xxvi  |

| 1               | Intro            | oduction                                          | 1     |

| 2               | Asic             | Design Flow                                       | 3     |

|                 | 2.1              | Specification                                     | 3     |

|                 | 2.2              | RTL Coding                                        | 5     |

|                 |                  | 2.2.1 Types of Verilog Code: RTL, Behavioral, and |       |

|                 |                  | Structural                                        | 6     |

|                 | 2.3              | Test Bench and Simulation                         | 6     |

|                 | 2.4              | Synthesis                                         | 9     |

|                 | 2.5              | Prelayout Timing Analysis                         | 10    |

|                 | 2.6              | APR                                               | 11    |

|                 | 2.7              | Back Annotation                                   | 12    |

|                 | 2.8              | Post layout Timing Analysis                       | 13    |

|                 | 2.9              | Logic Verification                                | 14    |

| 3               | Veri             | log Coding                                        | 16    |

|                 | 3.1              | Introduction to Basic Verilog Concepts            | 16    |

|                 |                  | 3.1.1 Verilog Syntax                              | 16    |

|                 |                  |                                                   | vii   |

|   |      | 3.1.2 Comments                                                              | 17         |

|---|------|-----------------------------------------------------------------------------|------------|

|   |      | 3.1.3 Numbers                                                               | 17         |

|   |      | 3.1.4 Verilog Data Type                                                     | 19         |

|   |      | 3.1.5 Signal Strength                                                       | 25         |

|   | 3.2  | 0                                                                           | 27         |

|   | 3.3  |                                                                             | 34         |

|   |      | 3.3.1 Combinational UDP                                                     | 35         |

|   |      | 3.3.2 Sequential UDP                                                        | 37         |

|   | 3.4  | Concurrent and Sequential Statements                                        | 40         |

| 4 | Cod  | ing Style: Best-Known Method for Synthesis                                  | 41         |

|   | 4.1  | Naming Convention                                                           | 41         |

|   | 4.2  | Design Partitioning                                                         | 43         |

|   | 4.3  | Clock                                                                       | 44         |

|   |      | 4.3.1 Internally Generated Clock                                            | 46         |

|   |      | 4.3.2 Gated Clock                                                           | 47         |

|   | 4.4  | Reset                                                                       | 51         |

|   |      | 4.4.1 Asynchronous Reset                                                    | 51         |

|   |      | 4.4.2 Synchronous Reset                                                     | 52         |

|   | 4.5  | Timing Loop                                                                 | 53         |

|   | 4.6  |                                                                             | 54         |

|   | 4.7  | Sensitivity List                                                            | 66         |

|   | 4.8  | Verilog Operators                                                           | 68         |

|   |      | 4.8.1 Conditional Operators                                                 | 68         |

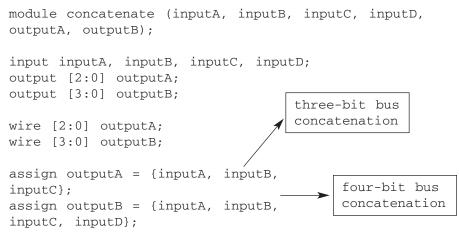

|   |      | 4.8.2 Bus Concatenation Operator                                            | 69         |

|   |      | 4.8.3 Shift Operator                                                        | 71         |

|   |      | 4.8.4 Arithmetic Operator                                                   | 78         |

|   |      | 4.8.5 Division Operator                                                     | 85         |

|   |      | 4.8.6 Modulus Operator                                                      | 92         |

|   |      | 4.8.7 Logical Operator                                                      | 100        |

|   |      | 4.8.8 Bitwise Operator                                                      | 105        |

|   |      | <ul><li>4.8.9 Equality Operator</li><li>4.8.10 Reduction Operator</li></ul> | 112<br>115 |

|   |      | 4.8.11 Relational Operator                                                  | 115        |

|   | 4.9  | Latch Inference                                                             | 117        |

|   |      | Memory Array                                                                | 121        |

|   |      | State Machine Design                                                        | 132        |

|   | 1.11 | 4.11.1 Intelligent Traffic Control System                                   | 132        |

| F | Dec  | ign Example of Programmable Timer                                           | 151        |

| 5 |      | ign Example of Programmable Timer                                           | 151        |

|   | 5.1  | Programmable Timer Design Specification                                     | 151        |

|   | 5.2  | Microarchitecture Definition for Programmable Timer                         | 153        |

|   | 5.3  | Flow 1 | Diagram Definition for Programmable Timer                                                                 | 155 |

|---|------|--------|-----------------------------------------------------------------------------------------------------------|-----|

|   | 5.4  | Verilo | g Code for Programmable Timer                                                                             | 161 |

|   | 5.5  | Synthe | esizable Verilog Code for Programmable Timer                                                              | 175 |

| 6 |      |        | mple of Programmable Logic Block for Peripheral                                                           |     |

|   | Inte | rface  |                                                                                                           | 181 |

|   | 6.1  | Progra | ammable Logic Block for Peripheral Interface                                                              |     |

|   |      |        | n Specification                                                                                           | 182 |

|   | 6.2  | Mode   | of Operation for Programmable Logic Block for                                                             |     |

|   |      | Periph | neral Interface                                                                                           | 185 |

|   |      | 6.2.1  | Mode 0 Operation                                                                                          | 185 |

|   |      |        | Mode 1 Operation                                                                                          | 187 |

|   |      |        | Mode 2 Operation                                                                                          | 188 |

|   | 6.3  | Micro  | architecture Definition for Programmable Peripheral                                                       |     |

|   |      | Interf |                                                                                                           | 189 |

|   | 6.4  | Flow 1 | Diagram Definition for Programmable Peripheral                                                            |     |

|   |      | Interf | ace                                                                                                       | 191 |

|   | 6.5  | Synthe | esizable Verilog Code for Programmable Peripheral                                                         |     |

|   |      | Interf | ace                                                                                                       | 213 |

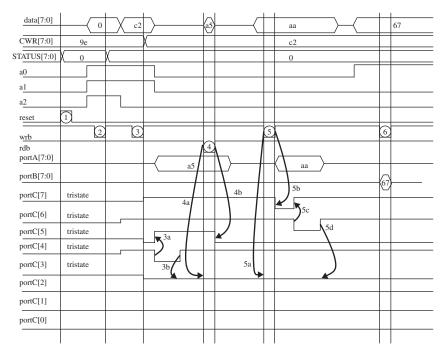

|   | 6.6  | Simula | ation for Programmable Peripheral Interface Design                                                        | 234 |

|   |      | 6.6.1  | Simulation for Mode 0 Operation with <i>PortA</i> , <i>PortB</i> ,                                        |     |

|   |      |        | and <i>PortC</i> as input and Output                                                                      | 235 |

|   |      | 6.6.2  | Simulation for Mode 0 Operation with <i>PortA</i> , <i>PortB</i> ,                                        |     |

|   |      |        | and <i>PortC</i> Lower as Input and <i>PortC</i> Upper as                                                 |     |

|   |      |        | Output                                                                                                    | 240 |

|   |      | 6.6.3  | Simulation for Mode 0 Operation with <i>PortA</i> , <i>PortB</i> ,                                        |     |

|   |      |        | and <i>PortC</i> Upper as Input and <i>PortC</i> Lower as Output                                          | 245 |

|   |      | 6.6.4  | Simulation for Writing and Reading Data from                                                              |     |

|   |      |        | STATUS and CWR Register                                                                                   | 249 |

|   |      | 6.6.5  | Simulation for Mode 1 Operation with <i>PortA</i> and                                                     |     |

|   |      |        | PortB as Strobed Input                                                                                    | 253 |

|   |      | 6.6.6  | Simulation for Mode 1 Operation with <i>PortA</i> as                                                      | 057 |

|   |      | ((7    | Strobed Input and <i>PortB</i> as Strobed Output                                                          | 257 |

|   |      | 6.6.7  | Simulation for Mode 1 Operation with <i>PortA</i> as                                                      | 262 |

|   |      | 6.6.8  | Strobed Output and <i>PortB</i> as Strobed Input<br>Simulation for Mode 1 Operation with <b>PortA</b> and | 262 |

|   |      | 0.0.0  | Simulation for Mode 1 Operation with <i>PortA</i> and <i>PortB</i> as Strobed Output                      | 267 |

|   |      | 6.6.9  | Simulation for Mode 2 Operation with <i>PortA</i> as                                                      | 207 |

|   |      | 0.0.9  | Strobed I/O and <i>PortB</i> as Input                                                                     | 272 |

|   |      | 6610   | Simulation for Mode 2 Operation with <i>PortA</i> as                                                      | 212 |

|   |      | 0.0.10 | Strobed I/O and <i>PortB</i> as Output                                                                    | 277 |

|   |      | 6.6.11 | Simulation for Mode 1 Operation with <i>PortA</i> and                                                     | 2,7 |

|   |      |        | <b>PortB</b> as Strobed Input and <b>STATUS</b> Register                                                  |     |

|   |      |        | Disabled                                                                                                  | 282 |

### **x** CONTENTS

| 6.6.12 Simulation for Mode 2 Operation with <i>PortA</i> as Strobed I/O and <i>PortB</i> as Output and <i>STATUS</i> |            |

|----------------------------------------------------------------------------------------------------------------------|------------|

| Register Disabled                                                                                                    | 287        |

| Appendix                                                                                                             | 293        |

| Appendix A.1. two-bit by two-bit adder<br>Appendix A.2. two-bit by two-bit subtractor                                | 293<br>295 |

| Appendix A.3. four-bit by four-bit multiplier                                                                        | 293        |

| Glossary                                                                                                             | 305        |

| Bibliography                                                                                                         | 307        |

| Index                                                                                                                | 308        |

### **Table of Figures**

| Figure 2.1  | Diagram Showing an ASIC Design Flow                | 4  |

|-------------|----------------------------------------------------|----|

| Figure 2.2  | Diagram Indicating Step 1 of an ASIC Design Flow:  |    |

|             | Specification                                      | 4  |

| Figure 2.3  | Diagram Showing the Definition of Architecture and |    |

|             | Micro Architecture                                 | 5  |

| Figure 2.4  | Diagram Indicating Step 2 of an ASIC Design Flow:  |    |

|             | RTL Coding                                         | 6  |

| Figure 2.5  | Diagram Indicating Step 3 of an ASIC Design Flow:  |    |

|             | Testbench and Simulation                           | 8  |

| Figure 2.6  | Diagram Indicating Step 4 of an ASIC Design Flow:  |    |

|             | Synthesis                                          | 9  |

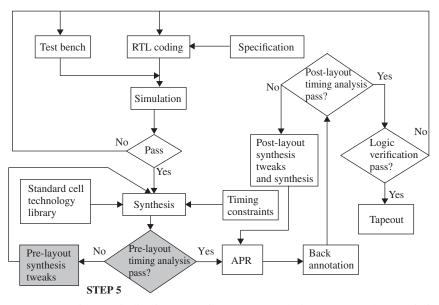

| Figure 2.7  | Diagram Indicating Step 5 of an ASIC Design Flow:  |    |

|             | Pre Layout Timing Analysis                         | 11 |

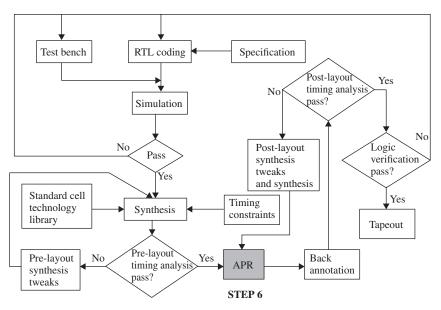

| Figure 2.8  | Diagram Indicating Step 6 of an ASIC Design Flow:  |    |

|             | Auto Place & Route (APR)                           | 12 |

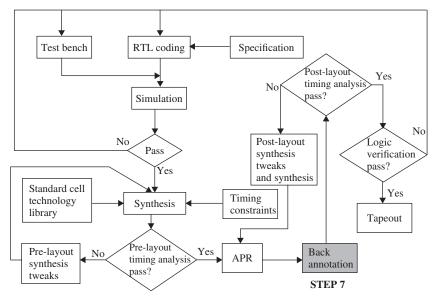

| Figure 2.9  | Diagram Indicating Step 7 of an ASIC Design Flow:  |    |

|             | Back Annotation                                    | 13 |

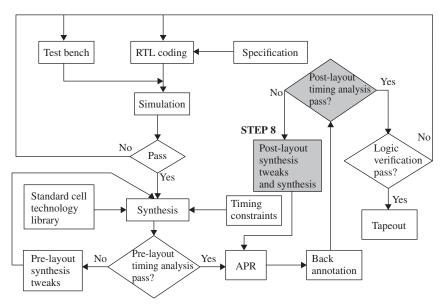

| Figure 2.10 | Diagram Indicating Step 8 of an ASIC Design Flow:  |    |

|             | Post Layout Timing Analysis                        | 14 |

| Figure 2.11 | Diagram Indicating Step 9 of an ASIC Design Flow:  |    |

|             | Logic Verification                                 | 15 |

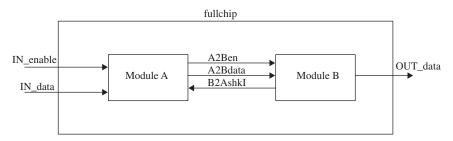

| Figure 4.1  | Diagram Showing Two Sub-modules Connected on a     |    |

|             | Fullchip Level                                     | 42 |

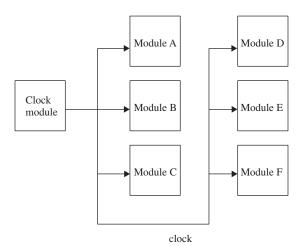

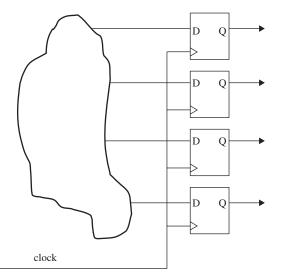

| Figure 4.2  | Diagram Showing a Fullchip Level of Global Clock   |    |

|             | Interconnect                                       | 44 |

| Figure 4.3  | Diagram Showing Ideal Connectivity of Clock Signal |    |

|             | in a Design                                        | 45 |

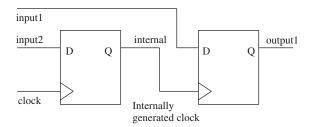

| Figure 4.4  | Diagram Showing an Output Flip-flop Driving        |    |

|             | Another Flip-flop                                  | 46 |

|             |                                                    |    |

xi

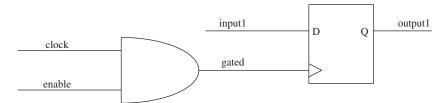

| Figure 4.5  | Diagram Showing a Gated Clock Driving a Flip-flop        | 47  |

|-------------|----------------------------------------------------------|-----|

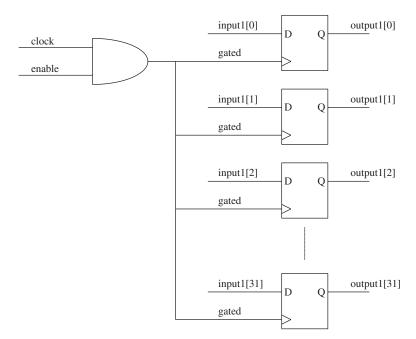

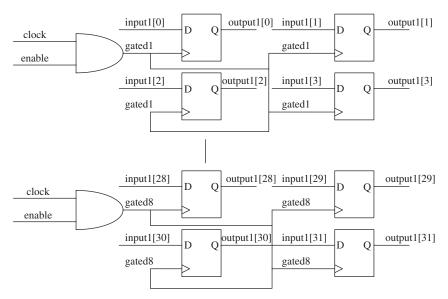

| Figure 4.6  | Diagram Showing Signal Gated Driving Clock of 32         |     |

|             | Flip-flops                                               | 49  |

| Figure 4.7  | Diagram Showing Multiple <i>Gated</i> Signal to Drive 32 |     |

|             | Flip-flops                                               | 49  |

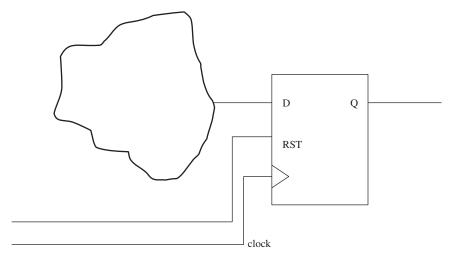

| Figure 4.8  | Diagram Showing a Design with an Asynchronous            |     |

|             | Reset Flip-flop                                          | 52  |

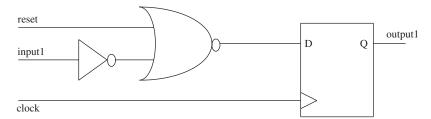

| Figure 4.9  | Diagram Showing a Design with a Synchronous Reset        |     |

|             | Flip-flop                                                | 53  |

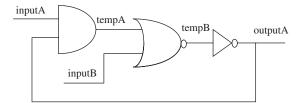

| Figure 4.10 | Diagram Showing a Design with Timing Loop                | 54  |

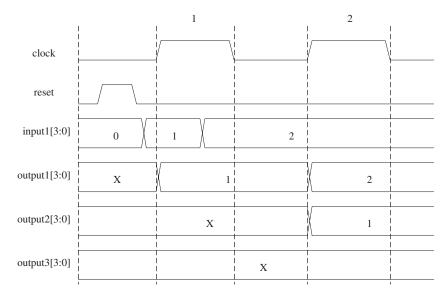

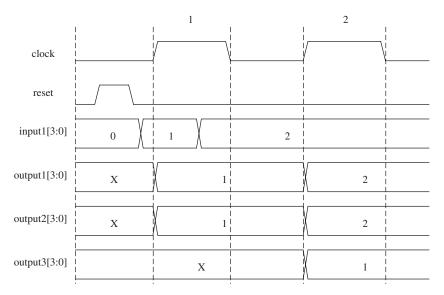

| Figure 4.11 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.8                                           | 58  |

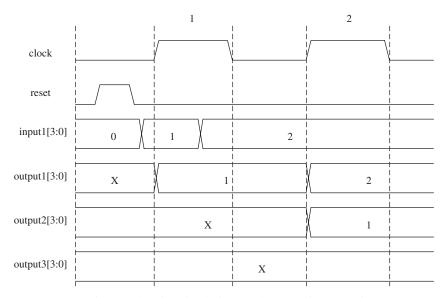

| Figure 4.12 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.9                                           | 58  |

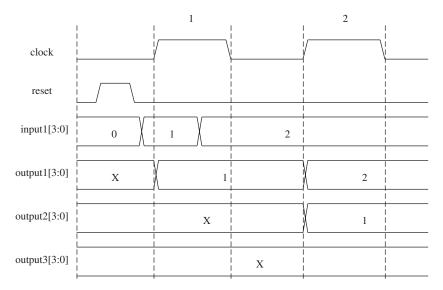

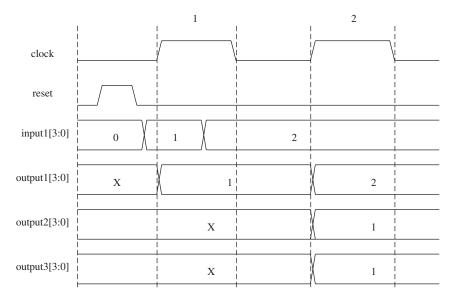

| Figure 4.13 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.10                                          | 59  |

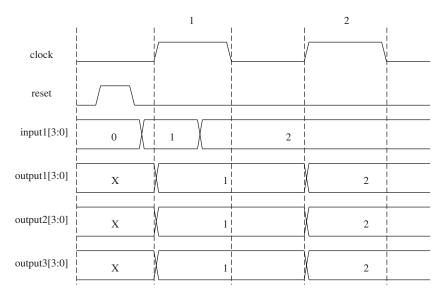

| Figure 4.14 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.12                                          | 59  |

| Figure 4.15 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.13                                          | 63  |

| Figure 4.16 | Diagram Showing Simulation Results of Verilog Code       |     |

|             | in Example 4.14                                          | 64  |

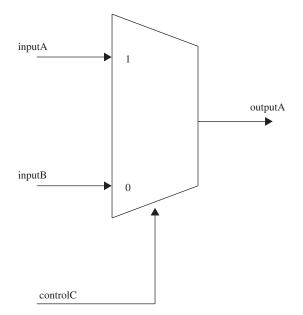

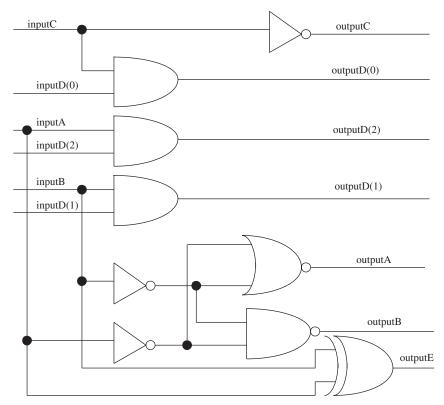

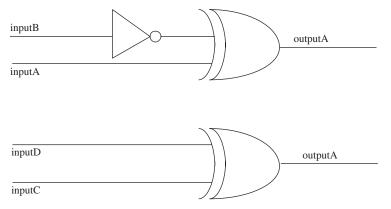

| Figure 4.17 | Diagram Showing Synthesized Logic for Module             |     |

|             | "conditional"                                            | 70  |

| Figure 4.18 | Diagram Showing Synthesized Logic for Module             |     |

|             | "shift_left"                                             | 72  |

| Figure 4.19 | Diagram Showing Synthesized Logic for Module             |     |

|             | "shift_right"                                            | 75  |

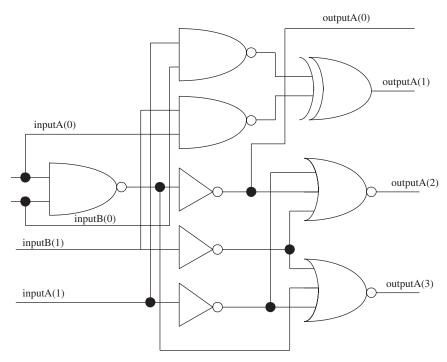

| Figure 4.20 | Diagram Showing Synthesized Logic for Module             |     |

|             | "addition"                                               | 79  |

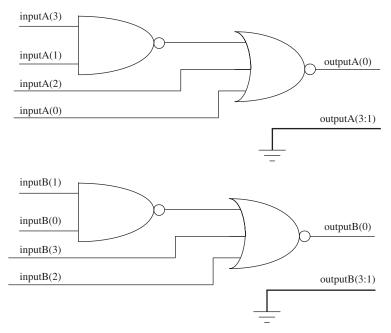

| Figure 4.21 | Diagram Showing Synthesized Logic for Module             |     |

|             | "subtraction"                                            | 81  |

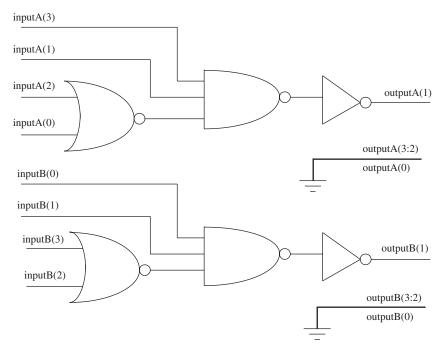

| Figure 4.22 | Diagram Showing Synthesized Logic for Module             |     |

|             | "multiplication"                                         | 83  |

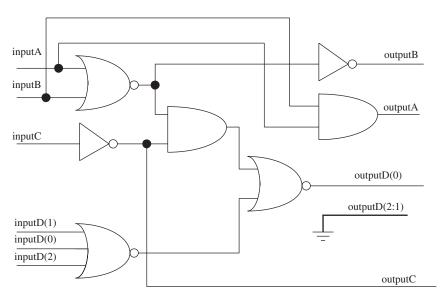

| Figure 4.23 | Diagram Showing Synthesized Logic for Design             |     |

|             | Module "division"                                        | 86  |

| Figure 4.24 | Diagram Showing Synthesized Logic for Design             |     |

|             | Module "modulus"                                         | 94  |

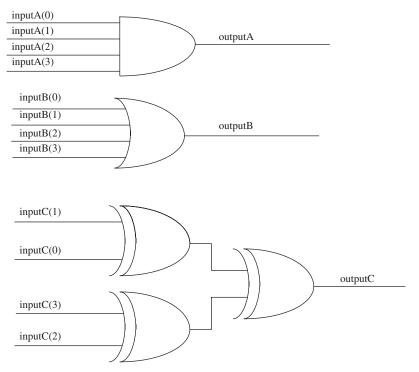

| Figure 4.25 | Diagram Showing Synthesized Logic for Verilog Code       |     |

| 0           | Module "logical"                                         | 100 |

| Figure 4.26 | Diagram Showing Synthesized Logic for Verilog Code       |     |

| 2           | Module " <i>bitwise</i> "                                | 107 |

| Figure 4.27 | Diagram Showing Synthesized Logic for Verilog Code       |     |

| -           | Module "logicequal"                                      | 113 |

| Figure 4.28 | Diagram Showing Synthesized Logic for Verilog Code<br>Module " <i>reduction</i> " | 115 |

|-------------|-----------------------------------------------------------------------------------|-----|

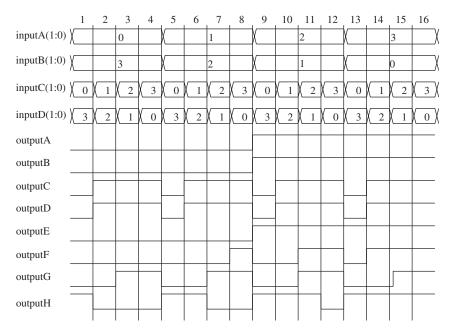

| Figure 4.29 | Diagram Showing Simulation Results of Verilog                                     | 110 |

| 8           | Testbench Module " <i>relational_tb</i> "                                         | 120 |

| Figure 4.30 | Diagram Showing Synthesized Logic for Module                                      |     |

| U           | "latch_infer"                                                                     | 122 |

| Figure 4.31 | Diagram Showing Synthesized Logic of Module                                       |     |

| U           | "latch_noninfer"                                                                  | 124 |

| Figure 4.32 | Diagram Showing Synthesized Logic for Module                                      |     |

| 0           | "case_infer"                                                                      | 125 |

| Figure 4.33 | Diagram Showing Synthesized Logic for Module                                      |     |

| 0           | "case_uninfer_diff"                                                               | 126 |

| Figure 4.34 | Diagram Showing Synthesis Representation of a One                                 |     |

| 0           | Bit Memory Cell                                                                   | 128 |

| Figure 4.35 | Diagram Showing Simulation Waveform for Verilog                                   |     |

|             | Testbench Module " <i>memory_tb</i> "                                             | 131 |

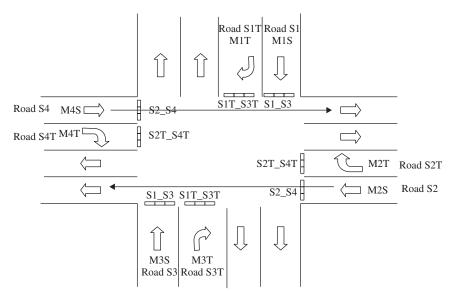

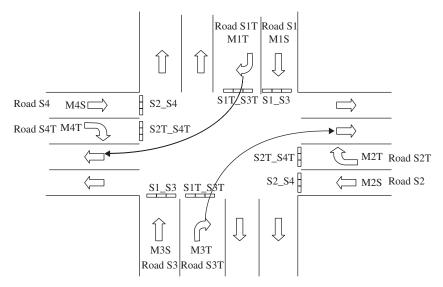

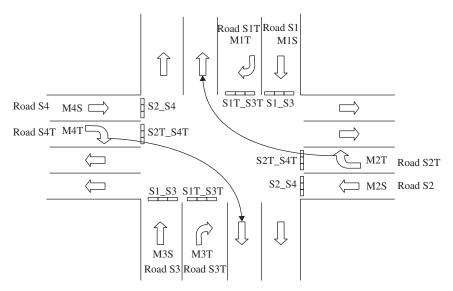

| Figure 4.36 | Diagram Showing an Interchange Junction Traffic Light                             | 133 |

| Figure 4.37 | Diagram Showing Possible Pass Scenario Whereby                                    |     |

|             | S1_S3 is GREEN                                                                    | 134 |

| Figure 4.38 | Diagram Showing Possible Pass Scenario Whereby                                    |     |

|             | S2_S4 is GREEN                                                                    | 135 |

| Figure 4.39 | Diagram Showing Possible Pass Scenario Whereby                                    |     |

|             | <i>S1T_S3T</i> is GREEN                                                           | 135 |

| Figure 4.40 | Diagram Showing Possible Pass Scenario Whereby                                    |     |

|             | S2T_S4T is GREEN                                                                  | 136 |

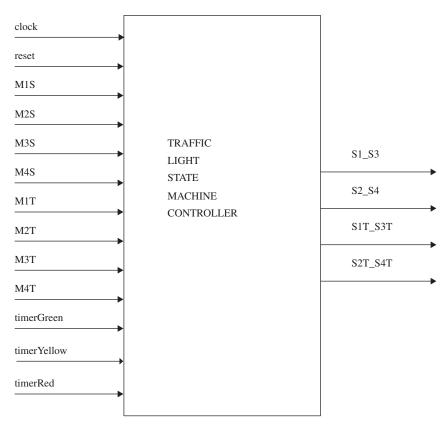

| Figure 4.41 | Diagram Showing Interface Signals for Traffic Light                               |     |

|             | Controller                                                                        | 136 |

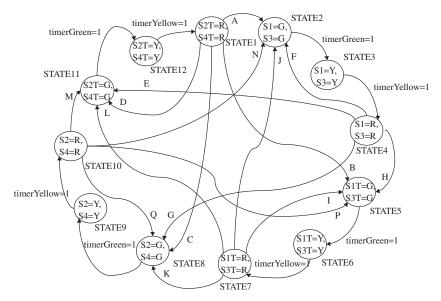

| Figure 4.42 | State Diagram for Traffic Light State Machine                                     |     |

|             | Controller                                                                        | 138 |

| Figure 4.43 | Diagram Showing Simulation Results of Testbench                                   |     |

|             | Module <i>state_machine_tb</i>                                                    | 149 |

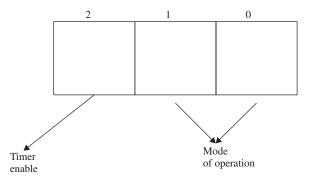

| Figure 5.1  | Diagram Showing Bits of Control Word Register                                     | 152 |

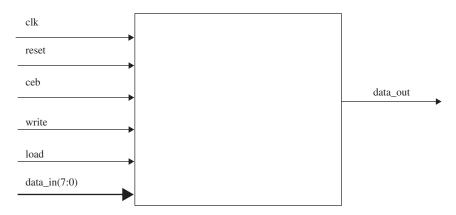

| Figure 5.2  | Diagram Showing the Interface Signals for                                         |     |

|             | Programmable Timer Design                                                         | 154 |

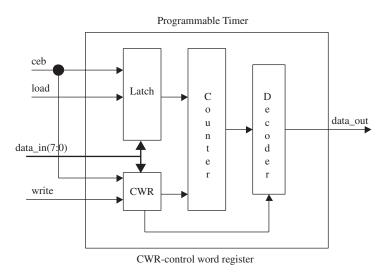

| Figure 5.3  | Micro-architectural Block Diagram of the                                          |     |

|             | Programmable Timer Design                                                         | 154 |

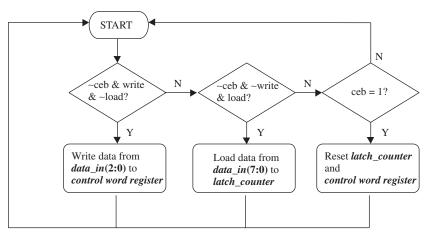

| Figure 5.4  | Flow Diagram for Loading Data Into Programmable                                   |     |

|             | Timer and Writing Data Into Control Word Register                                 | 155 |

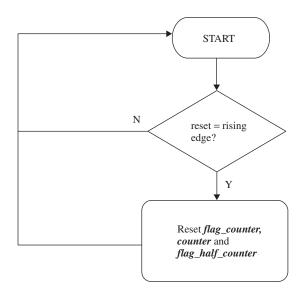

| Figure 5.5  | Flow Diagram for Reset of Programmable Timer                                      | 156 |

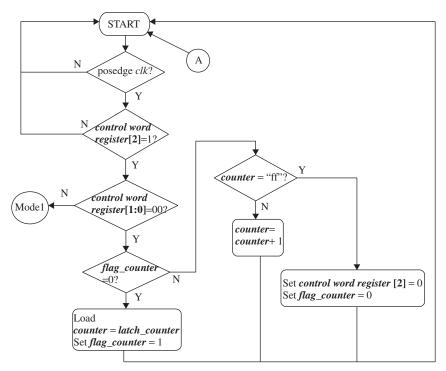

| Figure 5.6  | Flow Diagram for Mode 0 Operation                                                 | 157 |

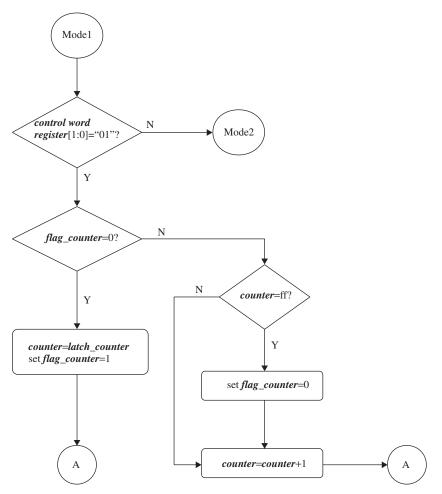

| Figure 5.7  | Flow Diagram for Mode 1 Operation                                                 | 158 |

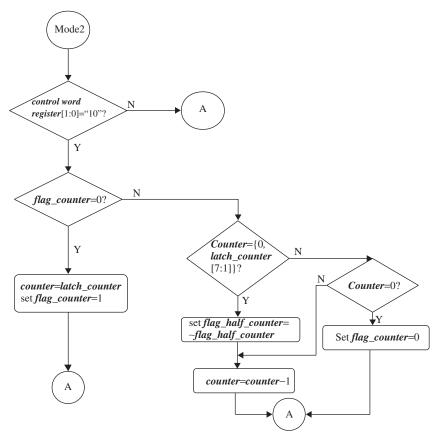

| Figure 5.8  | Flow Diagram for Mode 2 Operation                                                 | 159 |

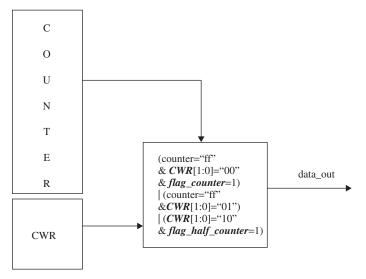

| Figure 5.9  | Diagram Showing Decoding of Control Word                                          |     |

|             | Register and Counter for Output Generation                                        | 160 |

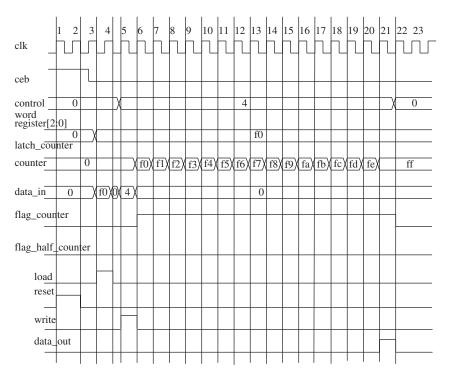

| Figure 5.10   | Diagram Showing Simulation Results of Verilog<br>Testbench for Mode 0                                                | 167 |

|---------------|----------------------------------------------------------------------------------------------------------------------|-----|

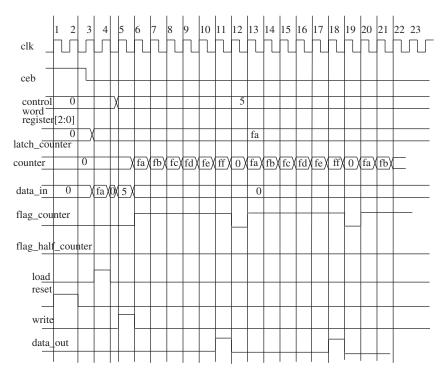

| Figure 5.11   | Diagram Showing Simulation Results of Verilog                                                                        |     |

| Figure 5.12   | Testbench for Mode 1<br>Diagram Showing Simulation Results of Verilog                                                | 170 |

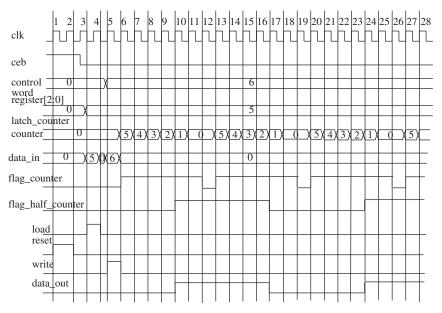

|               | Testbench for Mode 2                                                                                                 | 173 |

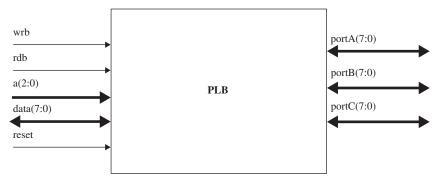

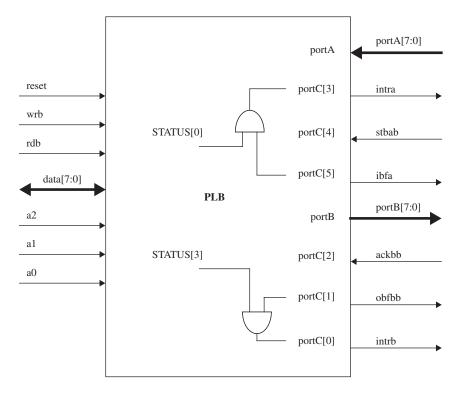

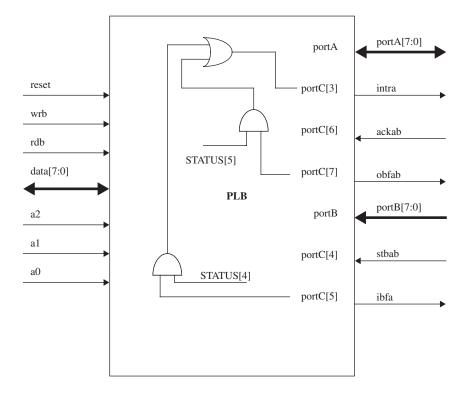

| Figure 6.1    | Diagram Showing Interface Signals of PLB                                                                             | 182 |

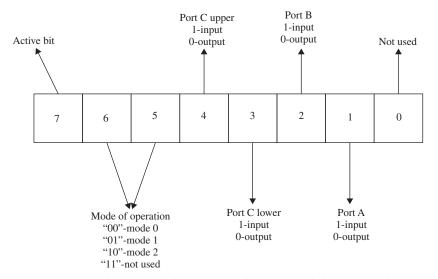

| Figure 6.2    | Diagram Showing Functionality of Each Bit in CWR<br>Register                                                         | 183 |

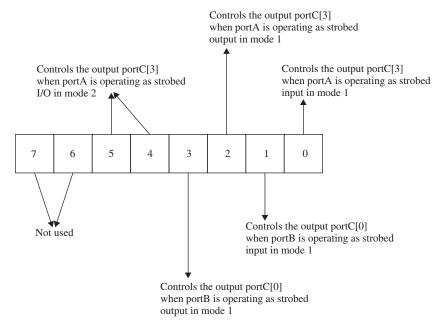

| Figure 6.3    | Diagram Showing Functionality of Each Bit in STATUS Register                                                         | 185 |

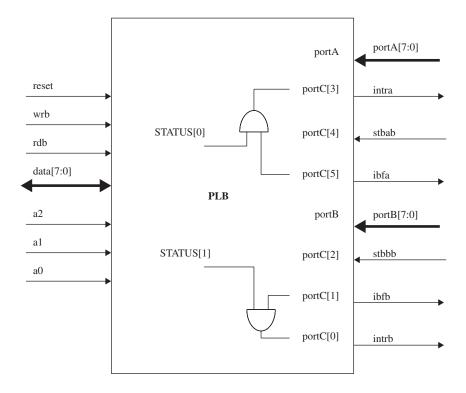

| Figure 6.4    | Diagram Showing Interface Signals in Mode 1<br>Operation with <i>PortA</i> and <i>PortB</i> as Strobed Input<br>Port | 100 |

| Figure 65     |                                                                                                                      | 188 |

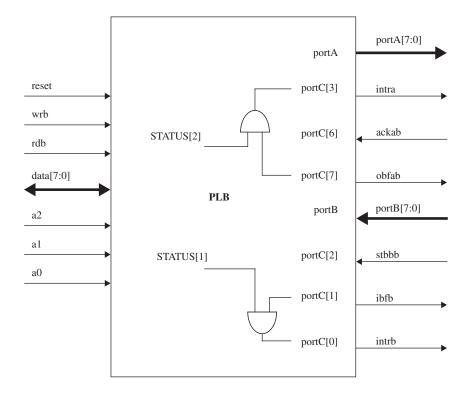

| Figure 6.5    | Diagram Showing Interface Signals in Mode 1                                                                          |     |

|               | Operation with <i>PortA</i> as Strobed Input Port and <i>PortB</i> as Strobed Output Port                            | 100 |

| E'array ( (   | PortB as Strobed Output Port                                                                                         | 189 |

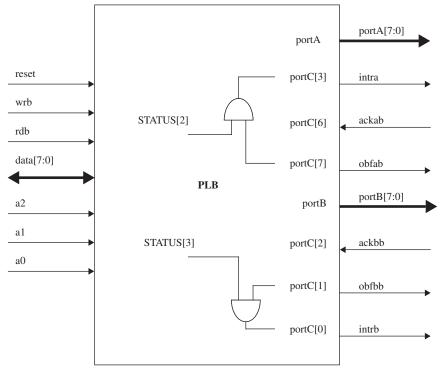

| Figure 6.6    | Diagram Showing Interface Signals in Mode 1                                                                          |     |

|               | Operation with <i>PortA</i> as Strobed Output Port and                                                               | 100 |

|               | PortB as Strobed Input Port                                                                                          | 190 |

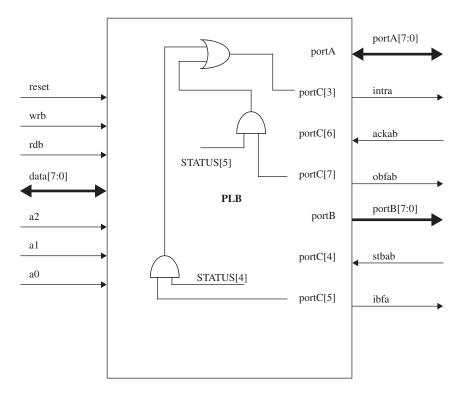

| Figure 6.7    | Diagram Showing Interface Signals in Mode 1                                                                          |     |

|               | Operation with <i>PortA</i> and <i>PortB</i> as Strobed Output Port                                                  | 191 |

| Figure 6.8    | Diagram Showing Interface Signals in Mode 2                                                                          |     |

|               | Operation with <i>PortA</i> as Strobed IO and <i>PortB</i> as Output Port                                            | 192 |

| Figure 6.9    | Diagram Showing Interface Signals in Mode 2                                                                          |     |

| C             | Operation with <i>PortA</i> as Strobed IO and <i>PortB</i> as                                                        |     |

|               | Input Port                                                                                                           | 193 |

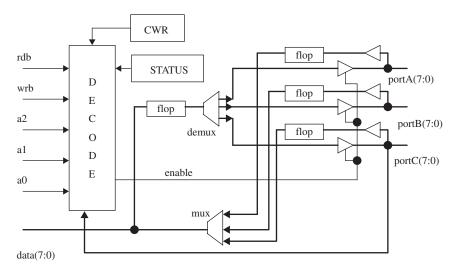

| Figure 6.10   | Micro-architectural Block Diagram of the                                                                             |     |

| 1.8410 0110   | Programmable Peripheral Interface Design                                                                             | 193 |

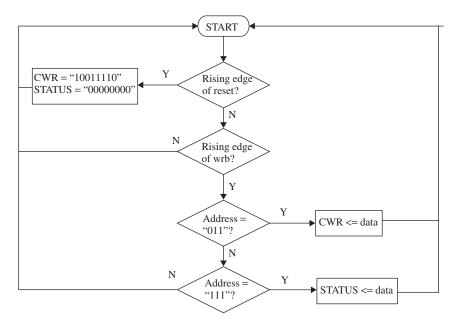

| Figure 6.11   | Flow Diagram for Writing Data to CWR Register and                                                                    | 175 |

| 1 iguie 0.11  | STATUS Register                                                                                                      | 194 |

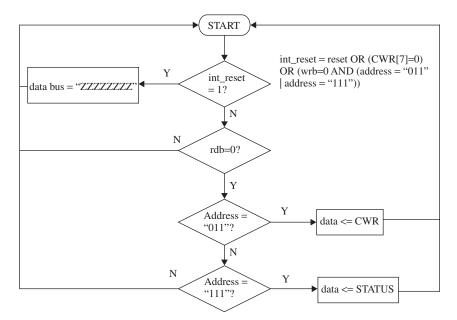

| Figure 6.12   | Flow Diagram for Reading Contents of <i>CWR</i> Register<br>and <i>STATUS</i> Register                               | 194 |

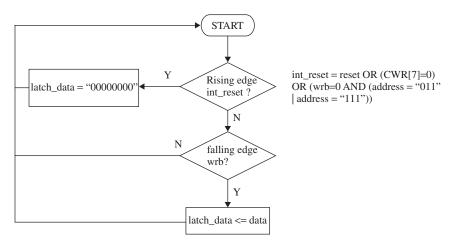

| Figure 6.13   | Flow Diagram for Latching Data From <i>data</i> Bus Onto                                                             | 175 |

| i iguie 0.15  | latch_data Bus                                                                                                       | 195 |

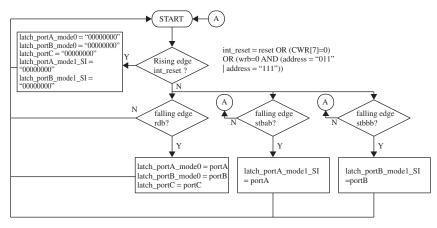

| Figure 6.14   | Flow Diagram for Latching Data From <i>portA</i> , <i>portB</i>                                                      | 195 |

| Figure 0.14   |                                                                                                                      | 106 |

| <b>D'</b> (15 | and <i>portC</i>                                                                                                     | 196 |

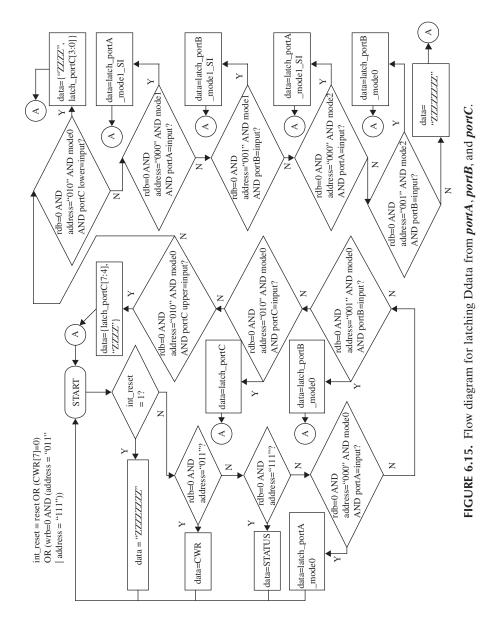

| Figure 6.15   | Flow Diagram for Latching Data From <i>portA</i> , <i>portB</i>                                                      | 407 |

|               | and <i>portC</i>                                                                                                     | 197 |

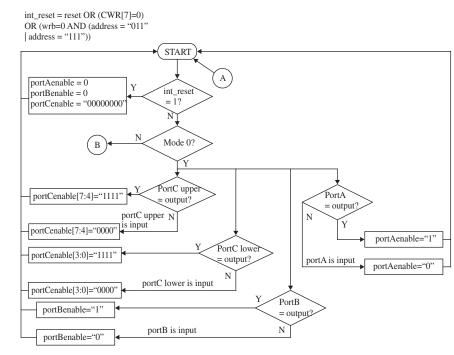

| Figure 6.16   | Flow Diagram to Generate the Enable Signals for                                                                      |     |

|               | PortA, PortB and PortC in Mode0                                                                                      | 199 |

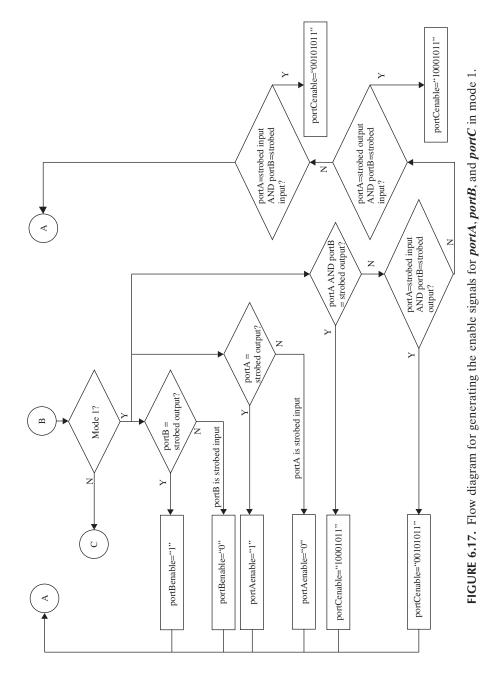

| Figure 6.17   | Flow Diagram to Generate the Enable Signals for                                                                      |     |

|               | PortA, PortB and PortC in Mode 1                                                                                     | 201 |

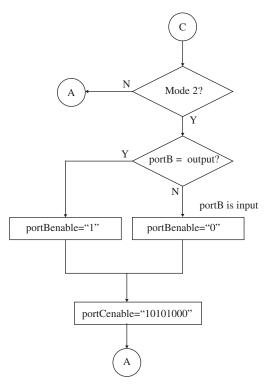

| Figure 6.18 | Flow Diagram to Generate the Enable Signals for         |     |

|-------------|---------------------------------------------------------|-----|

| C           | PortA, PortB and PortC in Mode 2                        | 202 |

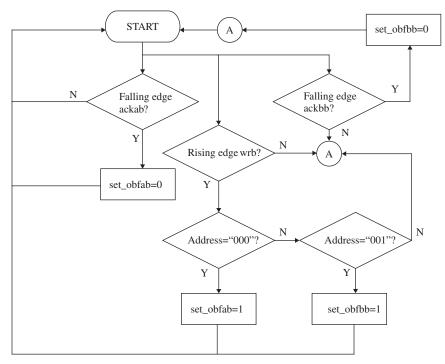

| Figure 6.19 | Diagram Showing Generation of set_obfab and             |     |

| C           | set_obfbb Logic                                         | 203 |

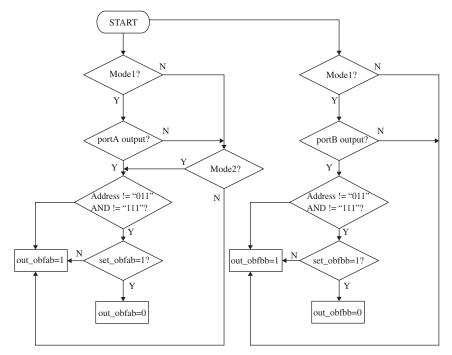

| Figure 6.20 | Diagram Showing Generation of <i>out_obfab</i> and      |     |

| -           | out_obfbb Logic                                         | 204 |

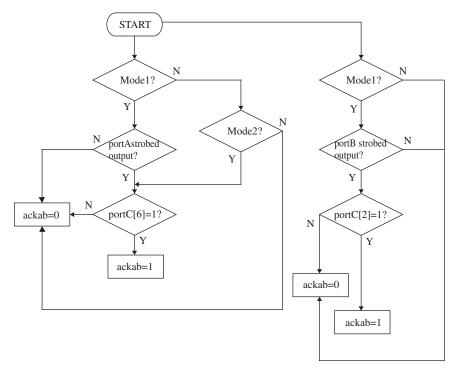

| Figure 6.21 | Diagram Showing Generation of ackab and ackbb           |     |

| C           | Logic                                                   | 205 |

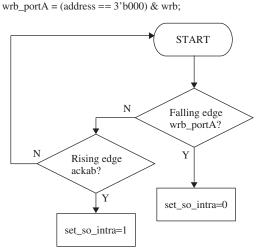

| Figure 6.22 | Diagram Showing Generation of <i>set_so_intra</i> Logic | 206 |

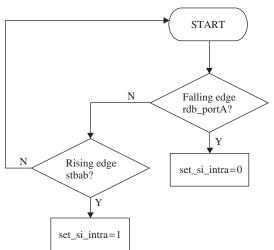

| Figure 6.23 | Diagram Showing Generation of <i>set_si_intra</i> Logic | 207 |

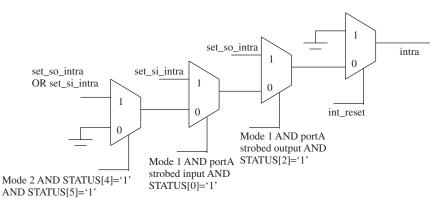

| Figure 6.24 | Diagram Showing Generation of intra Logic               | 207 |

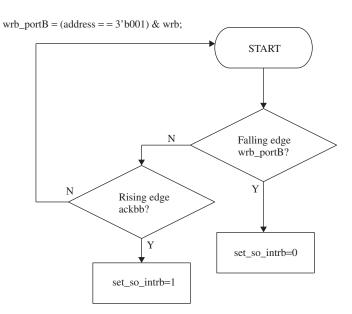

| Figure 6.25 | Diagram Showing Generation of set_so_intrb Logic        | 208 |

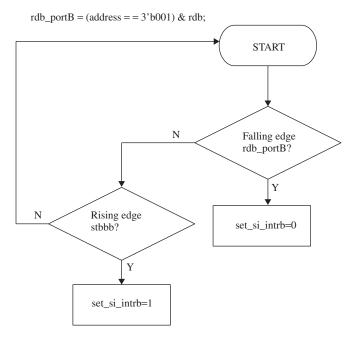

| Figure 6.26 | Diagram Showing Generation of <i>set_si_intrb</i> Logic | 209 |

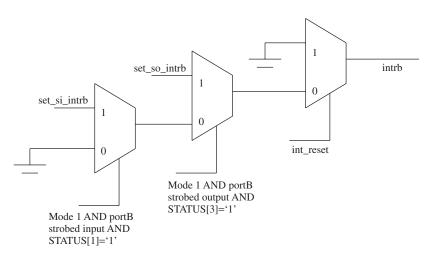

| Figure 6.27 | Diagram Showing Generation of intrb Logic               | 209 |

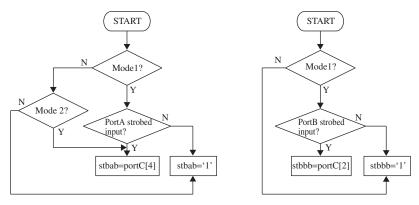

| Figure 6.28 | Diagram Showing Generation of stbab and stbbb           |     |

| -           | Logic                                                   | 210 |

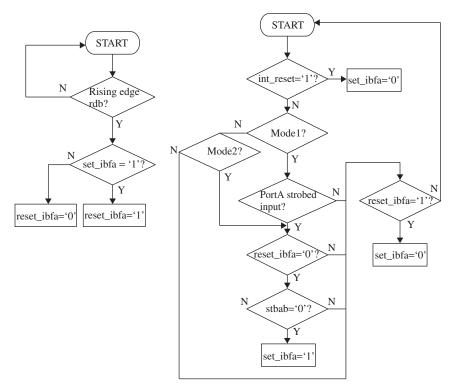

| Figure 6.29 | Diagram Showing Generation of <i>set_ibfa</i> and       |     |

| C           | reset_ibfa Logic                                        | 211 |

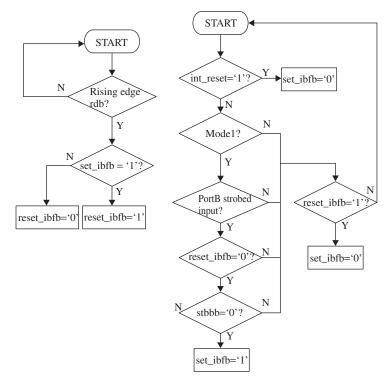

| Figure 6.30 | Diagram Showing Generation of <i>set_ibfb</i> and       |     |

| C           | reset_ibfb Logic                                        | 212 |

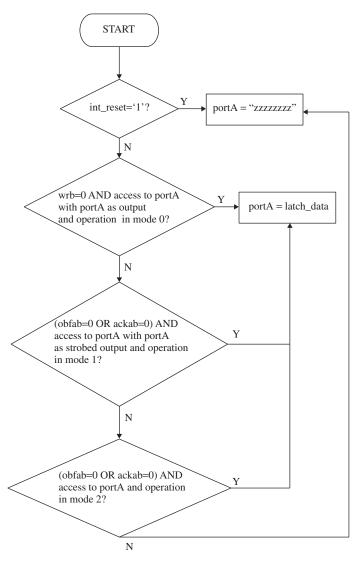

| Figure 6.31 | Diagram Showing Multiplexing of Signals to PortA        | 213 |

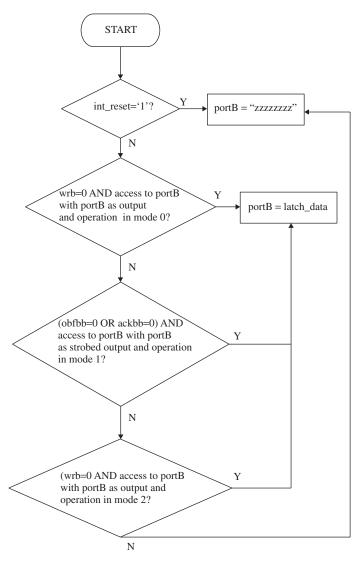

| Figure 6.32 | Diagram Showing Multiplexing of Signals to PortB        | 214 |

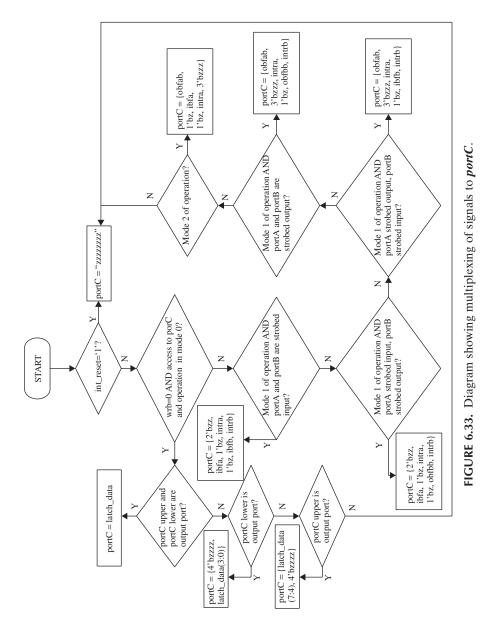

| Figure 6.33 | Diagram Showing Multiplexing of Signals to PortC        | 215 |

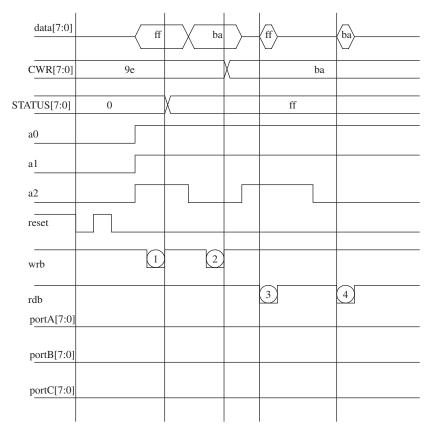

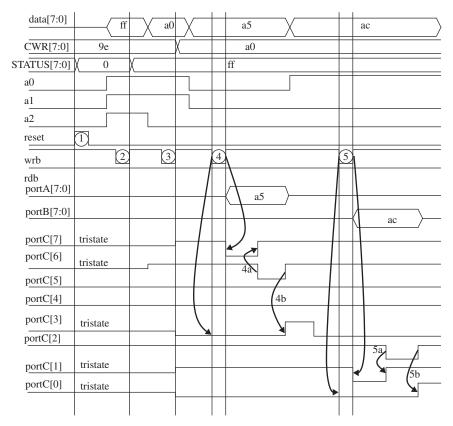

| Figure 6.34 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.2                                             | 239 |

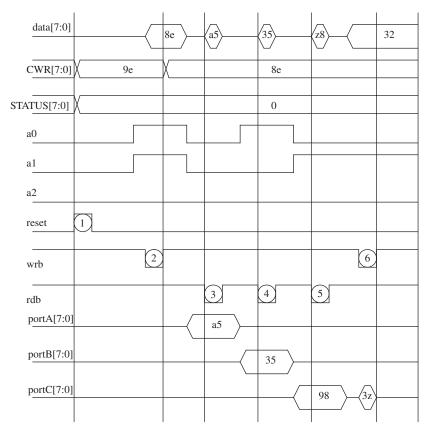

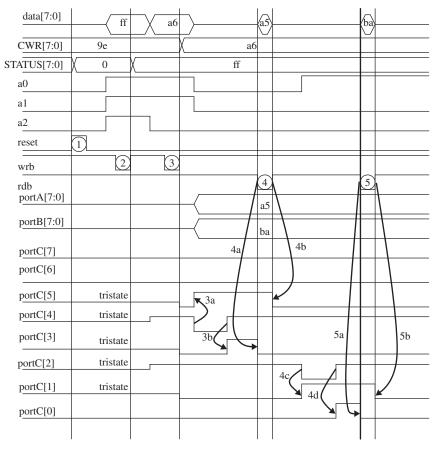

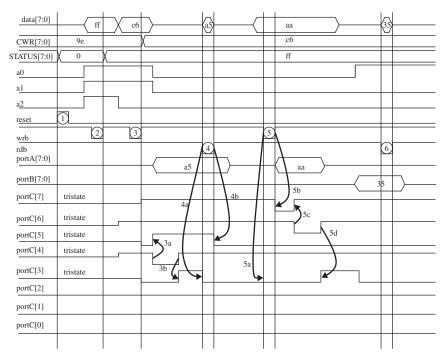

| Figure 6.35 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.3                                             | 244 |

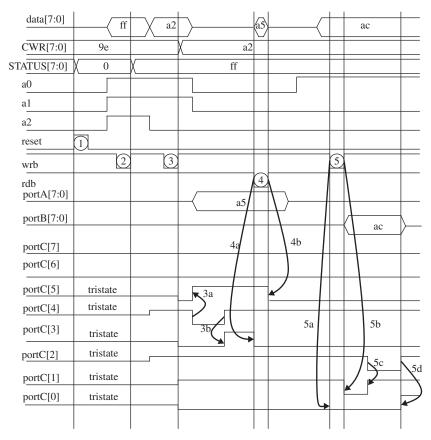

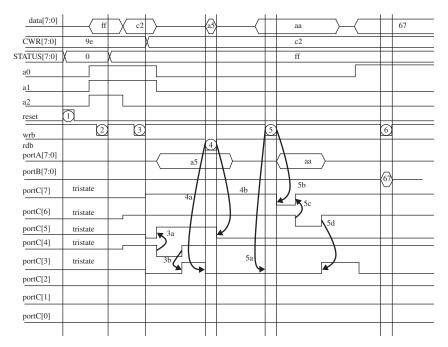

| Figure 6.36 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.4                                             | 248 |

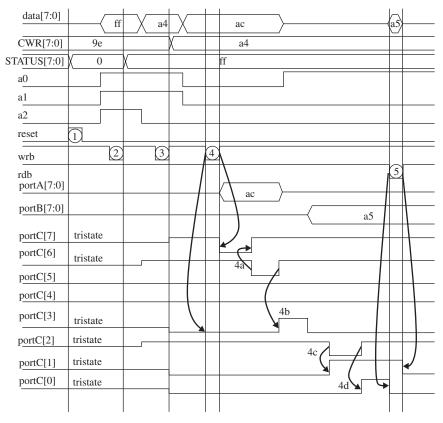

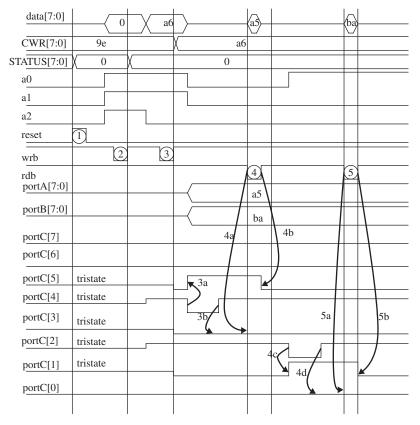

| Figure 6.37 | Diagram Showing Simulation Results of Testbench         |     |

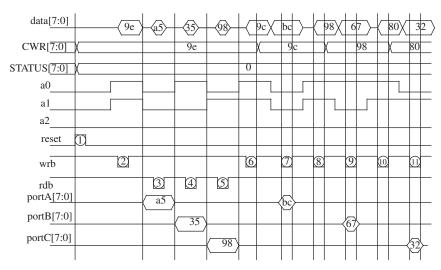

|             | Example 6.5                                             | 252 |

| Figure 6.38 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.6                                             | 256 |

| Figure 6.39 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.7                                             | 261 |

| Figure 6.40 |                                                         |     |

|             | Example 6.8                                             | 266 |

| Figure 6.41 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.9                                             | 271 |

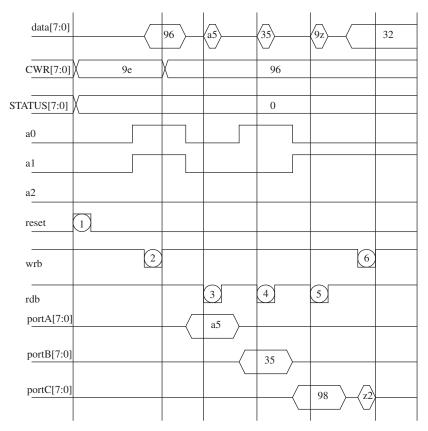

| Figure 6.42 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.10                                            | 276 |

| Figure 6.43 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.11                                            | 281 |

| Figure 6.44 | Diagram Showing Simulation Results of Testbench         |     |

|             | Example 6.12                                            | 286 |

#### xvi TABLE OF FIGURES

| Diagram Showing Simulation Results of Testbench     |                                                                                                                       |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Example 6.13                                        | 291                                                                                                                   |

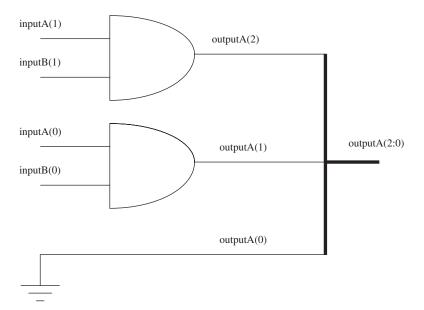

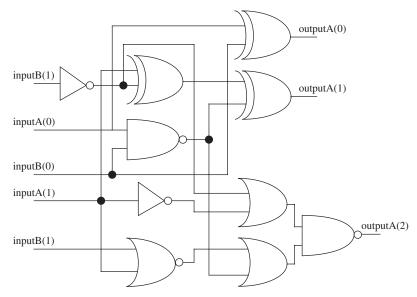

| Synthesized logic for the 2 bit by 2 bit adder      | 294                                                                                                                   |

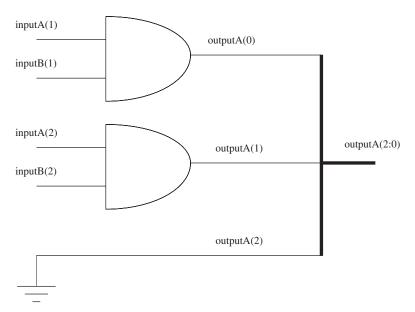

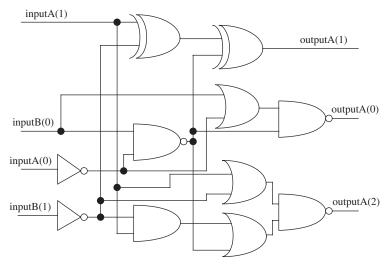

| Synthesized logic for the 2 bit by 2 bit subtractor | 296                                                                                                                   |

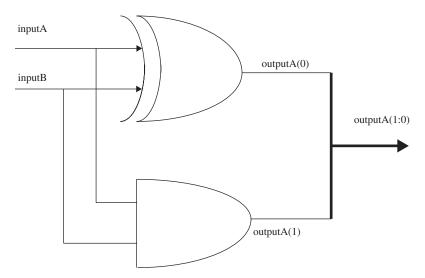

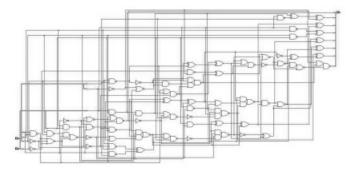

| Synthesized logic for the 4 bit by 4 bit multiplier | 298                                                                                                                   |

|                                                     | Example 6.13<br>Synthesized logic for the 2 bit by 2 bit adder<br>Synthesized logic for the 2 bit by 2 bit subtractor |

### **Table Of Examples**

| Example 3.1:  | Verilog Code Using Wire Declaration                | 19 |

|---------------|----------------------------------------------------|----|

| Example 3.2:  | Verilog Code Using Wire Declaration for a 4 Bit    |    |

| -             | Bus                                                | 20 |

| Example 3.3:  | Verilog Code Using Reg Declaration                 | 20 |

| Example 3.4:  | Verilog Code Using Reg Declaration for a 8 Bit Bus | 21 |

| Example 3.5:  | Verilog Code Showing a Tri Declaration             | 22 |

| Example 3.6:  | Verilog Code Using Strength Assignment             | 27 |

| Example 3.7:  | Example Showing Syntax Defining a UDP              | 35 |

| Example 3.8:  | Verilog Example for Defining a UDP Primitive and   |    |

| -             | Instantiating the Primitive                        | 35 |

| Example 3.9:  | Verilog Example for Defining a Sequential UDP      |    |

|               | Primitive and Instantiating the Primitive          | 37 |

| Example 3.10: | Verilog Example for Defining a Positive Edge       |    |

|               | Sequential UDP Primitive and Instantiating the     |    |

|               | Primitive                                          | 38 |

| Example 4.1:  | Verilog Example of Module A, Module B and          |    |

|               | Fullchip Interconnect                              | 43 |

| Example 4.2:  | Verilog Code for the Design of Figure 4.4          | 46 |

| Example 4.3:  | Verilog Code for Gated Clock Design Using          |    |

|               | BOOLEAN Assignment                                 | 47 |

| Example 4.4:  | Verilog Code for Gated Clock Design Using Gate     |    |

|               | Instantiation                                      | 48 |

| Example 4.5:  | Verilog Code for Gated Clock Design Using Gate     |    |

|               | Instantiation to Drive 32 Flip-flops               | 50 |

| Example 4.6:  | Verilog Code for an Asynchronous Reset Design      | 52 |

| Example 4.7:  | Verilog Code for a Synchronous Reset Design        | 53 |

| Example 4.8:  | Verilog Code Showing Usage of Non-blocking         |    |

|               | Statement                                          | 55 |

| Example 4.9:  | Verilog Code for Example 4.8 with the Output       |    |

|               | Assignment Re-arranged                             | 55 |

|               |                                                    |    |

xvii

| Example 4.10:                  | Verilog Code for Example 4.9 with the Output<br>Assignment Re-arranged | 56  |

|--------------------------------|------------------------------------------------------------------------|-----|

| Example 4.11:                  | Verilog Code for Testbench for Simulation of                           | 50  |

| Example 4.11.                  | Examples 4.8, 4.9 and 4.10                                             | 57  |

| Example 4.12:                  | Verilog Code Showing Example 4.8 Using Blocking                        | 51  |

| Enumpro 1.12.                  | Statement                                                              | 60  |

| Example 4.13:                  | Verilog Code Showing Example 4.9 Using Blocking                        |     |

| 1                              | Statement                                                              | 61  |

| Example 4.14:                  | Verilog Code Showing Example 4.10 Using Blocking                       |     |

| -                              | Statement                                                              | 61  |

| Example 4.15:                  | Verilog Code for Testbench for Simulation of                           |     |

|                                | Examples 4.12, 4.13 and 4.14                                           | 62  |

| Example 4.16:                  | Verilog Example Showing Sensitivity List for                           |     |

|                                | "always" Block                                                         | 66  |

| Example 4.17:                  | Verilog Code for Module "conditional"                                  | 69  |

| Example 4.18:                  | Verilog Example Showing a three-Bit and four-                          |     |

|                                | Bit Bus Concatenation                                                  | 70  |

| Example 4.19:                  | Verilog Code Using the Shift Left Operator                             | 71  |

| Example 4.20:                  | Verilog Code for Testbench to Simulate Module                          |     |

| -                              | "shift_left"                                                           | 71  |

| Example 4.21:                  | Simulation Results of Testbench Module                                 | 70  |

| F 1 4 22                       | "shift_left_tb"                                                        | 73  |

| Example 4.22:                  | Verilog Code Using the Shift Right Operator                            | 75  |

| Example 4.23:                  | Verilog Code for Testbench to Simulate Module                          | 76  |

| Example 4.24:                  | "shift_right"<br>Simulation Results of Verilog Testbench Module        | /0  |

| Example 4.24.                  | "shift_right_tb"                                                       | 77  |

| Example 4.25:                  | Verilog Code Using an Addition Operator                                | 79  |

| Example 4.25:<br>Example 4.26: | Verilog Testbench to Simulate Verilog Code for                         | 17  |

| Enumpre 1120.                  | Module " <i>addition</i> "                                             | 79  |

| Example 4.27:                  | Simulation Results for Verilog Testbench Module                        |     |

| . F                            | "addition_tb"                                                          | 80  |

| Example 4.28:                  | Verilog Code Using a Subtraction Operator                              | 81  |

| Example 4.29:                  | Verilog Testbench to Simulate Verilog Code for                         |     |

| -                              | Module "subtraction"                                                   | 81  |

| Example 4.30:                  | Simulation Results for Verilog Testbench Module                        |     |

|                                | "subtraction_tb"                                                       | 82  |

| Example 4.31:                  |                                                                        | 83  |

| Example 4.32:                  | Verilog Testbench to Simulate Verilog Code for                         |     |

|                                | Module "multiplication"                                                | 84  |

| Example 4.33:                  | Simulation Results for Verilog Testbench Module                        | _   |

|                                | "multiplication_tb"                                                    | 84  |

| Example 4.34:                  | Verilog Code Using a Division Operator                                 | 85  |

| Example 4.35:                  | Verilog Testbench to Simulate Verilog Code for                         | 0.7 |

|                                | Module "division"                                                      | 86  |

| Example 4.36: | Simulation Results for Verilog Testbench Module<br>"division"                           | 87  |

|---------------|-----------------------------------------------------------------------------------------|-----|

| Example 4.37: | Verilog Code Using a Modulus Operator                                                   |     |

| Example 4.38: | Verilog Testbench to Simulate Verilog Code for                                          |     |

|               | Module "modulus"                                                                        | 93  |

| Example 4.39: | Simulation Results for Verilog Testbench Module                                         |     |

|               | "modulus"                                                                               | 95  |

| Example 4.40: | Verilog Code Using Logical Operators                                                    | 101 |

| Example 4.41: | Verilog Testbench for Simulating Module                                                 |     |

|               | "logical"                                                                               | 102 |

| Example 4.42: | Simulation Results for Verilog Testbench Module<br><i>"logical_tb"</i>                  | 102 |

| Example 4.43: | Verilog Code Using Bitwise Operators                                                    | 106 |

| Example 4.44: | Verilog Testench for Simulation of Verilog Code<br>Module " <i>bitwise</i> "            | 108 |

| Example 4.45: | Simulation Results for Verilog Testbench Modulus<br>"bitwise_tb"                        | 109 |

| Example 4.46: | Verilog Code Using Logic Equality Operators                                             | 113 |

| Example 4.47: | Verilog Testbench to Simulate Module "logicequal"                                       | 113 |

| Example 4.48: | Simulation Results of Verilog Testbench Module                                          |     |

|               | "logicequal_tb"                                                                         | 114 |

| Example 4.49: | Verilog Code Using Reduction Operators                                                  | 116 |

| Example 4.50: | Verilog Testbench for Simulating Module                                                 |     |

|               | "reduction"                                                                             | 116 |

| Example 4.51: | Simulation Results of Verilog Testbench Module<br>"reduction_tb"                        | 117 |

| Example 4.52: | Verilog Code Using Relational Operators                                                 | 118 |

| Example 4.53: | Verilog Testbench for Simulation of Module<br>"relational"                              | 118 |

| Example 4.54: | Verilog Code Using "if" Statement Inferring                                             |     |

|               | Unwanted Latch                                                                          | 122 |

| Example 4.55: | Verilog Code Using "if" Statement That Does Not                                         |     |

|               | Infer Unwanted Latch                                                                    | 123 |

| Example 4.56: | Verilog Code for Incomplete "case" Statement                                            | 124 |

| Example 4.57: | Verilog Code Utilizing "default" Condition for                                          |     |

|               | "case" Statement                                                                        | 125 |

| Example 4.58: | Verilog Code Using "case" Statement with All                                            |     |

| -             | Conditions Specified                                                                    | 126 |

| Example 4.59: | Verilog Code to Obtain Multiplexer Functionality                                        | 10- |

|               | Using Conditional Operator                                                              | 127 |

| Example 4.60: | Verilog Code for a 1 KBit Memory Array                                                  | 128 |

| Example 4.61: | Verilog Testbench Module " <i>memory_tb</i> " to                                        | 100 |

| Example 462   | Simulate Module " <i>memory</i> "<br>Synthesizable Veriles Code for Troffic Light State | 129 |

| Example 4.62: | Synthesizable Verilog Code for Traffic Light State<br>Machine Controller                | 142 |

|               |                                                                                         |     |

| Example 4.63: | 6                                                                     |     |

|---------------|-----------------------------------------------------------------------|-----|

|               | state_machine                                                         | 147 |

| Example 5.1:  | Verilog Code for Programmable Timer                                   | 161 |

| Example 5.2:  | Verilog Testbench to Simulate Programmable Timer                      |     |

|               | Executing In Mode 0                                                   | 164 |

| Example 5.3:  | Verilog Testbench to Simulate Programmable Timer                      |     |

|               | Executing In Mode 1                                                   | 168 |

| Example 5.4:  | Verilog Testbench to Simulate Programmable Timer                      |     |

|               | Executing In Mode 2                                                   | 171 |

| Example 5.5:  | Synthesizable Verilog Code for Programmable                           |     |

|               | Timer                                                                 | 177 |

| Example 6.1:  | Synthesizable Verilog Code for PLB                                    | 216 |

| Example 6.2:  | Simulation with PortA, PortB and PortC as Input                       |     |

|               | and Output In Mode 0 Operation                                        | 235 |

| Example 6.3:  | Simulation with PortA, PortB and PortC Lower as                       |     |

|               | Input and PortC Upper as Output In Mode 0                             |     |

|               | Operation                                                             | 240 |

| Example 6.4:  | Simulation with <i>PortA</i> , <i>PortB</i> and <i>PortC</i> Upper as |     |

| -             | Input and PortC Lower as Output In Mode 0                             |     |

|               | Operation                                                             | 245 |

| Example 6.5:  | Simulation for Writing and Reading Data From                          |     |

| -             | STATUS and CWR Register                                               | 249 |

| Example 6.6:  | Simulation with <i>PortA</i> and <i>PortB</i> as Strobed Input        |     |

| -             | In Mode 1 Operation                                                   | 253 |

| Example 6.7:  | Simulation with <i>PortA</i> as Strobed Input and <i>PortB</i>        |     |

| -             | as Strobed Output In Mode 1 Operation                                 | 258 |

| Example 6.8:  | Simulation with <i>PortA</i> as Strobed Output and <i>PortB</i>       |     |

| -             | as Strobed Input In Mode 1 Operation                                  | 263 |

| Example 6.9:  | Simulation with <i>PortA</i> and <i>PortB</i> as Strobed              |     |

| -             | Output In Mode 1 Operation                                            | 267 |

| Example 6.10: | Simulation with <i>PortA</i> as Strobed IO and <i>PortB</i> as        |     |

| 1             | Input In Mode 2 Operation                                             | 273 |

| Example 6.11: | Simulation with <i>PortA</i> as Strobed IO and <i>PortB</i> as        |     |

| 1             | Output In Mode 2 Operation                                            | 277 |

| Example 6.12: | Simulation with <i>PortA</i> and <i>PortB</i> as Strobed Input        |     |

| 1             | In Mode 1 Operation with STATUS Register                              |     |

|               | Disabled                                                              | 282 |

| Example 6.13: | Simulation with <i>PortA</i> as Strobed IO and <i>PortB</i> as        |     |

| I             | Output In Mode 2 Operation with STATUS                                |     |

|               | Register Disabled                                                     | 287 |

|               |                                                                       |     |

### **List Of Tables**

| Table 2.1.  | The three types of Verilog Code                       | 7  |

|-------------|-------------------------------------------------------|----|

| Table 3.1.  | Table Indicating Value on Net C (net type tri) For    |    |

|             | Different Net Values on Driver A and B                | 24 |

| Table 3.2.  | Table Indicating Value on Net C (net type trior) for  |    |

|             | Different Net Values on Driver A and B                | 24 |

| Table 3.3.  | Table Indicating Value on Net C (net type triand) for |    |

|             | Different Net Values on Driver A and B                | 25 |

| Table 3.4.  | Table Indicating Value on Net C (net type trireg) for |    |

|             | Different Net Values on Driver A and B                | 25 |

| Table 3.5.  | Table Indicating Value on Net C (net type tri1) for   |    |

|             | Different Net Values on Driver A and B                | 25 |

| Table 3.6.  | Table Indicating Value on Net C (net type tri0) for   |    |

|             | Different Net Values on Driver A and B                | 26 |

| Table 3.7.  | Table Indicating Value on Net C (net type wand) for   |    |

|             | Different Net Values on Driver A and B                | 26 |

| Table 3.8.  | Table Indicating Value on Net C (net type wor) for    |    |

|             | Different Net Values on Driver A and B                | 26 |

| Table 3.9.  | Table Showing Different Strength Levels               | 27 |

| Table 3.10. | Truth Table for pmos Transistor Primitive             | 28 |

| Table 3.11. | Truth Table for nmos Transistor Primitive             | 28 |

| Table 3.12. | Truth Table for cmos Passgate Primitive               | 29 |

| Table 3.13. | Truth Table for notif0 Tri-state Inverter Primitive   | 31 |

| Table 3.14. | Truth Table for notif1 Tri-state Inverter Primitive   | 31 |

| Table 3.15. | Truth Table for bufif0 Tri-state Buffer Primitive     | 32 |

| Table 3.16. | Truth Table for bufif1 Tri-state Buffer Primitive     | 32 |

| Table 3.17. | Table Showing Functionality of UDP Module             |    |

|             | UDP_GATE                                              | 36 |

| Table 3.18. | Table Showing Functionality of UDP Module             |    |

|             | UDP_LATCH                                             | 37 |

|             |                                                       |    |

xxi

| Table 3.19. | 9. Table Showing Functionality of UDP Module              |     |

|-------------|-----------------------------------------------------------|-----|

|             | UDP_POS_FLOP                                              | 38  |

| Table 3.20. | Concurrent and Sequential Statements                      | 39  |

| Table 4.1.  | Differences in Simulation Resulting From an               |     |

|             | Incomplete Sensitivity List                               | 67  |

| Table 4.2.  | Truth Table Showing Functionality for Module              |     |

|             | "conditional"                                             | 69  |

| Table 4.3.  | Interface Signal Description for Traffic Light Controller | 137 |

| Table 5.1.  | Signal Description for Programmable Timer Design          | 153 |

| Table 6.1.  | Table Showing a Description of PLB's Interface Signals    | 183 |

| Table 6.2.  | Table Showing a Description of Bits 4 to 1 of CWR         |     |

|             | Register                                                  | 184 |

| Table 6.3.  | Table Showing a Description of Bits 2 and 1 of CWR        |     |

|             | Register                                                  | 184 |

| Table 6.4.  | Table Showing the Combinations of Functionality of        |     |

|             | PortA, PortB, PortC Upper and PortC Lower in Mode 0       |     |

|             | Operation                                                 | 186 |

| Table 6.5.  | Table Showing the Combinations of Functionality of        |     |

|             | PortA and PortB in Mode 1 Operation                       | 187 |

| Table 6.6.  | Table Showing the Combinations of Functionality of        |     |

|             | PortA and PortB in Mode 1 Operation                       | 189 |

### Preface

The complexity of integrated circuit (IC) chips has increased tremendously over the past 10 years. In the 1980s, designing an IC chip with several million transistors was simply unimaginable. Today, it is common to have several million transistors on an IC chip. This increase in IC chip complexity is mainly the result of integration of many functions into a single IC chip. With this fundamental change, the conventional method of schematic capture used in IC design became an obstacle to design engineers. It became extremely difficult for design engineers to "hand draw" the large amounts of schematics necessary to achieve the required functionality. Furthermore, IC chips are pushed onto the market at a very fast pace, creating a small time-to-market window. Designers are under constant pressure to design more complex IC chips at a faster rate.

Imagine design engineers needing to hand draw millions of transistors in their schematic! The task was simply impossible. A more efficient and productive method was needed to allow designers to create schematics with large numbers of logic gates within a reasonable timeframe. This lead to the development of h ardware description language (HDL).

This new method allows a designer to code the logic functionality of a circuit in HDL. The code is then synthesized into logic gates using a synthesis tool. A common synthesis tool used in the industry is Synopsys's Design Compiler. (To learn how to use Synopsys's Design Compiler and to write very high-speed integrated hardware description language [VHDL] code, refer to *VHDL Coding and Logic Synthesis with Synopsys*, by *Weng Fook Lee, Academic Press*.)

There are two types of HDL used in the industry: Verilog and VHDL. This book only addresses Verilog.

This book is written specifically for students and engineers learning to write synthesizable Verilog code. Chapter 1 introduces the use of VHDL and Verilog. Chapter 2 describes application-specific IC (ASIC) design flow. Flow

charts and descriptions are given to help the reader better understand ASIC design flow.

Chapter 3 discusses basic concepts of Verilog coding. This chapter shows the reader how numbers, comments, and Verilog data types and strengths can be used in Verilog coding. Use of Verilog gate-level primitives and user-defined primitives are also discussed.

Chapter 4 describes the common practices and coding style used when coding for synthesis. Naming convention, design partitioning, effects of timing loops, clock generation, reset usage, and sensitivity list are covered in this chapter. Verilog concepts of blocking and nonblocking statements are discussed in detail. Examples and waveforms are provided throughout to help the reader understand these concepts. Chapter 4 also gives examples of common coding style for Verilog operators. The concepts of latch inference, coding of memory array, and the state machine are also included. The state machine design example consists of design specification, state diagrams to show the functionality of the state machine, synthesizable Verilog code for the state machine, and test benches to verify the functionality of the state machine.

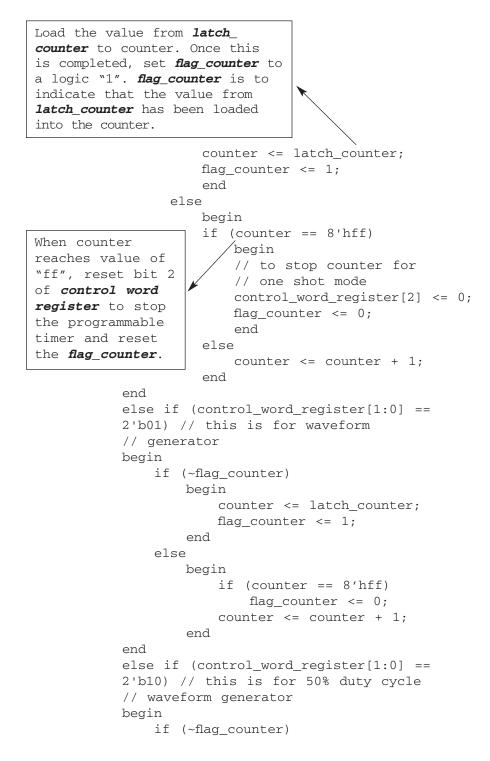

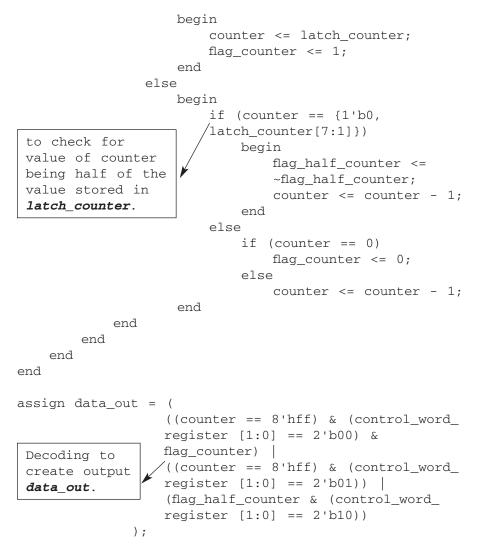

Chapter 5 shows the reader how a design project for a programmable timer is implemented. This chapter starts with a specification for a programmable timer. It then proceeds to show the reader how a microarchitecture can be derived from the specification. Flow charts are shown to help the reader understand the functionality that is required. Verilog code and Verilog test benches are included to show how the design example can be simulated and verified. Waveforms of output results are discussed.

Chapter 6 shows the design of a programmable logic block for peripheral interface (similar to the industry's 8255 PPI [programmable peripheral interface]). This chapter begins with the specification of the design. Microarchitecture of the design is discussed and flow charts are shown to help the reader understand the required functionality of the design. Synthesizable Verilog code for the design is shown with test benches for verification of different functionality of the design. Waveforms for output results are discussed.

This book gives many examples and is written with practicality in mind. It has 91 examples to help the reader understand the concepts and coding style that are being discussed. It begins with simple Verilog coding and progresses to complex real-life design examples. Chapter 4 shows a state machine design example of an intelligent traffic light system. Chapter 5 shows a design example of a programmable timer, beginning with product specification, microarchitecture definition, Verilog coding, and verification. This design example also shows the reader how Verilog code can be written and verified but cannot be synthesized into the required circuit.

To help the reader gain a better understanding of how these real-life design examples are achieved, flow charts, waveforms, and detailed explanations of simulation results are included.

### Acknowledgments

This book would not have been possible without the help of many people. I would like to thank Mike Van Buskirk, Colin Bill, Ken Cheong Cheah, Ed Bautista, Santosh Yachareni, Tim Chen, Yu Cheng, Murni, Boon Weng, Keith Wong, Azrul Halim, Azydee Hamid, Chun Keat Lee, Sun Chong See, Soo Me, Mona Chee, Dianne and Larry, and, of course, the staff at John Wiley & Sons.

### Trademarks

HDL Designer and Modelsim are trademarks of Mentor Graphics, Inc. Visual HDL is a trademark of Summit Design, Inc. Design Compiler, VCS, and Scirocco are trademarks of Synopsys, Inc. Verilog XL, NC Sim, and Ambit are trademarks of Cadence, Inc.

### Introduction

Since the early 1980s, when schematic capture was introduced as an efficient way to design very large-scale integration (VLSI) circuits, it has been the design method of choice for designers in the world of VLSI design.

However, the use of this method reached its limits in the early 1990s, as more and more logic functionality and features were integrated onto a single chip. Today, most application-specific integrated circuit (ASIC) chips consist of no fewer than one million transistors. Designing circuits this large using the method of schematic capture is time consuming and is no longer efficient. Therefore, a more efficient manner of design was required. This new method had to increase the designers' efficiency and allow ease of design, even when dealing with large circuits.

From this requirement arose the wide acceptance of HDL (hardware description language). HDL allows a designer to describe the functionality of a required logic circuit in a language that is easy to understand. The description is then simulated using test benches. After the HDL description is verified for logic functionality, it is synthesized to logic gates by using synthesis tools.

This method helps a designer to design a circuit in a shorter timeframe. The savings in design time is achieved because the designer need not be concerned with the intricate complexities that exist in a particular circuit, but instead is focused on the functionality that is required. This new method of design has been widely adopted today in the field of ASIC design. It allows designers to design large numbers of logic gates to implement logic features and functionality that are required on an ASIC chip.

Verilog Coding for Logic Synthesis, edited by Weng Fook Lee

#### 2 INTRODUCTION

The most widely used HDLs in the ASIC industry are Verilog and VHDL (very high-speed integrated circuit hardware description language). Each have advantages and disadvantages. The coding styles for these languages have some similarities as well as differences.

### **ASIC Design Flow**

Application-specific integrated circuit (ASIC) design is based on a design flow that uses hardware description language (HDL). Most electronic design automation (EDA) tools used for ASIC flow are compatible with both Verilog and very high speed integrated circuit hardware description language (VHDL).

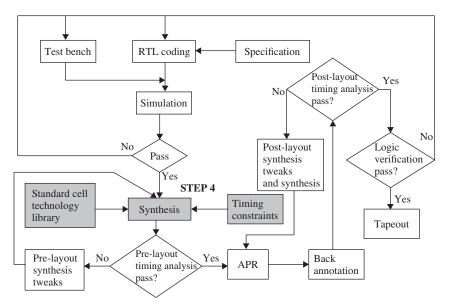

In this flow, the design and implementation of a logic circuit are coded in either Verilog or VHDL. Simulation is performed to check its functionality. This is followed by synthesis. Synthesis is a process of converting HDL to logic gates. After synthesis, the next step is APR (auto-place-route). APR is explained in more detail in Section 2.6.

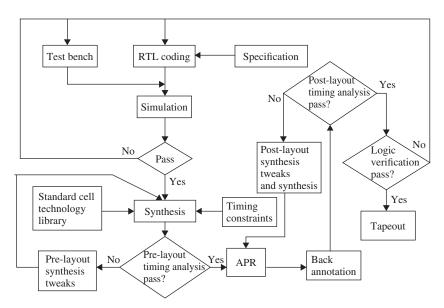

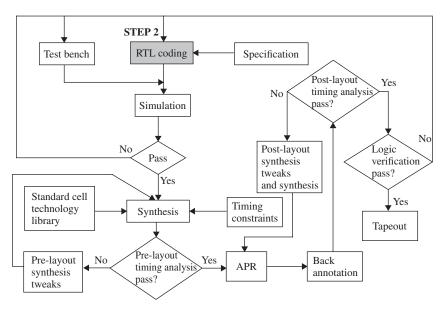

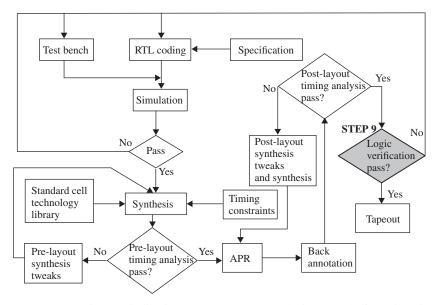

Figure 2.1 shows a diagram of an ASIC design flow, beginning with specification of an ASIC design to register transfer level (RTL) coding and, finally, to tapeout.

### 2.1 SPECIFICATION

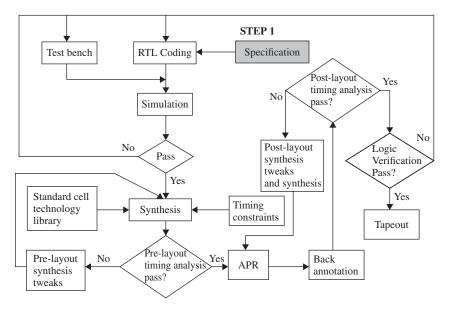

Figure 2.2 indicates the beginning of the ASIC flow: the specification of a design. This is Step 1 of an ASIC design flow. The design of an ASIC chip begins here.

Specification is the most important portion of an ASIC design flow. In this step, the features and functionalities of an ASIC chip are defined. Chip planning is also performed in this step.

During this process, architecture and microarchitecture are derived from the required features and functionalities. This derivation is especially impor-

Verilog Coding for Logic Synthesis, edited by Weng Fook Lee

ISBN 0-471-429767 Copyright © 2003 by John Wiley and Sons, Inc.

**FIGURE 2.1.** Diagram showing an ASIC design flow. Sections 2.1 to 2.9 explain each section of the ASIC flow in detail.

FIGURE 2.2. Diagram indicating Step 1 of an ASIC design flow: specification.

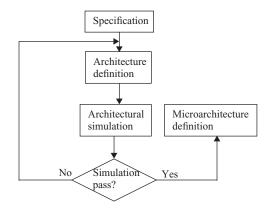

FIGURE 2.3. Diagram showing the definition of architecture and microarchitecture.

tant, as the architecture of a design plays an important role in determining the performance capabilities and silicon area utilization.

Figure 2.3 shows the process involved in defining the architecture and microarchitecture of a design. Specification contains a list of all features and functionalities required in the design. These include power consumption, voltage references, timing restrictions, and performance criteria. From this list, the chip architecture can be drafted. This defined architecture must take into consideration all required timing, voltage, and speed/performance of the design. Architectural simulations need to be performed on the drafted architecture to ensure that it meets the required specification.

During architecture simulations, the architectural definition will have to be changed if the simulation result shows it cannot meet any requirements in the specification. When all the requirements are met, this architecture is said to meet the required specifications. From here, a microarchitecture is drafted and defined to allow execution of the architecture from a design standpoint.

The microarchitecture is the key point that enables the design phase. A microarchitecture interfaces the design's architecture and circuit. It also allows transformation of an architectural concept into possible design implementation.

#### 2.2 RTL CODING

Figure 2.4 shows Step 2 of the ASIC design flow. This is the beginning of the design phase. The microarchitecture is transformed into a design by converting it into RTL code.

As shown in Section 2.1 (Step 1 of the ASIC design flow), architecture and microarchitecture are derived from specification. In Step 2, the micro-architecture, which is the implementation of the design, is coded in synthesizable RTL.

FIGURE 2.4. Diagram indicating Step 2 of an ASIC design flow: RTL coding.

There are several ways to obtain the RTL code. Some designers use graphical entry tools like Summit Design's Visual HDL or Mentor Graphics HDL Designer. These graphical entry tools allow designers to use bubble diagrams, flow charts, or truth table to implement the microarchitecture, which subsequently generate the RTL code either in Verilog or VHDL. However, some designers prefer writing the RTL code rather than using a graphical entry tool. Both approaches end in the same result: synthesizable RTL code that describes logic functionality of the specification.

#### 2.2.1 Types of Verilog Code: RTL, Behavioral, and Structural

Section 2.2 discusses RTL coding. In Verilog language, there are three types of Verilog code. For most cases of synthesis, synthesizable RTL code is used. Table 2.1 lists the differences and usage of each of the types of Verilog code.

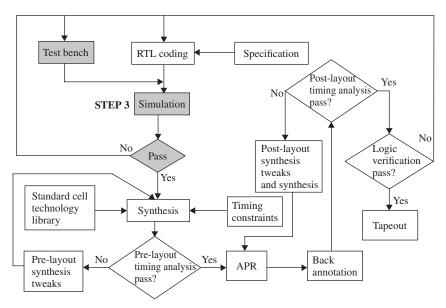

#### 2.3 TEST BENCH AND SIMULATION

Figure 2.5 shows Step 3 in the ASIC design flow, which involves creation of test benches. These are used to simulate the RTL code.

A test bench is basically a wraparound environment surrounding a design, which enables the design to be simulated. It injects a specified set of stimulus

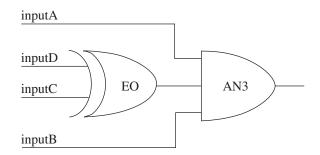

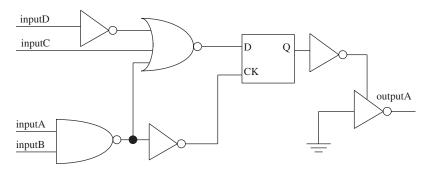

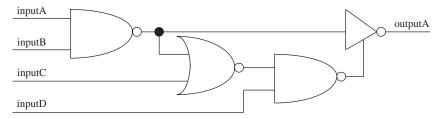

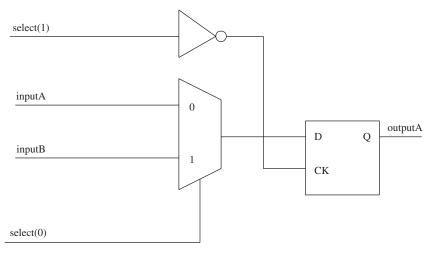

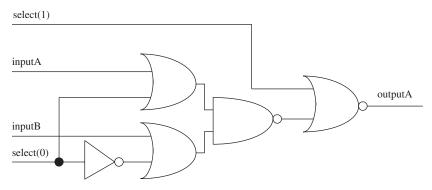

| Behavioral                                                                                                                                                                                                                                                                                             | Structural                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Behavioral coding is<br>used to describe a "black<br>box" design whereby the<br>output of the design is<br>specified for a certain<br>input pattern. Behavioral<br>code mimics the<br>functionality and<br>behavior of the "black<br>box" design. It is<br>normally used for system-<br>level testing. | Structural Verilog coding<br>has a data type structure<br>that defines the<br>different components and<br>their interconnects<br>present in a design. It<br>represents a netlist of a<br>design. Structural<br>Verilog is normally used<br>when passing netlist<br>information of a design<br>between design tools. For<br>example, upon completion<br>of synthesis, the netlist<br>of a design is passed to<br>APR (refer to Section 2.6<br>for explanation of APR)<br>using structural Verilog.                        |

| module behavior (inputA,<br>inputB, inputC, inputD,<br>outputA);                                                                                                                                                                                                                                       | module structural (inputA,<br>inputB, inputC, inputD,<br>outputA);                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| input inputA, inputB,<br>inputC, inputD;                                                                                                                                                                                                                                                               | input inputA, inputB,<br>inputC, inputD;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| output outputA;                                                                                                                                                                                                                                                                                        | output outputA;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

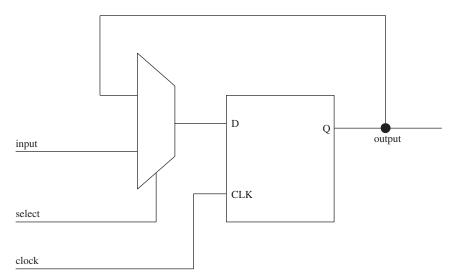

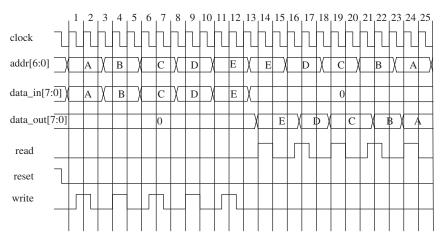

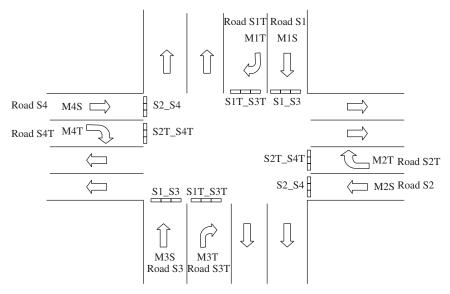

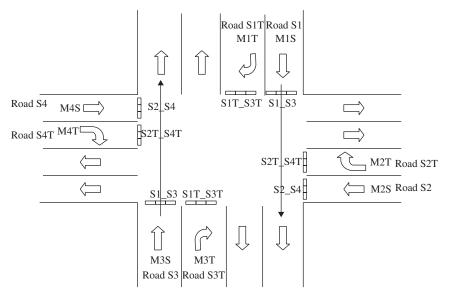

| reg outputA;                                                                                                                                                                                                                                                                                           | wire n30;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |