# J. Bhasker

# VERILOG® SYNTHESIS

A Practical Primer

# Verilog® HDL Synthesis A Practical Primer

#### Other books by the same author:

- A Verilog HDL Primer, Star Galaxy Press, Allentown, PA, 1997, ISBN 0-9656277-4-8.

- A VHDL Synthesis Primer, Second Edition, Star Galaxy Publishing, Allentown, PA, 1998, ISBN 0-9650391-9-6. (Based on IEEE Std 1076.3-1997 Arithmetic Packages, NUMERIC\_BIT and NUMERIC\_STD)

- A VHDL Synthesis Primer, Star Galaxy Publishing, Allentown, PA, 1996, ISBN 0-9650391-0-2.

- A VHDL Primer: Revised Edition, Prentice Hall, Englewood Cliffs, NJ, 1995, ISBN 0-13-181447-8. (Based on IEEE Std 1076-1993)

- A VHDL Primer, Prentice Hall, Englewood Cliffs, NJ, 1992, ISBN 0-13-952987-X. (Based on IEEE Std 1076-1987)

- A Guide to VHDL Syntax, Prentice Hall, Englewood Cliffs, NJ, 1995, ISBN 0-13-324351-6.

- VHDL Features and Applications: Study Guide, IEEE, 1995, Order No. HL5712.

- In Japanese: A VHDL Primer, CQ Publishing, Japan, ISBN 4-7898-3286-4, 1995.

- In German: Die VHDL-Syntax (Translation of A Guide to VHDL Syntax), Prentice Hall Verlag GmbH, 1996, ISBN 3-8272-9528-9.

aay 2993

# Verilog<sub>®</sub> HDL Synthesis A Practical Primer

Jayaram J. BHASKER

Distinguished Member of Technical Staff Bell Labs, Lucent Technologies

Star Galaxy Publishing

1058 Treeline Drive, Allentown, PA 18103

### EEL98/809

Copyright © 1998 Lucent Technologies. All rights reserved.

#### Published by:

Star Galaxy Publishing 1058 Treeline Drive, Allentown, PA 18103

Phone: 610-391-7296

Cover design: Jennifer Swanker

No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### WARNING - DISCLAIMER

The author and publisher have used their best efforts in preparing this book and the examples contained in it. They make no representation, however, that the examples are error-free or are suitable for every application to which a reader may attempt to apply them. The author and the publisher make no warranty of any kind, expressed or implied, with regard to these examples, documentation or theory contained in this book, all of which is provided "as is". The author and the publisher shall not be liable for any direct or indirect damages arising from any use, direct or indirect, of the examples provided in this book.

Verilog® is a registered trademark of Cadence Design Systems, Inc.

Printed in the United States of America

10987654321

**Library of Congress Catalog Card Number: 98-61058**

ISBN 0-9650391-5-3

Zindagi ka safar, hai ye kaisa safar,

("Life's travel, what a travel it is")

Koi samjha nahi, koi jana nahi,

("No one has understood it, no one knows about it")

Hai ye kaisi dager, chalte hai sub mager,

("What kind of goal it is, still everyone goes through it")

Koi samjha nahi, koi jana nahi

("No one has understood it, no one knows about it")

- A song from an Indian film "Safar"

## **CONTENTS**

| Foreword  |       |                                         | xiii |

|-----------|-------|-----------------------------------------|------|

| Preface   |       |                                         | xv   |

| CHAPTER 1 |       |                                         |      |

|           | Basic | es                                      | 1    |

|           | 1.1.  | What is Synthesis?, 1                   |      |

|           | 1.2.  | Synthesis in a Design Process, 3        |      |

|           | 1.3.  | Logic Value System, 6                   |      |

|           | 1.4.  | Bit-widths, 6                           |      |

|           |       | 1.4.1. Data Types, 6                    |      |

|           |       | Net Data Type, 6 Register Data Type, 8  |      |

|           |       | 1.4.2. Constants, 9                     |      |

|           |       | 1.4.3. Parameters, 10                   |      |

|           | 1.5.  | Value Holders for Hardware Modeling, 10 |      |

| CHAPTER 2 |       |                                         |      |

|           | Veril | og Constructs to Gates                  | 15   |

|           | 2.1.  | Continuous Assignment Statement, 16     |      |

2.2. Procedural Assignment Statement, 17 2.2.1. Blocking Procedural Assignment, 17 2.2.2. Non-blocking Procedural Assignment, 18 2.2.3. Target of Assignment, 19 2.2.4. Assignment Restrictions, 20 2.3. Logical Operators, 21 2.4. Arithmetic Operators, 22 2.4.1. Unsigned Arithmetic, 22 2.4.2. Signed Arithmetic, 23 2.4.3. Modeling a Carry, 24 2.5. Relational Operators, 25 2.6. Equality Operators, 27 2.7. Shift Operators, 28 2.8. Vector Operations, 30 2.9. Part-selects, 32 2.10. Bit-selects, 33 2.10.1. Constant Index, 33 2.10.2. Non-constant Index in Expression, 34 2.10.3. Non-constant Index in Target, 35 2.11. Conditional Expression, 36 2.12. Always Statement, 37 2.13. If Statement, 40 2.13.1. Inferring Latches from If Statements, 41 2.14. Case Statement, 45 2.14.1. Casez Statement, 48 2.14.2. Casex Statement, 49 2.14.3. Inferring Latches from Case Statements, 51 2.14.4. Full Case, 52 2.14.5. Parallel Case, 55 2.14.6. Non-constant as Case Item, 58 2.15. More on Inferring Latches, 59 Locally Declared Variable, 60 Variable Assigned Before Use, 61 Use Before Assigned, 62 2.15.1. Latch with Asynchronous Preset and Clear, 64 2.16. Loop Statement, 66 2.17. Modeling Flip-flops, 68 Local Use of Variables, 72

2.17.1. Multiple Clocks, 75

|   |             | 2.17.2. Multi-phase Clocks, 77                   |            |  |  |  |

|---|-------------|--------------------------------------------------|------------|--|--|--|

|   |             | 2.17.3. With Asynchronous Preset and Clear, 78   |            |  |  |  |

|   |             | 2.17.4. With Synchronous Preset and Clear, 81    |            |  |  |  |

|   | 2.18.       | More on Blocking vs Non-blocking Assignments, 84 |            |  |  |  |

|   | 2.19.       | Functions, 88                                    |            |  |  |  |

|   | 2.20.       | Tasks, 89                                        |            |  |  |  |

|   | 2.21.       | Using Values x and z, 93                         |            |  |  |  |

|   |             | 2.21.1. The Value x, 93                          |            |  |  |  |

|   |             | 2.21.2. The Value z, 93                          |            |  |  |  |

|   | 2.22.       | Gate Level Modeling, 97                          |            |  |  |  |

|   | 2.23.       | Module Instantiation Statement, 98               |            |  |  |  |

|   |             | 2.23.1. Using Predefined Blocks, 99              |            |  |  |  |

|   |             | Instantiating User-built Multipliers, 99         |            |  |  |  |

|   |             | Instantiating User-specific Flip-flops, 101      |            |  |  |  |

|   | 2.24.       | Parameterized Designs, 103                       |            |  |  |  |

|   |             |                                                  |            |  |  |  |

|   |             |                                                  |            |  |  |  |

| ١ | <b>Iode</b> | eling Examples 1                                 | <b>107</b> |  |  |  |

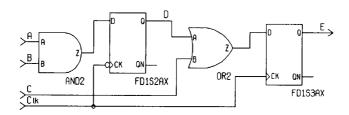

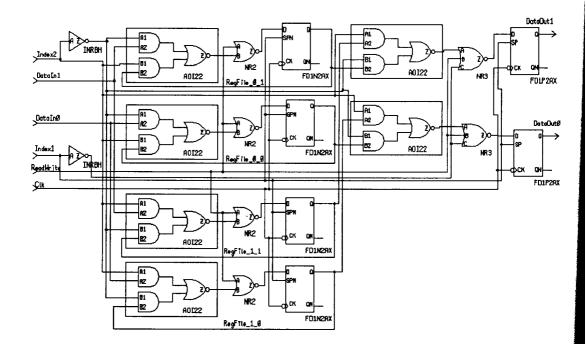

|   | 3.1.        | Modeling Combinational Logic, 108                |            |  |  |  |

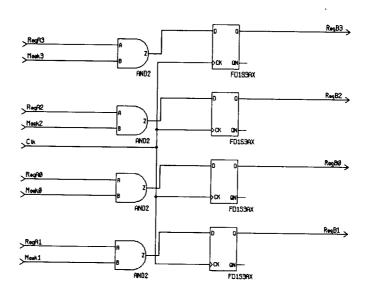

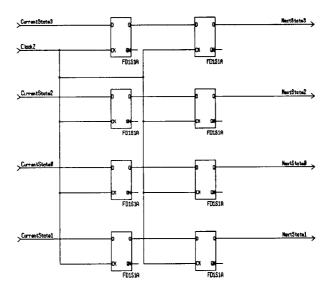

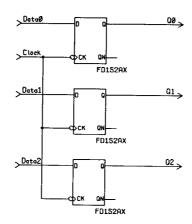

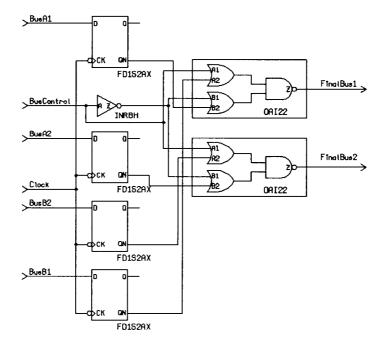

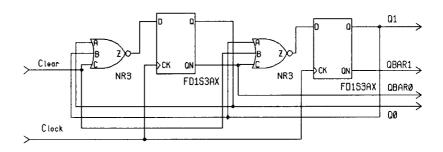

|   | 3.2.        | Modeling Sequential Logic, 110                   |            |  |  |  |

|   | 3.3.        |                                                  |            |  |  |  |

|   | 3.4.        | •                                                |            |  |  |  |

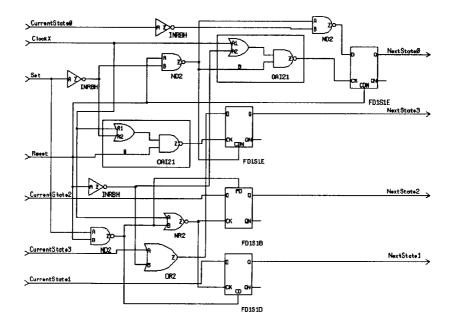

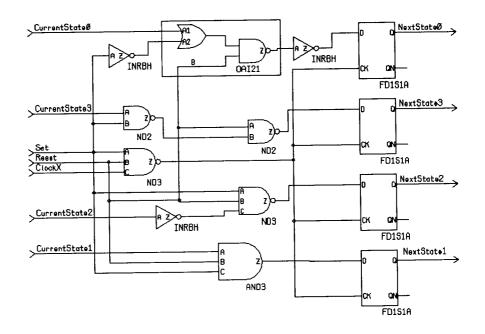

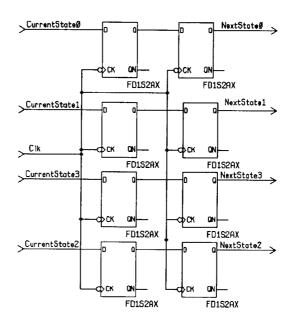

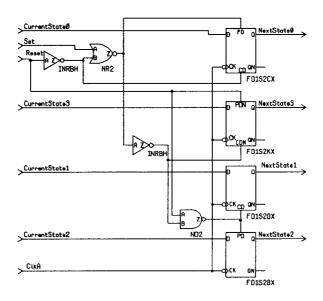

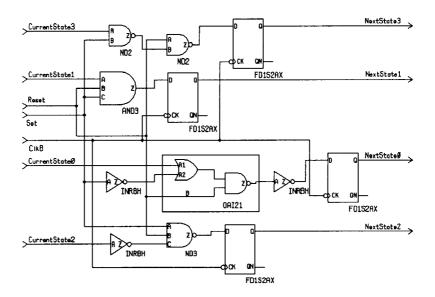

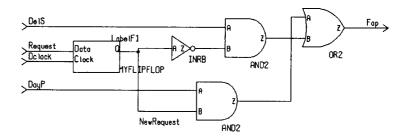

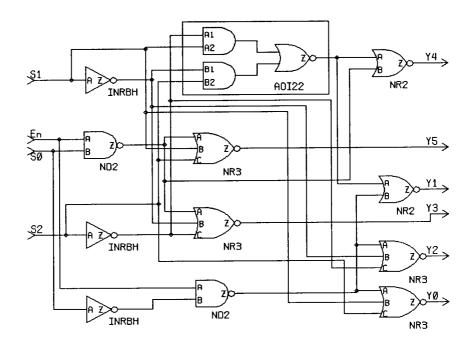

|   | 3.5.        | Modeling a Finite State Machine, 114             |            |  |  |  |

|   |             | 3.5.1. Moore FSM, 114                            |            |  |  |  |

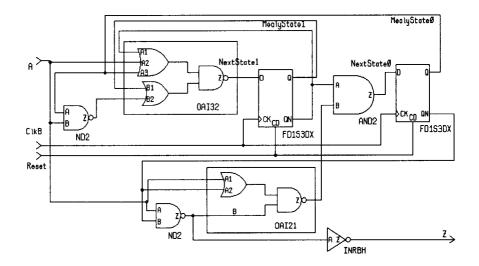

|   |             | 3.5.2. Mealy FSM, 117                            |            |  |  |  |

|   |             | 3.5.3. Encoding States, 121                      |            |  |  |  |

|   |             | Using Integers, 122                              |            |  |  |  |

|   |             | Using Parameter Declarations, 122                |            |  |  |  |

|   | 3.6.        | <b>C</b> .                                       |            |  |  |  |

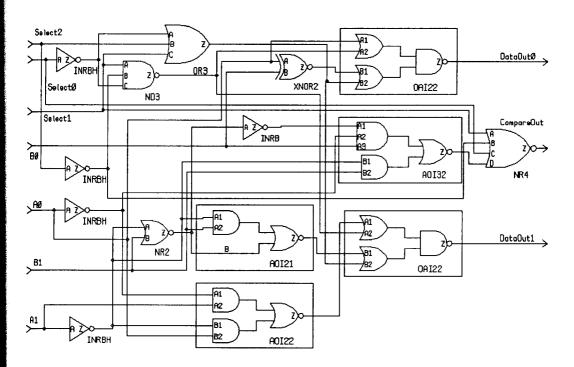

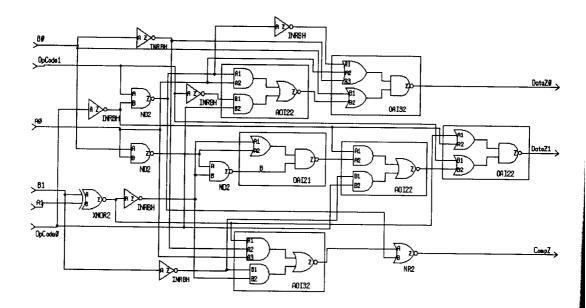

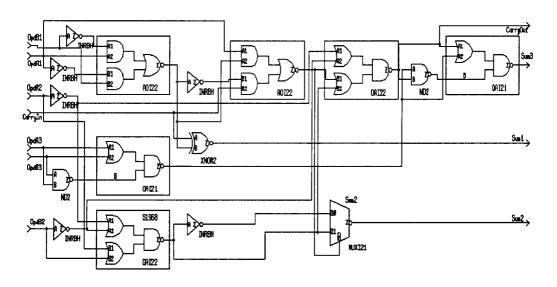

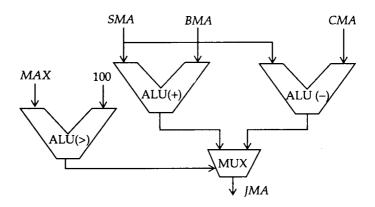

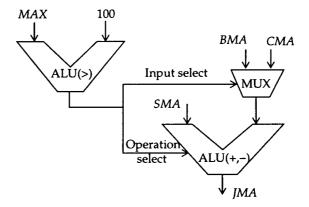

|   | 3.7.        | Modeling an ALU, 124                             |            |  |  |  |

|   |             | 3.7.1. A Parameterized ALU, 124                  |            |  |  |  |

|   |             | 3.7.2. A Simple ALU, 126                         |            |  |  |  |

|   | 3.8.        | •                                                |            |  |  |  |

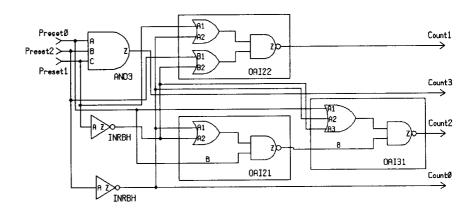

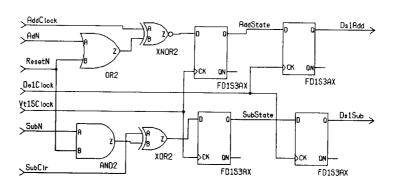

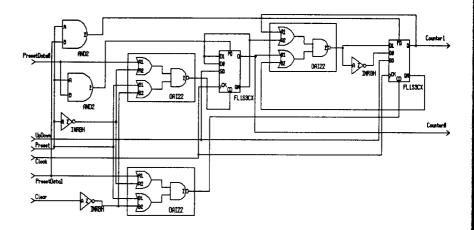

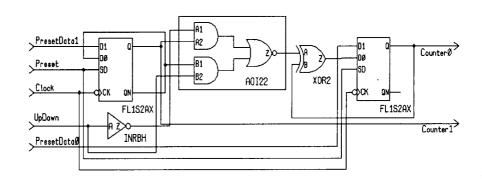

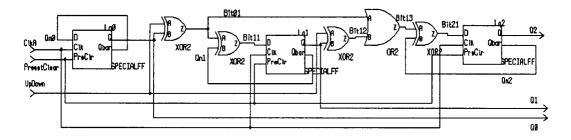

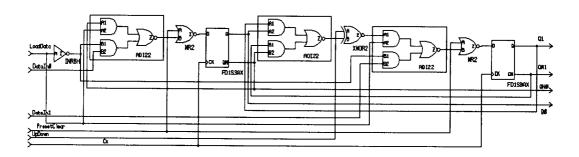

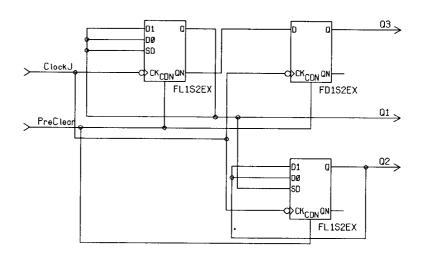

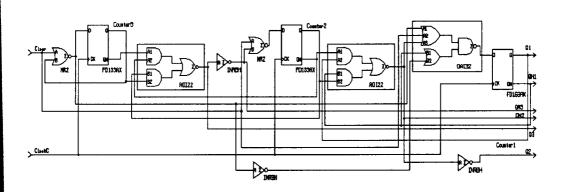

|   |             | 3.8.1. Binary Counter, 128                       |            |  |  |  |

|   |             | 3.8.2. Modulo-N Counter, 129                     |            |  |  |  |

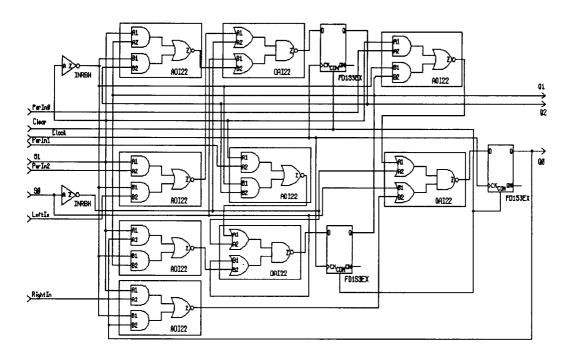

|   |             | 3.8.3. Johnson Counter, 130                      |            |  |  |  |

|   |             | 3.8.4. Gray Counter, 132                         |            |  |  |  |

|   | 3.9.        | Modeling a Parameterized Adder, 133              |            |  |  |  |

|   |             |                                                  |            |  |  |  |

**CHAPTER 3**

CHAPTER 4

**CHAPTER 5**

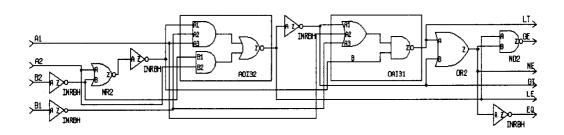

| 3.10. | Modeling a Parameterized Comparator, 134       |     |

|-------|------------------------------------------------|-----|

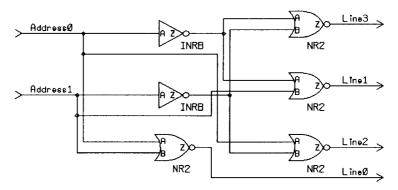

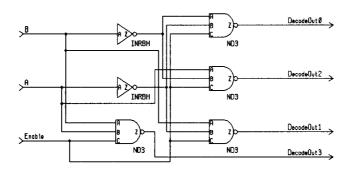

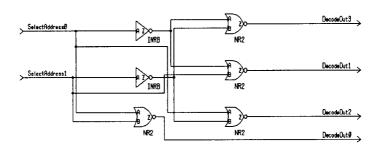

| 3.11. | Modeling a Decoder, 136                        |     |

|       | 3.11.1. A Simple Decoder, 136                  |     |

|       | 3.11.2. Binary Decoder, 136                    |     |

|       | 3.11.3. Johnson Decoder, 137                   |     |

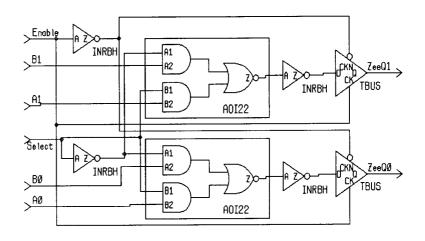

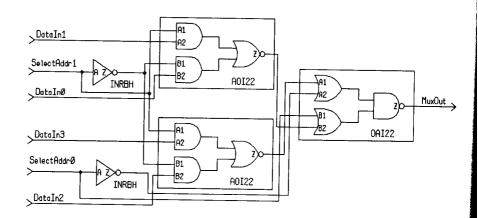

| 3.12. | Modeling a Multiplexer, 139                    |     |

|       | 3.12.1. A Simple Multiplexer, 139              |     |

|       | 3.12.2. A Parameterized Multiplexer, 140       |     |

| 3.13. | Modeling a Parameterized Parity Generator, 141 |     |

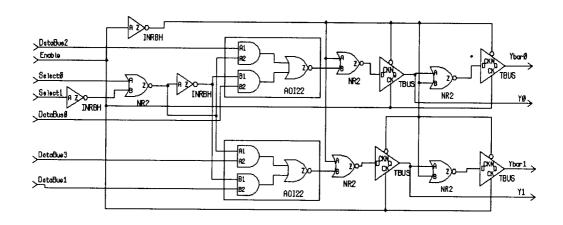

| 3.14. | Modeling a Three-state Gate, 143               |     |

| 3.15. | A Count Three 1's Model, 144                   |     |

| 3.16. | A Factorial Model, 146                         |     |

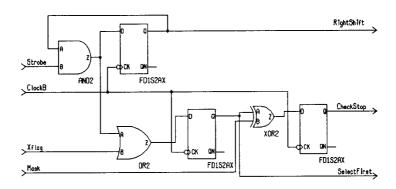

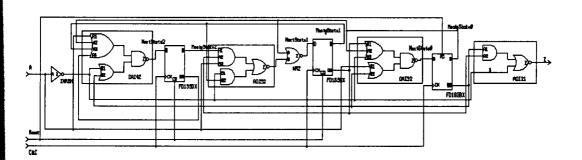

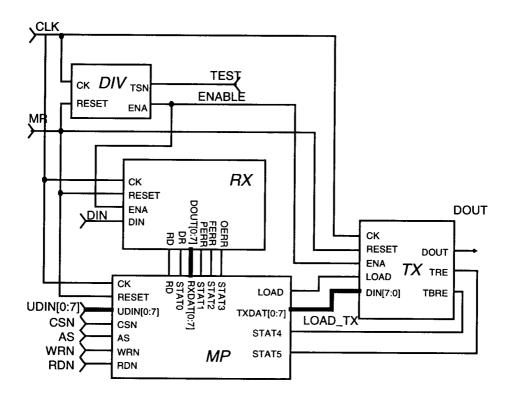

| 3.17. | An UART Model, 147                             |     |

| 3.18. | A Blackjack Model, 153                         |     |

|       |                                                |     |

|       |                                                |     |

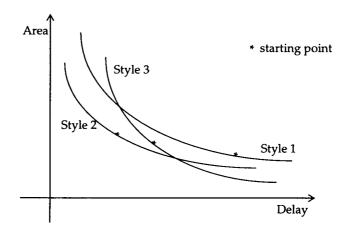

| Mode  | el Optimizations                               | 157 |

| 4.1.  | Resource Allocation, 158                       |     |

|       | Common Subexpressions, 161                     |     |

|       | Moving Code, 162                               |     |

|       | Common Factoring, 163                          |     |

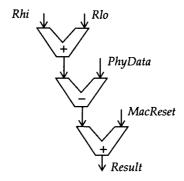

|       | Commutativity and Associativity, 164           |     |

|       | Other Optimizations, 165                       |     |

|       | Flip-flop and Latch Optimizations, 166         |     |

|       | 4.7.1. Avoiding Flip-flops, 166                |     |

|       | 4.7.2. Avoiding Latches, 167                   |     |

| 4.8.  | Design Size, 168                               |     |

|       | Small Designs Synthesize Faster, 168           |     |

|       | Hierarchy, 169                                 |     |

|       | Macros as Structure, 169                       |     |

| 4.9.  | Using Parentheses, 170                         |     |

|       |                                                |     |

|       |                                                |     |

| Verif | ication                                        | 173 |

| 5.1.  | A Test Bench, 174                              |     |

|       | Delays in Assignment Statements, 176           |     |

|       | Unconnected Ports, 178                         |     |

|       | •                                              |     |

|                                                                   | 5.4. | Missin  | ng Latches, 179                       |     |

|-------------------------------------------------------------------|------|---------|---------------------------------------|-----|

|                                                                   | 5.5. | More of | on Delays, 181                        |     |

|                                                                   | 5.6. | Event   | List, 182                             |     |

|                                                                   | 5.7. | Synthe  | esis Directives, 183                  |     |

|                                                                   | 5.8. | Variab  | ole Asynchronous Preset, 185          |     |

|                                                                   | 5.9. | Blocki  | ing and Non-blocking Assignments, 186 |     |

|                                                                   |      | 5.9.1.  | Combinational Logic, 186              |     |

|                                                                   |      | 5.9.2.  | Sequential Logic, 188                 |     |

| APPENDIX A Synthesizable Constructs  APPENDIX B A Generic Library |      |         | 191<br>199                            |     |

| Bibliograp                                                        | hy   |         |                                       | 209 |

| Index                                                             |      |         |                                       | 211 |

|                                                                   |      |         |                                       |     |

## **FOREWORD**

he topic of Verilog HDL synthesis has been in existence since 1988. However good textbooks on the topic have not covered basic concepts until now. This practical primer on Verilog HDL synthesis provides a comprehensive and practical description for this new technology. It takes the mystery out of HDL synthesis, by providing an easy to understand Verilog language semantic with respect to synthesis technology. Bhasker is an expert on synthesis: he has worked in synthesis for more than fourteen years. He is currently using his expertise in leading the efforts as the chair of IEEE working group for developing a Verilog RTL synthesis standard (PAR 1364.1) that is based on the OVI<sup>1</sup> RTL synthesis subset 1.0 released in April 1998. Bhasker is one of the architects for the OVI standard on RTL synthesis.

"Verilog HDL Synthesis, A Practical Primer" by J. Bhasker provides students and practicing logic designers with immediate access to well-organized information about Verilog HDL synthesis. It is easy to read and provides a very large number of examples of synthesizable Verilog HDL models. The reader is led systematically from Verilog HDL language constructs, their meaning in synthesis, how synthesis design technology transforms such constructs into gates, and their impact on design verifica-

<sup>1.</sup> Open Verilog International

tion. The book is rich in Verilog HDL model examples and their gate equivalence. The examples are simple and show the different styles of logic modeling such as combinational logic, sequential logic, and register and latched based design, finite state machines, arithmetic units and others.

The book is not just unique in covering HDL synthesis for beginners, but also goes into advanced topics such as how to get optimized logic from a synthesis model. Resource sharing and allocation is one of the topics covered under model optimization. Another unique topic is design verification. The book goes into the principles of synthesis model writing to ensure predictable and verifiable results. Although the chapter is intended for simulation, the same concepts can be applied for formal verification.

This book is the first comprehensive treatment for Verilog HDL synthesis. Bhasker has taught Verilog HDL and Verilog HDL synthesis at Lucent Technologies for more than three years. The book shows the knowledge that Bhasker has accumulated during his fourteen years on synthesis. Although this book is targeted for beginners, expert users can benefit from the basic principles as well as the advanced modeling topics in synthesis. Definitely, intellectual property (IP) developers should follow the modeling style recommended in this book.

Vassilios C. Gerousis Senior Staff Technologist, Motorola, Phoenix, Arizona Chairman, Technical Coordinating Committee (TCC), Open Verilog International

## **PREFACE**

ere is a practical and useful guide to Verilog HDL register-transfer level synthesis. A large number of synthesizable Verilog HDL examples are provided. Verilog HDL constructs that are supported for synthesis are described in detail. Furthermore, examples are shown using these synthesizable constructs collectively to model hardware elements. Common causes of functional mismatches between the design model and the synthesized netlist are described in detail and recommendations are made on how to avoid these.

To many, synthesis appears like a black-box; a design described in Verilog HDL goes in, and out comes a gate level netlist. It appears as if there is some mystique in this black-box approach. To take full advantage and usefulness of a synthesis system, it is important to understand the transformations that occur during the synthesis process. The purpose of this book is to expose the black-box myth by describing the transformations that occur during the synthesis process from a hardware description language model to a netlist; Verilog HDL is used as the modeling language.

The Verilog Hardware Description Language, often referred to as Verilog HDL, is an IEEE standard (IEEE Std 1364). The language can be used to describe the behavior, sequential and concurrent, or structure of a model. It can support the description of a design at multiple levels of ab-

straction ranging from the architecture level to the switch level. The language provides support for modeling a design hierarchically and in addition, provides a rich set of built-in primitives, including logic gates and user-defined primitives. Precise simulation semantics are associated with all the language constructs and therefore models written in this language can be verified using a Verilog HDL simulator.

Synthesis, in general, has a different meaning to different people. In this book, I refer to synthesis of a design described in Verilog HDL; this design describes combinational logic and/or sequential logic. In case of sequential logic, the clocked behavior of the design is expressly described. This precludes talking about logic synthesis (a design described in terms of primitive gates) and about high-level synthesis (behavior specified with no clocking information). The synthesis process transforms this Verilog HDL model into a gate level netlist. The target netlist is assumed to be a technology-independent representation of the modeled logic. The target technology contains technology-independent generic blocks such as logic gates, and register-transfer level (RTL) blocks such as arithmetic-logic-units and comparators. The succeeding phases of a synthesis process, which are technology translation (that is, mapping of generic gates to specific parts in a library) and module binding (that is, building RTL blocks using primitive gates) are not described in this book.

It is difficult to write a book on synthesis due to its rapidly evolving nature. In this book, I have therefore provided the basic information that will hold true by and large. I have tried to stay clear of ambiguous topics including implementation-specific issues. Because of the richness of the Verilog HDL language, there may be more than one way to describe a certain behavior. This book suggests one or two such modeling styles that are synthesizable. Again, not all constructs in the language can be synthesized since Verilog HDL was designed to be a simulation language. Therefore, in this book, I have showed constructs that would be supported by a majority of synthesis systems.

I have also avoided mentioning the various features of vendor-specific synthesis tools. However, there are certain cases when it becomes necessary to show an example of an implementation. In such a case, the feature is shown as it is implemented in the ArchSyn (version 14.0) synthesis system developed at Bell Labs, Lucent Technologies.

CAUTION: Not all available synthesis systems may support the Verilog HDL constructs described in this book. For more details on spe-

cific features of any synthesis system, the reader is urged to consult the respective vendors' documentation.

A Verilog Synthesis Interoperability Working Group, of which I am the Chair, is at present working to develop an IEEE standard for RTL synthesis.

This book assumes that the reader knows the basics about the Verilog HDL language. A good source to get such information is the precursor of this book "A Verilog HDL Primer", published by Star Galaxy Press.

This book is targeted to electrical engineers, specifically circuit and system designers, who are interested in understanding the art of synthesis. The book does not try to explain any of the synthesis algorithms. My belief is that by understanding what results to expect from synthesis, a designer will be able to control the quality of the synthesized designs by writing effective design models. This is because the synthesized structure is very sensitive to the way in which a certain model is written.

This book can be used as a text in a college course. In an electrical engineering curriculum, this book can be used in a VLSI course on computer-aided design. Students may use this book to write models and synthesize these using any available synthesis system. The transformations occurring during the synthesis process can thus be studied. In a computer science course, such as in an algorithms course on computer-aided design, students may write a simple synthesis program that reads in a subset of Verilog HDL and generates a synthesized netlist. Examples in this book can be used as test cases to understand the generated netlist.

Professional engineers will greatly benefit from this book when used as a reference. The presence of many examples with models and their synthesized netlists help an engineer in directly going to the page of interest and exploring the example models presented there.

#### Book Organization

Chapter 1 describes the basics of the synthesis process. The basics include topics such as what is a wire, a flip-flop or a state, and how the sizes of objects are determined.

Chapter 2 describes the mapping of Verilog HDL constructs to logic gates. It gives examples of combinational logic and shows how the Verilog HDL constructs get transformed into basic gates and interconnections. Styles for modeling sequential logic designs are also described along with examples for modeling asynchronous preset and clear, synchronous preset and clear, multiple clocks, and multiple-phase clocks.

Occasionally it becomes necessary to use pre-designed blocks in a design. Chapter 2 further describes how to model structure, including the capability to model partial structure in a behavior model.

Chapter 3 describes how Verilog HDL constructs are collectively used to model hardware elements. While Chapter 2 describes the mapping of Verilog HDL to logic gates, this chapter describes the opposite scenario, which is, how to model a hardware element in Verilog HDL for synthesis. Elaborate examples are provided for many common hardware elements, such as multiplexers, counters, decoders and arithmetic-logic-units.

Chapter 4 describes powerful techniques that can be applied to a Verilog HDL model to provide quality synthesized netlists. The optimizations described in this chapter may be performed automatically by a synthesis system; if not, it may have to be performed manually by the designer to achieve quality results.

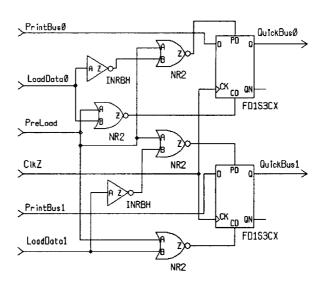

Having synthesized a Verilog HDL model, it is often necessary to validate the synthesized netlist with the input design model. Chapter 5 provides testbench writing strategies that can be used to verify the synthesis results. Because Verilog HDL is not specifically designed to be used as a synthesis language, functional differences may occur between the design model and the synthesized netlist. This chapter explains the cause of some such discrepancies.

In order to illustrate a subset of Verilog HDL supported for synthesis by a typical synthesis system, Appendix A provides a construct by construct description of what is supported by the ArchSyn synthesis system. However, such a subset may vary between different synthesis systems.

Appendix B presents the description of logic gates that are used in the synthesized netlists described in this book.

The synthesized netlists shown in this book are NOT optimized netlists; thus the logic shown in some cases may be suboptimal. This is acceptable since the purpose of this book is to show the transformation of Verilog HDL to gates and not that of demonstrating logic optimization

techniques. Some of the netlists have been optimized purposely so that the netlist could be captured as a figure in the book.

#### **Conventions**

The term designer is referred to in many places in the text. It is used as a generic term to refer to any reader of this text. In addition, the term "synthesis tool" and "synthesis system" are used interchangeably in the text. Either of these refers to the program that reads in a Verilog RTL model and generates a gate level netlist.

In all the Verilog HDL descriptions that appear in this book, reserved words are in **boldface**. Occasionally ellipsis (...) is used in Verilog HDL source to indicate code that is not relevant to that discussion. Certain words such as if and and are written in Courier font so as to indicate their special meaning rather than their English meaning.

All examples that are described in this book have been synthesized using the ArchSyn synthesis system. Logic gates used in the synthesized netlists are described in Appendix B.

#### Acknowledgments

I gratefully acknowledge the following individuals for reviewing drafts of this book and for providing many constructive suggestions for improvement including many thought-provoking comments. I sincerely appreciate their time and effort spent in reviewing this book in spite of their busy work schedules.

- i. Cliff Cummings from Sunburst Design

- ii. Joe Pick from Synopsys

- iii. Doug Smith from VeriBest

- iv. Egbert Molenkamp from University of Twente, the Netherlands

- v. Carlos Roman, Jenjen Tiao, Jong Lee and Sriram Tyagarajan from Bell Labs, Lucent Technologies

- vi. Jim Vellenga and Ambar Sarkar from Viewlogic Systems

Thank you very much!

I would also like to thank Hao Nham for providing an excellent atmosphere here at Bell Labs and for encouraging me to pursue my extracurricular activities (writing this book!) in addition to my regular work.

Of course, like my other books, this book would not be possible without the joy of my life, my family, my wife Geetha and my two rajahs, Arvind and Vinay, who provided me with the delight, pleasure and motivation to write yet another book!

J. Bhasker

August 1998

# C HAPTER

## **BASICS**

erilog HDL is a hardware description language that can describe hardware not only at the gate level and the register-transfer level (RTL), but also at the algorithmic level. This makes translating a design described in Verilog HDL to logic gates a non-trivial process.

This chapter explains the basics involved in the mapping of a Verilog HDL model to logic gates.

#### 1.1 What is Synthesis?

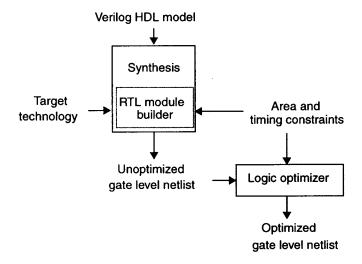

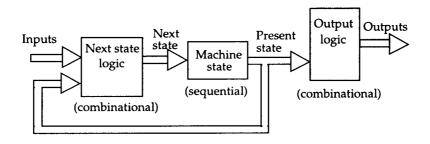

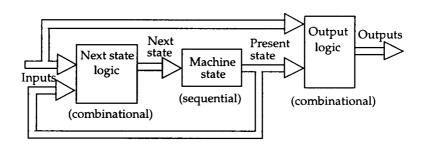

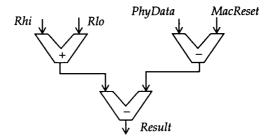

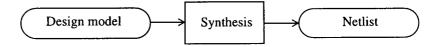

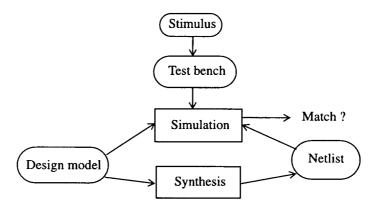

Synthesis is the process of constructing a gate level netlist from a register-transfer level model of a circuit described in Verilog HDL. Figure 1-1 shows such a process. A synthesis system may as an intermediate step, generate a netlist that is comprised of register-transfer level blocks such as flip-flops, arithmetic-logic-units, and multiplexers, interconnected

<sup>1.</sup> This is the definition used in this book.

by wires. In such a case, a second program called the RTL module builder is necessary. The purpose of this builder is to build, or acquire from a library of predefined components, each of the required RTL blocks in the user-specified target technology.

Figure 1-1 The synthesis process.

Having produced a gate level netlist, a logic optimizer reads in the netlist and optimizes the circuit for the user-specified area and timing constraints. These area and timing constraints may also be used by the module builder for appropriate selection or generation of RTL blocks.

In this book, we assume that the target netlist is at the gate level. The logic gates used in the synthesized netlists are described in Appendix B. The module building and logic optimization phases are not described in this book.

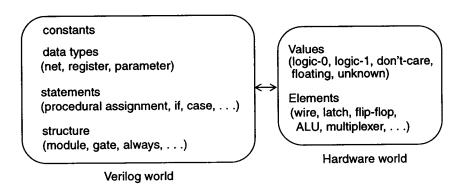

Figure 1-2 shows the basic elements of Verilog HDL and the elements used in hardware. A mapping mechanism or a construction mechanism has to be provided that translates the Verilog HDL elements into their corresponding hardware elements. Questions to ask are:

- How does a data type translate to hardware?

- · How are constants mapped to logic values?

- How are statements translated to hardware?

The following sections discuss these mappings in more detail.

Figure 1-2 The two worlds of synthesis.

#### 1.2 Synthesis in a Design Process

Verilog HDL is a hardware description language that allows a designer to model a circuit at different levels of abstraction, ranging from the gate level, register-transfer level, behavioral level to the algorithmic level. Thus a circuit can be described in many different ways, not all of which may be synthesizable. Compounding this is the fact that Verilog HDL was designed primarily as a simulation language and not as a language for synthesis. Consequently, there are many constructs in Verilog HDL that have no hardware counterpart, for example, the \$display system call. Also there is no standardized subset of Verilog HDL for register-transfer level synthesis.

Because of these problems, different synthesis systems support different Verilog HDL subsets for synthesis. Since there is no single object in Verilog HDL that means a latch or a flip-flop, each synthesis system may provide different mechanisms to model a flip-flop or a latch. Each synthesis system therefore defines its own subset of Verilog HDL including its own modeling style.

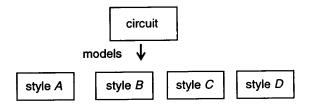

Figure 1-3 shows a circuit that is described in many different ways using Verilog HDL. A synthesis system that supports synthesis of styles A and B may not support that of style C. This implies that typically synthesis

#### CHAPTER 1 Basics

models are non-portable across different synthesis systems. Style  ${\cal D}$  may not be synthesizable at all.

Figure 1-3 Same behavior, different styles.

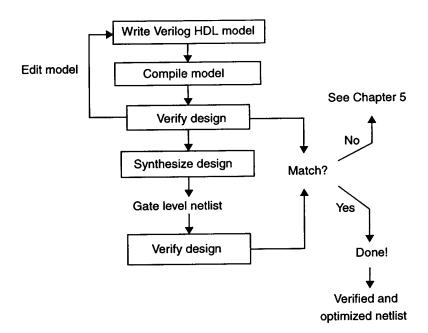

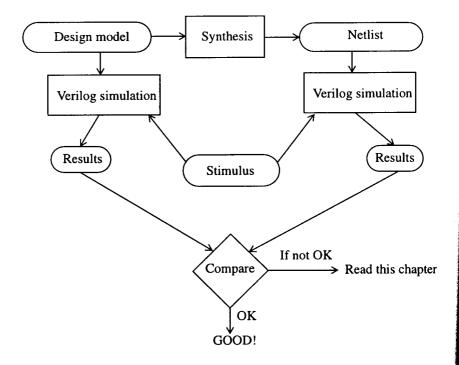

This limitation creates a severe handicap because now the designer not only has to understand Verilog HDL, but also has to understand the synthesis-specific modeling style before a synthesizable model can be written. The typical design process shown in Figure 1-4 can not always be followed for Verilog HDL synthesis.

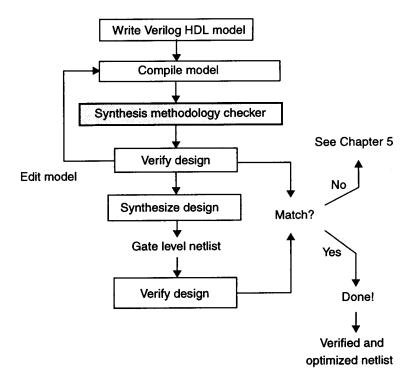

Figure 1-4 Typical design process.

The problem with this design process is that if the Verilog HDL model is written without knowing the synthesis modeling style (this assumes that the model is being written for synthesis; if not, then a non-synthesizable model may be perfectly okay), only during the synthesis phase will the designer learn about the synthesis-specific modeling restriction and style for synthesis. A model rewrite may be necessary at this point. Also a lot of time may have been wasted in the "Write Verilog HDL model" -> "Compile model" -> "Verify" -> "Edit model" loop. Instead, a more practical design process shown in Figure 1-5 has to be followed for Verilog HDL synthesis. The synthesis methodology checker is needed to ensure that the model being written is synthesizable. Note that this must be done within the first verification loop. In this way, after the verification results have been checked, a verified synthesizable model exists, which can then be synthesized.

Figure 1-5 New design process.

#### 1.3 Logic Value System

The common values used in modeling hardware are:

- logic-0

- logic-1

- high-impedance

- don't-care

- unknown

All these values are defined explicitly in Verilog HDL except for the don't-care value. A synthesis system treats the value x, when it is assigned to a variable, as a don't-care value. Here is the mapping between the Verilog HDL values and the hardware modeling values:

- 0 <--> logic-0

- 1 <--> logic-1

- z <--> high-impedance

- z <--> don't-care (in casex and casez statements)

- x <--> don't-care

- x <--> unknown

#### 1.4 Bit-widths

#### 1.4.1 Data Types

In Verilog HDL, a variable belongs to one of the two data types:

- i. net data type

- ii. register data type

#### **Net Data Type**

The size of a net is explicitly specified in a net declaration.

When no size is explicitly specified in a net declaration, the default size is one bit.

Here are the different kinds of net data types that are supported for synthesis.

```

wire wor wand tri supply0 supply1

```

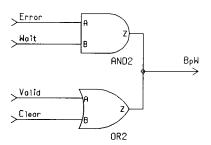

The wire net is the most commonly used net type. When there are multiple drivers driving a wire net, the outputs of the drivers are shorted together. Here is an example.

```

module WireExample (BpW, Error, Wait, Valid, Clear);

input Error, Wait, Valid, Clear;

output BpW;

wire BpW;

assign BpW = Error & Wait;

assign BpW = Valid | Clear;

endmodule

// Synthesized netlist is shown in Figure 1-6.

```

Figure 1-6 Multiple drivers driving a wire net.

The wor nets and wand nets are used when multiple driver resolution needs to be performed using or-logic and and-logic respectively. Upon synthesis, multiple drivers of such a net are connected together by an or gate (for a wor net) and by an and gate (for a wand net). Here is an example that shows this effect.

```

module UsesGates (BpW, BpR, Error, Wait, Clear);

input Error, Wait, Clear;

output BpW, BpR;

wor BpW;

wand BpR;

assign BpW = Error & Wait;

assign BpW = Valid | Clear;

assign BpR = Error ^ Valid;

assign BpR = ! Clear;

endmodule

// Synthesized netlist is shown in Figure 1-7.

```

Figure 1-7 Wand net and wor net have multiple drivers.

The tri net synthesizes just like the wire net.

A supply0 net synthesizes to a wire that is permanently connected to 0 (logic-0), while a supply1 net synthesizes to a wire that is permanently connected to 1 (logic-1).

#### Register Data Type

The different kinds of register<sup>1</sup> types that are supported for synthesis are:

<sup>1.</sup> A variable of a register type does not necessarily imply a set of flip-flops in hardware. See next section.

#### reg integer

A reg declaration explicitly specifies the size, that is, the corresponding number of bits of the variable in hardware. For example,

When no size is explicitly specified in a reg declaration, the default is one bit.

For an integer type, the maximum size is 32 bits and the number is assumed to be in 2's complement form. Optionally a synthesis system may perform data flow analysis of the model to determine the maximum size of an integer variable. For example,

```

wire [1:5] Brq, Rbu;

integer Arb;

. . .

Arb = Brq + Rbu;

```

Size of Arb is determined to be 6 bits. An adder of size 6 is sufficient. The leftmost bit is the carry bit.

The register types: time and real, are not supported for synthesis.

#### 1.4.2 Constants

There are three kinds of constants in Verilog HDL: integer, real and string. Real and string constants are not supported for synthesis.

An integer constant can be written in either of the following two forms.

- i. Simple decimal

- ii. Base format

When an integer is written in a simple decimal form, it is interpreted as a signed number. The integer is represented in synthesis as 32 bits in 2's complement form. If an integer is written in the base format form, then the integer is treated as an unsigned number. If a size is explicitly specified for the integer, then the specified size is the number of bits used for the integer; if not, 32 bits is used for the size. Here are some examples.

| 30    | Signed number, 32 bits                        |

|-------|-----------------------------------------------|

| -2    | Signed number, 32 bits in 2's complement      |

| 2'b10 | Size of 2 bits                                |

| 6'd-4 | 6-bit unsigned number (-4 is represented in   |

|       | 2's complement using 6 bits)                  |

| 'd-10 | 32-bit unsigned number (-10 is represented in |

|       | 2's complement using 32 bits)                 |

#### 1.4.3 Parameters

A parameter is a named constant. Since no size is allowed to be specified for a parameter, the size of the parameter is the same as the size of the constant itself.

```

parameter RED = -1, GREEN = 2;

parameter READY = 2'b01, BUSY = 2'b11, EXIT = 2'b10;

```

RED and GREEN are two 32-bit signed constants. READY, BUSY and EXIT are three parameters of size 2 bits each.

#### 1.5 Value Holders for Hardware Modeling

The basic value holders in hardware are:

- wire

- flip-flop (an edge-triggered storage element)

- latch (a level-sensitive storage element)

A variable in Verilog HDL can either be of the net data type or the register data type. For synthesis, a variable of net type maps to a wire in hardware and a variable of the register type maps either to a wire or a storage element (flip-flop or latch) depending on the context under which the variable is assigned a value. Let us look at a variable of register type in more detail.

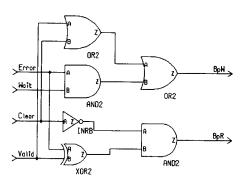

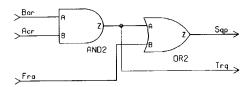

In Verilog HDL, a register variable retains its value through the entire simulation run, thus inferring memory. However, this is too general for synthesis. Here is an example of a variable that is used as a temporary and therefore need not be a candidate for a storage element.

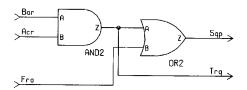

```

wire Acr, Bar, Fra;  // A wire is a net type.

reg Trq, Sqp;  // A reg is a register type.

...

always @ (Bar or Acr or Fra)

begin¹

Trq = Bar & Acr;

Sqp = Trq | Fra;

end

```

Variable Trq is assigned in the first statement and then used in the right-hand-side expression of the second statement. Verilog HDL semantics indicate that Trq retains its value through the entire simulation run. However, it is not necessary to store the value of Trq as a storage element in hardware, since it is assigned and used immediately. Figure 1-8 shows the logic generated.

Figure 1-8 Variable Trq is a wire.

Let us look at another example. In this case, variable Trq is used before its assignment.

```

wire Acr, Bar, Fra;

reg Trq, Sqp;

...

always @ (Bar or Acr or Fra)

begin

Sqp = Trq | Fra;

Trq = Bar & Acr;

end

```

<sup>1.</sup> **begin** ... **end** is a sequential block; all statements that appear within it execute in sequence.

The semantics of this always statement is very clear in Verilog HDL. Whenever an event occurs on Bar, Acr, or Fra (those in the event list), execute the always statement. Since Trq is used before its assignment, Trq has to hold its value during repeated executions of the always statement, thus inferring memory. However, it is not clear how to build a latch for Trq because Trq is not assigned a value under the control of any condition. A synthesis system may not create a latch in this case and may generate the circuit shown in Figure 1-9. Variable Trq is synthesized to a wire again. However, for functionality to match between the Verilog HDL model and the synthesized netlist, Trq must also be in the event list of the always statement. More of this is discussed in Chapter 5.

Figure 1-9 No latch for variable Trq.

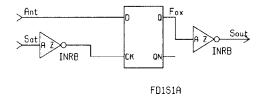

Here is an example where a latch is inferred for a variable.

```

wire Sat, Ant;

reg Fox, Sout;

...

always @ (Sat or Ant)

begin

if (! Sat)

Fox = Ant;

Sout = ! Fox;

end

```

The variable Fox is not assigned in the else-branch of the conditional statement. Consequently, a latch is inferred for Fox since it needs to retain its value when Sat is true. The circuit synthesized in shown in Figure 1-10.

How is a flip-flop inferred? It depends on the modeling style being followed and the context under which a variable is assigned a value. This

Figure 1-10 Variable Fox is a latch.

and other examples for flip-flop and latch inferencing are discussed in the next chapter. A memory in hardware can be modeled as an array of flip-flops or latches.

13

C HAPTER

# VERILOG CONSTRUCTS TO GATES

types and constants to hardware. This chapter describes the mapping of statements in Verilog HDL to logic gates in hardware. It also explains how operators, expressions and assignments are mapped to hardware. Each section of this chapter describes a particular synthesis construct or feature in a cookbook style for ease of reading and understanding. Most of the synthesized netlists are not optimized and do not represent minimal hardware.

#### 2.1 Continuous Assignment Statement

A continuous assignment statement represents, in hardware, logic that is derived from the expression on the right-hand-side of the assignment statement driving the net that appears on the left-hand-side of the assignment. The target of a continuous assignment is always a net driven by combinational logic.

Here is an example.

```

module Continuous (StatIn, StatOut);

input StatIn;

output StatOut;

assign StatOut = ~ StatIn; // Continuous assignment.

endmodule

// Synthesized netlist is shown in Figure 2-1.

```

Figure 2-1 Combinational circuit from continuous assignment statement.

The continuous assignment statement describes an inverter that has its input connected to *StatIn* and whose output is *StatOut*. Delays, if any, specified in a continuous assignment statement are usually ignored by a synthesis system. For example, in the continuous assignment:

```

assign #2 EffectiveAB = DriverA | DriverB;

```

the delay #2 is ignored for synthesis.

#### 2.2 Procedural Assignment Statement

A procedural assignment statement represents, in hardware, logic that is derived from the expression on the right-hand-side of the assignment statement driving the variable that appears on the left-hand-side of the assignment. Note that procedural assignments can appear only within an always statement<sup>1</sup>.

There are two kinds of procedural assignment statements:

- i. Blocking

- ii. Non-blocking

#### 2.2.1 Blocking Procedural Assignment

Here is an example of a blocking procedural assignment statement.

```

module Blocking (Preset, Count);

input [0:2] Preset;

output [3:0] Count;

reg [3:0] Count;

always @ (Preset)

Count = Preset + 1;

// Blocking procedural assignment.

endmodule

// Synthesized netlist is shown in Figure 2-2.

```

The blocking procedural assignment statement describes an adder that takes *Preset* and the integer 1 as inputs and places the result in the variable *Count*.

<sup>1.</sup> Procedural assignments can appear within an initial statement as well; however an initial statement is not supported for synthesis.

Figure 2-2 Combinational circuit from blocking procedural assignment.

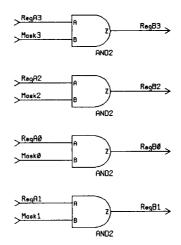

#### 2.2.2 Non-blocking Procedural Assignment

Here is an example of an non-blocking procedural assignment.

```

module NonBlocking (RegA, Mask, RegB);

input [3:0] RegA, Mask;

output [3:0] RegB;

reg [3:0] RegB;

always @ (RegA or Mask)

RegB <= RegA & Mask;

// Non-blocking procedural assignment.

endmodule

// Synthesized netlist is shown in Figure 2-3.</pre>

```

The blocking or non-blocking nature of an assignment does not cause any change to the combinational logic generated from the assignment state-

ment itself, but affects the use of the resultant value later on.

A good recommendation to follow is to use blocking assignments for modeling combinational logic and to use non-blocking assignments for modeling sequential logic; more on this is described in later sections.

The subtle differences between a blocking and a non-blocking procedural assignment are explored in section 2.18.

Figure 2-3 Combinational logic from non-blocking procedural assignment.

### 2.2.3 Target of Assignment

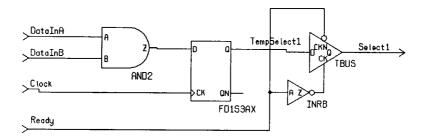

The target of a procedural assignment is synthesized into a wire, a flip-flop, or a latch, depending on the context under which the assignment appears in the Verilog HDL model. For example, if the previously described non-blocking procedural assignment statement appeared, say, under the control of a clock as shown in the following example, then the target is synthesized as a flip-flop.

```

module Target (Clk, RegA, RegB, Mask);

input Clk;

input [3:0] RegA, Mask;

output [3:0] RegB;

reg [3:0] RegB;

always @ (posedge Clk)

RegB <= RegA & Mask;

endmodule

// Synthesized netlist is shown in Figure 2-4.</pre>

```

Figure 2-4 Target of an assignment is a flip-flop.

# 2.2.4 Assignment Restrictions

Any kind of delay, delay control or intra-statement delay, specified in a procedural assignment (blocking or non-blocking) is ignored by a synthesis system. This can potentially lead to a functional mismatch between the design model and its synthesized netlist.

```

#5 RegB <= RegA & Mask;

// Delay control #5 is ignored.

RegB = #2 RegA & Mask;

// Intra-statement delay #2 is ignored.</pre>

```

There is another restriction on using both blocking and non-blocking assignments in a single model for synthesis.

A target cannot be assigned using a blocking assignment and a non-blocking assignment.

What this means is that if a target is assigned using a blocking (or a non-blocking) assignment, then the same target can only be assigned again using a blocking (or a non-blocking) assignment. Here is an example.

# 2.3 Logical Operators

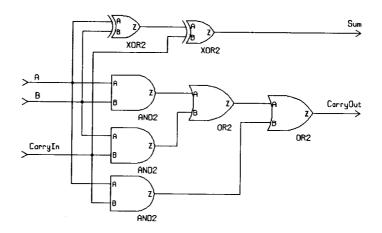

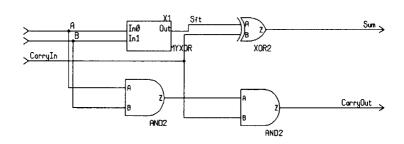

The logical operators get directly mapped onto primitive logic gates in hardware. Here is a model of a full-adder using continuous assignment statements.

Figure 2-5 Logical operators map to primitive logic gates.

# 2.4 Arithmetic Operators

In Verilog HDL, a reg type is interpreted as an unsigned number and an integer type is interpreted as a signed number in 2's complement form with the rightmost bit as the least significant bit. Thus, to synthesize an unsigned arithmetic operator, the reg type is used. To get a signed arithmetic operator, the integer type is used.

The net type is interpreted as unsigned numbers.

## 2.4.1 Unsigned Arithmetic

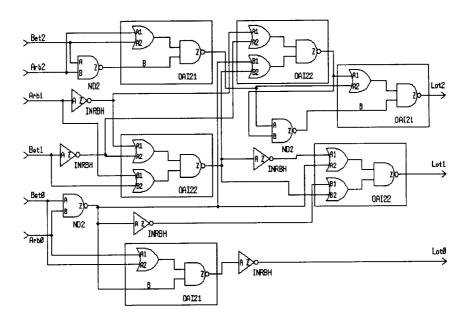

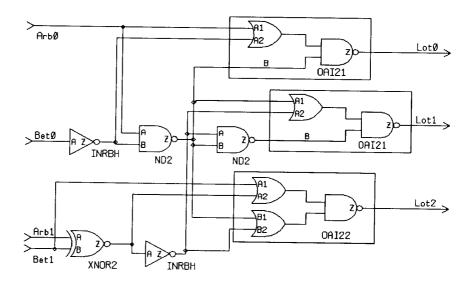

Here is an example that uses an arithmetic operator on unsigned numbers.

```

module UnsignedAdder (Arb, Bet, Lot);

input [2:0] Arb, Bet;

output [2:0] Lot;

assign Lot = Arb + Bet;

endmodule

// Synthesized netlist is shown in Figure 2-6.

```

Figure 2-6 A 3-bit adder.

In this example, a 3-bit adder is being modeled. The number system for the operands is unsigned since they are of the net type. The leftmost bit is the most significant bit.

## 2.4.2 Signed Arithmetic

Here is an example in which the operands are signed numbers. This is achieved by using the integer type.

```

module SignedAdder (Arb, Bet, Lot);

input [1:0] Arb, Bet;

output [2:0] Lot;

reg [2:0] Lot;

always @ (Arb or Bet)

begin: LABEL_A

// A sequential block requires a label if local

// declarations are present.

integer ArbInt, BetInt;

```

Figure 2-7 Signed adder.

Note that the adder logic with signed operands is the same as that with unsigned operands since the signed values are represented in 2's complement form.

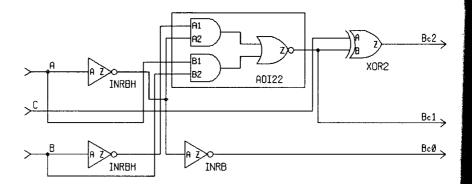

# 2.4.3 Modeling a Carry

It is natural to model a carry by simply using the result size to be one bit larger than the largest of the two operands. Alternatively, a concatenation could also be used as the target of an assignment with the carry bit explicitly specified. Here are examples of these.

```

wire [3:0] CdoBus, Sum;

wire [4:0] OneUp;

```

```

wire Bore:

assign OneUp = CdoBus + 1;

assign {Bore, Sum} = CdoBus - 2;

```

In the first continuous assignment, the result of the operation is five bits and OneUp[4] has the carry bit. If OneUp were declared as:

```

wire [3:0] OneUp;

```

then the carry bit would have been lost. In the second continuous assignment, *Bore* has the borrow bit of the subtraction operation.

#### 2.5 **Relational Operators**

The relational operators supported for synthesis are:

```

>, <, <=, >=

```

Relational operators can be modeled similar to arithmetic operators. In this case, the logic produced from synthesis is different depending on whether unsigned or signed numbers are being compared. If variables of a reg type or a net type are compared, an unsigned relational operator is synthesized. If integer variables are compared, then a signed relational operator is synthesized. Here is an example of a relational operator that is used with unsigned numbers.

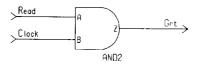

```

module GreaterThan (A, B, Z);

input [3:0] A, B;

output Z;

assign Z = A[1:0] > B[3:2];

// Variables A and B are of net type.

endmodule

// Synthesized netlist is shown in Figure 2-8.

```

Here is an example of synthesizing a signed relational operator. In this case, the operands for the relational operator are integer variables.

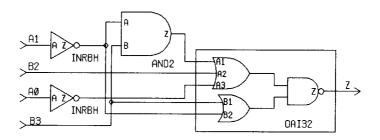

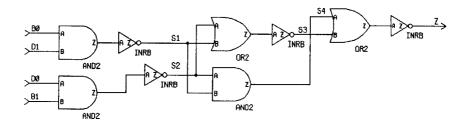

Figure 2-8 Unsigned ">" relational operator.

```

module LessThanEquals (ArgA, ArgB, ResultZ);

input [2:0] ArgA, ArgB;

output ResultZ;

reg ResultZ;

integer ArgAInt, ArgBInt;

always @ (ArgA or ArgB)

begin

ArgAInt = - ArgA;

ArgBInt = - ArgB;

// Store negative values just to show that the

// comparison is on signed numbers.

ResultZ = ArgAInt <= ArgBInt;

end

endmodule

// Synthesized netlist is shown in Figure 2-9.</pre>

```

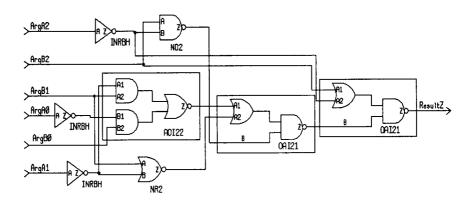

Figure 2-9 Signed "<=" relational operator.

## 2.6 Equality Operators

The equality operators supported for synthesis are:

```

==, !=

```

The operators === (case equality) and !== (case inequality) are not supported for synthesis.

Equality operators are modeled similar to arithmetic operators in terms of whether signed or unsigned comparison is to be made. Here is an example that uses signed numbers. Note that in this case, the operands of the equality operator are of integer type because values of this type represent signed numbers.

```

module NotEquals (A, B, Z);

input [0:3] A, B;

output Z;

reg Z;

always @ (A or B)

begin: DF_LABEL

integer IntA, IntB;

IntA = A;

```

```

IntB = B;

Z = IntA != IntB;

end

endmodule

// Synthesized netlist is shown in Figure 2-10.

```

Figure 2-10 Signed "!=" relational operator.

# 2.7 Shift Operators

Verilog HDL synthesis supports the left shift (<<) and the right shift (>>) operators. The vacated bits are filled with 0. The right operand, which is the amount of shift, may either be a constant or a variable. In both cases, combinational logic is produced. When shifting by a constant, simple rewiring is performed. When shifting by a variable, a general-purpose shifter is synthesized. This is shown in the following examples.

```

module ConstantShift (DataMux, Address);

input [0:3] DataMux;

output [0:5] Address;

assign Address = (~ DataMux) << 2;

endmodule

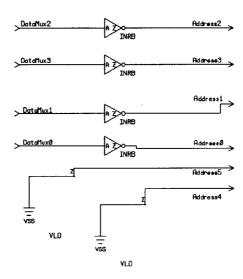

// Synthesized netlist is shown in Figure 2-11.</pre>

```

Figure 2-11 Constant shift.

```

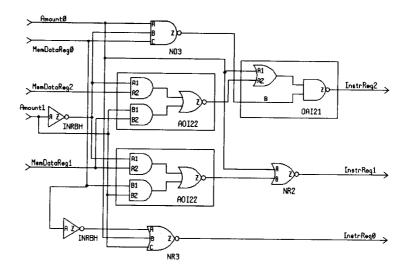

module VariableShift (MemDataReg, Amount, InstrReg);

input [0:2] MemDataReg;

input [0:1] Amount;

output [0:2] InstrReg;

assign InstrReg = MemDataReg >> Amount;

endmodule

// Synthesized netlist is shown in Figure 2-12.

```

As per Verilog HDL rules, when performing the left shift operation in module *ConstantShift*, the shifted bits from *DataMux* are not discarded but simply move into the higher order bits of *Address*. If *Address* were the same size as *DataMux*, then the high-order bits get shifted out and discarded.

Figure 2-12 Variable shift.

# 2.8 Vector Operations

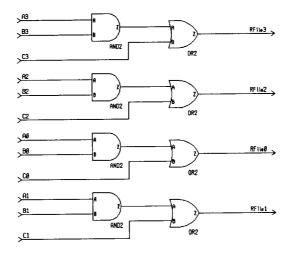

This example shows that vector operands can be used in expressions. The four bits of A are and'ed with the four bits of B, the result of which is or'ed with the four bits of C. The result is assigned (starting with the rightmost bit) to the target net RFile.

```

module VectorOperations (A, B, C, RFile);

input [3:0] A, B, C;

output [3:0] RFile;

assign RFile = (A & B) | C;

endmodule

// Synthesized netlist is shown in Figure 2-13.

```

Here is another example where the operands of a logical operator are vectors. In such a case, a series of logic gates to cover the range of the vector are produced.

Figure 2-13 Vector operations.

```

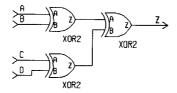

module VectorOperands (Bi, Stdy, Tap);

input [0:3] Bi, Stdy;

output [0:3] Tap;

assign Tap = Bi ^ Stdy;

endmodule

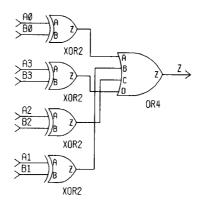

// Synthesized netlist is shown in Figure 2-14.

```

Four exclusive-or gates are synthesized since each operand in the right-hand-side is of size 4.

In the above examples on continuous assignments, there is a one-toone correlation between a continuous assignment statement and its synthesized logic. This is because a continuous assignment implicitly describes the structure.

Figure 2-14 A bank of logic gates.

## 2.9 Part-selects

Operations using part-selects can be used in a model. Here is an example.

```

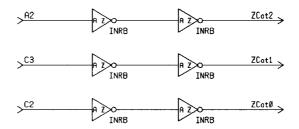

module PartSelect (A, C, ZCat);

input [3:0] A, C;

output [3:0] ZCat;

assign ZCat[2:0] = {A[2], C[3:2]};

endmodule

// Synthesized netlist is shown in Figure 2-15.

```

ZCat[2:0] and C[3:2] are examples of part-selects. Non-constant part-selects are not supported in Verilog HDL.

Figure 2-15 Part-select example.

### 2.10 Bit-selects

A bit-select can be a constant index or a non-constant index.

### 2.10.1 Constant Index

Here is an example that uses constant values for bit-select indices.

```

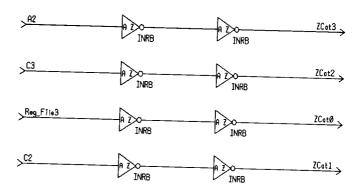

module ConstantIndex (A, C, Reg_File, ZCat);

input [3:0] A, C;

input [3:0] Reg_File;

output [3:0] ZCat;

assign ZCat[3:1] = {A[2], C[3:2]};

assign ZCat[0] = Reg_File[3];

endmodule

// Synthesized netlist is shown in Figure 2-16.

```

A[2], ZCat[0] and  $Reg\_File[3]$  are examples of bit-selects. The concatenation operator,  $\{\ \}$ , is used to generate a bigger array.

Figure 2-16 Constant bit-select.

# 2.10.2 Non-constant Index in Expression

It is possible to use a non-constant as an index in a bit-select as shown in the following model.

```

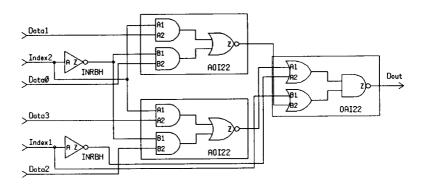

module NonComputeRight (Data, Index, Dout);

input [0:3] Data;

input [1:2] Index;

output Dout;

assign Dout = Data [Index];

endmodule

// Synthesized netlist is shown in Figure 2-17.

```

In this case, a multiplexer is generated as shown in the synthesized netlist.

Figure 2-17 Non-constant bit-select generates a multiplexer.

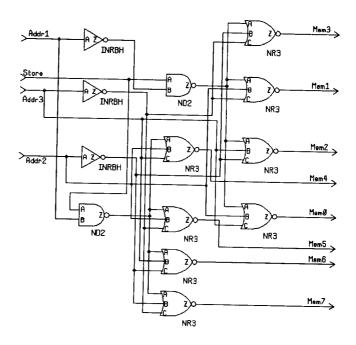

## 2.10.3 Non-constant Index in Target

Here is another example of a non-constant bit-select; this time it is used on the left-hand-side of an assignment. A decoder is synthesized for this behavior.

```

module NonComputeLeft (Mem, Store, Addr);

output [7:0] Mem;

input Store;

input [1:3] Addr;

assign Mem [Addr] = Store;

endmodule

// Synthesized netlist is shown in Figure 2-18.

```

Figure 2-18 A decoder generated from a non-constant bit-select.

# 2.11 Conditional Expression

A conditional expression selects between two expressions according to the value of a condition.

```

<condition> ? <expression1> : <expression2>

```

If the condition is true, select the first expression, else select the second. Here is an example.

Figure 2-19 Logic generated from a conditional expression.

## 2.12 Always Statement

An always statement is used to model the procedural behavior of a circuit. Here is an example of an always statement that contains procedural assignment statements.

```

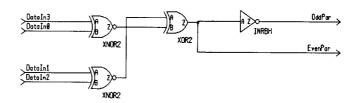

module EvenParity (A, B, C, D, Z);

input A, B, C, D;

output Z;

reg Z, Temp1, Temp2;

always @(A or B or C or D)

begin

Temp1 = A ^ B;

Temp2 = C ^ D;

Z = Temp1 ^ Temp2;

// Note that the temporaries are really not

// required. They are used here to illustrate the

// sequential behavior of the statements within

// the sequential block.

end

```

### endmodule

// Synthesized netlist is shown in Figure 2-20.

Figure 2-20 Procedural assignment statements.

All variables whose values are read in the always statement must appear in the event list (the parenthesized list following the "@" symbol); otherwise the functionality of the synthesized netlist may not match that of the design model. Here is a simple example that illustrates this point.

```

module AndBehavior (Z, A, B);

input A, B;

output Z;

reg Z;

always @ (B)

Z = A & B;

endmodule

// Synthesized netlist is shown in Figure 2-21.

```

Figure 2-21 Incomplete event list.

The semantics of the always statement specifies that whenever an event occurs on B, the assignment is to be executed and Z gets a value. If any events occur on A, this has no impact on the value of Z. However, the synthesized netlist of the above module, shown in Figure 2-21, shows an and gate. Here any time A or B changes, the value of Z is updated. Hence a

functional mismatch occurs. A synthesis system usually would issue a warning about such missing variables in the event list.

A good practice is to include all variables read in the always statement in the event list; this is true only when modeling combinational logic. When modeling sequential logic, a different kind of event list is required; this is described later.

A variable declared within an always statement holds a temporary value and does not necessarily infer a unique wire in hardware as the following example shows.

```

module VariablesAreTemporaries (A, B, C, D, Z);

input A, B, C, D;

output Z;

reg Z;

always @ (A or B or C or D)

begin: VAR_LABEL

integer T1, T2;

T1 = A & B;

T2 = C & D;

T1 = T1 | T2;

Z = ~ T1;

end

endmodule

// Synthesized netlist is shown in Figure 2-22.

```

Figure 2-22 One variable can represent many wires.

### CHAPTER 2 Verilog Constructs to Gates

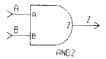

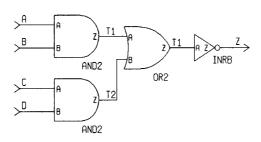

In the synthesized netlist, the output of the AND2 gate is the variable T1; so is the output of the OR2 gate. In this example, each assignment to the integer variable infers a unique wire.

## 2.13 If Statement

An if statement represents logic that is conditionally controlled. Here is an example.

```

module SelectOneOf (A, B, Z);

input [1:0] A, B;

output [1:0] Z;

reg [1:0] Z;

always @ (A or B)

if (A > B)

Z = A;

else

Z = B;

endmodule

// Synthesized netlist is shown in Figure 2-23.

```

Figure 2-23 Logic derived from an if statement.

Here is another example of an if statement.

```

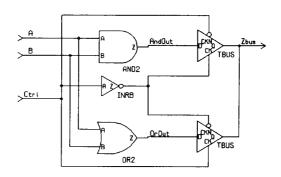

module SimpleALU (Ctrl, A, B, Z);

input Ctrl;

input [0:1] A, B;

output [0:1] Z;

reg [0:1] Z;

always @ (Ctrl or A or B)

if (Ctrl)

Z = A & B;

else

Z = A | B;

endmodule

// Synthesized netlist is shown in Figure 2-24.

```

Figure 2-24 Conditional selection of operations.

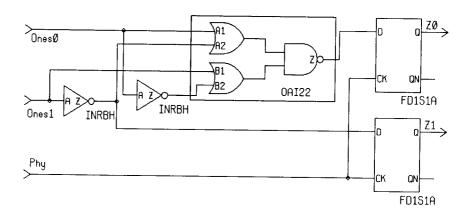

## 2.13.1 Inferring Latches from If Statements

Consider the always statement in the following module.

```

module Increment (Phy, Ones, Z);

input Phy;

input [0:1] Ones;

output [0:2] Z;

reg [0:2] Z;

```

```

always @ (Phy or Ones)

if (Phy)

Z = Ones + 1;

```

#### endmodule

// Synthesized netlist is shown in Figure 2-25.

Figure 2-25 A variable is synthesized as a latch.

The semantics of the always statement specifies that every time an event occurs on *Phy* or *Ones* (variables present in the event list), the if statement executes and the variable *Z* gets the value of *Ones* incremented by 1 if *Phy* is a 1. If *Phy* is a 0, the value in *Z* is retained; this is done using latches.

A general rule for latch inferencing is that if a variable is not assigned in all possible executions of an always statement (for example, when a variable is not assigned in all branches of an if statement), then a latch is inferred.

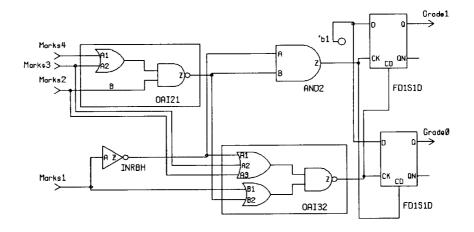

Here is another example of a variable that is not assigned in all branches of an if statement.

```

module Compute (Marks, Grade);

input [1:4] Marks;

output [0:1] Grade;

reg [0:1] Grade;

```

```

parameter FAIL = 1, PASS = 2, EXCELLENT = 3;

always @ (Marks)

if (Marks < 5)

Grade = FAIL;

else if ((Marks >= 5) & (Marks < 10))

Grade = PASS;

endmodule

// Synthesized netlist is shown in Figure 2-26.</pre>

```

Figure 2-26 A variable is inferred as a latch.

In this example, what should be the value of *Grade* if *Marks* has the value 12? It may be intended to be a don't care, but from the language semantics viewpoint, the variable *Grade* retains its last value, since no value is assigned to the variable explicitly when *Marks* has the value 12. Therefore a latch is inferred for *Grade* in keeping with the simulation semantics of a reg variable.

Arithmetic operations as conditional expressions, as in the previous example, should be avoided when inferring latches since there is a very high probability of race condition between the conditionals in the synthesized netlist; this might cause the latched value in the synthesized netlist to differ from that in the Verilog HDL model.

If a variable is not assigned in all branches of an if statement, and the intention is not to infer a latch, then the variable must be assigned a value

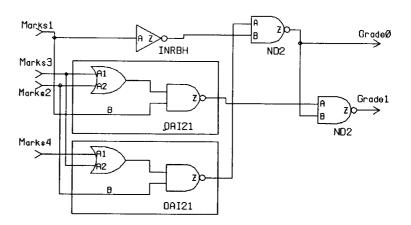

explicitly in all the branches of the if statement. If the previous example is modified by specifying the assignment to the variable in all branches, the following program is obtained.

```

module ComputeNoLatch (Marks, Grade);

input [1:4] Marks;

output [0:1] Grade;

reg [0:1] Grade;

parameter FAIL = 1, PASS = 2, EXCELLENT = 3;

always @ (Marks)

if (Marks < 5)

Grade = FAIL;

else if ((Marks >= 5) && (Marks < 10))

Grade = PASS;

else

Grade = EXCELLENT;

endmodule

// Synthesized netlist is shown in Figure 2-27.</pre>

```

Figure 2-27 Variable GRADE is not a latch.

In this case, variable *GRADE* is not a latch because it is assigned a value in all branches of the if statement.

### 2.14 Case Statement

A case statement is of the form:

The first branch that has a case item whose value matches the value of the case expression is selected. A case item may be a constant or a variable.

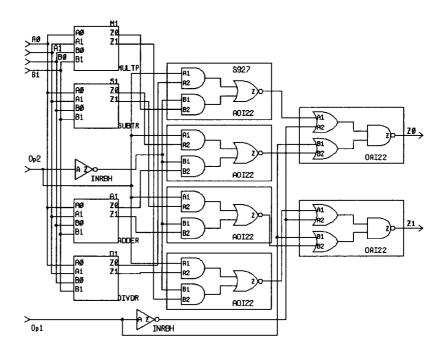

Here is an example of a case statement.

```

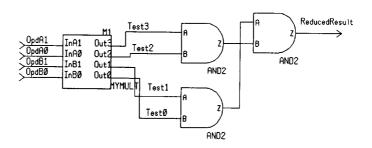

module ALU (Op, A, B, Z);

input [1:2] Op;

input [0:1] A, B;

output [0:1] Z;

reg [0:1] Z;

parameter ADD = 'b00, SUB = 'b01, MUL = 'b10,

DIV = 'b11;

always @ (Op or A or B)

case (Op)

ADD :

Z = A + B;

SUB :

Z = A - B;

MUL : Z = A * B;

DIV :

Z = A / B; // The A/B operation may not be

// supported by some synthesis tools.

endcase

endmodule

// Synthesized netlist is shown in Figure 2-28.

```

A case statement behaves like a nested if statement, that is, the value of the case expression (Op) is checked with the first case item (ADD), if it does not match, the second case item (SUB) is checked and so on. The equivalent if statement for the above case statement is shown next.

Figure 2-28 A 2-bit ALU.

```

if (Op == ADD)

Z = A + B;

else if (Op == SUB)

Z = A - B;

else if (Op == MUL)

Z = A * B;

else if (Op == DIV)

Z = A / B;

```

Here is another example of a case statement.

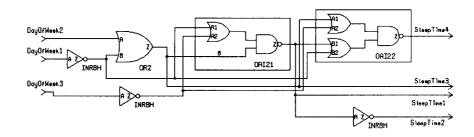

```

always @ (DayOfWeek)

case (DayOfWeek)

MON.

TUE.

WED.

SleepTime = 6:

THU:

FRI: SleepTime = 8;

SAT:

SleepTime = 9;

SUN:

SleepTime = 7;

default: SleepTime = 10:

// Enjoy!

// The default covers the case when DayOfWeek

// has value 7.

endcase

endmodule

// Synthesized netlist is shown in Figure 2-29.

```

Figure 2-29 A case statement example.

Here is another example of a case statement.

```

WAITS: RF1ag = APPLY;

default : RF1ag = DONTCARE;

endcase

endmodule

// Synthesized netlist is shown in Figure 2-30.

```

Figure 2-30 Logic generated from a case statement.

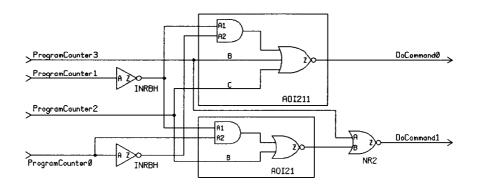

### 2.14.1 Casez Statement

In a casez statement, the value z is considered as a don't-care when it appears in a case item expression. The ? character can also be used alternatively for the character z. Values z and x are not allowed in a case expression. Additionally, value x cannot appear in a case item expression. Here is an example of a casez statement.

Figure 2-31 Casez statement example.

The casez statement is equivalent to the following if statement (note that the? character in a case item denotes a don't-care value).

```

if (ProgramCounter [3])

DoCommand = 0;

else if (ProgramCounter [2:3] == 2'b10)

DoCommand = 1;

else if (ProgramCounter [1:3] == 3'b100)

DoCommand = 2;

else if (ProgramCounter [0:3] == 4'b1000)

DoCommand = 3;

else

DoCommand = 0;

```

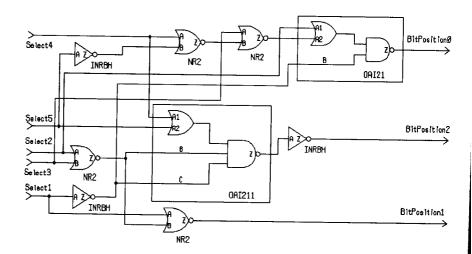

### 2.14.2 Casex Statement

In a casex statement, the values x and z (? for a z is ok too) in a case item expression are considered as don't-care values. These values, for synthesis purposes, cannot appear as part of the case expression. Here is an example of a casex statement used to model a priority encoder.

```

module PriorityEncoder (Select, BitPosition);

input [5:1] Select;

output [2:0] BitPosition;

reg [2:0] BitPosition;

always @ (Select)

casex (Select)

```

### CHAPTER 2 Verilog Constructs to Gates

```

5'bxxxx1 : BitPosition = 1;

5'bxxx1x : BitPosition = 2;

5'bxx1xx : BitPosition = 3;

5'bx1xxx : BitPosition = 4;

5'b1xxx : BitPosition = 5;

default : BitPosition = 0;

endcase

endmodule

// Synthesized netlist is shown in Figure 2-32.

```

Figure 2-32 A priority encoder using casex statement.

The semantics of this casex statement can best be expressed by its equivalent if statement.

```

if (Select [1])

BitPosition = 1;

else if (Select [2])

BitPosition = 2;

else if (Select [3])

BitPosition = 3;

else if (Select [4])

BitPosition = 4;

else if (Select [5])

BitPosition = 5;

```

```

else

BitPosition = 0;

```

### 2.14.3 Inferring Latches from Case Statements

A latch may be inferred for a variable assigned in a case statement, just like in an if statement. If a variable is not assigned a value in all possible executions of the always statement, such as when a variable is assigned a value in only some branches of a case statement, a latch is inferred for that variable. See the following example.

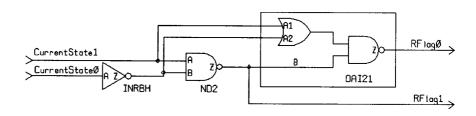

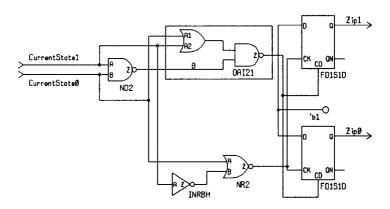

```

module StateUpdate (CurrentState, Zip);

input [0:1] CurrentState;

output [0:1] Zip;

reg [0:1] Zip;

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3;

always @ (CurrentState)

case (CurrentState)

S0,

S3: Zip = 0;

S1: Zip = 3;

endcase

endmodule

// Synthesized netlist is shown in Figure 2-33.

```

Figure 2-33 Latch inferred for a variable in a case statement.

The variable Zip is not assigned a value for all possible values of the input CurrentState. Therefore in keeping with the language semantics of a reg variable, a latch is inferred for Zip. The synthesized netlist shows the latch. In terms of latch inferencing, a case statement behaves identical to an if statement. If a latch is to be avoided, insert an initial value assignment to Zip before the case statement, as shown in the following code. The explicit assignment to Zip causes it to be defined for all values of CurrentState, and consequently for all possible executions of the always statement.

```

always @ (CurrentState)

begin

Zip = 0; // This statement added.

case (CurrentState)

...

endcase

end

```

The rules for inferring latches apply to casex and casez statements equally as well.

### **2.14.4** Full Case

In the previous section, we saw that a latch may be inferred for a variable that is not assigned a value for all possible values of a case expression. Sometimes it is the case that the designer does not expect the case expression to have any value other than those listed in the case items. Here is an example.

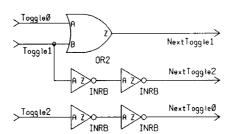

```

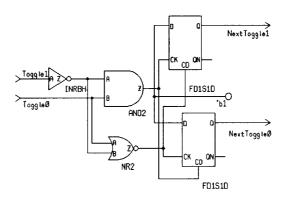

module NextStateLogic (NextToggle, Toggle);

input [1:0] Toggle;

output [1:0] NextToggle;

reg [1:0] NextToggle;

always @ (Toggle)

case (Toggle)

2'b01 : NextToggle = 2'b10;

2'b10 : NextToggle = 2'b01;

endcase

```

### endmodule

// Synthesized netlist is shown in Figure 2-34.

Figure 2-34 Latches are inferred for NextToggle.

The designer knows that *Toggle* cannot have any value other than 2'b01 and 2'b10. This information needs to be passed to the synthesis tool. If such information is not provided to the synthesis tool, latches are inferred for *NextToggle* (the two FD1S1D's in Figure 2-34) since it is not assigned a value for the case expression values 2'b00 and 2'b11. Such information is passed to a synthesis tool via a synthesis directive called *full\_case*. A *synthesis directive* is a special code in the model that provides additional information to a synthesis tool. The full\_case synthesis directive is specified as a Verilog HDL comment in the model associated with the case statement; since the synthesis directive appears as a comment, it has no effect on the language semantics of the model.

A synthesis tool on encountering such a directive on a case statement understands that all possible values (that can occur in the design) of the case expression have been listed and no other values are possible. Consequently, a variable assigned in all branches of the case statement will never infer a latch. Here is the case statement in the *NextStateLogic* module with the directive specified.

```

module NextStateLogicFullCase (NextToggle, Toggle);

input [1:0] Toggle;

output [1:0] NextToggle;

reg [1:0] NextToggle;

```

Figure 2-35 With full\_case synthesis directive: no latches.

As the synthesized netlist shows, no latches are inferred for *NextToggle* when the full\_case synthesis directive is used.

An alternative way to avoid latches in the above example is to specify a default branch in the case statement or to make a default assignment to all variables assigned in a case statement (in this example, NextToggle), prior to the case statement. Here is an example that uses a default branch to avoid inferring latches.

```

always @ (Toggle)

case (Toggle)

2'b01 : NextToggle = 2'b10;

2'b10 : NextToggle = 2'b01;

default : NextToggle = 2'b01; // Dummy assignment.

endcase

```

Here is the always statement that has a default assignment for NextToggle; no latches are inferred for NextToggle.

```

always @ (Toggle)

begin

```

```

NextToggle = 2'b01;  // Default assignment.

case (Toggle)

2'b01 : NextToggle = 2'b10;

2'b10 : NextToggle = 2'b01;

endcase

end

```

Caution, use of the full\_case directive can potentially lead to a functional mismatch between the design model and the synthesized netlist; see Chapter 5 for such examples.

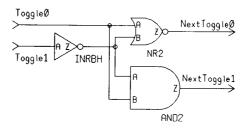

### 2.14.5 Parallel Case

Verilog HDL semantics of a case statement specifies a priority order in which a case branch is selected. The case expression is checked with the first case item, if it is not the same, the next case item is checked, if not the same, the next case item is checked, and so on. A priority order of case item checking is implied by the case statement. Additionally, in Verilog HDL, it is possible for two or more case item values to be the same or there may be overlapping case item values such as in casex and casez statements; however, because of the priority order, only the first one in the listed sequence of case items is selected.

To apply the strict semantics of a case statement in synthesis to hardware, a nested if-like structure (priority logic: if this do this, else if this do this, else . . .) is synthesized. Here is an example of a case statement.

Figure 2-36 Priority logic selects each branch.

The equivalent behavior of the case statement is expressed in the following if statement.

```

if (Toggle[0] == 'b1)

NextToggle = 3'b010;

else if (Toggle[1] == 'b1)

NextToggle = 3'b110;

else if (Toggle[2] == 'b1)

NextToggle = 3'b001;

else

NextToggle = 3'b000;

```

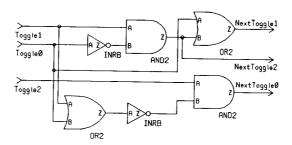

What if the designer knows that all case item values are mutually exclusive? In such a case, a decoder can be synthesized for a case statement control (the case expression is checked for all possible values of the case item values in parallel) instead of the priority logic (which could potentially be nested deep depending on the number of branches in the case statement).

The information that all case item values are mutually exclusive needs to be passed to the synthesis tool. This is done by using a synthesis directive called parallel\_case. When such a directive is attached to a case statement, a synthesis tool interprets the case statement as if all case items are mutually exclusive. Since the synthesis directive appears as a comment in the Verilog HDL model, it has no effect on the language semantics of the model. This implies that no priority logic is synthesized for the case statement control; instead decoding logic is used. Here is the case statement with the parallel\_case directive.

Figure 2-37 With parallel\_case directive: no priority logic.

The equivalent synthesis interpretation for the case statement is as follows (with only one if condition guaranteed to be true).

```

(Toggle[2] != 'b1))

NextToggle = 3'b000;

```

With the synthesis directive, decoding logic is synthesized for the branching logic as shown in Figure 2-37. Without the synthesis directive, priority logic is synthesized as shown in Figure 2-36.

A word of caution. The synthesis directive, parallel\_case, can potentially cause a functional mismatch between the design model and the synthesized netlist; Chapter 5 elaborates on this further.

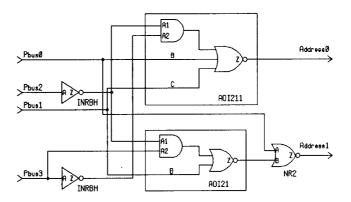

### 2.14.6 Non-constant as Case Item

In Verilog HDL, it is possible to have a non-constant expression as a case item. This is shown in the following example of a priority encoder.

It is necessary to specify the full\_case synthesis directive, otherwise latches are inferred for *Address*. Alternatively, an initial assignment to *Address* before the case statement can also be made to avoid latches; no synthesis directive is then necessary. This is shown in the following always statement.

```

always @ (Pbus)

begin

Address = 2'b00;

```

Figure 2-38 Priority encoder using case statement.

```

case (1'b1)

Pbus[0] : Address = 2'b00;

Pbus[1] : Address = 2'b01;

Pbus[2] : Address = 2'b10;

Pbus[3] : Address = 2'b11;

endcase

end

```

### 2.15 More on Inferring Latches

A latch can be inferred by using an incompletely specified if statement or a case statement, that is, if a variable is not assigned a value in all branches of an if statement or a case statement, a latch is inferred for that variable. Here is an example.

```

module LatchExample (ClockA, CurrentState, NextState);

input ClockA;

input [3:0] CurrentState;

output [3:0] NextState;

reg [3:0] NextState;

always @ (ClockA or CurrentState)

if (ClockA)

NextState = CurrentState;

```

#### endmodule

// Synthesized netlist is shown in Figure 2-39.

Figure 2-39 An incompletely specified condition infers a latch.

The variable *NextState* is assigned a value only when *ClockA* is 1. If *ClockA* is 0, *NextState* retains its previous value, thus inferring a latch.

### **Locally Declared Variable**

A variable declared locally within an always statement is also inferred as a latch if it is incompletely assigned in a conditional statement (if statement or case statement). This is shown in the following module.

```

module LocalIntLatch (Clock, CurrentState, NextState);

input Clock;