# PROCESSOR BASICS

In this chapter we start our focus on embedded systems with an introduction to the kinds of processors that are used. We describe the way processors operate and give examples of the instructions that make up embedded software programs. We also describe the way instructions and data are encoded in binary and stored in memory. Finally, we examine ways of connecting the processor with memory components.

## 7.1 EMBEDDED COMPUTER ORGANIZATION

In Section 1.5.1, we introduced the idea of an embedded system, in which one or more computers form part of the system. The computers run programs that implement the functions required of the system. Unlike a general-purpose PC, a computer in an embedded system has just those resources required to support its specialized operation. In this section, we will describe some of the general properties of embedded systems and the processing elements they contain. We won't deal with how the processing elements are designed; that is a significant field of study in its own right. Instead, we will treat them as black-box circuit components that we can use to build a digital system.

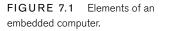

A computer embedded in a digital system generally contains the elements shown in Figure 7.1. The *central processing unit* (CPU), often called a *processor core* when it is embedded as part of an IC, is the element that processes data according to a program. The kinds of processing it can perform include the arithmetic operations that we described in Chapter 3. It can also evaluate logical conditions and select among alternate operations based on the outcomes of the conditions. We will describe the way a program is formed in more detail in Section 7.2. Meanwhile, suffice it to say that the program is encoded in binary form and stored in the *instruction memory* shown in the figure. The data upon which the program operates are also encoded in binary form and stored in the *data*

*memory*. In both cases, the memory is implemented using the kinds of memory components we described in Chapter 5. Whereas general purpose computers, such as PCs, usually store the instructions and data in the same memory, embedded computers typically separate the two. (This arrangement is often referred to as a Harvard architecture, named after the institution where the idea originated. The conventional approach with a single memory for instructions and data is called a von Neumann architecture, after the person who first described it.) The reason for the separation is that the instructions in an embedded computer are usually fixed during the manufacture of the system (or only occasionally upgraded in the field), and the amount of instruction memory required is known in advance. Hence, we usually store instructions in a ROM or flash memory component, and provide a RAM for the data memory. This differs from a general-purpose computer, in which one or more different programs need to be started at different times and run concurrently, and the amount of instruction memory is not known in advance.

The *input*, *output* and *input/output* (I/O) controllers in Figure 7.1 allow the computer to acquire data to be processed (input) and to deliver the results (output). In many embedded systems, the input data comes from sensors that sample physical properties, such as temperature, position, time, and so on. Similarly, the output data causes actuators to have a physical effect, such as moving a lever, turning a motor, heating some material, and so on. Input and output controllers can also deal with a user interface, consisting of switches, buttons and knobs for input and lights and LCD panels for outputs. For a complex user interfaces, devices such as a keyboard, mouse or display screen, as used in a general purpose computer, might also be employed. In all cases, the job of the input/output controller is to transform between a physical property or effect and a corresponding binary representation that can be processed by the CPU. We will describe how this can be done and how the CPU accesses the binary representation in Chapter 8.

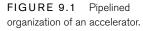

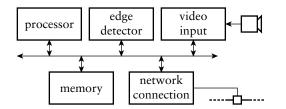

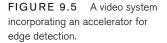

The *accelerator* in Figure 7.1 is a specialized circuit designed to implement specific processing operations with higher performance than can be achieved using the CPU. Not all embedded systems include

accelerators. The choice of whether to include an accelerator for any operation depends on the functional and performance requirements of the application, together with cost and other constraints that apply. We will discuss accelerators in more detail in Chapter 9, in which we include as an extended example an accelerator for detecting edges of objects in video images.

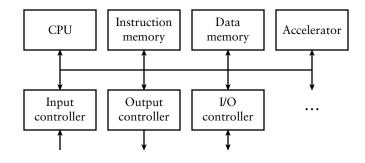

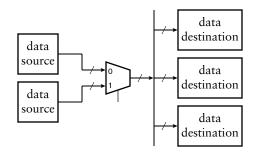

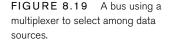

The final element in Figure 7.1 is the interconnection between the other elements. We use the term *bus* to refer to the collection of signals that form the interconnection. The figure shows just one bus connecting all of the elements. However, in more elaborate systems, there may be separate buses for connecting the memory and the input/output controllers with the CPU. There may even be separate buses for the instruction and data memories, since many high-performance processors can read further instructions concurrently with access to data by previous instructions. Accelerators, if included, might be connected to the CPU using the same bus as the memory, or using a separate dedicated bus. Figure 7.2 shows one possible organization for a high-performance embedded system with multiple buses. In this chapter, we will focus on the bus connecting the CPU and memory, and defer consideration of bus connections to input and output controllers and to accelerators until later chapters.

#### 7.1.1 MICROCONTROLLERS AND PROCESSOR CORES

CPUs for embedded systems come in a range of sizes for different applications. Some are single-chip *microprocessors*, consisting of a CPU by itself in a package. Most CPUs used in general-purpose PCs are also available in versions suitable for embedded applications. Examples include Pentium family CPUs from Intel and the PowerPC from Freescale Semiconductor. Other microprocessors are designed specifically for embedded applications. In both cases, we need to provide memory and I/O controllers as separate chips on a PCB. In contrast, single-chip *microcontrollers* include a CPU, instruction and data memory, and I/O controllers all in the one package. Many microcontroller vendors provide a family of chips, each with the same CPU, but varying in the amount of memory and the selection of I/O controllers. In some microcontroller families, the CPUs are relatively simple, operating just on 8-bit or 16-bit data, with relatively low performance. Other families have more complex CPUs that can operate on data up to 32 bits in length. The combination of a CPU with the on-chip memory and I/O controllers makes them suitable for a large range of costsensitive, low-performance applications.

An alternative to using a fixed function microprocessor or microcontroller is to include a CPU in an FPGA component. This has the advantage that the input/output controllers can be customized for an application, but still be included in the same package as the CPU. The CPU in the FPGA can be implemented as a fixed-function block embedded within the programmable fabric. The Virtex-II Pro and Virtex 4 FPGAs from Xilinx take this approach, and include one or more PowerPC processor cores. Alternatively, the CPU can be implemented as a soft core using the programmable resources of the FPGA. FPGA vendors provide soft core processor designs that users can include as part of their system. Examples include the MicroBlaze core from Xilinx, the Nios-II core from Altera, and the ARM core from Actel. These are all relatively high-performance CPUs that operate on data up to 32 or 64 bits in length. For simpler designs, a smaller soft core that operates on 8-bit data may suffice. It would take up less of the FPGA resources, and would fit in a smaller and cheaper FPGA component. The Xilinx PicoBlaze soft core is an example, as is the Gumnut core that we will introduce in Section 7.2.

If our design is implemented in an ASIC, we can also include a CPU and customized memory and input/output controllers. Several vendors provide processor core designs that can be included as blocks in ASICs. Among the most widely used are the ARM cores from ARM Ltd, the PowerPC cores from IBM, and the MIPS cores from MIPS Technologies. Given that we can customize the design on an ASIC, there is also opportunity to customize the CPU itself. Tensilica Inc. is a vendor that provides a customizable CPU based on the requirements of the program to be executed. Their approach involves analyzing the program and including only the CPU features needed to execute that program. They also allow extension of the CPU with customized hardware for specialized operations.

A final approach to mention is to include one or more *digital signal processors* (DSPs). These are specialized processing elements optimized for the kinds of operations involved in dealing with digitized signals, such as audio, video or other streams of data from sensors. Many signal processing applications require fixed-point or floating-point arithmetic operations to be performed at a high rate on large volumes of data. An ordinary CPU

would not be able to meet the performance requirements. Nonetheless, such applications often need a conventional CPU to perform other operations, such as interacting with the user and overall coordination of system operation. Hence, DSPs are often combined with conventional CPUs in heterogeneous *multiprocessor* systems. Modern cell phones are good examples. Another approach to providing DSP functionality is to extend a conventional CPU with additional hardware and instructions for digital signal processing. Some processor cores from ARM and MIPS include such extensions, and Tensilica processor cores can be similarly customized. Since digital signal processing is an advanced topic, we will defer consideration of DSP cores and embedded multiprocessor systems to advanced reference books.

- 1. What are the main elements of an embedded computer?

- 2. Why do embedded computers usually have separate instruction and data memories?

- 3. What is the difference between a microprocessor and a microcontroller?

- 4. What is meant by a *soft core* processor in an FPGA?

## 7.2 INSTRUCTIONS AND DATA

The function performed by a CPU is specified by a program, which consists of a sequence of instructions. Each instruction specifies one simple step in the program, such as getting a piece of data from memory, or adding two numbers. The repertoire of instructions for a given CPU is called the *instruction set* of the CPU. We also use the term *instruction set* architecture (ISA) to refer to the combination of the instruction set and other aspects of the CPU that are visible to the programmer. CPUs from different vendors have quite significantly different instruction sets, so a sequence of instructions developed for one CPU will not work on a CPU from a different vendor. When we develop the program for an application, we usually use a *high-level language*, such as C, C++ or Ada, and use a software tool called a *compiler* to translate the program into a sequence of instructions that performs the same operations. Apart from allowing us to work at a higher level of abstraction, this has the advantage that the program can be ported to work on a CPU with a different instruction set simply by using a different translator. However, when we are developing an embedded system in which the CPU interacts with circuits that we design, we often need to monitor the instruction-by-instruction operation of the CPU as we test and debug the design. At this level, it is important to understand how a CPU represents and processes individual instructions. We will just describe CPU operation at this level, and defer a discussion of programming using high-level languages to other books.

## KNOWLEDGE TEST QUIZ

The instructions of a program are encoded in binary and stored in successive locations of the instruction memory. The CPU *executes* the program by repeatedly following these steps:

- 1. *Fetch* the next instruction from the instruction memory.

- 2. Decode the instruction to determine the operation to perform.

- 3. *Execute* the operation.

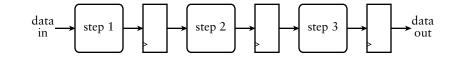

In order to keep track of which instruction to fetch next, the CPU has a special register called the program counter (PC), in which the address of the next instruction is kept. In the fetch step, the CPU uses the contents of the PC to do a read access from the instruction memory, and then increments the PC value. In the decode step, the CPU determines the resources required to perform the operation specified by the instruction. In a simple CPU, the decode step is correspondingly simple. In a larger CPU, however, decoding may involve such actions as checking for resource conflicts and availability of data, and waiting until resources are free. In the execute step, the CPU activates the appropriate internal resources to perform the operation. This involves setting control signals to make multiplexers supply the required operands and arithmetic hardware perform the required operation, and enabling registers to receive results. In a simple CPU, these steps are performed in order, and when the execute step is finished, the CPU starts again with the fetch step. More complex, high performance CPUs, however, can overlap the steps, provided they produce the same outcome as if the steps were performed in order. Techniques used within CPUs to execute several instructions in parallel include *pipelining* and superscalar execution, described in the reference book on computer architecture (see Section 7.5).

The data on which instructions operate is encoded in binary in fixedsize quantities. The smallest data item is usually 8 bits, called a *byte*. It is often used to represent an unsigned or a signed integer, or a character. Simple CPUs can only operate on 8-bit data, so they are referred to as 8-bit CPUs. Larger CPUs can operate on 16-bit or 32-bit *words* of data, as well as on 8-bit data, so they are referred to as 16-bit or 32-bit CPUs, respectively.

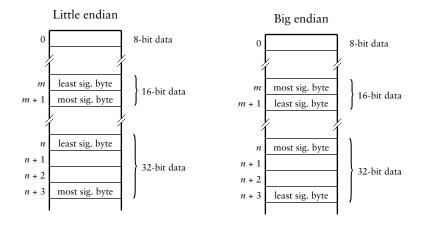

Regardless of the sizes of data that can be operated upon, the data memory is usually organized with 8-bit locations, each separately addressed. 16-bit or 32-bit data is stored in two or four successive locations. The order of the bytes within a word varies between CPUs, as shown in Figure 7.3. *Little-endian* CPUs store the byte containing the least significant bits at the lower address and the byte containing the most significant bits at the higher address. In contrast, *big-endian* CPUs store the bytes in the opposite order. (The terms "little endian" and "big endian" originated in Jonathan Swift's *Gulliver's Travels*, in which the people of two countries fight over which end of their breakfast eggs should be cut open.

FIGURE 7.3 Little-endian (left) and big-endian (right) memory layout for data words.

The terms were adopted by Danny Cohen in an article, cited in Section 7.5, in which he argues that either byte ordering is acceptable, provided it is used consistently.) Some CPUs require that 16-bit data be stored at even addresses and that 32-bit data be stored at addresses that are a multiple of four. Others allow 16-bit and 32-bit data to be stored at any address.

### 7.2.1 THE GUMNUT INSTRUCTION SET

Rather than trying to describe the characteristics of the instruction sets of all CPUs, we will present one relatively simple example that embodies most of the important concepts. The CPU that we will describe is an 8-bit soft core called the *Gumnut*, developed by the author. (A gumnut is a small seedpod of an Australian eucalyptus tree. It is something small from which large things grow.) Further information and files are provided in the supplementary material for this book for use in FPGA designs. The complete Gumnut instruction set is listed in Table 7.1. We use a notation for instructions called *assembly code*. An assembly-code program can be translated by a software tool called an *assembler* into a sequence of binary-coded instructions to be loaded into the instruction memory.

The Gumnut has an instruction memory of up to 4096 instructions (using 12-bit addresses) and a data memory of 256 bytes (using 8-bit addresses). When the CPU is reset, it clears the PC to 0, and starts the fetch-decode-execute cycle, fetching the first program instruction from address 0 in the instruction memory. Within the CPU, there are eight general-purpose registers, named r0 through r7, that can hold data to be operated upon by instructions. Register r0 is special, in that it is hard-wired to have the value 0, and any updates to it are ignored. The CPU also has two single-bit *condition-code* registers called Z (zero) and

|                        | INSTRUCTION                             | DESCRIPTION                                                           |

|------------------------|-----------------------------------------|-----------------------------------------------------------------------|

|                        | Arithmetic and logical instr            | ructions                                                              |

|                        | add rd, rs, op2                         | Add rs and op2, result in rd                                          |

|                        | addc rd, rs, op2                        | Add rs and op2 with carry, result in rd                               |

|                        | sub <i>rd</i> , <i>rs</i> , <i>op2</i>  | Subtract op2 from rs, result in rd                                    |

|                        | subc rd, rs, op2                        | Subtract op2 from rs with carry, result in rd                         |

|                        | and <i>rd</i> , <i>rs</i> , <i>op2</i>  | Logical AND of <i>rs</i> and <i>op2</i> , result in <i>rd</i>         |

|                        | or <i>rd</i> , <i>rs</i> , <i>op</i> 2  | Logical OR of <i>rs</i> and <i>op2</i> , result in <i>rd</i>          |

|                        | xor <i>rd</i> , <i>rs</i> , <i>op</i> 2 | Logical XOR of <i>rs</i> and <i>op2</i> , result in <i>rd</i>         |

|                        | mask rd, rs, op2                        | Logical AND of <i>rs</i> and NOT <i>op2</i> , result in <i>rd</i>     |

|                        | Shift instructions                      |                                                                       |

|                        | shl rd, rs, count                       | Shift rs value left count places, result in rd                        |

|                        | shr rd, rs, count                       | Shift rs value right count places, result in rd                       |

|                        | rol rd, rs, count                       | Rotate rs value left count places, result in rd                       |

|                        | ror rd, rs, count                       | Rotate <i>rs</i> value right <i>count</i> places, result in <i>rd</i> |

| egis-                  | Memory and I/O instruction              | ns                                                                    |

| an                     | $ldm rd$ , $(rs) \pm offset$            | Load to <i>rd</i> from memory                                         |

| <i>ınt</i> is<br>shift | stm $rd$ , $(rs) \pm offset$            | Store to memory from <i>rd</i>                                        |

| nt                     | inp $rd$ , $(rs) \pm offset$            | Input to <i>rd</i> from input controller register                     |

| ess,                   | out $rd$ , $(rs) \pm offset$            | Output to output controller register from <i>rd</i>                   |

| ress.                  | Branch instructions                     |                                                                       |

|                        | bz ± <i>disp</i>                        | Branch if Z is set                                                    |

|                        | bnz ± <i>disp</i>                       | Branch is Z is not set                                                |

|                        | $bc \pm disp$                           | Branch if C is set                                                    |

|                        | bnc ± <i>disp</i>                       | Branch if C is not set                                                |

|                        | Jump instructions                       |                                                                       |

|                        | jmp <i>addr</i>                         | Jump to <i>addr</i>                                                   |

|                        | jsb <i>addr</i>                         | Jump to subroutine at <i>addr</i>                                     |

|                        | Miscellaneous instructions              |                                                                       |

|                        | ret                                     | Return from subroutine                                                |

|                        | reti                                    | Return from interrupt                                                 |

|                        | enai                                    | Enable interrupts                                                     |

|                        | disi                                    | Disable interrupts                                                    |

|                        | wait                                    | Wait for interrupts                                                   |

|                        | stby                                    | Enter low-power standby mode                                          |

|                        |                                         |                                                                       |

TABLE 7.1 The Gumnut instruction set. *rd* and *rs* are registers, *op2* is a register (*rs2*) or an immediate value (*immed*), *count* is count of number of places to shift or rotate, *disp* is a displacement from the next-instruction address, and *addr* is a jump target address.

288

C (carry). They are set to 1 or cleared to 0 depending on the result of certain instructions, and can be tested to decide among alternative courses of action in the program.

#### Arithmetic and Logical Instructions

The arithmetic and logical instructions operate on 8-bit data values stored in the CPU's general-purpose registers and store the result in the destination register, rd. For each instruction, one value is taken from a source register, rs. The other value, op2, either comes from a second source register (rs2) or is an *immediate value* (*immed*). An immediate value is a value that is specified as part of the instruction, rather than being stored in a register or in memory. For example, the instruction

add r3, r4, r1

adds the values currently in registers r4 and r1 and puts the result in r3. Similarly, the instruction

add r5, r1, 2

adds the immediate value 2 and the value currently in r1 and puts the result in r5. Note that the destination register can be the same as a source register. For example, the instruction

sub r4, r4, 1

updates register r4 by decrementing its value.

The addition and subtraction instructions treat the data values as 8-bit unsigned integers. The addc instruction includes the value of the C condition code as a carry-in bit, and the subc instruction includes the C value as a borrow-in bit. All of the instructions in this group modify the Z and the C bits. They set Z to 1 if the instruction result is 0, and they clear Z to 0 if the result is nonzero. The add and addc instructions set C to the carry-out bit of the addition, the sub and subc instruction set C to the borrow out of the subtraction, and the remaining logical instructions clear C to 0. We will see later in this section how the condition-code bits are used by branch instructions.

EXAMPLE 7.1 Write a sequence of instructions to evaluate the expression 2x + 1, assuming the value of x is in register r3 and the result is to be put in r4.

SOLUTION We can multiply x by 2 by adding it to itself. The required instructions are

```

add r4, r3, r3

add r4, r4, 1

```

EXAMPLE 7.2 Write a sequence of instructions that sets the Z bit to 1 if the least significant 4 bits of r2 have the value 0101.

SOLUTION We can test whether a register value is equal to 0101 by subtracting 0101 from the value and putting the result in r0. The result value is ignored, but Z is set as a side-effect of the subtraction. However, the most significant 4 bits of r2 might contain 1s that we are not interested in, so we need to clear them to 0s before doing the subtraction. We can use an AND operation with the value 00001111 to clear the bit. The required instructions are:

and r1, r2, 0x0F sub r0, r1, 0x05

The notation "0x" is a prefix for a hexadecimal value in the Gumnut assembly code notation. Thus, 0x0F is the value 00001111 and 0x05 is the value 00000101.

#### Shift Instructions

The shift instructions shift or rotate 8-bit values taken from the general purpose register *rs* and store the result in register *rd*. The number of places to shift or rotate is specified in the instruction as *count*. For example, the instruction

```

shl r4, r1, 3

```

reads the value currently in register r1, shifts it left by 3 places and puts the result in r4. The shift-left and shift-right instructions discard the bits shifted past the end of the 8-bit byte and fill the vacated bit positions with 0s. The rotate-left and rotate-right instructions copy the bits shifted past the end of the byte around to the other end. All of these instructions set Z to 1 if the

instruction result is 0, and they clear Z to 0 if the result is nonzero. They set the C bit to the value of the last bit shifted past the end of the byte.

EXAMPLE 7.3 Write instructions that multiply the value in r4 by 8, ignoring the possibility of overflow.

SOLUTION Recall from Section 3.1.2 that we can multiply an unsigned binary integer by  $2^k$  by shifting k places to the left. Thus, since  $8 = 2^3$ , an instruction to multiply r4 by 8 is

shl r4, r4, 3

#### Memory and Input/Output Instructions

The Gumnut has separate instructions for accessing data memory and I/O controllers. We will discuss the operation of I/O controllers in detail in Chapter 8. For now, we simply point out that I/O controllers have registers that govern their operation, and that these registers can be read and written by the CPU. Just as locations in memory have addresses, each I/O controller register has an identifying address. The Gumnut uses 8-bit addresses for I/O controller registers, distinct from the 8-bit addresses it uses for locations in the data memory. We say that the Gumnut has separate *address spaces* for data memory and for I/O controller registers. This is in contrast to a number of other CPU instructions sets, in which I/O controller registers are part of the same address space as memory addresses. In those instruction sets, we say I/O registers are *memory mapped*.

For all of the Gumnut's memory and I/O instructions, the address to access is computed by adding the current value in rs and an offset value specified in the instruction. The load from memory instruction reads from the data memory at the computed address and puts the read value in register rd. The store to memory writes the value from register rd to the data memory at the computed address. The input and output instructions perform similar operations, but read or write to the I/O controller registers at the computed address. None of these instructions affect the values of the Z and C bits. As examples, the instruction

ldm r1, (r2)+5

calculates the memory address by adding the current value of r2 and the offset 5. It then reads from memory at that address and puts the read value in r1. Similarly, the instruction

stm r1, (r4)-2

stores the value from r1 into memory at the address 2 less than the current value of r4.

If we want to specify a particular address to access, we can use r0 as the register for *rs*. Recall that r0 always contains 0, so adding it to the offset value specified in the instruction just gives the offset value. In this case, we usually interpret the offset value as an unsigned 8-bit address. Our assembler tool allows us to imply the specification "(r0)" by omission and just write the address value, for example,

inp r3, 156

which reads from the I/O controller register at address 156 into r3. Similarly, if a register contains the address we want to access, we can use an offset of 0. Again, our assembler allows us to imply a 0 offset by omission, as in the instruction.

out r3, (r7)

EXAMPLE 7.4 Write instructions that increment a 16-bit unsigned integer stored in memory. The address of the least significant byte is in r2. The most significant byte is in the next memory location.

SOLUTION Since the Gumnut arithmetic instructions only operate on 8-bit data, we need to do two adds, with the carry from the first used in the second. The instructions are

ldm r1, (r2) add r1, r1, 1 stm r1, (r2) ldm r1, (r2)+1 addc r1, r1, 0 stm r1, (r2)+1

Since the load and store instructions do not affect the C bit, the C result from the first addition is preserved and used in the addc instruction.

#### **Branch Instructions**

The branch instructions allow us to conditionally change the normal flow of execution. We mentioned earlier that the CPU follows a fetch-decode-execute loop to execute instructions at successive addresses in the instruction memory. It uses a program counter (PC) register to keep track of the next instruction address, and increments this register after fetching each instruction. The branch instructions modify the sequential flow of execution by changing the PC value. Each form of branch tests a condition, and if the condition is true, adds a signed 8-bit displacement value to the PC. The displacement, specified in the instruction, indicates how many locations forward or backward the next instruction to execute is from the current instruction. (A displacement of 0 refers to the instruction after the branch, since the PC has already been incremented after fetching the branch instruction.) If the condition is false, the PC is unchanged, and execution continues sequentially. The different branch instructions allow us to test each of the Z and C condition code bits for being set to 1 or not set to 1. Since these bits are affected by arithmetic, logical and shift instructions, we often deliberately precede a branch instruction with one of these instructions to compare data values. In other cases, the condition code setting occurs as a serendipitous side effect of data operations that we need to perform anyway.

EXAMPLE 7.5 Suppose the value in data memory location 100 represents the number of seconds elapsed in a time interval. Write instructions to increment the value, wrapping around to 0 when the value increments above 59.

SOLUTION One possible sequence of instructions is

ldm r1, 100 add r1, r1, 1 sub r0, r1, 60 bnz +1 add r1, r0, 0 stm r1, 100

The first two instructions load the value into r1 and increment it. The sub instruction subtracts 60 from the new value and discards the result (by using r0 as the destination register). However, the Z condition code is updated as a side effect. If the new value is 60, the subtraction result is 0, so Z is set to 1; otherwise, it is cleared to 0. The branch instruction skips forward one instruction if Z is 0. The intervening add instruction, which is only executed when the incremented value was 60, overwrites the incremented value with 0. The final instruction, executed in all cases, stores the final value back to memory.

#### Jump and Miscellaneous Instructions

The first of the jump instructions, jmp, unconditionally breaks the sequential flow of execution by setting the PC to the address specified in the instruction.

EXAMPLE 7.6 Write instructions that test whether r1 is 0, and if so, clear the contents of memory location 100. If r1 is other than 0, the instructions should clear the contents of memory location 200 instead. Assume that the instructions start at address 10 in the instruction memory.

SOLUTION In the required sequence of instructions we have two alternative actions to perform, depending on whether r1 is 0. Since instructions are laid out in linear order in the instruction memory, we need to put the instructions for the two alternatives one after the other. We need an unconditional jump at the end of the first alternative to bypass the instructions for the second alternative. The instructions are

```

10: sub r0, r1, 0

11: bnz +2

12: stm r0, 100

13: jmp 15

14: stm r0, 200

15: ...

```

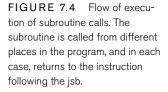

The second of the jump instructions, jsb, is somewhat more involved than the simple jump instruction. It allows us to execute a *subroutine*, that is, a collection of instructions that perform some desired operations and that we can invoke from different parts of the program. Starting execution of a subroutine is referred to as *calling* the subroutine. The jsb instruction is used in tandem with the ret instruction, which returns from the subroutine to the place of the call. The sequence of instruction execution for a subroutine is shown in Figure 7.4. Execution proceeds sequentially until the jsb is encountered. The jsb saves

the incremented PC value (the return address) in an internal register and then updates the PC with the subroutine address specified in the instruction. This causes instructions in the subroutine to be executed. Eventually, the subroutine executes a ret instruction, which restores the saved return address to the PC. Thus, execution continues with the instruction after the jsb. The program can include several jsb instructions that all refer to the same subroutine. In each case, the return address saved is the address of the instruction after the jsb. This allows execution to return to the right place, regardless of where the subroutine was called from.

The instructions in the subroutine can include any in the CPU's instruction set. This raises the possibility that the subroutine might include a jsb to call a sub-subroutine. The sub-subroutine might include a further jsb to call a sub-sub-subroutine, and so on. When the sub-sub-subroutine returns, execution should continue just after the jsb in the sub-subroutine, and when it returns, execution should continue just after the jsb in the sub-subroutine. In order to achieve this effect, the CPU needs more than just a single register to save return addresses. In fact, it needs a *push-down stack* of registers, as shown in Figure 7.5. Each time a jsb is executed, the return address for that jsb is pushed onto the stack. When a ret is executed, the return address used is the top entry on the stack, and that entry is popped from the stack. The Gumnut has a return-address stack that can hold up to eight entries, which is ample for most programs.

EXAMPLE 7.7 Suppose an application keeps track of a number of time intervals concurrently. Revise the sequence of instructions from Example 7.5 to form a subroutine that increments the number of seconds stored in the memory location whose address is in r2. Show how to call the subroutine to increment values in locations 100 and 102.

SOLUTION We can rewrite the instructions to form a subroutine as follows:

ldm r1, (r2) add r1, r1, 1 sub r0, r1, 60 bnz +1 add r1, r0, 0 stm r1, (r2) ret

Assuming the first instruction in the subroutine is at location 20 in the instruction memory, the calling instructions are

FIGURE 7.5 The push-down return-address stack after two nested calls (top) and a third nested call (bottom).

add r2, r0, 100 jsb 20 add r2, r0, 102 jsb 20

The remaining miscellaneous instructions deal with *interrupts*, which are a way of responding to events signaled by I/O controllers. The enableinterrupt instruction allows the CPU to respond to interrupt events, and the disable-interrupt instruction prevents the CPU from responding. When the CPU responds to an interrupt event, it saves the address of the instruction it is about to execute and, instead, starts executing instructions in a special subroutine called an *interrupt handler*. The interrupt handler finishes with a return-from-interrupt (reti) instruction rather than a ret instruction. The wait instruction suspends execution until an interrupt occurs, and the stby instruction enters a low-power standby mode until an interrupt occurs. The difference is that the CPU would normally be able to respond to an interrupt immediately when suspended using a wait instruction, whereas it could take some time to power up from a stby instruction. We will describe interrupt processing in more detail as part of our discussion of input/output in Chapter 8.

#### 7.2.2 THE GUMNUT ASSEMBLER

As we mentioned earlier, programs can be written in assembly language and translated into a sequence of binary-coded instructions by an assembler. The supplementary material for this book includes a simple assembler for the Gumnut, called *gasm*. The *gas User Guide*, also included in the supplementary material, provides a detailed description of the assembly language and how to use the assembler. We will describe a few key points here, illustrated by the program in Figure 7.6.

; Program to determine greater of value\_1 and value\_2 text org 0x000 ; start here on reset jmp main ; Data memory layout data value 1: byte 10 value 2: byte 20 result: bss 1

**FIGURE 7.6** A Gumnut assembly language program to find the greater of two values.

| ; Main program   |             |                               |   |                    |

|------------------|-------------|-------------------------------|---|--------------------|

|                  | text<br>org | 0x010                         |   |                    |

| main:            | ldm<br>ldm  | r1, value_1<br>r2, value 2    | ; | load values        |

|                  | sub<br>bc   | r0, r1, r2<br>value_2_greater |   | compare values     |

|                  | stm<br>jmp  | r1, result<br>finish          | ; | value_1 is greater |

| value_2_greater: |             | r2, result                    | ; | value_2 is greater |

| finish:          | jmp         | finish                        | ; | idle loop          |

FIGURE 7.6 (continued) A Gumnut assembly language program to find the greater of two values.

We have seen in Verilog models that we can include comments, starting with the characters "//", to describe parts of the model. We can also include comments in assembly language programs. In Figure 7.6, comments start with the ";" character and extend to the end of the line. Comments are especially important in assembly language programs, since each instruction performs only a single simple step. We use comments to describe the larger intent of a sequence of instructions.

The assembler lets us specify both the instructions to be included in the instruction memory and the contents of the data memory. We tell the assembler which memory we are specifying using the text (for instruction memory) and data (for data memory) *directives*. A directive does not represent a CPU instruction. Rather, it tells the assembler what to do when translating the program. Rather than requiring us to specify the address for each instruction and data item, the assembler adds instructions and data items at increasing addresses in each memory, starting at address 0. It automatically keeps track of where it is up to by using a *location counter* for each of the instruction and data memories. We can direct the assembler to change the location counter for the memory currently being filled by using an org (short for "origin") directive. For example, in Figure 7.6, the org 0x010 directive in the second text segment tells the assembler to continue placing instructions from location  $010_{16}$ .

Within a data segment, we can include directives that specify the initial contents of data memory locations. The byte directive specifies the contents of an 8-bit location. The bss (short for "block starting with symbol") directive reserves a specified number of bytes of memory storage without initializing their content. We can precede each of these directives with a *label* that represents the starting address of the locations. The assembler works out the address for us. We can then refer to the label in instructions in the program. For example, the ldm instructions in Figure 7.6 refer to the labels value\_1 and value\_2 to load the initialized content of the data memory locations, and the stm instruction refers to the label result to store the greater value in the reserved location.

The advantage of using labels is that, when we revise the program, we don't need to revise the address values, since the assembler will work out new values when the program is reassembled.

Within a text segment, we include the instructions that form the program. Each instruction can be labeled, and the labels can be referenced in branch and jump instructions. Again, the assembler works out the instruction addresses represented by the labels, so that we don't have to work out branch displacements manually, or update references when we change the program.

One final point to note about the program in Figure 7.6 is that, once it completes its task, it doesn't stop executing. The Gumnut does not include any instructions for stopping. Instead, we include a *busy loop* at the end of the program. This just consists of an instruction that jumps back to itself, performing no useful work. Busy loops are common in embedded systems, since we usually do not want an embedded computer to stop (unless we turn the power off). An alternative is to have a CPU instruction or other facility that *suspends* operation until some activity is needed, such as responding to an I/O event. (On the Gumnut, we could use a wait or stby instruction.) This has the advantage that power consumption in the suspended state is typically much lower than in the active state. For this reason, suspending is preferred in battery-powered and other power sensitive applications.

#### 7.2.3 INSTRUCTION ENCODING

The instructions of a program are a form of information, and so, like any other information, can be encoded in binary. If we were to list all of the possible instructions, taking into account the operation to be performed and any registers, addresses, immediate values, and so on, we could devise an instruction coding taking up the smallest number of bits. However, decoding instructions would then be complex, leading to a large and slow decoder circuit within the CPU. Instead, instruction sets are usually encoded by separating a code word into distinct *fields*, each of which encodes one aspect of an instruction. The primary field is the *opcode*, short for operation code, that specifies the operation to be performed and, by implication, the layout of the remaining fields within the code word. By keeping the field layout simple and regular, we make the circuit for the instruction decoder simple and, hence, fast.

As an illustration, the instruction encoding for the Gumnut is shown in Figure 7.7. (The full details of the instruction encoding are described in Appendix D.) Each instruction code word is 18 bits long. The left-most bits, together with the function code (fn), form the opcode. Those instructions that specify register numbers have the numbers encoded in 3-bit binary form in separate fields of the instruction word. Similarly, instructions that specify immediate values, offsets, or displacements have those

| Arith/Logical<br>Register  | 4<br>1 1 1 0                                          | 3<br><i>rd</i>                                      | 3<br><i>rs</i> | 3<br>rs2   | 2           | 3<br>fn |

|----------------------------|-------------------------------------------------------|-----------------------------------------------------|----------------|------------|-------------|---------|

| Arith/Logical<br>Immediate | 1 3<br>0 <i>fn</i>                                    | 3<br><i>rd</i>                                      | 3<br>rs        |            | 8<br>immed  |         |

| C1 : (.                    | 3 1                                                   | 3                                                   | 3              | 3          | 3           | 2       |

| Shift                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | <i>rd</i>                                           | <i>rs</i>      | count      | 8           | fn      |

| Memory, I/O                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | rd                                                  | rs             |            | °<br>offset |         |

|                            | 6                                                     | 2                                                   |                |            | 8           |         |

| Branch                     |                                                       | 1 0 f                                               | n              |            | disp        |         |

| Jump                       | 5                                                     | $\begin{array}{c c} 1 \\ \hline 0 & fn \end{array}$ |                | 12<br>addr |             |         |

|                            | 7                                                     |                                                     | 3              |            | 8           |         |

| Miscellaneous              | 1 1 1 1                                               | 1 1 0                                               | fn             |            |             |         |

FIGURE 7.7 Instruction encoding for the Gumnut, showing the layout and size of fields within instructions.

values binary encoded in the right-most 8 bits of the instruction word. In several of the instruction formats, some bits remain unused. While this may waste some storage space within the instruction memory, the simplicity of encoding and the consequent simplicity of decoding is a trade-off worth making. As we mentioned earlier, it is the task of the assembler to translate instructions specified in textual assembly language into this binary encoding. Conversely, if we are testing a design that includes an embedded Gumnut, we may need to disassemble binary-coded instructions, that is, to determine the instructions corresponding to binary instruction code words processed by the embedded core.

EXAMPLE 7.8 Given that the function code for the addc operation is 001, what is the binary instruction word for the instruction

addc r3, r5, 24

SOLUTION This is an arithmetic/logical immediate instruction, so the left-most bit is 0, and the function code is 001. The destination register r3 is encoded as 011, the source register number as 101, and the immediate value as 00011000. So the complete instruction word is 0 001 011 101 00011000, or, in hexadecimal, 05D18.

EXAMPLE 7.9 What instruction is represented by the hexadecimal instruction word 2ECFC? SOLUTION The binary instruction word is 111110110011111100. The left-most bits, 111110, indicate that this is a branch instruction. The function code 11 specifies a bnc instruction. The next two bits are 0, but are ignored in any case. The right-most 8 bits are the signed 2s-complement displacement -4. So the instruction is bnc -4.

## 7.2.4 OTHER CPU INSTRUCTION SETS

The Gumnut instruction set is relatively simple, compared to those of other CPUs. Nonetheless, it contains all the essential elements, and is quite sufficient for writing realistic embedded programs. It is similar to the instruction set of the PicoBlaze 8-bit soft core provided by Xilinx. One thing that distinguishes both of these CPUs from other commonly used 8-bit cores and microcontrollers is that all instructions are encoded in the same length. Moreover, the instruction length is not a multiple of 8 bits. (In both cases, it is 18 bits, which is one of widths to which a memory block in a Xilinx FPGA can be configured.) An example of an 8-bit microcontroller that takes a different approach is the 8051 from Intel and other vendors. It originated as a stand-alone microprocessor, and was subsequently released in microcontroller versions with various amounts of memory and I/O controllers included on chip. Its instruction set inherits from those of previous general purpose CPUs, in which a single memory address space was shared between instructions and data. Since locations in the 8051 memory are 8 bits wide, instructions are a multiple of 8-bit bytes. The opcode is included in the first byte. For some instructions the next one or two bytes contain further information to specify the instruction, such as an address and immediate data.

Another distinguishing characteristic of the 8051, compared to the Gumnut and PicoBlaze, is that the instruction set contains a much larger repertoire of operations. We call CPUs with instruction sets like this *complex instruction set computers* (CISCs), in contrast to the Gumnut and similar CPUs, which are *reduced instruction set computers* (RISCs). Many of the operations that can be expressed as one instruction on an 8051 would have to be implemented using a sequence of two or three instructions on a Gumnut. However, the complexity of the instructions. It also makes it difficult for the CPU to fetch and decode instructions. It also makes it difficult to implement a number of important CPU internal design techniques for increasing performance. For this and other reasons, RISC CPUs tend to dominate now.

The CPUs that we have mentioned thus far in this section are classified as 8-bit CPUs, as they operate only on 8-bit data. If the information to be represented in an embedded system is predominantly 16-bit, 32-bit or 64-bit data, using an 8-bit processor is very cumbersome. We may not be able to meet performance constraints, due to the number of instructions needed to implement 16-bit, 32-bit or 64-bit operations using 8-bit instructions. The alternative is to use a larger CPU whose instructions can operate on the larger data sizes directly. Most of the widely used processor cores for FPGAs and ASICs are 32-bit or 64-bit RISC CPUs. They have 32-bit or 64-bit registers and perform arithmetic and logical operations on data in those registers. They can load and store 8-bit, 16-bit, 32-bit and 64-bit data between registers and data memory. Instructions are encoded in fixed-length instruction words, usually 16 or 32 bits long. The larger, higher performance CPUs include instructions to operate on floating-point data as well as integers. Examples of this type of CPU include the PowerPC, ARM, MIPS and Tensilica cores that we mentioned earlier.

- 1. What is meant by the *instruction set* of a CPU?

- 2. What three steps are repeatedly performed by a CPU to execute a program?

- 3. How does the CPU keep track of which instruction to execute next?

- 4. What is meant by the terms *little endian* and *big endian*?

- 5. What does an assembler do?

- 6. What does each of the following Gumnut instructions do?

```

addc r2, r3, 25

shr r1, r1, 3

ldm r5, (r1)+4

bnz -7

jsb do_op

ret

```

7. What is the binary instruction word for the following Gumnut instruction?

bnc +15

8. What Gumnut instruction is represented by the hexadecimal instruction word 05501?

## KNOWLEDGE TEST QUIZ

## 7.3 INTERFACING WITH MEMORY

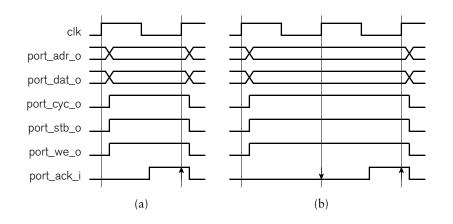

The way in which a CPU is connected to instruction and data memories depends on the implementation fabric used for both the CPU and the memories. In most embedded systems, the instruction memory is implemented with ROM, NOR flash memory, SRAM, or a combination of these. Including flash memory gives us the opportunity to upgrade the embedded software in the field. The data memory is usually implemented just with SRAM. Typically, the CPU and the memories each have a set of connection signals for the CPU/memory interface, and it is our job to join them together. If the two sets of signals are compatible, our job is relatively easy. Often, however, the sets of signals are designed in isolation, or according to different conventions. In such cases, we need to include glue logic to complete the interface.

One of the simplest cases of interfacing a CPU with memory is that of an embedded 8-bit core within an FPGA. The core includes interface signals that connect directly to those of the FPGA's memory blocks.

EXAMPLE 7.10 The memory interface signals of the Gumnut core are described in the following Verilog module definition:

```

module gumnut ( input

clk_i,

input

rst_i,

output

inst_cyc_o,

output

inst_stb_o,

input

inst ack i.

output [11:0] inst_adr_o,

input [17:0] inst_dat_i,

output

data_cyc_o,

data_stb_o,

output

output

data_we_o,

input

data ack i.

output [7:0] data_adr_o,

output [7:0]

data_dat_o,

input [7:0] data dat i.

...);

endmodule

```

Show how to include an instance of the Gumnut core in a Verilog model of an embedded system with a  $2K \times 18$ -bit instruction memory and a  $256 \times 8$ -bit data memory.

**SOLUTION** The ports in the module can interface with the control signals of a flow-through SSRAM and a ROM implemented using FPGA SSRAM blocks, as described in Sections 5.2.2 and 5.2.5. In our module for our embedded system, we include the necessary nets and variables to connect to an instance

of the Gumnut entity, and use the nets and variables in always blocks for the instruction and data memories. The module is

```

module embedded_gumnut;

reg [17:0] inst_ROM [0:2047];

reg [7:0]

data_RAM [0:255];

wire

clk;

wire

rst;

wire

inst_cyc_o;

inst_stb_o;

wire

inst_ack_i;

req

wire [11:0] inst_adr_o;

reg [17:0] inst_dat_i;

wire

data_cyc_o;

wire

data_stb_o;

wire

data_we_o;

reg

data_ack_i;

data_adr_o;

wire [7:0]

wire [7:0]

data_dat_o;

reg [7:0]

data_dat_i;

. . .

gumnut CPU ( .clk_i(clk_i), .rst_i(rst_i),

.inst_cyc_o(inst_cyc_o), .inst_stb_o(inst_stb_o),

.inst_ack_i(inst_ack_i),

.inst_adr_o(inst_adr_o), .inst_dat_i(inst_dat_i),

.data_cyc_o(data_cyc_o), .data_stb_o(data_stb_o),

.data_we_o(data_we_o), .data_ack_i(data_ack_i),

.data_adr_o(data_adr_o), .data_dat_o(data_dat_o),

.data_dat_i(data_dat_i), ... );

initial $readmemh("inst_ROM.data", inst_ROM);

always @(posedge clk) // Instruction memory

if (inst_cyc_o && inst_stb_o) begin

inst_dat_i <= inst_ROM[inst_adr_o[10:0]];</pre>

inst_ack_i <= 1'b1;</pre>

end

else

inst_ack_i <= 1'b0;</pre>

always @(posedge clk) // Data memory

if (data_cyc_o && data_stb_o)

if (data_we_o) begin

data_RAM[data_adr_o] <= data_dat_o;</pre>

data_dat_i

<= data_dat_o;

data_ack_i

<= 1'b1;

end

```

Note that the instruction address port of the Gumnut core is 12 bits wide, whereas the  $2K \times 18$ -bit instruction memory uses an 11-bit-wide address. In this design, we simply leave the most significant address bit of the core unconnected. Each location in the instruction memory thus appears twice in the Gumnut's instruction address space: once at an address with the most significant bit 0, and once at an address with the most significant bit 1. We would normally just use one address for the location and ignore the other alias address.

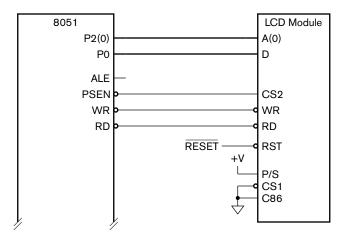

Single-chip microcontrollers, such as those based on the 8051 described in Section 7.2.4, include a small amount of instruction and data memory on the microcontroller chip. However, many of them are able to address additional off-chip memory, using a number of the chip pins for the external memory interface signals. Since using the pins for this purpose reduces the number of pins available for inputs and outputs, the memory interface pins are often multiplexed to perform different functions at different times. This complicates the connection between the microcontroller and external memory.

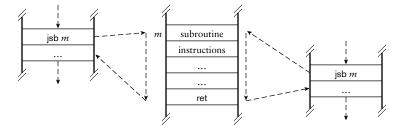

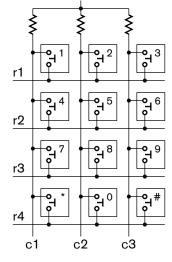

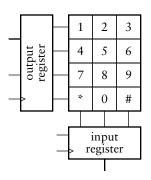

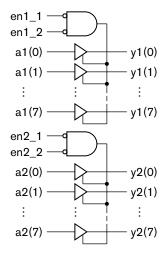

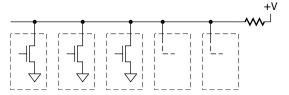

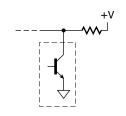

As an illustration, we will describe how to expand the memory of the 8051 microcontroller. The 8051 can access up to 64K bytes of instruction memory and 64K bytes of data memory, however, there are only 256 bytes of data memory and 4K to 16K bytes of instruction memory on the chip. The chip has two 8-bit input/output ports, P0 and P2, as well as a number of control signals, that can be used to connect to external memory. Figure 7.8 shows how they would be used to connect to an external 128K  $\times$  8-bit asynchronous SRAM, in which the lower 64K locations are used for instructions and the upper 64K locations for data. P2 provides the most significant address byte, and P0 is multiplexed with the least significant address byte and instruction and data bytes. Since information transfer on P0 is bidirectional, tristate drivers are used internally in the microcontroller and in the memory data pins.

The 8051 activates the address-latch enable (ALE) signal when it drives the least significant address bits on P0. We provide an 8-bit latch to hold these bits for the remainder of the memory access cycle. During an instruction read access, the 8051 activates the program-store enable  $(\overrightarrow{PSEN})$  signal, driving it to a low logic level. At other times, including data

FIGURE 7.8 Connection between an 8051 microcontroller and an external combined instruction and data memory.

305

accesses, the signal is at a high logic level. Hence, we can use this signal directly as the most significant address bit to distinguish between instruction and data accesses to the external memory. The 8051 activates the  $\overline{\text{RD}}$  signal during data read accesses and the  $\overline{\text{WR}}$  signal during data write accesses. We use  $\overline{\text{WR}}$  directly to control the memory's write enable ( $\overline{\text{WE}}$ ) signal. However, we need a small amount of glue logic to derive the chip enable ( $\overline{\text{CE}}$ ) and output enable ( $\overline{\text{OE}}$ ) signals. We could implement this glue logic, together with the address latch, in a small PAL component.

Microcontrollers and processor cores that access 16-bit, 32-bit or 64-bit data generally need data memories that are wider than 8 bits, even though addresses correspond to 8-bit locations. This allows the CPU to access a complete data word with one read or write operation. A common approach is to make the data memory one word wide, with the byte locations arranged within the words. Figure 7.9 shows the case of byte addressing within a 32-bit-wide memory. Depending on whether the CPU is big endian or little endian, the most significant byte of a 32-bit word is stored in the byte with the lowest or highest address, respectively, of a 32bit location. Most 32-bit CPUs ensure that 32-bit data words are stored at locations whose addresses are a multiple of four. This allows the word to be read or written with just one memory access, rather than requiring two partial memory accesses, which would be the case if the word were split over two adjacent 32-bit locations. Similarly, CPUs ensure that 16-bit halfwords are stored at locations whose addresses are a multiple of two, and that 64-bit double-words are stored at locations whose addresses are a multiple of eight, for the same reason.

Reading from data memory is quite straightforward. A 32-bit CPU, for example, reads the whole 32-bit word containing the required data item. If the required item is only a 16-bit halfword or an 8-bit byte, the CPU usually extracts the item from the appropriate memory data

|   | 0    | 1 | 2  | 3  |

|---|------|---|----|----|

|   | 4    | 5 | 6  | 7  |

|   | 8    | 9 | 10 | 11 |

| ļ | ,  , |   |    |    |

FIGURE 7.9 Arrangement of bytes within words in a 32-bit wide memory.

signals and places it in a destination register. Writing a 32-bit word is similarly straightforward. The CPU places the word on the 32 memory data signals, and the memory performs a write operation. Writing a 16-bit halfword or an 8-bit byte is more involved, since we must ensure that the other bytes in the corresponding 32-bit memory location are not affected. The CPU typically provides separate byte write enable control signals instead of (or in addition to) the overall write enable control signal. Alternatively, it might provide separate byte enable signals instead of an overall memory enable signal. To write an 8-bit byte, the CPU places the byte value on the eight memory data signals corresponding to the position of the byte within a 32-bit word and activates the associated byte enable signal. The memory then performs a write operation, updating only the enabled byte within the addressed word. Similarly, to write a 16-bit halfword, the CPU places the halfword value on the appropriate 16 memory data signals and activates the associated two byte enable signals. The memory then writes only those two bytes of the addressed word.

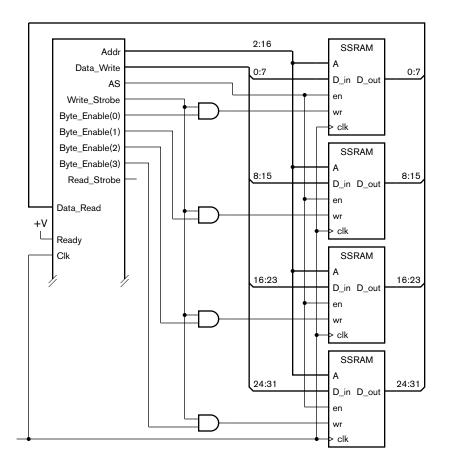

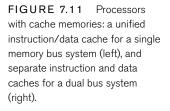

EXAMPLE 7.II The Xilinx MicroBlaze 32-bit processor core has connections to a  $32K \times 32$ -bit data memory as shown in Figure 7.10. (AS stands for "address strobe." This signal is active for each memory access.) Describe how the following memory operations proceed: a word read from address 00F00; a byte read from address 00F13; a word write to address 1E010; a byte write to address 1E016; and a halfword write to address 1E020.

SOLUTION Word read from 00F00: The address is a multiple of four. Write\_Strobe is 0, so all four memory components perform a read operation, providing the 32-bit data on the Data\_Read signal.

Byte read from 00F13: The address is 3 more than a multiple of four, so the byte is at offset 3 within a word. However, Write\_Strobe is 0, so all four memory components perform a read operation, providing the 32-bit data on the Data\_Read signal. The CPU extracts the required byte from Data\_Read(24:31).

Word write to 1E010: The address is a multiple of four. Write\_Strobe is 1 and all four Byte\_Enable signals are 1, so all four memory components perform a write operation, taking the 32-bit data from the Data\_Write signal.

Byte write to 1E016: The address is 2 more than a multiple of four, so the byte is at offset 2 within a word. The CPU provides the byte data on Data\_Write(16:23). Write\_Strobe and Byte\_Enable(2) are 1, and the remaining Byte\_Enable signals are 0. The memory component connected to Data\_Write(16:23) performs a write operation. The remaining components perform a read operation, but the data they supply on Data\_Read(0:7), Data\_Read(8:15) and Data\_Read(24:31) is ignored.

Halfword write to 1E020: The address is a multiple of four, so the halfword is at offset 0 within a word. The CPU provides the halfword data on Data\_Write(0:15). Write\_Strobe, Byte\_Enable(0) and Byte\_Enable(1) are 1, and the remaining

Byte\_Enable signals are 0. The memory components connected to Data\_Write(0:7) and Data\_Write(8:15) perform a write operation. The remaining components perform a read operation, but the data they supply on Data\_Read(16:23) and Data\_Read(24:31) is ignored.

Some embedded systems require memory storage for large amounts of data. In such systems, it may be more appropriate to use dynamic memory (DRAMs) rather than SRAMs, given the lower cost per bit of DRAM components. As we mentioned in Section 5.2.4, controlling DRAMs is relatively complex, particularly for modern high-performance synchronous and DDR DRAMs, so we won't go into details here.

## 7.3.1 CACHE MEMORY

High performance embedded processors need to access instructions and data at higher rates than simple processors. For such processors,

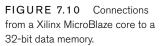

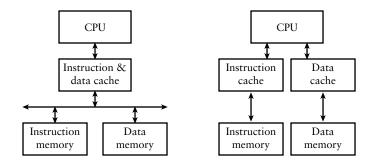

the memory access time of a large SRAM or DRAM memory system is significantly longer than the clock cycle time of the processor, potentially making the memory a performance bottleneck. Many processors avoid the bottleneck by including a *cache* in the path between the processor and memory. A cache is a small, fast memory that stores the most frequently used items from the main memory. By making access to these items faster, we reduce the average access time experienced by the processor. Figure 7.11 shows two possible organizations: a single cache for both instructions and data, and separate caches.

Operation of a cache is predicated on the *principle of locality*, which involves two important observations about the way programs access memory. The first is that a small proportion of instructions and data account for the majority of memory accesses over a given interval of time. The second is that those items stored in locations adjacent to a recently accessed item are likely to be accessed next. To take advantage of these observations, we divide the collection of locations in main memory into fixed-sized blocks, often called *lines*, and copy whole lines at a time from main memory into the cache memory. When the processor requests access to a given memory location, the cache checks whether it already has a copy of the line containing the requested item. If so, the cache has a hit, and it can quickly satisfy the processor's request. If not, the cache has a miss, and must cause the processor to wait. The cache then copies the line containing the requested item from main memory into the cache memory. When the requested item is available in the cache, the processor can proceed with its requested access. The fact that neighboring items are also copied into the cache means that subsequent processor requests are likely to result in cache hits. As operation of the system proceeds, more and more lines are copied into the cache memory, resulting in a reduced miss rate. When the cache memory is full, some of the copied lines must be replaced by incoming lines. Ideally, the cache should replace the least recently used line. Since keeping track of usage history is complex, most caches use an approximation to determine which line to replace. In the

steady state, caches can achieve miss rates of the order of 1% of processor requests. Thus, the average access time seen by the processor is very close to the access time of the cache memory.

For a system with cache memory, most of accesses to main memory are to entire lines, rather than to single locations. Since the processor is kept waiting during a main-memory operation, it is desirable to reduce the waiting time by making cache-line accesses as fast as possible. There are a number of advanced techniques that we can use to enable a higher rate of data transfer, or *memory bandwidth*. These include:

- Wide memory: Sufficient memory chips are used so that an entire cache line can be accessed at once. The line can then be transferred back to the cache on a wide bus in one clock cycle, or over a narrower bus in several clock cycles.

- Burst transfers: The CPU issues the first address of a line to be accessed in memory. The memory then performs a sequence of accesses at successive locations, starting from the first address. This technique obviates the time required to transfer the address for locations other than the first.

- Pipelining: The memory system is organized as a pipeline so that steps of different memory operations can be overlapped. For example, the pipeline steps might be address transfer, memory access, and returning read data to the CPU. Thus, the memory system could have three memory operations in progress concurrently, with one operation completed per clock cycle.

- Double data rate (DDR) operation: Rather than transferring data items only on rising clock edges, data can be transferred on both rising and falling clock edges. This doubles the rate at which data is transferred, hence the name.

These and a number of other techniques can be used in combination to form a memory system with sufficient bandwidth to allow the processor and cache to operate with minimal waiting time. A detailed discussion is beyond the scope of this book. The topic is addressed in books on computer organization and computer architecture (see Section 7.5).

- 1. When might we need glue logic to connect a memory to a CPU?

- 2. In the 8051 microcontroller, why are data signals and the least significant eight address signals multiplexed onto the same set of pins?

- 3. How many bits wide would the data memory for a 32-bit CPU typically be?

## KNOWLEDGE TEST QUIZ

- 4. Why does a 32-bit CPU provide separate byte-enable signals for its data memory?

- 5. What two observations about the way programs access memory define the principle of locality?

- 6. What is meant by the terms cache hit and cache miss?

- 7. During a cache miss, what happens?

- 8. What is meant by the term *memory bandwidth*?

## 7.4 CHAPTER SUMMARY

- ► A computer system generally contains a central processing unit (CPU), instruction and data memory, input and output (I/O) controllers, and possibly special-purpose accelerators. The elements are interconnected by one or more buses.

- ➤ A microprocessor is a single-chip CPU that can be used in a general purpose computer or an embedded computer. A microcontroller is a single-chip computer incorporating a CPU, memory and I/O controllers. A digital signal processor (DSP) is a CPU specialized for processing streams of data from digitized signals.

- Microprocessors and CPUs in microcontrollers range in scale from simple 8-bit versions to complex 32-bit and 64-bit versions, referring to the size of data that can be processed in a single operation.

- ► CPUs can be implemented as predesigned cores and as soft cores.

- ► The instruction set of a CPU is its repertoire of instructions, usually including arithmetic and logical instructions, memory and I/O instructions, branch and jump instructions, and other miscellaneous instructions.

- ► Little-endian CPUs store multi-byte data with the least significant byte at the lowest address and the most significant byte at the highest address. Big-endian CPUs store the bytes in the opposite order.

- ► Instructions are encoded in binary. However, we usually develop programs using assembly language or a high-level language and use a translator (an assembler or compiler) to translate into binary-coded instructions.

- ► Instruction and data memories are usually connected directly to the CPU using memory-interface signals. Memories for 8-bit, 16-bit and 32-bit CPUs are commonly 8, 16 and 32 bits wide, respectively.

- Memories for high-performance CPUs can use a number of techniques for improving the memory bandwidth, including burst transfers, pipelining and double data rate (DDR) operation.

## 7.5 FURTHER READING

On Holy Wars and a Plea for Peace, Danny Cohen, Internet Engineering Note 137, 1980, available at http://www.rdrop.com/~cary/html/ endian\_faq.html. This is the paper that originally adopted the terms "little endian" and "big endian" to refer to byte order.

- Computer Architecture: A Quantitative Approach, 4th Edition, John L. Hennessy and David A. Patterson, Morgan Kaufmann Publishers, 2007. Includes a discussion of advanced memory system organization. The book also describes techniques, such as caches, used within high-performance CPUs to avoid delays due to memory accesses.

- Computers as Components: Principles of Embedded Computing System Design, Wayne Wolf, Morgan Kaufmann Publishers, 2005. A more advanced reference on embedded systems design, covering CPU and DSP instruction sets, embedded systems platforms, and embedded software design.

- Multiprocessor Systems-on-Chips, Ahmed Jerraya and Wayne Wolf, Morgan Kaufmann Publishers, 2004. Describes hardware, software and design methodologies for embedded systems containing multiple processor cores.

- Engineering the Complex SOC: Fast, Flexible Design with Configurable Processors, Chris Rowen, Prentice Hall, 2004. Describes an approach to system-on-chip design based on extensible processors, using the Tensilica processor as an example.

- ARM System-on-Chip Architecture, 2nd Edition, Steve Furber, Addison-Wesley, 2000. Describes the ARM instruction set, a number of ARM processor cores, and some examples of embedded applications using ARM cores.

- Power Architecture Technology, IBM, http://www.ibm.com/ developerworks/power. Resources describing the PowerPC architecture and processor cores.

- See MIPS Run, 2nd Edition, Dominic Sweetman, Morgan Kaufmann Publishers, 2006. Describes the MIPS architecture, instructions set, and programming.

## EXERCISES

EXERCISE 7.1 Suppose an embedded system includes two processor cores with a 32-bit wide dual-port memory for sharing data between the processors. Processor 1 is little endian, and processor 2 is big endian. Use the hexadecimal values 1234 (16 bits) and 12345678 (32 bits) to show how data is not shared correctly. How might the problem be remedied?

EXERCISE 7.2 Write Gumnut instructions to evaluate the expression 2(x + 1), assuming the value of x is in register r2 and the result is to be put in r7.

EXERCISE 7.3 Write Gumnut instructions to evaluate the expression 3(x-1), assuming the value of x is in register r2 and the result is to be put in r7. EXERCISE 7.4 Write Gumnut instructions to clear bits 0 and 1 of the value in register r1, leaving other bits unchanged, and to put the result in r2.

EXERCISE 7.5 Write Gumnut instructions to multiply the value in r4 by 18, ignoring the possibility of overflow. Hint:  $18 = 16 + 2 = 2^4 + 2^1$ .

EXERCISE 7.6 Write Gumnut instructions to increment the value in r3 modulo 60. If the result is 0, the value in r4 is to be incremented modulo 24.

EXERCISE 7.7 Write Gumnut instructions to test whether the 8-bit value in memory location 10 is equal to 99. If so, location 11 is to be set to 1; otherwise, location 11 is to be cleared to 0.

EXERCISE 7.8 Write Gumnut instructions to test whether r3 is 1 and input register 7 is also 1. If so, output register 8 is to be set to the hexadecimal value 3C.

EXERCISE 7.9 Write a Gumnut subroutine to clear a number of consecutive locations in memory to 0. The first address is provided in register r2 and the number of locations is provided in r3. Show a call to the subroutine to clear 10 locations starting from address 196.

EXERCISE 7.10 Write a complete Gumnut program to find the average of a sequence of eight 8-bit numbers stored in memory, and to write the result into a location in memory. Initialize the eight numbers to be the integers 2, 4, 6, ..., 16. Use a 16-bit sum to calculate the average, and shift instructions to divide by 8.

EXERCISE 7.II Write a complete Gumnut program that monitors the value of input controller register 10. When the value changes from 0 to a non-zero value, the program increments a 16-bit counter and writes the counter value to output controller registers 12 (least significant byte) and 13 (most significant byte). The program should not terminate.

EXERCISE 7.12 Using the information in Appendix D, determine the encoding for the following Gumnut instructions:

- a) sub r3, r1, r0

- b) and r7, r7, 0x20

- c) ror r1, r1, 3

- d) Idm r4, (r3)+1

- e) out r4, 10

- f) bz +3

- g) jsb 0x68

EXERCISE 7.13 What Gumnut instructions are encoded by the following 18-bit hexadecimal values?

- a) 009C0

- b) 38227

- c) 3353D

- d) 24AFD

- e) 3EA02

- f) 3C580

- g) 3F401

EXERCISE 7.14 Modify the design in Figure 7.8 to provide separate instruction and data memories for the 8051: a  $64K \times 8$ -bit ROM for the instruction memory and a  $64K \times 8$ -bit asynchronous SRAM for the data memory. The ROM has the same control signals as the SRAM except for the  $\overline{WE}$  signal.

EXERCISE 7.15 Suppose a cache can satisfy a processor request in 5ns if it has a hit; otherwise the memory access time of 20ns must be added to the hit time. What is the average access time seen by the processor core for instructions for miss rates of 5%, 2% and 1%?

EXERCISE 7.16 Suppose a CPU with 32-bit instructions has an instruction cache with 16-byte lines. Addresses refer to bytes in memory. The cache is initially empty. Instructions are then fetched from the following addresses in order: 0, 4, 8, 92, 96, 100, 4, 8, 12, 16. For each fetch, determine whether the cache hits or misses. Assume no lines are replaced during execution of the sequence.

# I/O INTERFACING

# 8

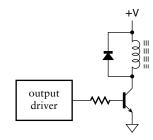

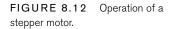

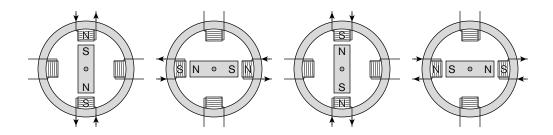

In the previous chapter, we introduced the notion of input/output (I/O) controllers that connect an embedded computer system with devices that sense and affect real-world physical properties. In this chapter, we will describe a range of devices that are used in embedded systems and show how they are accessed by an embedded processor and by embedded software.

## 8.1 I/O DEVICES

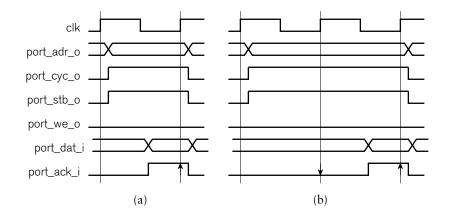

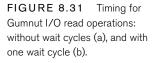

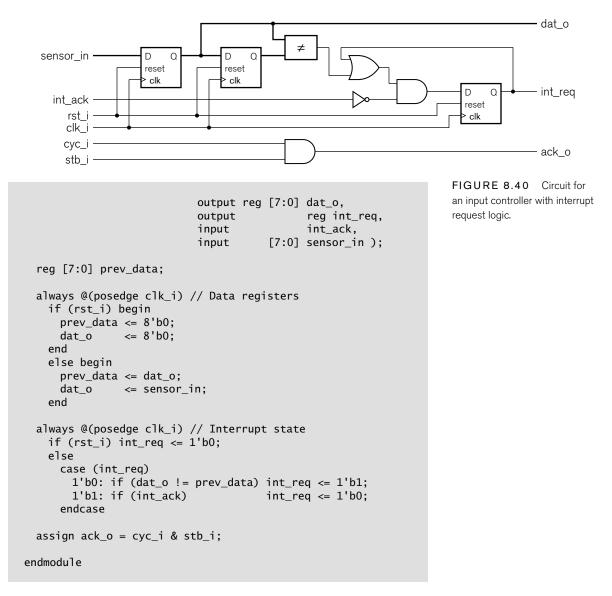

Digital systems with embedded computers are pervasive in our lives. We interact with many of them directly. Some are tools that we use in activities such as communication, entertainment, and information processing. These digital systems must incorporate human interface devices to allow us to control their operation and to receive responses. Other digital systems operate autonomously or under indirect control from us. Examples of such systems include industrial control systems, remote sensing devices and telecommunications infrastructure. These systems must incorporate devices to sense and affect the state of the physical world, as well as devices to communicate with one another, with controlling computers and with human interface devices.