# FPGA Implementation of MIMO Wireless Communications System

Ian Griffiths Supervised by Assoc. Prof. Brett Ninness

November 1, 2005

A thesis submitted in partial fulfillment of the requirements for the degree of Bachelor of Engineering in Computer Engineering at The University of Newcastle, Australia.

#### Abstract

Wireless communications have grown tremendously over the last decade, wireless LAN and mobile telephones have been the main reasons for the growth. There is a demand for ever faster wireless communications as this will allow for new applications such as widespread wireless broadband Internet access.

Multi-Antenna transmission schemes, using multiple antennas at the transmitter and/or receiver, have been proposed as a way to fulfill the demand for increased capacity. They are particularly attractive because they do not require any additional transmission bandwidth, and unlike traditional systems use multi-path interference to their benefit.

The aim of this project is to implement a particular multi-antenna scheme, a  $2 \times 2$ Alamouti code, on a PCI testbed card developed by the University. The testbed is very flexible, most of the computing power is provided by a 600,000 gate Xilinx FPGA. There are also 12 sockets that can be used for radio transceiver modules, or custom ASICs.

At the time of writing, designs have been created for all the major components of a MIMO system except for a channel estimator. The designs have been verified by simulation, both before mathematical simulation, and behavioural simulation of VHDL code. The simulation results have been favourable with the MIMO scheme significantly outperforming the equivalent SISO scheme.

# **Key Contributions**

The key contributions I have made to this project are:

- Creation of Octave (MATLAB) simulation of a MIMO wireless communications system using the Alamouti code.

- Implementation of the components of MIMO system using the C programming language, allowing bit accurate simulation of final hardware design

- Design of hardware implementation of components of MIMO system and writing VHDL code to implement these designs

Ian Griffiths

Brett Ninness

# Contents

| 1        | Introduction  |                             |                                          |    |  |  |  |  |  |

|----------|---------------|-----------------------------|------------------------------------------|----|--|--|--|--|--|

|          | 1.1           | Motiva                      | ation                                    | 1  |  |  |  |  |  |

| <b>2</b> | The           | Theoretical Background      |                                          |    |  |  |  |  |  |

|          | 2.1           |                             | ity of Wireless Communication Systems    | 2  |  |  |  |  |  |

|          | 2.2           | -                           | $\dot{\mathbf{r}}$                       |    |  |  |  |  |  |

|          | 2.3           | Model                       | ling the Wireless Communications Channel | 4  |  |  |  |  |  |

|          | 2.4           | Multi-Antenna Systems     5 |                                          |    |  |  |  |  |  |

|          | 2.5           |                             | lamouti Code                             |    |  |  |  |  |  |

|          | 2.6           | Chann                       | el Estimation                            | 9  |  |  |  |  |  |

| 3        | Nev           | vcastle                     | University Wireless Testbed Project      | 10 |  |  |  |  |  |

| Ū        | 3.1           |                             | ation for Testbed                        | 10 |  |  |  |  |  |

|          | 3.2           |                             | ed Hardware                              |    |  |  |  |  |  |

|          | 3.3           |                             | ed Final Year Projects                   |    |  |  |  |  |  |

| 4        | Simulation 13 |                             |                                          |    |  |  |  |  |  |

| т        | 4.1           |                             |                                          |    |  |  |  |  |  |

|          | 7.1           | 4.1.1                       | Alamouti Encoder                         |    |  |  |  |  |  |

|          |               | 4.1.2                       | Channel Estimator                        |    |  |  |  |  |  |

|          |               | 4.1.3                       | Alamouti Decoder                         |    |  |  |  |  |  |

|          | 4.2           | -                           | evel Simulation                          |    |  |  |  |  |  |

|          | 4.2           | 4.2.1                       | Alamouti Encoder                         |    |  |  |  |  |  |

|          |               | 4.2.1                       | Channel Estimator                        |    |  |  |  |  |  |

|          |               |                             |                                          |    |  |  |  |  |  |

|          |               | 4.2.3                       | Alamouti Decoder                         |    |  |  |  |  |  |

|          | 4.0           | 4.2.4                       | Fixed Point                              |    |  |  |  |  |  |

|          | 4.3           | Simula                      | ation Results                            | 19 |  |  |  |  |  |

## CONTENTS

|              | 4.4                                                                                                                             | Other Work Completed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                              |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| <b>5</b>     | Har                                                                                                                             | Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |  |  |  |  |  |

|              | 5.1                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |  |  |  |  |  |

|              | 5.2                                                                                                                             | Alamouti Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                              |  |  |  |  |  |

|              | 5.3                                                                                                                             | Alamouti Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                              |  |  |  |  |  |

|              | 5.4                                                                                                                             | Channel Estimator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                              |  |  |  |  |  |

| 6            | Conclusions and Further Work 2                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |  |  |  |  |  |

|              | 6.1                                                                                                                             | Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                              |  |  |  |  |  |

|              | 6.2                                                                                                                             | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                              |  |  |  |  |  |

| $\mathbf{A}$ | Hig                                                                                                                             | High Level Simulation Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |  |  |  |  |  |

|              | A.1                                                                                                                             | Alamouti Encoder Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                              |  |  |  |  |  |

|              | A.2                                                                                                                             | Channel Estimator Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                              |  |  |  |  |  |

|              | A.3                                                                                                                             | Alamouti Decoder Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                                                              |  |  |  |  |  |

| в            |                                                                                                                                 | Low-Level Simulation Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 |  |  |  |  |  |

| в            | Low                                                                                                                             | -Level Simulation Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                              |  |  |  |  |  |

| В            | Low<br>B.1                                                                                                                      | <b>-Level Simulation Source Code</b><br>BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>32</b><br>32                                                 |  |  |  |  |  |

| в            |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |  |  |  |  |  |

| В            | B.1                                                                                                                             | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                              |  |  |  |  |  |

| в            | B.1<br>B.2                                                                                                                      | BPSK Modulator    .    .    .    .      Alamouti Encoder    .    .    .    .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32<br>33                                                        |  |  |  |  |  |

| в            | B.1<br>B.2<br>B.3                                                                                                               | BPSK Modulator       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 32<br>33<br>33                                                  |  |  |  |  |  |

| в            | <ul><li>B.1</li><li>B.2</li><li>B.3</li><li>B.4</li><li>B.5</li></ul>                                                           | BPSK Modulator       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 32<br>33<br>33<br>34                                            |  |  |  |  |  |

|              | <ul><li>B.1</li><li>B.2</li><li>B.3</li><li>B.4</li><li>B.5</li></ul>                                                           | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36                                      |  |  |  |  |  |

|              | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>Har</li> </ul>                                        | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36<br><b>39</b>                         |  |  |  |  |  |

|              | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>Har</li> <li>C.1</li> </ul>                           | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36<br><b>39</b><br>39                   |  |  |  |  |  |

|              | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>Har</li> <li>C.1</li> <li>C.2</li> </ul>              | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36<br><b>39</b><br>39<br>40             |  |  |  |  |  |

|              | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>Har</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> </ul> | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36<br><b>39</b><br>39<br>40<br>40       |  |  |  |  |  |

|              | <ul> <li>B.1</li> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>Har</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> </ul> | BPSK Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>33<br>34<br>36<br><b>39</b><br>39<br>40<br>40<br>41 |  |  |  |  |  |

## iii

# Chapter 1

# Introduction

# 1.1 Motivation

In recent years the telecommunications industry has experienced phenomenal growth, particularly in the area of wireless communication. This growth has been fueled by the widespread popularity of mobile telephones and wireless computer networking.

However, there are limits to growth, and the radio spectrum used for wireless communications is a finite resource. Therefore considerable effort has been invested in making more efficient use of it. Using the spectrum more efficiently caters for the ever increasing demand for faster communications since more bits per second can be transmitted using the same bandwidth.

Recently a major research focus in this area has been the use of multiple antennas for transmitting and receiving instead of the traditional single antenna systems [1]. It has been proposed that using multiple transmit and receive antennas, and associated coding techniques could increase the performance of wireless communication systems [3, 6, 7, 8]. So far there has been a lot of theoretical research but relatively few practical systems have been demonstrated [4, 5].

The university has undertaken a research project to create a testbed for multiantenna wireless communications. The outcome of this project is a PCI card with a programmable logic chip and sockets for multiple pluggable modules that can be used for radio transceivers or custom signal processing hardware.

I will be implementing a particular scheme known as the "Alamouti scheme" (see Section 2.5 for more detail). It is one of the simplest multi-antenna schemes, as it uses only 2 transmit and 2 receive antennas.

# Chapter 2

# **Theoretical Background**

In this chapter the theory underlying this project and the MIMO system being implemented will be examined. We will begin with a brief overview of the capacity of wireless communication systems, and examine the environments in which they are used. Finally the theory of multi-antenna communications is introduced. Particular attention is paid to the Alamouti code, and associated techniques such as channel estimation.

## 2.1 Capacity of Wireless Communication Systems

In 1948 Claude Shannon discovered that there was an upper limit to the capacity of a channel for error free transmission of information:

$$C = B \log_2(1 + SNR) \tag{2.1}$$

where B is the transmission bandwidth, and SNR is the signal to noise ratio of the channel. This equation gives the absolute maximum capacity of the channel (in bits/second). Thus it appears the only way to increase the capacity of the communications system is to increase the bandwidth used in transmission, or to increase SNR.

Multi-Antenna systems use a rather novel approach to increase the overall capacity of a wireless communications system; use more channels. Each of the individual transmission channels is still limited according to Equation 2.1, however the overall capacity of the system is now the sum of the capacities of the individual channels.

In the case of multi-antenna systems these individual channels are not totally separate transmission channels. Instead, these systems exploit multi-path propagation to provide independent channels even though the radio signals are being sent across the

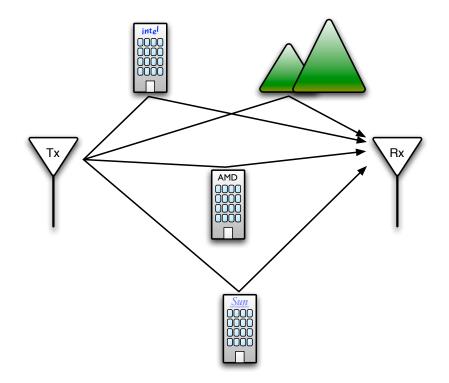

Figure 2.1: Simplified example of multi-path propagation

same transmission environment.

# 2.2 The Transmission Environment

It is useful to understand a little about the transmission environment of a modern wireless communication system before investigating how multi-antenna systems work. As stated in the introduction, the major drivers of wireless communication are mobile telephones and wireless LANs (e.g. IEEE 802.11b otherwise known as Wi-Fi), therefore it is prudent to examine the typical transmission environments in which these systems operate.

The wireless environment in which these technologies operate (urban settings) is typically characterised by multi-path propagation. As the name suggests, multi-path propagation occurs when there are multiple transmission paths between the transmitter and the receiver. In an urban environment this is typically caused by the radio waves reflecting off buildings and other obstacles. A simplified example of this effect can been seen in Figure 2.1 In a traditional single antenna system (henceforth referred to as Single Input, Single Output or SISO) multi-path propagation can be a problem as it causes Inter-Symbol Interference. The traditional response to multi-path interference has been to lengthen the symbol period so that most of the reflections have died out before the symbol is sampled at the receiver. Obviously, unless other measures are taken, this will reduce the data rate of the system.

Multi-Antenna systems (referred to as Multiple Input, Multiple Output or MIMO<sup>1</sup>) however, use multi-path propagation to their benefit, and in fact rely on some amount being present.

### 2.3 Modelling the Wireless Communications Channel

Under certain assumptions the complicated transmission environment can be mathematically modelled by using complex numbers to represent the magnitude and phase change of the transmission channel. The assumption made by this model is that the channel is a so called "flat fading" channel.

Flat fading refers to the frequency response of the channel being "flat", meaning that all frequencies are subjected to the same attenuation. One of the side effects of flat fading is that there is no Inter-Symbol Interference (ISI).

Even if the actual transmission environment is not flat fading this model can still be used provided the bandwidth of the transmitted signal is small enough. In particular the bandwidth needs to be less than the inverse of the delay spread<sup>2</sup> of the channel for the flat-fading assumption to hold. This means that there should be negligible ISI.

The use of complex numbers in the model derives from the fact that it is possible to represent a real-valued bandpass signal using complex numbers, see appendix A.1 in [2]. It is from this complex number representation that the "in-phase" and "quadrature" components of a signal are derived. The in-phase component is the real part of the complex representation, and the quadrature component is the imaginary part.

For a SISO system this model can reduce the entire transmission environment to a single complex number. The system can then be represented using Equation 2.2, where h is the complex number representing the channel, x is the input signal, and e is a

<sup>&</sup>lt;sup>1</sup>I will generally refer to MIMO systems, which have multiple antennas at both transmitter and receiver, however it is also possible to have Multiple Input, Single Output (MISO) or Single Input, Multiple Output (SIMO) systems. Much of the theory applies to these systems also.

<sup>&</sup>lt;sup>2</sup>The delay spread of a channel is the elapsed time between when the first and last of the multi-path reflections arrive at the receiver.

complex number modelling the thermal noise at the receiver.

$$y = hx + e \tag{2.2}$$

Similarly MIMO systems can be modelled with Equation 2.3. The variables have the same meaning as for the SISO case, however instead of the scalar complex numbers in Equation 2.2 the variables are matrices of complex numbers.

$$Y = HX + E \tag{2.3}$$

### 2.4 Multi-Antenna Systems

One possible way to improve the reliability of wireless communications is to employ *diversity*. Diversity is the technique of transmitting the same information across multiple channels to achieve higher reliability. It operates on the principle that it is unlikely that all of the channels used to transmit the redundant information will be experiencing *deep*  $fading^3$  at the same time. Even if one particular channel is unusable the information may still be recovered from the redundant transmission over the other channels. Therefore the overall reliability of the communications system is improved, at the cost of transmitting redundant information.

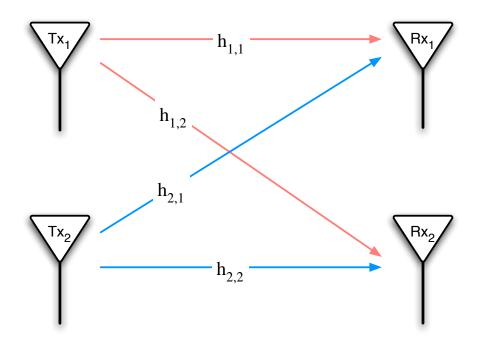

If multiple antennas are used at the transmitter or receiver there are potentially multiple transmission channels between the transmitter and receiver. See Figure 2.2 for an example of the potential channels in a  $2 \times 2$  MIMO system. These multiple channels can be used to exploit diversity.

In the 2×2 system in Figure 2.2 there is the potential for both transmit and receive diversity. Receive diversity is when the same information is received by different antennas. For instance the information sent from  $Tx_1$  is transmitted across channels  $h_{1,1}$  and  $h_{1,2}$ , and received by both  $Rx_1$  and  $Rx_2$ . Transmit diversity is when the same information is sent from multiple transmit antennas. One possible way to achieve this is to code across multiple symbols periods. For instance, at time t antenna  $Tx_1$  could transmit the symbol s then at time t + 1 antenna  $Tx_2$  would transmit the same symbol, s. The Alamouti scheme uses a method similar to this to obtain transmit diversity.

MIMO systems are able to achieve impressive improvements in reliability and capacity by exploiting the diversity offered by the multiple channels between the transmit and

$<sup>^{3}</sup>$ Wireless channels are time varying, and occasionally the channel gain may drop to zero. This is called deep fading, and makes the channel unable to transmit any useful information.

Figure 2.2: Potential Communications Channels in a  $2 \times 2$  MIMO system

receive antennas. Different coding schemes vary in their exact approaches, however all seek to use the available channels to increase capacity and/or reliability.

### 2.5 The Alamouti Code

The coding scheme implemented in this project is an Alamouti code, therefore this code will be examined in closer mathematical detail.

The Alamouti code, so called because it was proposed by S.M Alamouti in [7], belongs to a class of codes called Space-Time Block Codes (STBC). The *Space-Time* refers to coding across space and time. Coding across space by using multiple transmit and receive antennas, and across time by using multiple symbol periods. Like normal block codes the Alamouti code operates on blocks of input bits, however rather than having 1 dimensional code vectors it has 2 dimensional code matrices.

STBCs can be described by a code matrix, which defines what is to be sent from the transmit antennas during transmission of a block. The code matrix is of dimension  $N_t \times t_b$  where  $N_t$  is the number of transmit antennas and  $t_b$  is the number of symbol periods used to transmit a block. So the rows of the matrix represent the transmit antennas, and the columns are the time (symbol) periods.

The code matrix for the Alamouti code is given in Equation 2.4.

$$X = \begin{bmatrix} s_1 & -s_2^* \\ s_2 & s_1^* \end{bmatrix}$$

(2.4)

The code belongs to a special subclass of STBCs known as Orthogonal Space Time Block Codes (OSTBC). The code matrices of OSTBCs satisfy the following constraint.

$$XX^{H} = \sum_{n=1}^{n_{s}} |s_{n}|^{2} \cdot (\alpha I)$$

(2.5)

where  $n_s$  is the number of symbols,  $s_n$  is the nth complex symbol,  $\alpha$  is an arbitrary constant and  $(.)^H$  denotes the Hermitian conjugate<sup>4</sup>.

There are a number of properties that make OSTBCs particularly interesting. Foremost is that Maximum Likelihood (ML) detection of different symbols is *decoupled*. In the case of the Alamouti code this means that the two symbols which are coded together can be detected independently at the receiver. In other words the same techniques used to detect symbols one at a time in a SISO scheme can be used in the Alamouti scheme as well.

Using Equations 2.3 and 2.4 the received matrix in a 2x2 system can be written as

$$Y = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \begin{bmatrix} s_1 & -s_2^* \\ s_2 & s_1^* \end{bmatrix} + \begin{bmatrix} e_{11} & e_{12} \\ e_{21} & e_{22} \end{bmatrix}$$

(2.6)

now, let

$$r_{11} \triangleq h_{11}s_1 + h_{12}s_2 + e_{11} \tag{2.7}$$

$$r_{12} \triangleq -h_{11}s_2^* + h_{12}s_1^* + e_{12} \tag{2.8}$$

$$r_{21} \triangleq h_{21}s_1 + h_{22}s_2 + e_{21} \tag{2.9}$$

$$r_{21} \triangleq -h_{21}s_2^* + h_{22}s_1^* + e_{22} \tag{2.10}$$

These are the signals that are received by each of the antennas at the receiver across the two time periods. The above expressions can be obtained by expanding Equation 2.6. The first digit of the subscript denotes the receive antenna, and the second digit is the

<sup>&</sup>lt;sup>4</sup>The Hermitian conjugate of a matrix is the complex conjugate, transpose, i.e.  $X^{H} = (X^{*})^{T}$

time period when the signal is received. Equation 2.6 can now be re-written as

$$Y = \begin{bmatrix} r_{11} & r_{12} \\ r_{21} & r_{22} \end{bmatrix}$$

(2.11)

In [7] Alamouti states that the transmitted symbols  $s_1$  and  $s_2$  can be estimated in a maximum likelihood fashion by first combining the received signals according to the following equations

$$\tilde{s}_1 = h_{11}^* r_{11} + h_{12} r_{12}^* + h_{21}^* r_{21} + h_{22} r_{22}^*$$

(2.12)

$$\tilde{s}_2 = h_{12}^* r_{11} - h_{11} r_{12}^* + h_{22}^* r_{21} - h_{21} r_{22}^*$$

(2.13)

and then using a standard Maximum Likelihood detector to attempt to recover  $s_1$  and  $s_2$  from  $\tilde{s_1}$  and  $\tilde{s_2}$ . This is the *decoupled* ML detection that is common to all OSTBCs.

The validity of Alamouti's proposed system can been seen by substituting the values of  $r_{11}$ ,  $r_{12}$ ,  $r_{21}$  and  $r_{22}$  from Equations 2.7, 2.8, 2.9 and 2.10 into Equations 2.12 and 2.13 to obtain the following.

$$\tilde{s_{1}} = h_{11}^{*}(h_{11}s_{1} + h_{12}s_{2} + e_{11}) +h_{12}(-h_{11}^{*}s_{2} + h_{12}^{*}s_{1} + e_{12}^{*}) +h_{21}^{*}(h_{21}s_{1} + h_{22}s_{2} + e_{21}) +h_{22}(-h_{21}^{*}s_{2} + h_{22}^{*}s_{1} + e_{22}^{*}) = s_{1}(|h_{11}| + |h_{12}| + |h_{21}| + |h_{22}|) +h_{11}^{*}e_{11} + h_{12}e_{12}^{*} + h_{21}^{*}e_{21} + h_{22}e_{22}^{*}$$

$$(2.14)$$

similarly

$$\tilde{s}_{2} = s_{2}(|h_{11}| + |h_{12}| + |h_{21}| + |h_{22}|)$$

$$-h_{11}e_{12}^{*} + h_{12}^{*}e_{11} - h_{21}e_{22}^{*} + h_{22}^{*}e_{21}$$

$$(2.15)$$

Equations 2.14 and 2.15 show that when the received signals are combined according to Equations 2.12 and 2.13 the transmitted symbols are combined coherently and weighted by a positive factor, i.e.  $|h_{11}| + |h_{12}| + |h_{21}| + |h_{22}|$ . The noise samples however, get combined in an incoherent manner. This is how the Alamouti scheme is able to achieve an improvement in performance over SISO systems.

# 2.6 Channel Estimation

To use the equations in the above section to decode the received signal the receiver needs to have so-called *channel knowledge*. This means the values of the  $h_{xy}$  terms in Equation 2.6 must be known. In practice it is not possible to obtain exact values for these terms, however they can be estimated.

There are a number of methods for estimating the channel matrix, the simplest being training based estimation. With training based channel estimation a data block known to both the transmitter and receiver, called the training block, is transmitted before the start of the actual data in each code block. The channel matrix can then be estimated at the receiver using the following equation.

$$\hat{H} = Y_t X_t^H (X_t X_t^H)^{-1}$$

(2.16)

where  $X_t$  is the known training block sent by the transmitter,  $Y_t$  is the received training block, and  $(.)^H$  denotes the Hermitian conjugate.

Equation 2.16 relies on a the training block being designed to satisfy the following equation

$$X_t X_t^H = \rho^2 I \tag{2.17}$$

fortunately, by design the Alamouti code matrix, and any other OSTBC, satisfies this equation. So a possible training block is simply a known pre-amble prepended before the actual data.

The validity of this method for channel estimation can be seen by substituting Equations 2.3, and 2.17 into Equation 2.16.

$$\hat{H} = (HX_t + E)X_t^H (X_t X_t^H)^{-1} = HX_t X_t^H (X_t X_t^H)^{-1} + EX_t^H (X_t X_t^H)^{-1} = H + EX_t^H (\rho^2 I)^{-1} = H + error term$$

The channel estimate obtained via this method can then be used in the detector described in Section 2.5. This method is not optimal in a maximum likelihood sense, however it is fairly easy to understand and implement.

# Chapter 3

# Newcastle University Wireless Testbed Project

This chapter will review the wireless testbed that is the target device for this project. First the motivations for creating the testbed are explained, then there will be a brief overview of the hardware present on the card. Finally some related final year projects are mentioned.

### 3.1 Motivation for Testbed

The reasons for wanting a device to be able to conduct practical testing of MIMO systems are obvious, however, there are many different approaches to building such a device ranging in complexity, cost and flexibility.

In [5] the authors put forward a classification scheme for different types of testbeds. The simplest approach they recognised is targeted towards burst mode transmissions, and offline signal processing. This design minimises the cost, however it also severely limits the scenarios in which the testbed can be used, because the signal processing is not done in real-time. The testbed card used in this project is much more powerful and provides for real-time operation, using a Field Programmable Gate Array (FPGA) chip to perform the signal processing. Thus it lies towards the opposite end of the spectrum presented by the authors.

Employing a more sophisticated approach allows the testbed card to more accurately reflect the environments where the MIMO algorithms are likely to be implemented. Not only is real-time transmission and decoding possible, but the hardware present is similar to the final deployment environment. Typically the deployment environments will have

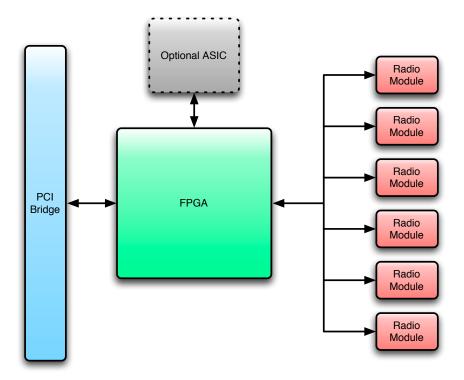

Figure 3.1: Testbed Block Diagram

limited computing power, or use Application Specific Integrated Circuits (ASICs). The testbed card has an FPGA for signal processing. Typically FPGAs are used as an intermediate step in the development of ASICs so the testbed card will also be valuable in the development of ASICs.

### 3.2 Testbed Hardware

The testbed that has been developed at the university has been designed for flexibility. There are sockets for 12 expansion modules on the card. These sockets may be used for radio transceiver modules, or a custom ASIC, or numerous other possibilities.

The main computing power of the board comes from a programmable logic device, which can be easily reconfigured to implement any coding scheme, even SISO schemes. In addition an ASIC may be added to the board to provide additional signal processing capabilities.

A block diagram of the architecture of the testbed can be seen in Figure 3.1. This shows only one possible configuration of the card, however, it gives an idea of the reconfigurability of the testbed. The radio modules may be swapped for different units, or even exchanged for a Digital Signal Processing (DSP) chip, or something else entirely. The FPGA, which is central, can be reprogrammed to perform different tasks, or route signals in different directions. The only function that is fixed is the PCI bridge, however this is obviously not a drawback as the PCI standard is somewhat fixed.

The testbed also has provisions for using a custom ASIC, which will not be used in this project. However, in the long term this expandability will greatly increase the possible applications for the testbed. In addition to being used as a prototyping tool the testbed could be used to easily verify ASIC designs in a realistic setting before they go into large scale production.

The radio modules used in this project are based on a commercially available 2.4GHz transceiver (Maxim MAX2822). These chips are compatible with the physical layer of the IEEE 802.11b standard for wireless networking. However they are not being used in this manner on the testbed, rather they are being used simply as radio transmitters and receivers.

### **3.3 Related Final Year Projects**

A number of other students have worked on the testbed at various stages of its development. While my work stands alone to some degree, it also relies on the work of these students. Therefore it is prudent to reference their work.

In 2004 Chris Shaw completed a final year project entitled "Linux Device Driver for Wireless Testbed". He worked on a Graphical User Interface (GUI) program to ease the use of the testbed hardware, and extended a driver written by Alan Murray in 2003/2004. However, at the time there was no hardware available to him, so he implemented a simulation of the hardware in the driver.

This year in his project titled "Linux Device Driver and Graphical Interface Support for Research Testbed" Nathan Tomkins is re-implementing much of Chris' work. He is porting Alan Murray's driver to the 2.6 series Linux kernel<sup>1</sup>, and writing a new GUI using the Python programming language.

In addition to these students John Dalton has been working on the testbed hardware. He designed the testbed card and is also carrying out testing.

<sup>&</sup>lt;sup>1</sup>The original driver was based on the 2.4 series Linux kernel, however since it was written nearly every Linux distribution has switched to the newer 2.6 kernels. Thus it is becoming rather difficult to use the driver, a situation which will only get worse with time.

# Chapter 4

# Simulation

I followed the general hardware design process in this project, the first stage of which is to conduct a high-level simulation of the proposed design to work through any algorithmic or mathematical issues. Typically this simulation is produced using MATLAB, or a similar maths package.

After the simulation is completed and the algorithm is correct the next stage is to move onto a low-level "bit accurate" C implementation. Bit accurate refers to the fact that for a given set of input bits the C implementation will produce the correct output bits. This step is used because typically C is much easier to write and debug than Hardware Description Language (HDL) code such as VHDL.

The next stage is to implement the design using the chosen HDL, in this case VHDL. The bit accurate C code is used to verify that the VHDL is correct by comparing the outputs of the two implementations.

Once the VHDL is debugged in simulation and producing the correct output the design can be uploaded to the FPGA for final testing.

In this chapter the simulations, both high- and low-level that were created during the project will be examined, and the results obtained will be presented.

# 4.1 High-Level Simulation

The initial high-level simulation was implemented using Octave, an open source equivalent of MATLAB. The code used for simulation can be found in Appendix A.

#### 4.1.1 Alamouti Encoder

The first component in the system that was simulated was the encoder. This was chosen first as it is a fairly simple component.

There are two distinct steps in the encoding process. First the input bits are modulated into symbols (represented by complex numbers), then the complex symbols are encoded using the Alamouti code matrix given in Equation 2.4.

I have chosen to use a Binary Phase Shift Keying (BPSK) constellation for modulation. The main reason for using BPSK is because it is a very simple scheme. A side effect of the Alamouti scheme, which is a rate 1 code, is that the overall system has the same data rate as the SISO system using BPSK.

Initially the encoder I implemented was designed as a combined BPSK modulator and Alamouti encoder. The input bits were used to decide which of four matrices were output. The matrices were manually constructed and hard-coded into the simulation. This design made it fairly difficult to switch the modulation or coding scheme. It was also fairly error prone as the code matrices were manually constructed, and it was fairly easy to leave out a negative sign or make other simple mistakes. The main reason for using the combined design at first was because it was very simple to implement.

I revised the design to simulate the modulator and encoder separately in a slightly more modular fashion. This design allows for the modulation scheme to be easily changed, say to QPSK, or QAM. This more modular design was used at the lower level implementations also.

The source code for the simulated encoder can be found in Appendix A.1.

#### 4.1.2 Channel Estimator

As stated in Section 2.6 the Alamouti decoder needs channel knowledge, so a channel estimator is required.

In the high-level simulation the high level features of Octave were taken advantage of and Equation 2.16 was simply converted to Octave code. This approach is not possible for the low level implementations, instead the matrix operations must be implemented manually.

The source code for the channel estimator can be found in Appendix A.2.

#### 4.1.3 Alamouti Decoder

As with the encoder a simple, but fairly inflexible design was used initially for the decoder. This was design was chosen for the same reasons as with the encoder, simplicity

and ease of simulation.

The initial decoder design used a brute force technique that was by no means optimal in a computational complexity sense. It used the channel estimate, and the four <sup>1</sup> possible code matrices to construct an estimate of the potential received matrices. These were then compared to the actual received matrix and the one which was "closest" was deemed to be the correct output. The "closeness" of the pairs of matrices was evaluated by taking the Frobenius norm of the difference of the two.

The final decoder design uses the method presented in Section 2.5 with a combiner and a separate symbol detector. In the case of BPSK the symbol detector can just be a simple threshold detector. This decoder design is also used in the low level implementations.

The source code for the decoder can be found in Appendix A.3.

# 4.2 Low-Level Simulation

The low-level simulation was carried out using programs written in C, which output data to, and read input data from plain text files. A number of supporting programs were written to enable the results to be imported into Octave for analysis and graphing.

As mentioned above the high level constructs such as matrix operations, and complex numbers had to be manually implemented for this simulation. The representation of complex numbers in particular took a number of revisions before a final structure was settled upon. The initial approach was to use the struct keyword of C to create a complex number "structure". This approach was discarded because this approach could not be used in the VHDL hardware design. Instead the complex numbers were simply represented as separate arrays or variables for the real and imaginary parts of each number.

The source code for the low-level simulation can be found in Appendix B

#### 4.2.1 Alamouti Encoder

The encoder used the same design as the high-level simulation, with a separate BPSK modulator and Alamouti encoder.

The BPSK modulator took an 8-bit **char** input, and produced two arrays, representing the real and imaginary parts of the symbols, for output. It simply runs through the input testing a bit at a time. If the bit in question is a 1 then the symbol for a 1 is

<sup>&</sup>lt;sup>1</sup>When using BPSK modulation there are only 4 possible code matrices (X), corresponding to the input bits 00, 01, 10, and 11.

placed into the output arrays, otherwise the symbol for a 0 is put into the output. The actual symbols that are used to represent 1 and 0 are defined in a header file, so can be easily changed.

The Alamouti encoder takes the two arrays output by the BPSK modulator as input and produces two 2-dimensional arrays as output. These arrays represent the real and imaginary parts of the symbols that are sent to the Radio Frequency (RF) "front-ends" on each of the transmit antennas of the testbed card. It loops through the input arrays operating on pairs of symbols at a time. In line with Equation 2.4 the symbols are first copied straight through to the output arrays unmodified. Then the symbols are swapped over to the opposite transmit antenna and complex conjugated, also one symbol is negated. Complex conjugation is achieved by simply negating the imaginary part of the input before placing it into the output. Also the complex conjugation, and extra negation operations are combined into a single step for the relevant symbol by negating the real part instead of the imaginary.

The source code for the low-level encoder can be found in Appendix B.2

#### 4.2.2 Channel Estimator

When implementing the channel estimator it became obvious that if the training block was a pre-defined fixed matrix then Equation 2.16 simplifies to multiplying a matrix by another constant matrix. Equation 2.16, with the constant term highlighted, is repeated below

$$\hat{H} = Y_t \times \underbrace{X_t^H (X_t X_t^H)^{-1}}_{constant \ term}$$

(4.1)

This means that if the training block is fixed then the channel estimator is simply a complex matrix multiplier.

This is the basis for the design of the low-level channel estimator simulation. The training block, and the constant part of the channel estimation equation are stored in header files and are used in the code by using the **#include** directive. A small Octave script was written so that the training block could be defined in the script, then the constant term would be automatically calculated, and both then output straight into a header file ready for use. This script was then incorporated into the build process using the **Makefile**.

No real attempt was made to optimise the matrix multiplication process, three nested for loops were used, and one element of the output matrix was calculated at a time. It was decided that trying to optimise the C code would not be overly useful as the main purpose of the simulation was to be correct not optimal.

The source code for the low-level simulation of the Alamouti encoder can be found in Appendix B.3

#### 4.2.3 Alamouti Decoder

The Alamouti decoder uses the same design as the decoder in the high-level simulation, with a separate "combiner" and demodulator.

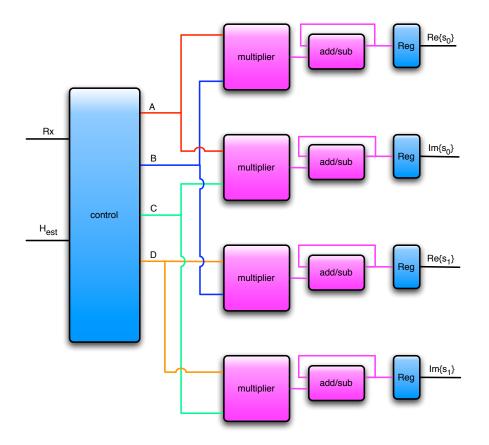

The actual algorithm implemented by the combiner is fairly straightforward, however for the low-level implementation the mathematical expressions for each symbol estimate were expanded and simplified to remove the complex numbers and operations. The resulting expressions are shown in Equations 4.2 - 4.5

$$s0_{re} = Re\{h_{0,0}\} \times Re\{y_{0,0}\} + Im\{h_{0,0}\} \times Im\{y_{0,0}\} \\ + Re\{h_{0,1}\} \times Re\{y_{0,1}\} + Im\{h_{0,1}\} \times Im\{y_{0,1}\} \\ + Re\{h_{1,0}\} \times Re\{y_{1,0}\} + Im\{h_{1,0}\} \times Im\{y_{1,0}\} \\ + Re\{h_{1,1}\} \times Re\{y_{1,1}\} + Im\{h_{1,1}\} \times Im\{y_{1,1}\}$$

(4.2)

$$s0_{im} = Re\{h_{0,0}\} \times Im\{y_{0,0}\} - Im\{h_{0,0}\} \times Re\{y_{0,0}\} \\ - Re\{h_{0,1}\} \times Im\{y_{0,1}\} + Im\{h_{0,1}\} \times Re\{y_{0,1}\} \\ + Re\{h_{1,0}\} \times Im\{y_{1,0}\} - Im\{h_{1,0}\} \times Re\{y_{1,0}\} \\ - Re\{h_{1,1}\} \times Im\{y_{1,1}\} + Im\{h_{1,1}\} \times Re\{y_{1,1}\}$$

(4.3)

$$s1_{re} = Re\{h_{0,0}\} \times Re\{y_{0,0}\} + Im\{h_{0,1}\} \times Im\{y_{0,0}\} \\ - Re\{h_{0,0}\} \times Re\{y_{0,1}\} - Im\{h_{0,0}\} \times Im\{y_{0,1}\} \\ + Re\{h_{1,1}\} \times Re\{y_{1,0}\} + Im\{h_{1,1}\} \times Im\{y_{1,0}\} \\ - Re\{h_{1,0}\} \times Re\{y_{1,1}\} - Im\{h_{1,0}\} \times Im\{y_{1,1}\}$$

(4.4)

$$s1_{im} = Re\{h_{0,1}\} \times Im\{y_{0,0}\} - Im\{h_{0,1}\} \times Re\{y_{0,0}\} \\ + Re\{h_{0,0}\} \times Im\{y_{0,1}\} - Im\{h_{0,0}\} \times Re\{y_{0,1}\} \\ + Re\{h_{1,1}\} \times Im\{y_{1,0}\} - Im\{h_{0,0}\} \times Re\{y_{0,1}\} \\ + Re\{h_{1,1}\} \times Im\{y_{1,0}\} - Im\{h_{0,0}\} \times Re\{y_{1,1}\}$$

(4.5)

So, after expansion and simplification, the expression for each component is essentially a sum of products.

The combiner inputs are four  $2 \times 2$  arrays, two for the real and imaginary parts of the channel estimate, and two for the real and imaginary parts of the received samples.

The outputs are two  $2 \times 1$  arrays, representing the real and imaginary parts of the two symbol estimates.

The BPSK demodulator part of the decoder exploits the sign bit of the 2's complement binary number format used in computers, and the fact that the BPSK constellation in use is made up of only real numbers. Because the transmitted symbols are real numbers only, the imaginary part of the input to the demodulator is discarded. Thus the demodulator simply outputs the inverse of the sign bit of the input. Therefore, any symbol with a negative real part is demodulated as 0, and any with a positive real part is demodulated as a 1.

The source code of the low-level implementation of the Alamouti decoder can be found in Appendix B.4.

#### 4.2.4 Fixed Point

In addition to implementing the complex numbers and matrix operations manually the low-level simulation was also converted to run using fixed-point arithmetic. The reason for this conversion is because the use of floating-point arithmetic in the final hardware design is infeasible because of the associated complexity. Therefore to maintain the bit accurate nature of the simulation it must also be converted to use fixed-point.

The conversion process involved first working out the dynamic range of the numbers at each stage in the system, and trying to assess the required accuracy. This assessment needed to be done so that a fixed point number format could be chosen. The choice of number format constrains both the dynamic range, and accuracy of the numbers represented, therefore care must be taking in choosing an appropriate number format.

A few formats were evaluated in the simulation, each with varying ranges and accuracies. The aim was to find the format that used the least bits, but still provided acceptable performance. The reason for wanting as few bits as possible is to try to make the hardware implementation as simple as possible. It takes less time to multiply two 8 bit numbers than it does to multiply two 32 bit numbers, and it uses far less hardware also. Thus it is easier to have an efficient hardware implementation if the number format used has as few bits as possible. The final design uses a 16-bit format with 8 bits for the integral part, and 8 bits for the fractional part, this is known as an 8.8 fixed point format.

After the number format was chosen, all the mathematical operations needed to be converted to fixed point also. This conversion process involves making sure that the radix point is in the correct place after the operation. For addition and subtraction the radix point does not move. However multiplication and division both move the radix point, so they must be corrected. For multiplication the correction is achieved using an arithmetic right shift, for division it is a left shift. Note, there are no divisions in the algorithms being implemented, only multiplication's.

The fixed-point conversion process was performed by first writing a header file that defined the fixed point types and also some functions to convert fixed-point numbers to floating-point and vice-versa. These functions were mostly used for debugging, however the floating-to-fixed conversion functions were used to simulate the analogue to digital converters at the receiver. Finally a function that performed fixed point multiplication was written, and all the multiplication operators were replaced with calls to this function.

The fixed-point conversion was carried out on a copy of the source code of the original floating-point simulation. This resulted in one fixed point simulation and one floating point one, this was intentional. Having two copies allowed the comparison of the fixed-point implementation to the floating-point one to make sure that the fixed-point implementation performed acceptably.

The source code for the fixed point functions can be found in Appendix B.5

# 4.3 Simulation Results

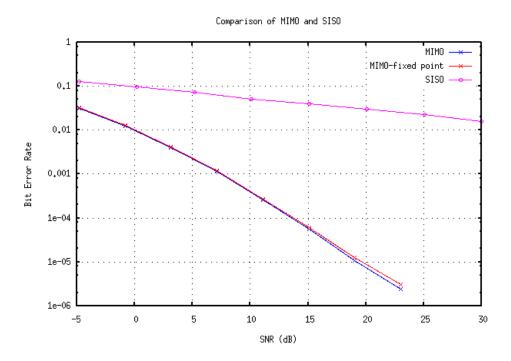

The simulation produced the expected results, confirming that there is a considerable performance gain from using the MIMO coding scheme. Figure 4.1 shows a comparison of the simulated MIMO and SISO schemes. As can be seen from the plot the MIMO scheme achieves a much lower Bit Error Rate at the same Signal to Noise Ratio than the SISO scheme. This simulation is perhaps a little unfair on the SISO scheme as the channel model in the simulation is very simplistic, and likely much "worse" than a real channel would be. The MIMO scheme is not greatly affected by this harsh channel because it is designed to work in this kind of environment.

Also, note that there is a curve for the fixed point implementation of the MIMO system. As can be seen in Figure 4.1 the fixed point implementation performs nearly as well as the floating point one, there is only a very minor difference in BER. This difference only really becomes apparent at higher signal to noise ratios, up to roughly 15 dB the two MIMO implementations are virually indistinguishable.

This plot was created using the low-level simulation. Previously an attempt was made to create a similar plot using the high-level simulation. This was not as successful because the simulation ran too slowly to capture enough data to make the plot accurate. It was calculated that using the high-level simulation it could take up to 70 hours to

Figure 4.1: Simulation Results - MIMO and SISO Comparison

obtain reliable data for a single point on the plot. However using the low-level simulation made it possible to collect all the data used in Figure 4.1 within one day.

### 4.4 Other Work Completed

Before the low-level simulation was implemented the initial high-level simulation was ported to C++ using the extension interface the Octave provides <sup>2</sup>. The major reason for doing this work was to speed up the simulation, and it was also thought that this could provide the basis for the low-level, bit accurate, simulation.

As noted in Section 4.3 the initial Octave simulation ran fairly slowly. After porting this simulation to C++ it was able to simulate around 450 bits/s on a PC with an AMD Athlon 2000+ processor. However after writing the C++ version the initial Octave implementation was revised and optimised. After optimisation the Octave simulation was able to simulate 400 bits/s on the same PC.

In the meantime it was realised that it would be fairly difficult to make the C++ code form the basis of the bit accurate implementation. The main reason for this difficulty is because the interface to Octave requires that high-level C++ features, such as object-

<sup>&</sup>lt;sup>2</sup>This is similar to the Mex interface that MATLAB provides to allow functions to be coded in C.

orientation, be used. These features do not map too well into hardware, so it was decided to cease developing the C++ code, and begin the low-level simulation again from scratch using C rather than C++.

# Chapter 5

# Hardware Design

After the simulations were completed and the expected results were verified the final step in the hardware design process was to actually implement the designs in a Hardware Description Language (HDL). For this project VHDL was chosen to implement the designs as I have previous experience using it.

Implementing the designs in hardware poses some unique challenges. Considerations such as how many clock cycles a given operation takes, or whether an operation can be completed in parallel with another, rarely matter at earlier stages in the process. However details like these are critically important when implementing hardware.

At the time of writing all the major components in the MIMO system have been implemented as VHDL except for the channel estimator. The implemented components have all been tested to verify correct operation. All components produce exactly the same output as the bit accurate low-level simulation, so performance will be identical. However, the individual components have not yet been joined together to form a complete system. See Section 6.1 for more details.