Diamond Sponsor:

# Engineers' Guide to FPGA & CPLD Solutions

# Trends to Watch in the Evolution of Programmable Logic

Dual-Architecture FPGAs Provide New Opportunities for Embedded Developers

**FPGAs Pave Way for 5G, 400Gb/s Communications**

## Annual Industry Guide

Hardware and software for FPGA system and application engineers

## EECatalog www.eecatalog.com/fpga

**Gold Sponsors**

#### **Featured Products**

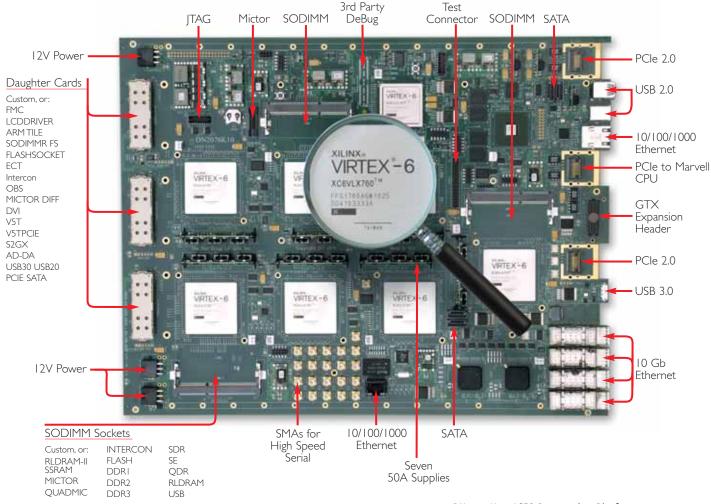

The Virtex®-6 FPGA Connectivity Kit is a high performance connectivity development, debug and demonstration platform.

The X6-RX from Innovative Integration is a flexible receiver that integrates IF digitizing with signal processing on a PMC IO module.

The XDSP-55 FPGA accelerator board from Scan Engineering Telecom is intended for high-performance SDR or data processing applications.

## Why build your own ASIC prototyping hardware?

DN2076K10 ASIC Prototyping Platform

## All the gates and features you need are – off the shelf.

Time to market, engineering expense, complex fabrication, and board troubleshooting all point to a 'buy' instead of 'build' decision. Proven FPGA boards from the Dini Group will provide you with a hardware solution that works — on time, and under budget. For eight generations of FPGAs we have created the biggest, fastest, and most versatile prototyping boards. You can see the benefits of this experience in our latest Virtex-6 Prototyping Platform.

We started with seven of the newest, most powerful FPGAs for 37 Million ASIC Gates on a single board. We hooked them up with FPGA to FPGA busses that run at 650 MHz (1.3 Gb/s in DDR mode) and made sure that 100% of the board resources are dedicated to your application. A Marvell MV78200 with Dual ARM CPUs provides any high speed interface you might want, and after FPGA configuration, these I GHz floating point processors are available for your use.

Stuffing options for this board are extensive. Useful configurations start below \$25,000. You can spend six months plus building a board to your exact specifications, or start now with the board you need to get your design running at speed. Best of all, you can troubleshoot your design, not the board. Buy your prototyping hardware, and we will save you time and money.

#### Engineers' Guide to FPGA and CPLD Solutions 2011 www.eecatalog.com/fpga

#### VP/Associate Publisher

Clair Bright - cbright@extensionmedia.com (415) 255-0390 ext. 15

#### Editorial

Editorial Director John Blyler jblyler@extensionmedia.com (503) 614-1082 Editor Cheryl Coupé ccoupe@extensionmedia.com

#### **Creative/Production**

**Graphic Designers** Keith Kelly Nicky Jacobson

Production Coordinator Spryte Heithecker - traffic@extensionmedia.com

Online Director Jeff Cheney

#### **Advertising/Reprint Sales**

VP/Associate Publisher Embedded Electronics Media Group Clair Bright - cbright@extensionmedia.com (415) 255-0390 ext. 15

Sales Director Karen Popp - kpopp@extensionmedia.com

Sales Manager Marcy Carnerie - mcarnerie@extensionmedia.com

Marketing/Circulation Jenna Johnson - jjohnson@extensionmedia.com

To Subscribe www.extensionmedia.com/free

Extension Media, LLC Corporate Office

President and Publisher Vince Ridley vridley@extensionmedia.com

Vice President, Sales Embedded Electronics Media Group Clair Bright cbright@extensionmedia.com

Vice President, Business Development Melissa Sterling msterling@extensionmedia.com

**Special Thanks to Our Sponsors**

Engineers' Guide to FPGA and CPLD Solutions 2011 is published by Extension Media LLC. Extension Media makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this Catalog nor obes it make a commitment to update the information contained herein. Engineers' Guide to FPGA and CPLD Solutions 2011 is Copyright® 2011Extension Media LLC. No information in this Catalog may be reproduced without expressed written permission from Extension Media 01786 108 Mission 2013 and an end of the spectre companies. Every attempt was made to include it nitis Catalog are held by their respective companies. Every attempt was made to include it nitis Catalog are held by their respective companies. Every attempt was made to include it nitis Catalog are held by their respective companies. Every attempt was made to include it nitis Catalog are held by their respective companies. Every attempt was made to include it mission and service and an adverse data and the indicated by their companies.

## Welcome to the 2011 Engineers' Guide to FPGA and CPLD Solutions

In this year's edition of the 2011 Engineers' Guide to FGPA and CPLD Solutions, you'll learn more about the best-in-class programmable platforms – silicon, software, IP, boards, kits, reference designs – Xilinx and our ecosystem partners are delivering to hardware and software designers.

Our flagship FPGA platforms fully exploit the benefits of Moore's Law to deliver increased performance, densities and system-level functionality, while driving down cost and power consumption. Whether you're seeking a solution for compute-intensive, high-speed, high-density SoC applications or applications where size, power, and cost are key considerations, we offer a simple, smart path for getting to market quickly with innovative new products in a fiercely competitive global market place.

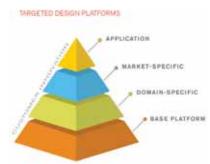

You can pick and choose from a variety of Targeted Design Platforms to jumpstart your development projects, taking advantage of open standards, common design methodologies, development tools, and run-time platforms, including: base (silicon, IP, logic tools, boards, reference designs), domain-specific (embedded processing, DSP or logic/connectivity IP & tools, FMC daughter cards), and market-specific (IP, custom tools & boards).

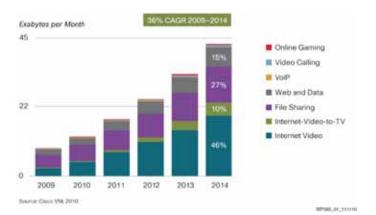

In 2011 and beyond, a key growth driver for the electronics industry – and FPGAs – is an insatiable bandwidth demand from all corners of the globe. In 2014, annual global IP traffic is projected to exceed 3/4 of a zettabyte (1,000,000,000,000,000,000,000 bytes).

This phenomenon extends far beyond the traditional communications sector into a broad set of end markets: automotive infotainment and driver safety, 3-D digital displays (handheld camcorders, TV, cinema projection), ultrasound imaging , high-definition video surveillance, robotic surgical instruments, even reconfigurable multi-processor computing in outer space, to name just a few.

In the coming year, look for Xilinx to roll out an expanded portfolio of 28nm programmable platforms

that will enable dramatic breakthroughs for designers. Our 7 series platforms (www.xilinx. com/7) will set a new bar for the industry in power efficiency, capacity, performance and high bandwidth, while extending our Targeted Design Platform strategy at 28nm. And, our new ARM-based Extensible Processing Platform solution will offer a combination of superior performance and high-processing horsepower and lower cost and power for emerging embedded systems applications in markets such as intelligent video, wireless communication, and automotive infotainment.

Today, FPGA designers are at the forefront of low-cost innovation, bringing to market inventive new products that enrich the quality of our everyday lives. We look forward to witnessing again the magnificent spirit of innovation you'll bring to the diverse markets you serve.

*Mosle Gavriele* President and CEO Xilinx

#### Contents

| Trends to Watch in the Evolution of Programmable Logic<br>By Cheryl Coupé                                                          | 4  |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| Cut your development time and cost with smart debugging and ZeBu<br>By EVE-USA Inc.                                                | 6  |

| Dual-Architecture FPGAs Provide New Opportunities for Embedded Developers<br>By Cheryl Coupé                                       | 8  |

| View from the EDA Side<br>By Cheryl Coupé                                                                                          | 11 |

| Intellectual Property and FPGA-based Designs<br>By Cheryl Coupé                                                                    |    |

| <b>FPGAs Pave Way for 5G, 400Gb/s Communications</b><br>By Gilles Garcia, director, Wired Communication Business Unit, Xilinx Inc. |    |

#### **Products and Services**

#### FPGAs & CPLDs

#### FPGA Chips

| Lattice Semiconductor  |    |

|------------------------|----|

| LatticeECP3 FPGAs      | 15 |

| Xilinx, Inc.           |    |

| Xilinx Spartan-6 FPGAs | 16 |

| Xilinx Virtex-6 FPGAs  | 17 |

|                        |    |

#### Boards & Kits

#### **Boards / Hardware**

#### **Innovative Integration**

| X5 Family PCI Express XMC Modules | 9 |

|-----------------------------------|---|

| X6-RX                             | 0 |

#### Xilinx, Inc.

| Spartan-6 FPGA Connectivity Kit                | 21 |

|------------------------------------------------|----|

| Spartan-6 FPGA DSP Kit                         | 22 |

| Spartan-6 FPGA Evaluation and Development Kits | 23 |

| Spartan-6 FPGA Market-specific Kits            | 24 |

| Virtex-6 FPGA DSP Kit                          | 25 |

| Virtex-6 FPGA Market-specific Kits             | 26 |

| Xilinx Embedded Kits                           | 27 |

| Xilinx Transceiver Characterization Kits       | 28 |

|                                                |    |

#### **Development Boards & Kits**

#### Xilinx, Inc.

| Virtex-6 FPGA Connectivity Kit | 29 |

|--------------------------------|----|

|--------------------------------|----|

#### FPGA Boards

#### **Alpha Data**

ADM-XRC-6T1 - Xilinx Reconfigurable Computer - XMC ..... 30

| CES - Creative Electronic Systems SA<br>VCP-8166                               | 31 |

|--------------------------------------------------------------------------------|----|

| <b>Lyrtech</b><br>Perseus 601X                                                 | 32 |

| Pentek, Inc.<br>Now Shipping The NEW Cobalt Series of Virtex-6 VPX<br>Modules! | 33 |

#### **Scan Engineering Telecom**

| SAMC-713 High performance Virtex-6 AMC with VITA 57.1 |    |

|-------------------------------------------------------|----|

| expansion site                                        | 34 |

| XDSP-55 Programmable FPGA Accelerator board           | 35 |

#### Xilinx, Inc.

| Virtex-6 FPGA ML605 Evaluation Kit |

|------------------------------------|

|------------------------------------|

#### **Development Tools**

#### **Design Tools**

| S | yno | psv | vs, | Inc |

|---|-----|-----|-----|-----|

|   |     |     |     |     |

| Synplify Premier - Fast, | Reliable | FPGA | Implementat | ion and |    |

|--------------------------|----------|------|-------------|---------|----|

| Debug                    |          |      | ·           | 3       | 37 |

#### **Development Tools**

| Xilinx, Inc.            |    |

|-------------------------|----|

| Xilinx ISE Design Suite | 12 |

#### DSP and Embedded Development Tools

| Lauterbach         |    |

|--------------------|----|

| TRACE32 PowerTools | 39 |

## SPARTAN.

- Easy-to-use, low power, serial transceivers support up to 3.125Gbps to enable industry standards such as PCIe<sup>®</sup>

- Low voltage option reduces total power consumption by 65% over previous generations

- Integrated DSP, memory controllers, and clocking technology simplifies designs

## VIRTEX

- High bandwidth serial connectivity with up to 72 low-power transceivers supporting up to 11.18Gbps

- Ultra high-performance DSP using up to 2016 low-power, performance-optimized DSP slices

- Integrated high-performance ExpressFabric<sup>™</sup> technology running at 600 MHz clocking and performance-tuned IP blocks

- Proven cost-reduction with EasyPath<sup>™</sup>-6 FPGAs

# **Potential. Realized.**

Unleash the full potential of your product design with Xilinx<sup>®</sup> Virtex<sup>®</sup>-6 and Spartan<sup>®</sup>-6 FPGA families — the programmable foundation for Targeted Design Platforms.

- Reduce system costs by up to 60%

- Lower power by 65%

- Shrink development time by 50%

#### Realize your potential. Visit www.xilinx.com/6.

© Copyright 2010 Xilinx, Inc. All rights reserved. Xilinx and the Xilinx logo are registered trademarks of Xilinx in the United States and other countries. All other trademarks are property of their respective holders.

EECatalog INDUSTRY TRENDS

# Trends to Watch in the Evolution of Programmable Logic

From one-of-a-kind fabrication agreements to dual-architecture system-on-chips, there are plenty of developments to keep track of *By Cheryl Coupé*

With a steady stream of news around strategic alliances, mergers, acquisitions, start-ups (and blow-outs), it can be tough to keep track of what's important in the evolution of programmable logic devices and tools. Here are a few FPGA trends and announcements EE Catalog is keeping an eye on, with the help of industry experts to put that news into perspective.

## ASICs yield some ground in the face of FPGA performance improvements

As the performance and power consumption of FPGAs improves and the design costs for complex ASICs rise, FPGAs

"it then makes sense for FPGA vendors to capitalize on the knowledge and expertise that already exists in the industry and to add these CPU cores to their parts. They are providing their customers with easily recognizable CPU cores that are already widely accepted and known to the industry, allowing for designs done with these parts to more closely match what designers are looking to put into their end silicon solutions." Wawrzyniak expects to see more of these dual-architecture devices as Intel and ARM make competitive thrusts into each other's traditional markets, and developers will be the beneficiaries of this intersection, with new, innovative tools and devices to meet

design challenges.

have become viable options for a wider range of new designs. Programmable logic offers low non-recurengineering ring (NRE) charges, offthe-shelf availability and the advantage of reprogrammability to accommodate design with little changes design impact to

While ASICs are yielding ground to programmable devices, designers should expect to see coexistence for some time into the future.

schedules and costs. But while ASICs are yielding ground to programmable devices, designers should expect to see coexistence for some time into the future.

According to Richard Wawrzyniak, senior analyst at Semico Research, FPGAs still have two remaining areas of concern – power consumption and price point – although both of these have become more manageable over time as FPGA manufacturers make improvements to their products. And as design costs for ASICs and systems-on-chips (SoCs) continue to rise, the need for an acceptable alternative also increases. Wawrzyniak believes that as power issues are addressed, FPGAs will find their way into more applications that were closed to them just a few years ago.

#### Dual-architecture devices change the competitive landscape

A trend that continues to bear watching is the combination of microprocessor and FPGA in a range of configurations as hard- or soft-core dual architectures. Common CPU cores and instruction sets, such as ARM and the Intel Atom, are familiar and widely used. According to Wawrzyniak,

Jeff Garrison, Syndirector opsys of FPGA marketing, implementation, "The agrees. com-FPGA bination of and microprocessor allows designers their to customize systems embedded for a target applica-

tion – increasingly important in vertical markets such as industrial, automotive, wireless, military and aerospace," he says. Standard processors offer an existing ecosystem of operating system and IP support that can be leveraged, and designers are typically familiar with available tools for software development for both the processor core as well as the programmable portion of the design. Garrison cautions designers to allocate time early in the design schedule, however, to decide what logic to implement in the software that runs on the processor and what to implement in the FPGA. "Clearly the timing-critical portions of the design should go in the faster FPGA while non-critical portions should go in the processor; however this partitioning is not always so black and white," he states.

While debug is an increasingly difficult and time-consuming task for FPGA designers, EDA vendors continue to enhance debug technology for embedded (and non-embedded) FPGA design, and have developed software that interfaces with FPGA vendor-provided tools to support processor-based design in their FPGAs. As Synopsis' Garrison says, "Distinguishing problems in the hardware versus the software can be difficult enough, and then further isolating to the true source can be very time-consuming. For this reason it is important to supplement simulation with debug tools that work with operating hardware."

#### Intel-Achronix fab announcement raises questions

Beyond current dual-architecture devices, the November

announcement that Intel will build FPGAs for startup Achronix Semiconductor Corp. additional raises questions. With both Xilinx and Actel (now Microsemi) developing products that combine their programmable technology logic with hard ARM processor cores, industry watchers wonder if the Intel-Achronix

It makes sense for FPGA vendors to capitalize on the knowledge and expertise that already exists in the industry and to add these CPU cores to their parts.

agreement is a precursor to Intel eventually combining programmable logic with its Atom cores on the same die.

Semico's Wawrzyniak cautions against reading too much into the announcement, which is still early in the implementation process, but offers three points of speculation:

- Intel is signaling that they are willing to make their cuttingedge manufacturing capability available to small companies on a limited basis to enable new technology to enter the market sooner than would otherwise be the case.

- Intel seems to be interested in matching their existing processor capability with programmable logic, with the requirement that the programmable logic can function at close to, or at the same level, as the performance of their processor technology.

- Since the entire manufacturing supply chain for these high-performance devices is now within the US, the Department of Defense may be very interested in these parts, which will more closely match the performance levels of mil/aero systems being deployed.

#### New technologies arise in FPGA chips and prototyping tools

Joe Gianelli, vice president of marketing and business development for InPA Systems, an integrated FPGA prototyping start-up, sees a range of opportunities for new FPGA chip and prototyping companies. For chip companies, he sees two main opportunities: vertical niches that are financially unattractive for big players, and leapfrog technology for larger end markets that the big players aren't likely to innovate. In the first case, he mentions Silicon Blue as "serving the high-volume/low-price programmable segment with better low-power technology and simplicity in design that enables it to price lower." For the latter case, he identifies Achronix as "serving the very high-speed programmable market segment with asynchronous clocking technology that creates a new segment."

Semico's Wawrzyniak taps Tabula as a company to watch,

believe saying, "I their 'Space-Time' technology brings a large increase in performance to designers who need it – especially in the communications area. I also believe that their technology could be deployed to solve system-level issues in other areas outside of strictly programmable logic issues."

Gianelli also sees opportunities for InPA as a supplier of leapfrog EDA technology in the area of rapid FPGA prototyping. "I see the greatest opportunity in serving the verification needs of the ever-growing complex SoC designs," he states. "I see this today with full custom SoCs but see a growing opportunity in the near future as programmable platforms will become almost as large and complex, and there will be far more of these design starts."

Wawrzyniak also comments on FPGA-market acquisitions from an IP standpoint. "The acquisition of Virage Logic by Synopsys and of Denali by Cadence earlier this year shows that the IP market is entering another phase of its evolution," he posits. "I believe a few of the larger IP vendors will now, either through acquisition or through already existing internal resources, offer IP subsystems as products to the market at large. This could have a very large impact on how SoC are designed and represents the first major change in SoC design methodology in many years." Wawrzyniak suspects that more acquisitions of IP companies might be made over time to facilitate the trend towards IP subsystem products.

Cheryl Berglund Coupé is Editor of EECatalog. com. Her articles have appeared in EE Times, Electronic Business, Microsoft Embedded Review and Windows Developer's Journal and she has developed presentations for the Embedded Systems Conference and ICSPAT. She has held

2

a variety of production, technical marketing and writing positions within technology companies and agencies in the Northwest.

# Cut your development time and cost with smart debugging and ZeBu

EVE complements their high-performance, low-cost hardware-assisted verification platforms with tools and methodology for effective debugging, including new CSA technology.

#### By EVE-USA Inc.

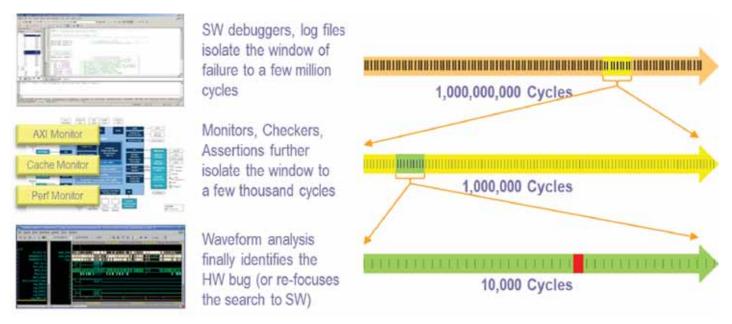

FPGA based hardware-assisted verification tools – like EVE's family of Xilinx based ZeBu systems – provide a high-performance, low-cost solution for fast System-On-Chip (SOC) emulation. However, providing multi-MHz performance and offering the most cycles per dollar aren't the only requirements for a world class emulator like ZeBu. Sure, ZeBu users can boot Linux on an embedded processor design in just minutes, or process a full HD video frame in under a second – but what happens when a failure occurs after a billion cycles of testing? Billion-cycle debugging requires not only advanced debugging technology, but also a smart methodology to leverage that technology effectively.

EVE is a pioneer in providing debugging technology and design access within FPGA based hardware-assisted verification platforms. ZeBu fast emulators provide complete Register Transfer Level (RTL) access to your emulated design – even to the combinational signals. In addition to supporting multiple probe types for design access and waveform generation, ZeBu systems are well-appointed with a wide array of debugging technology, including: SystemVerilog Assertion (SVA) support, built-in logic analysis and trace memory, ZEMI-3 transactors, save & restore capabilities, and an offline debugging framework. These tools enable an efficient debugging methodology to quickly reproduce, isolate and identify the source of billion-cycle failures.

Before you can even start looking for a billion-cycle bug, you must be able to quickly reproduce the failing test. And since debugging in emulation is typically a multipass affair, maintaining the highest performance possible throughout the bulk of the debug process is critical. ZeBu emulators are the fastest on the market and support designs of up to 1 billion ASIC gates, so reproducing an error after a billion cycles takes only minutes, even at the full-chip level. Additional ZeBu technology, such as save & restore and the offline debugging framework, provides users with further improvements in the reproduction of tests in co-simulation, co-emulation, and in-circuit emulation environments. Also critical for a smart debugging methodology is the generation and use of relevant information over raw data. Even for small designs, dumping a billion cycles worth of waveforms is often an unrealistic debugging solution. Wading through that much waveform data without any context could take forever - if your waveform viewer could even open up a file that big! For smart debugging, you need high-abstraction debugging technology that provides insight into the root cause of the failure without sacrificing performance. ZeBu users can leverage software debuggers, ZEMI-3 monitor transactors, logic analysis, SVAs, and pre-compiled Static and Flexible probe sets to isolate the sub-system and the appropriate time window or trigger point of the failure. These technologies execute at MHz speeds and above, enabling multiple rounds of convergent debugging without giving up vital performance.

Waveform generation and detailed debugging should only occur after a realistically usable time window and subsystem has been isolated. With ZeBu's Dynamic probes, integrated with EVE's new Combinational Signal Access (CSA) technology, users have run-time access to any sequential or non-sequential net in the design without requiring any re-compilation or the insertion of additional probe logic. RTL waveforms can be generated live during a run, or offline for improved performance and efficient resource utilization, and can be used to ultimately identify the source of the billion-cycle failure.

With ZeBu, you get more than just a high-performance, low-cost FPGA based emulation system. You also get the debugging technology you need, including CSA and offline waveform generation, to implement a smart debugging methodology to quickly reproduce, isolate and identify bugs. ZeBu cuts the development time and cost of your entire SOC project, enabling billion-cycle hardware verification, software validation and hardware/software co-verification. To learn more about ZeBu emulators and smart debugging, please contact the professionals at info@ eve-team.com or visit http://www.eve-team.com.

Figure 1: Reproduce, isolate and identify the source of a billion-cycle failure with ZeBu

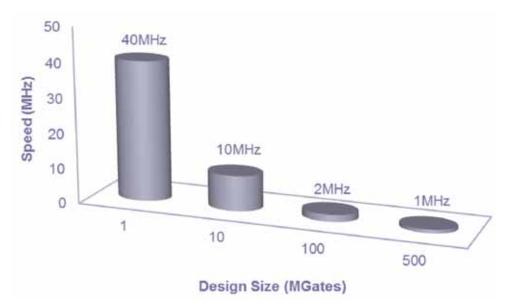

Figure 2: ZeBu Performance by Design Size

**EECatalog** SPECIAL FEATURE

## Dual-Architecture FPGAs Provide New Opportunities for Embedded Developers

While FPGAs still require trade-offs in price and performance, advances in architectures and development tools can address a wide range of design goals

By Cheryl Coupé

With the integration of hard or soft-core microprocessors, today's FPGAs give embedded developers new levels of performance and flexibility. But as always, there are trade-offs to consider in the ASIC-FPGA decision. EECatalog spoke to Glenn Steiner, senior processor technical manager at Xilinx, Mike Kendrick, manager of software product planning at Lattice Semiconductor and Matt Ferraro, engineer at Connect Tech about what those trade-offs are, and how developers can best take advantage of new FPGA devices and tools.

**EE Catalog:** How are FPGA vendors helping embedded developers address design goals such as reduced bill-of-material (BOM) costs, reduced power consumption or shortened design cycles?

**Glenn Steiner, Xilinx:** Embedded processing using FPGAs for customization and improving system performance has become an integral part of a growing number of applications across a wide range of end markets, including aerospace and defense, wired and wireless

communications, automotive, audio/video broadcast, industrial control, test and measurement and consumer. Driving this trend is the need to reduce cost, weight, area and power by means of large-scale integration through SoC design, while at the same time enabling design reuse and mitigating design risk as well as obsolescence. As a SoC platform, FPGAs provide embedded designers with deep levels of integration and high levels of parallel processing performance. But they also offer design flexibility so that designers can respond to changing standards, evolving customer needs and any other change in design requirements and still meet their time-to-market window.

Embedded designers have traditionally purchased generalpurpose processors, or ASSP-based processors, in an attempt to match processing and peripheral capabilities against system requirements. While FPGAs can be used to bridge missing IP and system performance gaps in their traditional role, today's FPGAs with integrated hard or soft processors enable designers to implement complete systems-on-a-chip to reduce BOM costs. In addition, placing data processing either with the processor or the FPGA logic results in lower system costs as well as lower power consumption compared to other implementations. For example, a Pentium-style processor can perform data processing on an HD video stream at the cost of over \$100 and tens of watts, while an FPGA costing one tenth the price can perform the same function at one tenth the power.

In an effort to substantially simplify and accelerate the means by which both embedded software and hardware designers gain access to these benefits, FPGA vendors like Xilinx are developing fully-functional, tested and supported targeted reference designs for its FPGAs in addition to tools and development platforms to enable a productive design environment.

*Mike Kendrick, Lattice Semiconductor:* Soft processors embedded within the FPGA allow high-functional density for many different functions that do not require high-speed parallelism. This is the standard value proposition of a processor – it takes up minimal silicon area

to execute sequential software that is highly malleable, but low performance. Now this capability is available integrated into an FPGA.

As the cost per FPGA look-up table (LUT) falls quickly, processor LUT count remains constant, so the economics of integrating a processor within an FPGA continue to improve compared to a two-chip solution. Also, the reduced chip count, compared to a two-chip solution, reduces manufacturing costs and mean time between failure among other benefits, resulting in a less expensive, more reliable product.

Using an embedded processor can lead to lower power, particularly if the processor does not increase the size of the FPGA needed in the first place for the particular design. Finally, soft processors are insurance against obsolescence versus the discrete processor catalog.

**Matt Ferraro, Connect Tech:** By embedding a microprocessor within an FPGA you can simplify the overall design. In many complex applications, the FPGA and processor require separate memory, flash, debug ports and pro-

#### **EECatalog** SPECIAL FEATURE

gramming chains – which now can be shared. As well, the processor's requirement for additional voltage rails, power sequencing and power on reset circuits is all but eliminated, with current FPGAs having very lenient startup conditions. Not only is BOM cost reduced, but the complexity of the PCB design and layout is significantly reduced. Now designers only need learn the intricacies of one complex device instead of two, significantly reducing the time to market.

**EE Catalog:** What's happening with dual-architecture FPGA/microprocessor packages? Where is this trend heading and what are the application needs that are driving this evolution?

**Steiner:** Processor-centricsolutions-including microprocessors, ASICs, ASSPs, and application processors – are a dominant force in today's

As the cost per FPGA look-up table (LUT) falls quickly, processor LUT count remains constant, so the economics of integrating a processor within an FPGA continue to improve compared to a two-chip solution.

semiconductor market. Many of these products are designed as SoC solutions, including a core processor engine that is complemented by common- and application-specific IP. Yet, with the continuing progression of Moore's Law, new product investments continue to escalate, resulting in fewer new product starts with products optimized for only the highest volume markets. This trend towards a commodity model limits customers' ability to optimize and differentiate, which makes achieving a competitive advantage an increasingly difficult goal. FPGAs with embedded processors enable the reversing of this trend.

The coupling of processor and FPGA continues to evolve. Compact, soft processors such as the Xilinx PicoBlaze processor were developed for small, early-generation FPGAs, and were ideal for state machine or simple functions such for GPIO, keyboard and display control. Next, complex soft processors like the MicroBlaze processor are capable of running operating systems such as Linux and are used in applications ranging from motor control to portable medical devices. Hardened processor cores, such as the PowerPC processor, have now been in multiple generations of FPGAs where higher performance processors have been required for applications such as radar imaging.

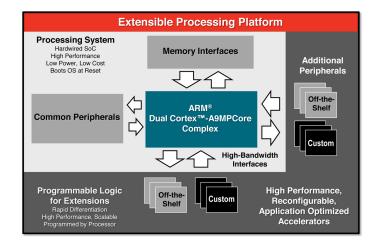

Next-generation architectures will focus on processor centricity with complete hardening of the processor, peripherals, memory interfaces and IO paths. This approach provides software developers a familiar programming environment within an optimized, full featured, powerful, yet low-cost, low-power processing platform. Meanwhile, system architects and logic designers can fully leverage the programmable logic to extend, customize, optimize and differentiate their solutions.

**Kendrick:** The question is whether an FPGA with an embedded hard processor can find a viable application space, compared to the use of a discrete processor plus an FPGA, or the use of an embedded soft processor.

Compared to a two-chip solution (discrete processor and FPGA), the FPGA with an embedded hard processor limits the choice of processor to use and, in most applications, delivers much less performance. This is because new generations of discrete processors are released frequently and their performance quickly surpasses the FPGA's on-chip processor. On the other hand, using

an on-chip processor can be the less expensive approach, but only if performance requirements for speed and capability are modest.

Compared to a SoC ASIC, the on-FPGA chip processor approach results in a higher unit cost and provides less flexibility (e.g., the bus structure). However, the on-FPGA chip solution presents less risk, since it is possible to go to production with a prototype.

Ferraro: In the early days of FPGA embedded processing, 'soft core' processors were implemented using FPGA resources (LUT and flip fops). Most of these processors were developed by the FPGA companies, having proprietary architectures and instruction sets, like the Xilinx MicroBlaze or Altera NIOS. Third-party processor IP existed to implement more common architectures, but the cost was prohibitive to all but the largest companies with high-volume applications. These soft processors were significantly slower than external processors, and not capable of handling anything more than a complex statemachine. Then FPGA vendors started to incorporate hard processor IP directly onto the FPGA die, licensing architectures like the PowerPC (in Xilinx's Virtex family). For many applications, the cost of a high-end FPGA is too high, while the capability of a PowerPC is overkill. So more recently the focus has been incorporating more popular embedded architectures, like ARM Cortex and eventually Intel's Atom.

**EE Catalog:** What do engineers need to know about development tools for these dual architectures? What will the learning curve be? How will that impact adoption?

### EECatalog SPECIAL FEATURE

Steiner: Programmable logic devices are well-supported by sophisticated tools suites. These tools provide logic designers an environment rich in features to optimize their IP solutions and render them onto FPGA. In this environment, the programming languages are hardware-oriented such as Verilog and VHDL.

However, software developers work almost exclusively in high-level languages, such as C/C++, which are also well supported by today's processor-based solutions. For the Extensible Processing Platform, Xilinx will support familiar software development and debug environments, using tools such as ARM Real View and related third-party tools, Eclipse-based IDEs, GNU, Xilinx Software Development Kit and others. The programmable logic portion can be developed and debugged using the standard ISE Design Suite, and other third party HDL and algorithmic design tools.

Because the Extensible Processing Platform takes a processorcentric approach (it boots the Processing System at reset and then manages the programmable logic configuration), a more software-centric development flow is enabled. This flow enables the system architect, logic designer and software developer to work in parallel, using their familiar programming environments, then merge the final releases into the software baseline. As a result, key partitioning decisions on system functions/performance can be made early and throughout the development process.

This is critical for embedded systems where application complexity is driving tremendous levels of system performance against tightly-managed cost, schedule and power budgets. It is important to note that the AMBA-AXI interfaces are key in enabling the software-centric flow because they present a seamless, common and well-defined environment for the hardware extensions. While the logic designer will need to deeply understand this technology, for the software developer the AMBA interfaces abstract the extended logic as memory mapped calls. This allows for a straightforward interplay of hardware and software programming in a parallel state of development.

**Kendrick:** The biggest issue for new SoC designers using this dual-architecture technology will be getting visibility of what is going on internally when the processor and complex logic are all integrated onto one chip.

Current SoC ASIC designers will see an improvement in debug because they will have more ability to do board-level testing and validation rather than relying so heavily on modeling and verification.

Embedded designers will have a challenge with the hardware shifting under them. They will be used to a much more static hardware platform (e.g., a catalog discrete processor), so this will have to be managed with the new flexibility afforded by processors integrated with programmable logic

Xilinx's architecture for a new Extensible Processing Platform is optimized for system power, cost and size. Based on ARM's dual-core Cortex-A9 MPCore processor and Xilinx's 28 nm programmable logic fabric, the Extensible Processing Platform takes a processor-cen-

Ferraro: Many of the FPGA vendors have well-supported tool chains, advertising the drag-and-drop approach of building up peripherals for an embedded processor system within an FPGA. However, the new developer should be forewarned that this supposedly seamless approach works well with development boards, but not so much with custom hardware which will require tweaking peripheral parameters and likely timing constraints. Creating custom peripherals for hardware co-processing can require a more advanced knowledge of VHDL or Verilog. In addition, many popular embedded operating systems will offer board support packages (BSPs) for FPGA/microprocessor architecture, but again these BSPs target development boards. The designers must be prepared to develop their BSP, specifically boot loaders and other startup routines. While the learning curve is steep, attending a training seminar and experimenting with development boards cuts the time dramatically.

Cheryl Berglund Coupé is Editor of EECatalog.com. Her articles have appeared in EE Times, Electronic Business, Microsoft Embedded Review and Windows Developer's Journal and she has developed presentations for the Embedded Systems Conference and ICSPAT. She has held a variety of production,

technical marketing and writing positions within technology companies and agencies in the Northwest. **EECatalog** Special Feature

## View from the EDA Side

EDA vendors speak out on strategies to meet embedded design goals with FPGAs

By Cheryl Coupé

While shiny new chip designs draw attention, electronic design automation (EDA) firms work diligently behind the scenes to create tools and systems that help embedded developers address design goals such as reduced bill-of-materials (BOM) costs, reduced power consumption and shortened design cycles. EE Catalog asked several EDA vendors how they are helping embedded developers meet these goals.

Juergen Jaeger, senior product manager at Cadence,

responds, "At first, the answer seems very obvious: just put the hardware part (the chip), including the embeddedprocessor(s) into one or more FPGAs, thus providing a pre-silicon platform that allows the developer to experiment and make decisions about what should be realized in the hardware and software. These findings can be used to guide the partitioning between

While today's economic climate doesn't necessarily support riskier approaches, I see this changing as companies realize that without some risk-taking, they'll never move out of their incremental box.

hardware and software and to achieve the BOM and power consumption goals." But, he continues, "as it often the case, the devil lies in the details."

For this approach to deliver the expected results, the developer must be able to easily map the hardware portion of the design into the FPGA and quickly implement hardware design iterations to experiment with multiple hardware/ software partitioning scenarios. The developer must also be able to preserve the integrity and functionality of the original RTL; that is, there are no FPGA-specific changes required.

In order to accomplish this, embedded developers need to look beyond the FPGA to the overall design and verification flow. Jaeger states, "The key requirement for this flow is not to optimize it for maximum FPGA performance, but rather for implementation and iteration speed, as well as for ease-of-use." Taking a somewhat different approach is InPA Systems, a start-up integrating custom or fixed FPGA prototypes with existing EDA verification environments (from Cadence, Mentor Graphics, and Synopsys) to achieve fast time-to-pre-silicon-prototypes. Joe Gianelli, InPA's VP of marketing and business development, sees risks and opportunities for developers moving to new technologies. These decisions can affect high-level design goals such as leapfrogging competitors.

> Gianelli says, "In most cases, moving to a new device from an FPGA prototyping vendor (e.g., Altera or Xilinx), or moving to a new tool from a fullline EDA vendor (e.g., Cadence or Synopsys) is low risk, and the opportunity is fairly incremental." While this path involves least the amount of change and risk, developers taking the well-paved road in favor of a riskier path

that may not work may also miss opportunities to leapfrog past their competitors." While today's economic climate doesn't necessarily support riskier approaches," Gianelli continues, "I see this changing as companies realize that without some risk-taking, they'll never move out of their incremental box."

Let's take a closer look at a few common design goals and see what EDA vendors have to say.

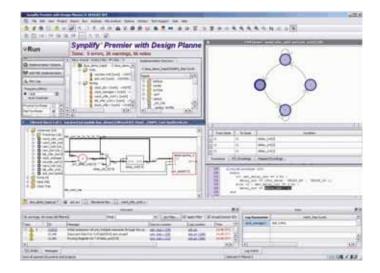

#### **Cost reduction**

Jeff Garrison, director of marketing for FPGA implementation at Synopsys, states that using a synthesis tool that is timing-driven is key to cost-reduction efforts as the performance requirement can be specified and then, once met, the tool will focus on area optimization. "By minimizing logic cell use while meeting required timing performance, a design's power consumption and size can often fit into a smaller, less expensive FPGA and possibly a cheaper package," he says. "Using a one-size smaller FPGA can save 20% or more, which is significant, especially when volume is in the hundreds or thousands of parts."

Daniel Platzker, product marketing director at Mentor Graphics, takes a similar approach. Because the FPGA may be the most expensive component on the board, BOM costs can be significantly reduced by targeting the least expensive device that still meets requirements. This is where EDA vendors – which are typically device agnostic – can help. Their tool flows allow designers to flexibly target the most competitively priced device for each project from any FPGA supplier. "Third-party tool vendors develop and continue to improve technologies such as physical synthesis so development teams can maximize design performance for the cheapest possible device—from multiple FPGA vendors," Platzker says.

#### **Power consumption**

Mentor's Platzker notes that reducing power consumption is becoming a higher priority as more FPGAs are adopted in portable devices. While static power is largely driven by the silicon architecture, and hence up to the FPGA vendors to address, EDA vendors offer system-level design methodologies and implementation flows that can help designers reduce power in other ways.

"At the system level, transaction-level modeling methodologies are now available for writing ESL models with associated power estimates, allowing designers to evaluate and optimize the interaction and power consumption of various IP components at an early stage of the design cycle," says Platzker. "Once the design is stabilized in RTL form, RTL synthesis can reduce dynamic power of clock networks, design logic, memories and I/O banks through algorithms transparent to the user. For example, optimal clock buffers can be put in place to shut off logic networks not in use, and memories can be split in ways so each memory access activates fewer embedded RAM components."

Synopsys' Garrison also addresses smaller designs, which tend to consume less power. He notes that Synopsys FPGA synthesis can optionally power down bits in BlockRAMs and DSP blocks when they are not being used, in order to reduce dynamic power consumption. In addition, "partial reconfiguration allows for a section of the design to be reconfigured on the fly, which can result in power reduction by making it possible to power down parts of the design," he comments.

#### **Productivity/shortened design cycle**

One concern for productivity is design tool turnaround time for today's very large FPGAs. Luckily, EDA and FPGA vendors are working together to address this by supporting incremental design flows and improving tool runtime. As an example, Garrison explains that Synopsys and Xilinx have been working together to support the Xilinx Design Preservation flow, which allows portions of the design that have met timing to be 'preserved' so that further changes at the top level don't introduce new problems. EDA vendors are also helping with support for partial reconfiguration in FPGAs, which allows for a section of the design to be reconfigured on the fly, enabling logic changes to be made in the deployed system.

Mentor's Platzker states, "EDA vendors are working to reduce the FPGA design cycle at every point of the flow, from design creation, through verification, implementation and finally board integration. Design houses are best served by standardizing on a well-integrated solution that includes ESL design, advanced verification methodologies such as test-bench coverage and assertions, vendor independent synthesis and I/O assignment solutions that simplifies the board integration process. A comprehensive ESL-to-FPGA gate flow not only ensures consistent results but also provides a single point of support for quick problem resolution. It's a combination that ultimately shortens the design cycle."

Cheryl Berglund Coupé is Editor of EECatalog. com. Her articles have appeared in EE Times, Electronic Business, Microsoft Embedded Review and Windows Developer's Journal and she has developed presentations for the Embedded Systems Conference and ICSPAT. She has held

a variety of production, technical marketing and writing positions within technology companies and agencies in the Northwest.

# Intellectual Property and FPGA-based Designs

#### Insight from the Trenches

By Cheryl Coupé

Intellectual property (IP) subsystems allow developers to add functionality quickly and effectively. But as these subsystems proliferate, a range of design and test issues arise. EE Catalog asked several industry pundits what issues developers need to be aware of relating to IP subsystems, especially for specific vertical-market applications such as medical, automotive and others. Insight comes from Richard Wawrzyniak, senior analyst at Semico Research; Glenn Steiner, Xilinx senior processor technical manager; Jeff Garrison, Synopsys director of marketing, FPGA implementation; Mike Kendrick, manager of software product planning at Lattice Semiconductor Corporation; and Joe Gianelli, VP marketing and business development, InPA Systems.

## Look for horizontal, rather than vertical, markets for IP subsystems

Richard Wawrzyniak, senior analyst, Semico Research

SoC designers are looking to acquire IP that addresses system-level problems instead of merely licensing many discrete IP blocks from many separate vendors and then taking that IP to build up to the system-level solutions they really need. SoC designers are

looking to move up a layer of abstraction to reduce the amount of effort they are expending to design this type of functionality into their systems.

Because designers are looking to acquire system-level functionality instead of a collection of discrete IP blocks, I believe the market for this type of solution will not be vertical in nature, but horizontal. Designers are looking for a communications subsystem, or a video subsystem, etc. that will be aimed at a particular market segment like medical, automotive, etc. I do not believe IP subsystem vendors will be able to address all the possible market niches for subsystem solutions with specific products. Instead, IP subsystem vendors will create subsystems that provide a certain amount of functionality at the system level that SoC designers will then shape into the correct configuration through applications software. In addition, since these subsystem products are configured around their own internal interconnects, it will be possible for the SoC designers to swap out individual IP blocks within the subsystem for other IP blocks that more fully meet the needs of the application as required. This will provide the designer with the correct level of granularity, but at a fraction of the effort and cost he had been expending previously.

FPGAs have been the vehicle of choice for several years for SoC designers who were looking to test or prove out a specific type of IP or even many types of IP before actually needing to design the SoC and taking a test chip through a shuttle program at a silicon foundry. The advent of the IP subsystem will not change this relationship between SoC designers and FPGA vendors. If anything, the relation will become tighter and more important as SoC designer look to try out many different types of IP subsystems to find the right one for their design.

Incidentally, the Intel-Achronix, Intel-Altera and ARM-Xilinx announcements lend support to the development of the IP subsystem trend – although I don't believe it was at all intentional – merely co-incidental. IP solutions that function at the system level require FPGAs that both have the right level of performance (so that applications software can be executed at close to system speeds) and that have the right types of CPU cores (CPU cores that match what SoC designers will use) that closely mirror what will be used in the final silicon solutions.

Having FPGAs that can execute at system speeds and that have the right types of CPU cores will give a boost to Soc designers in evaluating the IP subsystem products about to enter the market.

## Embedded kits support parallel hardware and software development

Glenn Steiner, Xilinx senior processor technical manager

Embedded software developers have very different environmental needs than their hardware engineering counterparts. Specifically, the software developer wants a compiler, a debugger, an Eclipse-based integrated design environment, an industry-

standard operating system (e.g., Linux,  $\mu C/OS$ ), a robust set of software libraries and a stable processor system with well-defined peripherals. Embedded hardware designers, however, are more concerned about system architecture, IP verification and timing closure. They require pre-verified hardware reference designs as starting points to evaluate the underlying FPGA platform. From there, they might add standard IP, integrate some custom IP and also remove IP blocks that they do not need. Ideally, they need a highlevel environment to make these design changes quickly, without having to modify RTL code (VHDL or Verilog) for each change.

For example, Xilinx has developed an embedded processing targeted reference design in the form of a fully functional and widely applicable MicroBlaze Processor Sub-System (PSS), accompanied by all of the requisite software design environment components that specifically and uniquely fulfill these requirements. Serving as the base for a new generation of embedded processing platforms, the Micro-Blaze PSS integrates essential processing, memory and I/O functions and is supported by a strong software ecosystem, offering middleware stacks and industry-leading operating systems such as Linux and  $\mu$ C/OS-II.

When used with the new Spartan-6 and Virtex-6 FPGA Embedded Kits, the MicroBlaze PSS allows software application developers to begin writing and porting their application code to the embedded platform before any hardware development has begun. Moreover, application software developers can immediately evaluate the performance of the processor, internal and external memory, bus architectures and I/Os against their system requirements. The developers can even begin optimizing their application software to the MicroBlaze PSS in parallel with the hardware design effort. Similarly, the new embedded kits provide everything the hardware design team needs to quickly evaluate the Xilinx embedded platform capabilities, as well as modify and extend these to their specific application needs.

Recognizing the needs of specific vertical markets, kits are now available targeting applications such as industrial Ethernet, industrial video processing, broadcast connectivity and high-performance digital signal processing. Thus, the kits create the opportunity for both the hardware and software design teams to move quickly and simultaneously through their respective evaluation and development processes. This methodology will of course support the Extensible Processing Platform.

#### Efforts under way to enable multi-vendor IP use while protecting it from unlawful practices

Jeff Garrison, Synopsys director of marketing, FPGA implementation

Using IP in today's FPGA designs is the norm for almost all vertical market applications. Of course the type of IP required for the different vertical markets vary, but the basic need for integrating IP into an FPGA design flow is widespread. The IP can come from in-house development on a previous design, the FPGA vendor themselves or from a third-party IP provider. In most cases the cost to develop standard functions like USB, SATA, PCIe, Ethernet, memory controllers, etc. is more than buying from a third party.

Developing IP in house and then remaining competitive by continuing to quickly adapt to standards changes and enhancements is much more than acquiring third-party IP. Third-party IP is typically delivered with constraints applicable to its interfaces, and with test harnesses applicable to specific nodes within the IP. For this reason, it is vital that synthesis tools provide controls that allow users to preserve IP boundaries for constraints application and preserve specific test nodes within the IP that will be probed during test.

One of the key challenges the industry faces is enabling IP use across a range of design tools from multiple vendors while still protecting the IP from reverse engineering and other unlawful practices. Tools such as simulators need to be able to decrypt protected IP to accurately simulate the IP's behavior within the design, while transformative tools such as synthesis need to both decrypt and encrypt the results in order to produce the fastest, smallest, lowest power design implementation. For this reason there needs to be a standard way for all EDA / FPGA vendors and IP providers to enable and protect IP used throughout the tool chain.

Synopsys, Xilinx and others are working toward the ratification of IEEE-P1735 which seeks to establish a standard for encryption and rights management for electronic design IP. Synthesis tools for example, must be able to read the IP in order to optimize logic surrounding the IP in the context of the overall design while producing an encrypted result that can be used by further downstream tools like place and route. Likewise, it would be extremely beneficial for debugging tools to be able to report on key signals within the IP for debug purposes. With rights management implemented, an IP provider could identify key signals within their IP that debug tools could access for this purpose.

Cheryl Berglund Coupé is Editor of EECatalog. com. Her articles have appeared in EE Times, Electronic Business, Microsoft Embedded Review and Windows Developer's Journal and she has developed presentations for the Embedded Systems Conference and ICSPAT. She has held

a variety of production, technical marketing and writing positions within technology companies and agencies in the Northwest.

### **Lattice Semiconductor**

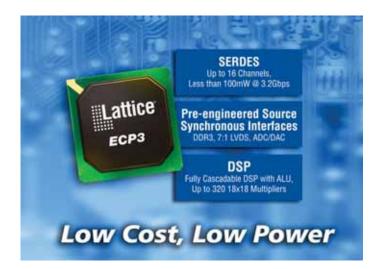

#### LatticeECP3 FPGAs

Proven 3rd Generation FPGA Platform

LatticeECP3<sup>™</sup> is the best-in-class mid-range FPGA with high-performance SerDes, full-featured DSP blocks, and support for state-of-the-art memory interfaces including DDR3. It offers 35% to 100% more silicon resources in smaller packages compared to competitors. The lowpower LatticeECP3 FPGAs are used in a wide-range of applications, such as wireless and wireline communication, video processing, security and surveillance, industrial networking, industrial automation, computing, storage, medical equipment, and consumer.

LatticeECP3 offers up to 150K LUTs of logic capacity and 7 Mbits of memory for system integration, cascadable high-performance DSP blocks for signal processing, high-speed memory interfaces including DDR3 at 800 Mbps, and up to 1 Gbps LVDS performance for ADC/DAC and SPI4.2 interfaces. LatticeECP3 further enables you to build high-speed systems with proven 3.2 Gbps lowpower SerDes qualified for a number of protocols – PCI Express 1.1, Ethernet (GbE, SGMII & XAUI), SDI (3G/HD/ SD), Serial RapidIO, CPRI, and JESD204A. LatticeECP3 devices also provide enhanced FPGA configuration options, such as, encryption, dual-boot capability, and superfast configuration via parallel flash.

To accelerate design of LatticeECP3 powered systems, Lattice also offers a number of generic and applicationspecific development kits, an expanding portfolio of free readymade reference designs, and a set of economical IP suites (PCI Express, Gigabit Ethernet Connectivity, DSP Signal Processing, and Video & Display). The reference designs, source code, and documentation can be downloaded for free from the Lattice website. To learn more about LatticeECP3 FPGA family and IP solutions, please visit: www.latticesemi.com/ecp3.

#### **FEATURES & BENEFITS**

- Low-power, high-value FPGA fabric. Logic densities from 17K to 150K LUTs, up to 7 Mbits of embedded block RAM, up to 300 Kbits of distributed RAM.

- Low power, high quality 3.2 Gbps SerDes (up to 16) with built-in pre-emphasis and equalization. Qualified for PCI Express, Ethernet (GbE, SGMII, & XAUI), SDI (3G/HD/SD), Serial RapidIO, CPRI, and JESD204A.

- High performance, cascadable DSP blocks with 2 multipliers, multiplexers, and ALU. Up to 160 DSP blocks can be cascaded together for high performance filter design and wide arithmetic functions.

- High-speed memory interfaces including DDR3 at 800 Mbps, and up to 1 Gbps LVDS performance for ADC/DAC and SPI4.2 interfaces.

- Advanced Configuration Options. Configure the LatticeECP3 with SPI boot flash or parallel burstmode flash. Protect designs with 128-bit AES. Dual-boot capability provides backup configuration copy. TransFR™ I/O facilitates live updates while system is in operation.

#### **APPLICATION AREAS**

Wireless and Wireline Communication, Large and Small LCD Display Interfaces, Video Game Consoles, Video and Image Processing, Security & Surveillance, Industrial Networking, Industrial Automation, Computing, Storage Controllers, Gaming Equipment, Medical Equipment, Consumer, etc.

**CONTACT INFORMATION**

Lattice Semiconductor 5555 NE Moore Ct. Hillsboro, OR 97124 USA www.latticesemi.com

### Xilinx, Inc.

#### Xilinx Spartan-6 FPGAs

The Xilinx® Spartan®-6 FPGA family offers an optimal balance of cost, power, and performance for consumer, automotive, surveillance, wireless, and other cost and power-sensitive applications.

Built for connectivity and low power, Spartan-6 FPGAs provide the programmable foundation for Xilinx Targeted Design Platforms that accelerate innovation and improve differentiation of lower power 'greener' electronics products. Spartan-6 FPGAs benefit from Xilinx's holistic approach to lowering power through hardware, software, power estimation tools, and demonstration boards with power measurement capabilities.

System developers can meet the demand for new features with twice the capability at half the power consumption. Spartan-6 FPGAs are fabricated using mature, low power 45-nanometer process technology. A rich selection of built-in blocks – including second generation DSP slices, low power (150-180mW per) high-speed serial transceivers, and PCI Express® interface cores – enable greater system-level integration and power savings.

Spartan-6 FPGAs bring 65 percent lower power than previous Spartan families with innovations in system-level power management to reduce static and dynamic power, advanced power control modes, and a lower power 1.0V core option. In addition, fast, flexible I/Os deliver over 12Gbps memory access bandwidth with 3.3 volt compatibility and RoHS-compliant Pb-free packaging.

#### FEATURES & BENEFITS

- Advanced power control features such as hibernate and suspend modes for ultra low-power applications

- Low power operation mode when not in use is ideal for battery powered applications

- Only low cost and low power FPGA to have integrated high-speed serial transceivers

- Integrated hard memory controller enables DDR3 memory support in low-cost FPGA

- Low power device option lowers operating voltage to 1.0V to reduce power by an additional 30 percent

#### **TECHNICAL SPECS**

- Spartan-6 LX FPGAs The industry's lowest risk and lowest cost solution for high-performance logic

- Spartan-6 LXT FPGAs The industry's lowest risk and lowest cost solution for serial connectivity

- Spartan-6 LX FPGAs for absolute lowest cost with up to 150K logic density, 4.8Mb memory, integrated memory controllers, and up to 180 DSP blocks at 250 MHz

- Spartan-6 LXT FPGAs for lowest risk, lowest cost serial connectivity with up to eight low power 3.125Gbps GTP transceivers, integrated PCI Express core, and up to 180 DSP slices at 250 MHz

- Start designing today with the Spartan-6 FPGA Evaluation Kit that provides all elements needed to design right out of the box

#### **AVAILABILITY**

Available now! Visit: http://www.xilinx.com/spartan6

#### **APPLICATION AREAS**

Automotive, Broadcast Video, Consumer Electronics, Wired/Wireless Communications, Aerospace & Defense, and Industrial, Scientific and Medical Instrumentation

#### **CONTACT INFORMATION**

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 USA 408-559-7778 Telephone more\_info@xilinx.com www.xilinx.com/spartan6

### Xilinx, Inc.

#### Xilinx Virtex-6 FPGAs

The Xilinx® Virtex®-6 FPGA family is optimized for the higher bandwidth and lower power demands of wireless/ wired communications, broadcast, and aerospace/defense electronics.

Virtex-6 FPGAs provide the high performance programmable foundation for Xilinx Targeted Design Platforms that accelerate innovation and improve product differentiation of compute-intensive applications. At up to 50 percent lower power and 20 percent lower cost than previous generations, Virtex-6 FPGAs benefit from Xilinx's holistic approach to lowering power through hardware, software, power estimation tools, and demonstration boards with power measurement capabilities.

Virtex-6 FPGAs use the combination of high performance 40-nanometer process technology, innovative circuit design techniques, and architectural enhancements to deliver more computational performance and faster networking, while significantly reducing both static and dynamic power consumption.

DSP bandwidth exceeds 1,000GMACS with over 2000 DSP slices and optimized ratios of logic, Block RAM, and distributed RAM. This computational bandwidth is augmented with over 500Gbps of total serial bandwidth that is also optimized to reduce overall system power consumption for system architects designing the 'green' central offices and data centers of the future. With Virtex-6 FPGAs, even further power savings can be realized with enhanced support for partial reconfiguration and low-voltage device options.

#### FEATURES & BENEFITS

- Low power and high performance with greatly simplified power system design

- Optimized feature mix delivers two-fold increase of Flipflops and BRAM with six times more DSP than similar-sized devices

- Integrated system blocks save up to 10X static power compared to soft implementations

- Devices operate on 1.0V core voltage with a 0.9V low-power option that reduces power by an additional 20 percent

- New I/O power reduction features allow low power modes for memory interfaces

#### **TECHNICAL SPECS**

Virtex-6 LXT FPGAs for high-performance logic, DSP and serial connectivity with up to 36 low-power 6.6Gbps GTX transceivers and 864 DSP slices at 600 MHz

- Virtex-6 SXT FPGAs for ultra high-performance DSP and serial connectivity with up to 36 low-power 6.6Gbps GTX transceivers and 2,016 DSP slices at 600 MHz

- Virtex-6 HXT FPGAs for the industry's highest bandwidth with line rates in excess of 11Gbps and over 1Tbps serial connectivity with 720 SelectIO<sup>™</sup> pins and up to 72 multi-rate transceivers

- Virtex-6 CXT FGPAs For applications requiring 3.75Gbps serial connectivity and corresponding logic performance

- EasyPath<sup>™</sup>-6 Lowest total product cost for high-performance FGPAs

- Start designing today with the Virtex-6 FPGA Evaluation Kit that provides all elements needed to design right out of the box

#### **AVAILABILITY**

Available now! Visit: http://ww w.xilinx.com/virtex6

#### **APPLICATION AREAS**

Automotive, Broadcast Video, Consumer Electronics, Wired/Wireless Communications, Aerospace & Defense, and Industrial, Scientific and Medical Instrumentation

#### **CONTACT INFORMATION**

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 USA 408-559-7778 Telephone more\_info@xilinx.com www.xilinx.com/virtex6

Market-revealing keynote speakers

Technically focused embedded

seminars and workshops

Vendors demonstrating

newest technologies

Network with the

brightest engineers

UPCOMING LOCATIONS

> Santa Clara 1/27/11

> > Huntsville, AL 2/15/11

## Melbourne, FL 2/17/11

Can you afford to miss it? FREE admission, lunch, parking and prize drawing entries at each event. RTECC is your best opportunity to discover a new world of possibilities within the embedded market.

> Register for a FREE Guest Pass Today!

## RTECC TRANSPORTING ENGINEERS INTO THE WORLD OF EMBEDDED

ARE YOU BEING LEFT BEHIND?

ANNOUNCING Distinguished Speaker @ RTECC Don't Miss this Keynote...

Santa Clara - January 27th David Francis Doody, Lead Engineer Realtime Flight Operations, JPL

## **Innovative Integration**

#### **X5 Family PCI Express XMC Modules**

**OS Support**: Windows, Linux, and VXWorks/Wind River **Bus Interface**: PCI Express, adapters for PCI, cPCI, & VPX

The X5 module family integrates high performance I/O with Xilinx Virtex5 FPGA computing core on 75x150mm module (IEEE1386) with a PCI Express interface. The Virtex5 SXT FPGA provides up to 640 DSP48 elements combined with memory that is critical to implementing efficient signal processing algorithms and data acquisition.

Innovative's unique Velocia architecture provides up to 1 GB/s data streaming to the host that is flexible & extensible for all types of applications. It's fast and easy to use—allowing you to concentrate on your application work because it handles all the data flow and routing. You can freely mix high rate data streams with control and status making it easy to adapt to you application, yet still achieve the full GB/s data rate capabilities of the PCle interface.

All X5 modules are architected to deliver high data throughput to the Host, along with the flexibility of usercustomizable FPGA signal processing. Board specific analog or digital I/O flows directly into the user-configurable Xilinx 5 logic device. The supplied stock logic functionality allows the board to be used out-of-the-box as a high-speed I/O board in which the large onboard DDR2 DRAM is configured as an enormous virtual FIFO data buffer. The QDR SRAM interface is a very highspeed local cache for custom algorithms running within the FPGA. Download pricing and data sheets from www. innovative-dsp.com

#### FEATURES & BENEFITS

- Ultra-fast signal capture, generation & co-processing - Spartan 3 & Virtex-5 FPGA, huge DDR/QDR memory, multi-lane PCI Express with a private J16 user I/O port. Excellent choice for SDR, signal intelligence, RADAR, radio test equipment.

- X5-210M: PCI Express XMC Module with Four 250 MSPS 14-bit A/Ds, Virtex5 FPGA, and DDR2/QDR-II Memory

- X5-G12: PCI Express XMC Module with Dual channel 1 GSPS,12-bit Digitizer, Virtex5 FPGA and 512MB Memory

- X5-400M PCIe XMC Module Two 400 MSPS, 14-bit TI ADS5474 ADCs and Two 500 MSPS, 16-bit DACs, Virtex5 FPGA and 512 MB Memory

- X5-GSPS: PCI Express XMC Module with Two 8-bit National ADC08D1500 A/Ds, Virtex5 FPGA and 512 MB Memory

#### **TECHNICAL SPECS**

- 400 MSPS, 14-bit A/D channels Two 500 MSPS, 16-bit DAC channels +/-1V, 50 ohm, SMA inputs and outputs

- Xilinx Virtex5, SX95T FPGA

512 MB DDR2 DRAM

4 MB QDR-II SRAM

- 8 Rocket IO private links, 2.5 Gbps each 1 GB/s, 8-lane PCI Express Host Interface

- Power Management features XMC Module (75x150 mm) PCI Express (VITA 42.3)

- Ruggedization Levels for Wide Temperature Operation Adapters for VPX, Compact PCI, Desktop PCI and Cabled PCI Express System

#### **AVAILABILITY**

Shipping

#### **APPLICATION AREAS**

- Wireless Receiver and Transmitter

- WLAN, WCDMA, WiMAX front end

- RADAR

- Electronic Counter Measures (ECM)

- Electronic Warfare

- High Speed Data Recording and Playback

- High speed servo controls

- Spectral Analysis

- IP development

#### **CONTACT INFORMATION**

Innovative Integration 2390 Ward Avenue Simi Valley, CA 93065 USA

805-578-4260 Telephone 805-578-4225 Fax sales@innovative-dsp.com www.innovative-dsp.com

#### X6-RX

OS Support: Windows, Linux, and VXWorks/Wind River Bus Interface: natively xmc/pmc adapters to VPX, cPCI, PCI, PCI Express

The X6-RX is a flexible receiver that integrates IF digitizing with signal processing on a PMC IO module. Up to 24 configurable receiver channels with a powerful Xilinx Virtex 6 FPGA signal processing core, & high performance PCI Express/PCI host interface. With the X6-RX, IF recorders can log both the digitized raw data & channels real-time sustaining rates over 2 GB/s.

The X6-RX features four, 16-bit 160 MSPS A/Ds with dual digital downconverters (DDC). IF frequencies of up to 300 MHz are supported. The sample clock is from either a low-jitter PLL or external input. Multiple cards can be synchronized for sampling & downconversion.

A Xilinx Virtex6 SX315T (LX240T at initial release) with 4 banks of 128MB DRAM provide a very high performance DSP core with over 2000 MACs (SX315T). The close integration of the analog IO, memory & host interface with the FPGA enables real-time signal processing at extremely high rates.

Onboard DDC ASIC device, connected directly to the FPGA, provides up to 24 narrowb &/or 8 wideb & channels with input from two A/D channels. The DDC performs complex or real downconversion, with flexible controls for mixing, filtering, decimation, output formats & data rates. Channels can be synchronized to support beam forming or frequency hopped systems.

Power is less than 15W for typical operation. VITA 20 conduction cooling is used with a heat-spreader & sink are Ruggedization levels for wide-temperature operation & conformal coating are supported.

#### **FEATURES & BENEFITS**

- Four 160 MSPS, 16-bit A/D channels Down-Converter ASIC supporting up to 24 Narrowband or 8 Wideband Channels +/-1V, AC-Coupled, 50 ohm, SMA inputs

- Xilinx Virtex6 SX315T/SX475T or LX240T 4 Banks of 128MB DRAM Ultra-low jitter programmable clock

- x8 PCI Express Gen2, providing 2 GB/s sustained transfer rates

- PCI 32-bit, 66 MHz with P4 to Host card

- PMC/XMC Module (75x150 mm)

15W typical

Conduction Cooling per VITA 20

Ruggedization Levels for Wide Temperature Operation Adapters for VPX, Compact PCI, desktop PCI and cabled PCI Express systems

#### **TECHNICAL SPECS**

- Available XMC carrier adapters offer conduction & convection cooling & are available for a range of interfaces including Desktop PCI, Desktop PCI Express, Cabled PCI Express, CompactPCI, & PXI/PXI Express.

- Extremely versatile, easily adapted for use in virtually any type of system. The X6-RX is also readily installed into Innovative Integration's elnstrument Embedded PC, SBC-ComEx Single-Board Computer, & Andale Data Loggers.

- PCI gen 2 to 24 Megabytes per second. 200 fS clock jitter

- 15 watt nominal power dissapation!

- Military rugged versions available.

#### **AVAILABILITY**

Shipping

#### **APPLICATION AREAS**

- Wireless Receiver

- WLAN, WCDMA, WiMAX front end

- RADAR

- Medical Imaging

- High Speed Data Recording and Playback

- IP Development

#### **CONTACT INFORMATION**

Innovative Integration 2390 Ward Avenue Simi Valley, CA 93065 USA 805-578-4260 Telephone 805-578-4225 Fax sales@innovative-dsp.com www.innovative-dsp.com

## Xilinx, Inc.

#### Spartan-6 FPGA Connectivity Kit

#### Supported Xilinx FPGA/CPLDs: Spartan-6 LXT

The Xilinx® Spartan®-6 FPGA Connectivity Kit is a complete, easy-to-use connectivity development and demonstration platform using the low-cost Spartan-6 LXT device family. As a Xilinx Connectivity Targeted Design Platform, this kit provides the hardware, software, IP, and Targeted Reference Designs needed to create high-speed serial systems and other connectivity applications right out of the box.

The Spartan-6 LXT FPGA enables designing with industry-standard high-speed serial protocols including PCI Express® (version 1.1), Ethernet (GMII, SFP), and DDR3, as well as enabling designs using other serial standards and proprietary implementations up to 3.125G/ps and multiple parallel protocols including 3.3V I/O standards.

The Connectivity Kit with Spartan-6 LXT FPGA simplifies design, development, and validation of multi-protocol systems with an efficient, low-cost programmable connectivity solution. Production-proven methodologies and tool suites delivered with the kit enable designers to analyze and debug high-speed serial solutions in real time.

The kit integrates the critical components of connectivity development to accelerate design, implement low-cost protocol bridging, and provide higher efficiency alternative to LVDS communication. It also serves as the starting point for market-specific connectivity design platforms with scalable building block architecture, Targeted Reference Designs, and hardware ecosystem of industry-standard FMC daughter card extensions.

#### FEATURES & BENEFITS

- Comprehensive connectivity development platform with all the hardware, software, firmware, IP, and reference designs needed to create fully functional working system

- ISE® Design Suite Logic and Embedded Editions tailored for system designers with ChipScope™ Pro Analyzer and Serial IO Toolkit (device-locked to Spartan-6 LX45T FPGA)

- Pre-verified, customizable Targeted Reference Design integrates PCIe<sup>®</sup>, Gigabit Ethernet, and on-board DDR3 memory with virtual FIFO and optimized Packet DMA to accelerate bandwidth

- Multiple example designs including hard memory controller, iBERT, and others

#### **TECHNICAL SPECS**

- RoHS-compliant SP605 board with Spartan-6 LX45T FPGA, universal power supply, and accessory cables

- On-board FMC daughter card connector for plugin scalability

- USB flash drive with device driver files, design source files, applications

- Downloadable documentation with schematics, Gerber files, board BOM, and detailed user guides

#### **AVAILABILITY**

Available today at: www.xilinx.com/kits

#### **APPLICATION AREAS**

Aerospace/Defense, Broadcast, Data Processing and Storage, Industrial Automation, Medical Imaging, Wired Communcations, Wireless Communications

**CONTACT INFORMATION**

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 USA 408-559-7778 Telephone more\_info@xilinx.com www.xilinx.com/kits

#### **Spartan-6 FPGA DSP Kit**

#### Supported Xilinx FPGA/CPLDs: Spartan-6 LX, Spartan-6 LXT