# **Engineers' Guide to FPGA & PLD Solutions**

ALLIN BI IN

**Automotive Electronics Fuels Need for High-Reliability Devices**

**FPGAs: Good Company in Consumer Mobile Devices Seeking Differentiation**—Fast

**Practical Tips For External** Logic Analyzer FPGA Debug

## www.eecatalog.com/fpga

Market Leader Sponsor

Gold Sponsors

# World First MGT<sup>\*</sup>-based FPGA Debug

EXOSTIV

www.yugosystems.com

**Observability** Reloaded

Up to 8GB storage

Up to 32.768 nodes

## FPGA DEBUG RELOADED

## SUPERIOR EMBEDDED SOLUTIONS

## **DESIGN YOUR SOLUTION TODAY** CALL 480-837-5200

### www.embeddedARM.com

## NEW! TS-4740 Computer Module

Pricing Starts At \$**176**

- I GHz Marvell PXA168 ARM CPU

- 512 MB DDR3 RAM and 4 GB eMMC Flash ж.

- 25 KLut FPGA, 1x Gigabit Ethernet, 1x 10/100 Ethernet

- Ix microSD card, 1x USB Host, 1x USB OTG

- 121x DIO, 1x I2C, 1x SPI, 1x CAN, 6x UARTs

- -40 °C to 85 °C Industrial Temperature Range

- Supports video acceleration up to 720p

- Boots Debian Wheezy with Linux Kernel 2.6.34

### **Computer-on-Modules**

#### State of the Art Embedded Design

- TS-4600: 450 MHz low cost w/ 2 Ethernets

- TS-4710: Up to 1 GHz PXA168 w/ video

- TS-4720: Like TS-4710 + 2 GB eMMC Flash & 2 Ethernets .

- TS-4200: Atmel ARM9 w/ super low power

- TS-4800: 800 MHz FreeScale iMX515 w/ video

## NEW<sup>1</sup> TS-7700 Single Board Computer

High Performance Compact Computer

Available with TS-ENC750 enclosure and TS-752 interface board

#### **Features:**

- Up to 1 GHz ARM CPU = 2x USB Host

- 512 MB RAM

- 8 KLut FPGA

- 2x microSD Socket

- 1x 10/100 Ethernet

#### **Benefits:**

- Hardware flexibility with on-board FPGA

- Several control I/O interfaces

- Launches your application in under a second

- Easy development w/ Debian and Linux 2.6.34

- High data reliability with 2x microSD RAID storage

- -40 °C to 85 °C industrial temperature range

We've never discontinued a product in 30 years

Embedded systems that are built to endure

Support every step of the way with open source vision

Unique embedded solutions add value for our customers

## www.embeddedARM.com

- 55x DIO, 1x CAN

- 1x SPI, 1x I2C, 1x I2S

- 128 MB NVRAM 6x Serial Ports

## Welcome to the 2015 Engineers' Guide to FPGA and PLD Solutions

It's always a good thing when answers to questions don't just set out the facts but go further, pointing out connections or setting details into an historical context. Synopsys's Troy Scott does just that in this issue. (See "A Few Questions on...FPGA-based Prototyping Software Tools.") For example, he compares the culture change he believes must take place as development teams adopt Design for Productivity (DFP) best practices with the earlier shift from "an emphasis on ASIC design productivity to ASIC verification productivity."

Anything that's large and unable to say no to hefty power meals doesn't sound right for mobile designs. However, you'll read in an article by Mauri Delostrinos of Lattice Semiconductor that the emergence of low-gate-count devices as small as 1.4 x 1.48mm that use power sparingly and are inexpensive has opened the way for FPGAs to have a companion chip role in mobile devices. Delostrinos explains why "Mobile Industry Processor Interface (MIPI) displays are a major application area for FPGAs."

On the topic of mobile as in automobile, Dr. Raik Brinkmann of OneSpin Solutions argues that for automotive safety critical design, the "traditional approach of running an FPGA design on the actual hardware to provide a functional testing environment cannot satisfy the verification needs of the standards...." His very thorough article also addresses such topics as the relationship between aggressive design optimizations and error introduction.

One relationship 4DSP's Jason Cella discusses for us is that involving increased mobile broadband traffic and the limited amount of available wireless spectrum—an unhealthy relationship when the result is call interference. But adaptive beamforming—and FPGAs—can help.

Also in this issue, WIN Enterprises looks at what's helpful to highperformance computing projects, Keysight Technologies acknowledges that "probing the FPGA external I/O signals that are part of the real design" can be challenging and BittWare's Jeff Milrod shares his perspective on protoyping.

Anne Fisher

anne Fisher

Managing Editor P.S. To subscribe to our series of Engineers' Guides for embedded developers and engineers, visit: www.eecatalog. com/subscribe

## Engineers' Guide to FPGA and PLD Solutions 2015

www.eecatalog.com/fpga

#### Vice President & Publisher

Clair Bright cbright@extensionmedia.com (415) 255-0390 ext. 15

#### Editorial

Editor-in-Chief Chris A. Ciufo cciufo@extensionmedia.com Managing Editor Anne Fisher afisher@extensionmedia.com

Creative/Production Production Manager Spryte Heithecker

Media Coordinator Yishian Yao

**Graphic Designers** Nicky Jacobson Caldin Seides

Senior Web Developer Mariam Moattari

#### Advertising/Reprint Sales

Vice President & Publisher Embedded Electronics Media Group Clair Bright cbright@extensionmedia.com (415) 255-0390 ext. 15

Sales Manager Michael Cloward mcloward@extensionmedia.com (415) 255-0390 ext. 17

Marketing/Circulation Jenna Johnson

To Subscribe www.eecatalog.com/subscribe

#### Extension

M E D I A Extension Media, LLC Corporate Office (415)255-0390

President and Group Publisher Vince Ridley vridley@extensionmedia.com

Vice President, Sales Embedded Electronics Media Group Clair Bright cbright@extensionmedia.com

Vice President, Business Development Melissa Sterling msterling@extensionmedia.com (415)-970-19100

#### **Special Thanks to Our Sponsors**

The Engineers' Guide to FPGA and PLD Solutions is published by Extension Media LLC. Extension Media makes no varranty for the use of its products and assumes no responsibility for any errors which may appear in this Catalog nor does it make a commitment to update the information contained herein. The Engineers' Guide to FPGA and PLD Solutions is Copyright @2014 Extension Media LLC. No information in this Catalog may be reproduced without expressed written permission from Extension Media @ 1786 18th Street, San Francisco, CA 94107-2343.

All registered trademarks and trademarks included in this Catalog are held by their respective companies. Every attempt was made to include all trademarks and registered trademarks where indicated by their companies.

Register and get your tickets now! **embedded-world.de**

## Nürnberg, Germany February 24 – 26, 2015 embedded world 2015 Exhibition & Conference

... it´s a smarter world

### THE gathering for the embedded community!

The world's largest event for embedded technologies brings together all the players in the embedded sector for a productive conversation.

Make sure you are there when contacts and networks are being cemented on the international level and new trends are being set.

Media partners elektroniknet.de computer-automation.de energie-und-technik.de MEDIZIN-we-elektronik.DE Markt&Technik DESIGN (3)

EKTRON

NOW-HOW FÜR ENTWICKLER

automotive

MEDIZIN®elektronik

Trade fair organizer NürnbergMesse GmbH Tel +49(0)911.8606-4912 visitorservice@nuernbergmesse.de

Congress organizer WEKA FACHMEDIEN GmbH Tel +49(0)89.2 55 56-13 49 info@embedded-world.eu

### CONTENTS

| Automotive Electronics Fuels Need for High-Reliability Devices<br>By Dr. Raik Brinkmann, OneSpin Solutions                 | 5  |

|----------------------------------------------------------------------------------------------------------------------------|----|

| FPGAs: Good Company in Consumer Mobile Devices Seeking Differentiation—Fast<br>By Mauri Delostrinos, Lattice Semiconductor | 8  |

| Practical Tips For External Logic Analyzer FPGA Debug<br>By Brad Frieden, Keysight Technologies                            | 11 |

| A Few Questions onFPGA-based Prototyping Software Tools<br>By Anne Fisher, Managing Editor                                 | 15 |

| Don't Swallow the Camel and Other FPGA Wisdom<br>By Anne Fisher, Managing Editor                                           | 18 |

| The FPGA Advantage for Beamforming<br>By Jason Cella, 4DSP, LLC                                                            | 20 |

| Once Earmarked for FPGA Always Earmarked for FPGA?<br>By Todd Sirois, WIN Enterprises                                      | 22 |

### **PRODUCT SERVICES**

#### **FPGAs & PLDs**

| FPGA Chips               |    |

|--------------------------|----|

| Xilinx, Inc.             |    |

| 7 series FPGA Portfolio  | 25 |

| 20 nm UltraScale Devices |    |

|                          |    |

### FPGA and SoC Chips

| Xilinx, Inc. |  |

|--------------|--|

|--------------|--|

| Xilinx Low-End Portfolio27 |

|----------------------------|

|----------------------------|

#### SoC

#### Xilinx, Inc.

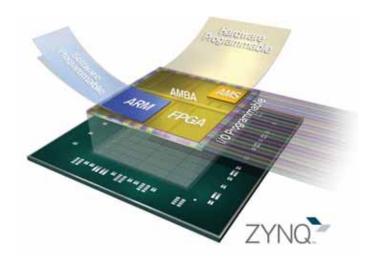

| Zyng-7000 All Programmable SoC 28 | Zyng-7000 All | Programmable | SoC | 28 |

|-----------------------------------|---------------|--------------|-----|----|

|-----------------------------------|---------------|--------------|-----|----|

Cover image courtesy of Daimler Mercedes-Benz

#### **Boards & Kits**

#### Design Kits

| Xilinx, Inc.                            |    |

|-----------------------------------------|----|

| Kintex UltraScale KCU105 Evaluation Kit | 29 |

| Zynq-7000 All Programmable              |    |

| SoC ZC702 & ZC706 Evaluation Kits       | 30 |

#### **Development Tools**

Design Tools

| Xilinx, Inc.        |   |

|---------------------|---|

| Vivado Design Suite | 1 |

### **Verification Tools**

#### **Development Tools**

| Yugo Systems |    |

|--------------|----|

| EXOSTIV™     | 32 |

**EECatalog** SPECIAL FEATURE

## Automotive Electronics Fuels Need for High-Reliability Devices

Already working on behalf of custom automotive devices, verification tools based on formal methods are now helping put FPGAs in the driver's seat—can mil/aero, transportation, power generation and other safety-critical areas be far behind?

#### By Dr. Raik Brinkmann, OneSpin Solutions

Safety critical design of automotive electronics, including those using FPGAs, falls under the new ISO 26262 standard. The need for more complex functions and high performance in an ultra-reliable environment plays a substantial role in automotive embedded system design.

Field Programmable Gate Arrays (FPGAs) offer flexibility and density at affordable implementation cost, so it is not surprising that the use of FPGAs in automotive systems is expanding. With custom devices being expensive to produce, many design teams resorted to Micro Controller Units (MCUs) for many functions. FPGAs offer an attractive alternative to a software only functional model, while retaining the design cost benefits of the MCU. In addition, modern FPGAs contain convenient hardware functions useful in automotive applications, and may also be updated in the field. Another area where FPGAs shine is in boosting performance for compute-intensive automotive applications such as Advanced Driver Assistance Systems (ADAS).

The traditional approach of running an FPGA design on the actual hardware to provide a functional testing environment cannot satisfy the verification needs of the standards, and using simulation only improves the situation slightly. Developers have been using verification tools based on formal methods for custom automotive devices. It's an approach that can meet FPGA needs as well.

#### **The Impact of Automotive Failsafe Requirements**

Today the simplest of modern vehicles will contain a number of processors, and this runs into the hundreds of compute elements for high-end vehicles. Electronics are present throughout the safety critical components in the car, aid the driver in its safe operation, and introduce a new level of comfort. However, if one of these critical systems fails during operation, the result is catastrophic. As such, standards have been ratified, such as ISO 26262, which lay down design and verification metrics that must be followed for these devices to be employed by automakers.

For example, the highest safety standard (or "Automotive Safety Integrity Level") defined in ISO 26262 is ASIL-D, and this sets the required likelihood of malfunction to a

#### **Triple Modular Redundancy**

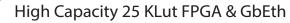

Figure 1. For critical areas of logic, Triple Modular Redundancy (TMR) is sometimes leveraged.

statistically defined failure rate of 10–9 per hour, a staggering 1 in every 114,155 years. Furthermore, these requirements must be measured on the final gate level representation of the device, not the Register Transfer Level (RTL) used for design and simulation, and the failure introduced during testing without any additional hardware being incorporated on the device. To ensure that these metrics may be met, engineers add additional failsafe structures into their designs.

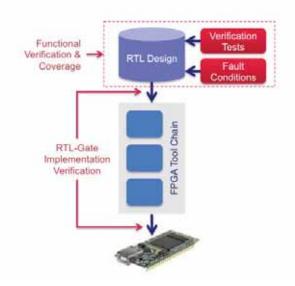

To take another case, in the event of rare, spurious memory data errors, error correction code mechanisms are used where data is encoded when written into memory, and decoded on a read. Any errors caused by external factors are picked up and corrected using this method. Although it's a significant overhead to added error correcting codes on key RAMs, this method guarantees against memory defects.

### **FPGA Verification Flow**

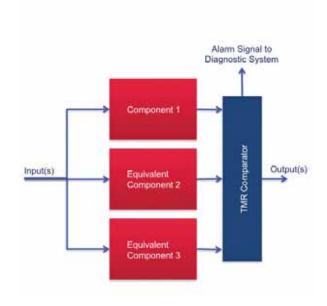

Figure 2. Test methods must be even more rigorous than existing verification practices.

Similarly for critical areas of logic, Triple Modular Redundancy (TMR) is sometimes leveraged. See Figure 1. Instead of just one logic block, three are employed to perform the same function. The output of two of the blocks is continuously compared and if there is a difference, the third block is used to arbitrate between the other two. An alarm bit is also raised on a difference, and if this alarm bit occurs frequently, the overall safety diagnostic system will flag the device for future replacement.

#### **The Verification of Safety Critical Designs**

The verification of overall device design and implementation, together with the validation that these safety systems operate correctly, of course requires test methods even more rigorous than existing verification practices. (See Figure 2.) The exhaustive and rigorous nature of the technology makes formal verification techniques a natural choice for these devices.

Bugs introduced through design error, or by the tool chain during implementation, must be eliminated by thorough verification. To ensure that the verification environment is properly qualified for this purpose, it's essential to employ high quality verification coverage. The rate of verification coverage, that is the proportion of the design proven to have been tested, must be as close to 100% as possible, and this metric must be produced somewhat independently of the verification tools employed. Techniques for testing coverage by analyzing the ability of the verification environment to detect errors in any part of the design code have become established as a mechanism for producing this metric. A number of automotive electronics companies now use Observation Coverage that employs an exhaustive formal-based approach to understand if a design change will trigger verification checks.

Observation Coverage uses a mechanism where the design code is temporarily altered to see if the checks within the verification environment flag these changes. By manipulating these alterations and using the exhaustive nature of the formal techniques, it is possible to establish a precise test metric for the entire design, without the overhead of some similar methods.

#### **Aggressive Design Optimizations**

While Observation Coverage assists in proving that design verification has been properly carried out, in an FPGA design additional verification is required to ensure that the design described at the RTL level has properly passed through the synthesis and place and route tool chain without the introduction of additional bugs. For FPGAs, this is particularly important due to the advanced nature of FPGA synthesis. FPGA synthesis targets fixed device fabrics. To produce the highest quality design, they employ a range of aggressive design optimizations. On occasion these optimizations may introduce errors of their own.

Equivalency Checking (EC) tools that use formal verification to exhaustively compare RTL descriptions against resulting gate level code are commonplace in the ASIC world, but are new to FPGAs. However, they are rapidly being employed on large FPGA designs to counter the time it takes to weed out tool chain errors. For FPGAs, specialized EC tools are required

### **Inserting Faults In Memory Test**

Figure 3. Formal methods offer a mechanism for introducing faults without changing the design code.

that can support the complex sequential nature of the synthesis optimizations. By employing FPGA EC, engineers can safely leverage these optimizations to produce the highest quality design possible, with confidence that bugs will not be introduced. For Safety Critical designs EC usage goes further by proving that the tool chain has not introduced errors after the RTL has been fully validated.

#### **Understanding Forward and Reverse Mapping**

For ISO 26262 there is another reason why these tools are required. The verification of faulty device scenarios must be carried out on the final gate level design, not the RTL code. As such, understanding the forward and reverse mapping of the RTL to gate design such that test faults may be properly inserted and results interpreted is key, and this may also be accomplished with these EC Tools.

To test for the system's ability to recover or absorb faults, a methodology must be leveraged that allows these faults to be introduced without changing the design code, and the correct operation observed. Formal methods provide an easy mechanism for this, (Figure 3). Properties may be written that specify the correct operation of the system. Faults are then injected at various intervals and locations using formal constraints during verification, and the properties examined to ensure they still hold true. If they do, the system has been proven to respond correctly to these faults.

#### **Automotive FPGAs Here to Stay**

Custom hardware devices clearly have advantages over MCUs for many automotive applications but to produce an ASIC often cannot be justified given the expected volumes and design effort required. FPGAs fit this need perfectly and enable a number of unique capabilities especially useful in this environment. However, the testing of these devices has to meet safety critical hardware standards, introducing design and verification overheads. Formal Methods provide an effective way to meet the requirements of the standards for FPGAs, driving the use of the tools in this application, as well as other safety critical areas such as the aerospace, power generation, and defense industries. Using a formal tool based flow improves design quality, return on investment and time-to-market.

Dr. Raik Brinkmann is President and Chief Executive Officer of OneSpin Solutions.

## FPGA and PLD Solutions ONLINE

## www.eecatalog.com/fpga

## Explore...

- Top Stories and News

- White Papers

- Expert Opinions (Blogs)

- Exclusive Videos

- Valuable Articles

## Sign up for the FPGA Quarterly Report email newsletter

### → www.eecatalog.com/fpga

## FPGAs: Good Company in Consumer Mobile Devices Seeking Differentiation—Fast

Why a companion chip role for today's smaller, less power hungry FPGAs serves smartphones, smart watches, wearables and to-be-imagined mobile consumer devices well.

#### By Mauri Delostrinos, Lattice Semiconductor

Apple released its first generation iPhone on June 29, 2007; now we are using seventh-generation iPhone 5C and iPhone 5S products that have been available since last year. As I write this, news is breaking that Apple has sent out invites to an event that the company is hosting in Cupertino on September 9, with the tagline "Wish we could say more" to discuss the iPhone 6. The "i" brand—starting with iPods and then iPads before the emergence of the iPhone—has become so successful, first as an aspirational product, then as an ubiquitous item, that 100s of many different "i-\_\_" products have been produced.

Similarly, a quick Internet search identifies that since 2009, Samsung has launched more than 100 smartphones, tablets, phablets, cameras and watches that bear the Galaxy brand alone. Products from other big name players such as LG, Sony and HTC also proliferate in the market, and then there are emerging makers in Asia looking to provide similar products, usually at a lower price premium.

What these well-known market research snippets ably demonstrate is the short lifecycle of any one product generation. Also in evidence: the reduced profitability window that any manufacturer of such consumer items has available to exploit and the essential speed of new product development. Also, with the huge choice on offer to consumers, manufacturers must constantly evolve new features and functions to differentiate themselves in a very competitive marketplace.

#### The Re-spin Conundrum

Early generation products in this sector used an architecture based on a processor and an application-specific signal processor (ASSP). This is a valid approach, especially in a cost-sensitive market. However, there are two major problems given the need for fast development and product differentiation. Developing any form of ASIC or ASSP-based solution requires a great deal of effort based on early marketing decisions, which can be costly and time-consuming to change in response to evolving competitor and consumer influences. Second, processors have limited ability to handle different I/O, memory types, display and sensor interfaces. Therefore, if the design calls for, say, a different type of sensor, either you'll need to change your processor or manage some form of bridging solution in an ASIC re-spin.

For these reasons—chiefly centering on speed of development and flexibility—manufacturers are now increasingly implementing mobile designs that use FPGAs in a companion chip role. Traditionally, FPGAs would have been considered too big, too expensive and too power-hungry for mobile consumer applications. However, with the advent of low gate count devices that are as small as  $1.4 \times 1.48$ mm, consume as little as  $21 \mu$ W and cost only 50 cents the picture has changed. For example, a Chipworks teardown identifies a Lattice FPGA inside Samsung's Galaxy S5.

Figure 1: The dramatic shift from FPGA (28 nm Virtex-7) to programmable ASIC-like SoC (20 nm Virtex Ultrascale).

### **EECatalog** SPECIAL FEATURE

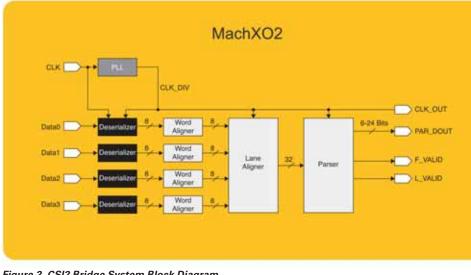

Figure 2. CSI2 Bridge System Block Diagram

#### **Easily Switching Display Types**

Within this context of the arrival of smaller and less expensive FPGAs, Mobile Industry Processor Interface (MIPI) displays are a major application area for FPGAs. The majority of image sensors in the consumer market use the MIPI CSI2 interface. The MIPI has become the interface standard for the majority of components in consumer mobile devices. Camera Serial Interface 2 (CSI2) is the MIPI interface specification focused specifically on cameras. Often the ASSP used in smartphone and especially wearable electronics does not have

a CSI2 interface. FPGAs can perform a bridging function to convert from CSI2 to parallel CMOS, enabling the manufacturer to easily switch display types and suppliers as is commercially advantageous.

Figure 1 shows this CSI2 to CMOS parallel function being performed by a member of Lattice's MachX02 FPGA family.

The CSI2 Bridge converts the CSI2 interface to a parallel sensor interface for an ISP. True LVDS input pads on the MachXO2 device handle the 200 mV common mode voltage of the MIPI DPHY high-speed interface. The CSI2 interface from the image sensor can be 1, 2 or 4 data lanes. To keep the FPGA density small, the CSI2 bridge is typically synthesized for a single CSI2 format. In most embedded applications the image sensor is typically configured for a single CSI2 output format at all times. However, multiple CSI2 formats can be supported for "on-the-fly" switching by adding multiple instantiations of the mipi csi2 serial2parallel NGO in each desired format. Figure 2 depicts the system block diagram.

#### Support for Custom Functionality Efforts

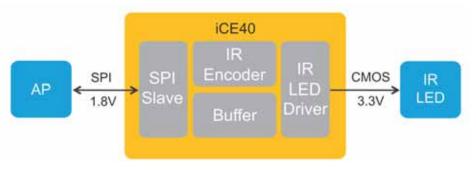

It is tempting to be skeptical about how much can usefully be achieved using small—both in terms of actual size and gate count—FPGAs. In fact, many features such as IR Tx/ Rx Control, Bar Code Emulation, Pedometer, Activity Monitoring, Sensor Pre-Processing and LED Control can he successfully implemented in devices such as Lattice's newly introduced iCE40 Ultra FPGA family. Integration of high current sink LED drivers, multipliers and accumulators

optimizes custom function implementation, standard serial interfaces such as SPI & I2C and a whole host more of hardened IP. This ASSP-like integration reduces system power and speeds implementation so designers can spend more time on implementing their custom functionality.

FPGAs can take on many other functions in the consumer space. For example, they can be used to capture LVDS video data at high speed and process it using the on-chip sysDSP

Figure 3. FPGA enables timing-critical IR-LED control.

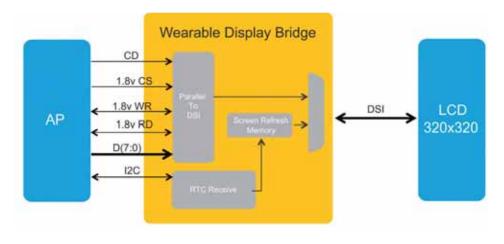

Figure 4. Wearable Display Bridge – Standard Parallel Bus to single to MIPI DSI

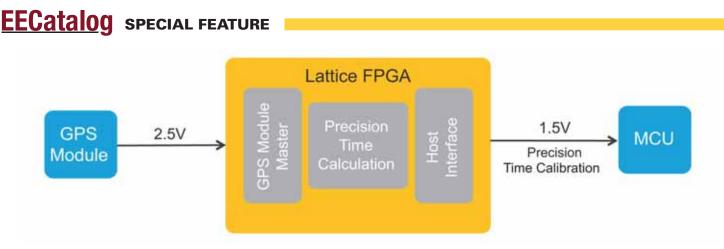

Figure 5: Smart Watch-Auto Time Calibration + IO Bridge

block and embedded RAM. Another application adds a universal remote function within a smartphone using just a tiny iCE40 FPGA as shown in Figure 3.

Figure 4 details a standard parallel bus to single to MIPI DSI bridge that improves battery life in wearable displays by enabling the applications processor to remain in sleep mode for longer.

Figure 5 shows a design for a smart watch. In this application the FPGA is delivering an auto time calibration + IO bridge function. By so doing the FPGA overcomes the problem that some MCUs do not support 2.5V IOs, needed to interface with GPS modules enabling the watch to automatically reset time when the user travels to a new time zone.

FPGA flexibility enables the imagination to run riot. Smart glasses can include branding held in simple code, and intelligent lighting effects—whether user, context or sensor stimulated—can be simply realized using LEDs.

Designers working in the consumer market who have not considered using field programmable devices before may have concerns about the design methodology. Support is available in the form of tools for the following:

- Design Entry

- Synthesis

- Implementation

- Analysis

- On-chip Debug Hardware Analysis

- Simulation

- Programming

- Deployment

#### Support for third-party tools is also available.

Therefore, designers can develop, run and simulate their RTL code, then run the code and validate it in hardware. Software developers like this design methodology too as it enables C/C++ to be supported with soft-processor IP doing way with the need for developers to learn a new hardware language in order to implement a solution.

Lattice Diamond supports VHDL, Verilog, EDIF, schematics and multiple implementations. It also features an easy to use GUI, but as a script is sometimes the fastest way to do a task, full Tcl scripting support is also provided.

#### Conclusion

New generation FPGAs that have been architected for low power and small size, targeting mobile consumer applications, are currently being used in high-volume applications and are proving beneficial in adding flexibility to the development of products such as smartphones, tablets, eBooks and wearable electronics. Alongside devices that are fully uncommitted, FPGAs are also starting to be introduced that incorporate hardened features—memory, I/O, display and sensor interfaces, SERDES —which combine the flexibility of programmability with the efficiency of commonly demanded features. Either way, designers who have previously avoided taking the FPGA path may wish to reconsider.

Mauri Delostrinos is currently Consumer Account Manager at Lattice Semiconductor based in San Jose, California. He is responsible for developing strategic planning for selected Consumer Accounts and for supporting major consumer device manufacturers in the Bay Area and beyond. A graduate of the

Stanford University School of Business, Delostrinos has also held Applications and Field Applications Engineering roles with Lattice, during which time he participated in Product Definitions for next generation FPGA families and supported key accounts and leading consumer companies in the Silicon Valley.

## Practical Tips For External Logic Analyzer FPGA Debug

Already working on behalf of custom automotive devices, verification tools based on formal methods are now helping put FPGAs in the driver's seat—can mil/aero, transportation, power generation and other safety-critical areas be far behind?

#### By Brad Frieden, Keysight Technologies

Today's design tools provided by FPGA vendors offer powerful debug capabilities through a variety of debug cores. Integrated logic analyzers allow for a designer to probe many internal FPGA nets and store captured signal traces in block RAM for analysis and viewing. Although these "inside the chip" tools are very useful, there are times when the deep memory capture available in an external logic analyzer or mixed-signal oscilloscope can be very helpful to further discover the root cause of the failure in a prototype, or to view a particular operation in a design, such as capturing one complete video frame in a video processing design. Powerful debug-oriented trigger techniques are also helpful to trap bugs. This article will explore techniques for all of these topics.

#### **Routing Signals Out of an FPGA Design**

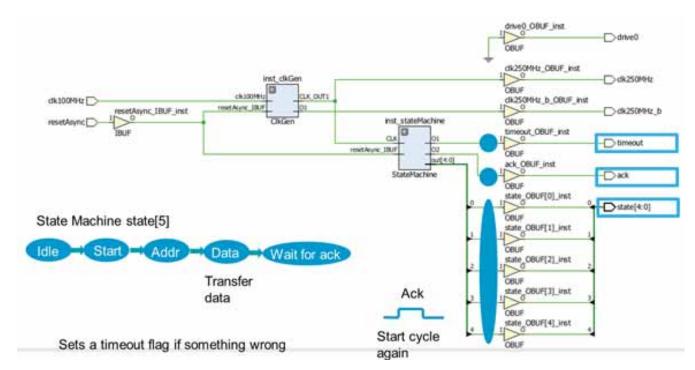

Consider an example Xilinx Zynq 7020 system on chip (SoC) Vivado demo design where a five-bit "one-hot" state machine (shown in Figure 1) represents a process of moving data. The state machine should go through the "idle" state, the "start" state, "address" state, "data" state where data should be moved, and then reach the "waiting for acknowledge" state. Once the data is received, an acknowledge signal should come back. But in our demo scenario, something's going wrong, and only part of the data is getting transferred.

Understandably, some key signals of interest include the "state" five-bit parallel bus, the acknowledge bit and a timeout bit that gets set if something goes wrong in the design. Sometimes a prototype system hasn't been laid out on a PC board so that there is easy access to the real I/O signals, but there may be some FPGA pins dedicated for debug and routed to a header or connector. How does one get nets of interest, in this case, inside the FPGA I/O ring, routed to that debug connection point? Those desired nets are shown in Figure 1 with blue circles and an oval.

Figure 1. Expected data transfer state machine operation and schematic for the implemented design

Figure 2. Tcl script syntax and steps to route out a net to a desired FPGA debug pin.

Step 1 From Xilinx Vivado, attach "Mark\_debug" property to the wires of interest.

A first step to routing out the "state", "ack" and "timeout" signals is to attach a "mark debug" property to the wires of interest. This first step ensures that nets of interest do not get optimized away during synthesis. It also ensures that the signal names are preserved through synthesis so that they can still be "found" after synthesis.

In this case, the "state[5]" five-bit bus, the "ack" one-bit signal and "timeout" one-bit signal are all of interest.

In the case of the "ack" signal, one needs to place in the source:

wire ack;

assign ack = ack;

(\* mark\_debug = "true" \*) wire ack;

This must also be done for "state[5]" and "timeout".

Step 2 Implement the design and uncheck "MARK\_DEBUG" and "DON'T\_TOUCH".

The second step is to implement the design and then uncheck the "MARK\_DEBUG" and "DON'T\_TOUCH" attributes for each of the nets desired for probing. This is done in the "Net Properties" window in Vivado. This allows the freedom to route out signals from those nets to debug ports. Specifically, the way this is done, from the schematic view of the post-implemented design, one clicks on and highlights each net of interest, and then unchecks these two attributes.

It's important to note that if a signal of interest is already being routed to an FPGA pin as part of the real design, as in this case, then one must select the net just prior to the final OBUF and route that net out for debug. The name of such signals should have been preserved because of the "MARK\_DEBUG" statement that was placed in the source for those signals.

For example, by clicking on the net just prior to the final OBUF before the "ack" signal output in the design, one would see in a Vivado net description field that the net name is called "ack\_ orig". This is the preserved net name that will be used in the next step for signal route out.

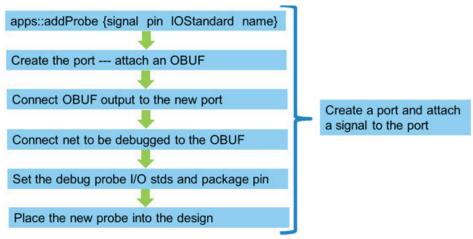

Step 3 Run a Tcl script to route out

each desired signal.

A Tcl script, provided by Xilinx, can now be run to make an incremental compile to route out each net of interest to a pin specified, with the name chosen by the designer for that routed out net. This script is located at http://www.xilinx. com/support/answers/53266.html. The syntax and basic steps of this script are shown in Figure 2.

Now the script can be run with these four parameters, resulting in the desired incremental compile and route out of this signal. This is repeated for the five bits of the state machine and for the acknowledge signal as follows:

| Net prior to OBUF | Pin | I/O Std  | Chosen output name |

|-------------------|-----|----------|--------------------|

| ack_orig          | L21 | LVCMOS18 | ack_routeout       |

| State0_orig       | P22 | LVCMOS18 | state0_routeout    |

| State1_orig       | M21 | LVCMOS18 | state1_routeout    |

| State2_orig       | M22 | LVCMOS18 | state2_routeout    |

| State3_orig       | J18 | LVCMOS18 | state3_routeout    |

| State4_orig       | K18 | LVCMOS18 | state4_routeout    |

| timeout_orig      | L22 | LVCMOS18 | timeout_routeout   |

#### Logic Analyzer Setup

The logic analyzer is then set up for measurements. The first step is to define "labels" for the five bit state machine, the acknowledge signal, and the timeout signal, where logic analyzer channels are assigned to each of these labels. The threshold level is set to a value at the midpoint of the LVCMOS18 logic level. And sampling is chosen for "State" mode capture so that sample points are taken, synchronous with the clock of the DUT. This provides a functional capture with the very deep memory of the logic analyzer. A trigger is set for the rising edge of the timeout flag, which is suspected to be asserted since the system is failing. The logic analyzer is run, it does trigger on the timeout flag, and by right clicking on the screen, and selecting "Zoom Out

| HE to HE - 40 mi |                                          |      |                 |                    |                                                                                                                 |                       |

|------------------|------------------------------------------|------|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|

|                  |                                          |      |                 |                    |                                                                                                                 |                       |

|                  | 12 172 Delay -531.961                    |      | l:              |                    |                                                                                                                 |                       |

| Butteriel        | Segre Tropper -54                        | 4 ve | a 638 un 434 un | -832 vie - 630 vie | 42514 - 42514                                                                                                   | 629 se -622 se -620 s |

| time             |                                          |      |                 |                    |                                                                                                                 | 111111111111          |

| @ E state        | - 1 20                                   | -18  | 1014            | K inter            | WatterAck                                                                                                       | Waltbrack             |

| ED-E state       | - 3 × B                                  |      | ( at            | (                  | X 10                                                                                                            | 10 10                 |

| E etate(0)       | X =                                      | 1    | 1 to            | 1.000              | a                                                                                                               | 0                     |

| -E state(1)      | × *                                      | 1    |                 |                    | ä                                                                                                               | 0                     |

|                  | X *                                      | 1    |                 | 1.00               | d diama dia diama dia | - ¢                   |

| E-weith          | X =                                      | 12   | 0               |                    | 0                                                                                                               | .0 (B                 |

| \$ state(4)      | X *                                      | N:   |                 | 0                  |                                                                                                                 |                       |

| Bas              | × *                                      | 0    | 8               |                    |                                                                                                                 |                       |

| Etmeout .        | 5 1                                      |      |                 | _                  | <u></u>                                                                                                         |                       |

| 6                |                                          |      | A .             | A I                |                                                                                                                 |                       |

|                  |                                          |      | 1 C C           | F .                | ò                                                                                                               |                       |

|                  |                                          |      |                 |                    | 1                                                                                                               |                       |

| •1               | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |      |                 |                    |                                                                                                                 |                       |

Figure 3. View of missing acknowledge after two cycles of the state machine

Full", a flurry of activity is seen around 500 µs prior to the timeout flag rising edge trigger point.

By zooming into this flurry of activity, it can be seen in Figure 3 that for a couple cycles of the state machine, an acknowledge bit was returned, but then on a third round no acknowledge ever comes.

By zooming in once again in the vicinity of the missing acknowledge signal, the detailed steps of the one-hot state machine can be seen in Figure 4, highlighted with a red box.

The sequence is correct for the state machine leading up to the "Wait for Ack" state.

Idle -> Start -> Addr -> Data -> Wait for Ack

The external logic analyzer, with its state capture of the routed out internal FPGA nets. validated the correct basic state machine functionality. But it hasn't yet revealed a root cause of failure. So the next step

toward finding the root cause of failure is to move the probe points to the external FPGA signals that are part of the real design, and observe them with a deep memory, high-speed timing capture.

#### Probing Critical, "Real" FPGA **External Signals in the Design**

Probing the FPGA external I/O signals that are part of the real design can be a challenge. There has to be some kind of access to the signals in order to probe them. One approach, when laying out the board, is to route the most critical signals through a probing footprint just in case there is a need to probe the signals later. It can also

-Catabell -Elisawers -E state(2)

-Elatere(3) LE man [4]

Ward

Back

## **Alternate Trigger Technique for When There Is No** "Timeout" Signal Available Finally, it is important to know how to set up complex .(#1× DEES HAAN NTH QQ \* DEE B atta affa Delay -528.404507 us B H AL T 28 H ः। = =

ŝ

**EECatalog** SPECIAL FEATURE

be helpful to make sure there is an access to vias under the FPGA for such critical signals. Logic analyzer probes can be soldered onto these vias if necessary.

Low-cost high performance portable logic analyzers now offer 5 GHz timing capture with deep memory, so it is possible to look at signals, like those in this design, and sort out functional versus timing issues. Such timing measurements don't replace the timing accuracy, or signal integrity view of signals provided by an oscilloscope measurement, but they do allow access to and viewing of many signals at one time. The logic analyzer set up is similar to that used before, however one major difference is that it is set to the "Timing" capture mode, and different logic analyzer channels are assigned to

the bus and signal names --- this time with the channels that are probing the real, external FPGA external signals, "ack", "state[5]" and "timeout". Also, with a 5 GHz timing capture, very deep memory is required to look back in time for the root cause of failure. In this case, 4M samples depth is chosen.

Through a similar process as before, and ultimately zooming in to that state machine burst where an acknowledge never comes back, a different kind of view is seen in Figure 5 where a basic timing issue between clock and state machine data is identified. The clock rising edge is not centered on the state machine data.

triggers when debugging and validating such logic designs. Here, conveniently, there was a timeout flag that could be probed, either internally or externally, and with deep

Figure 4. View of state machine functional sequence just prior to missing "ack"

## **EECatalog** SPECIAL FEATURE

|                 | Concession of Street, St |          | -           | -     |           | 2.   17n | 23     | 11 12 13 | 8, 8,            | • •   | 77        | 19.9      |   | ф II    | -0 III  | _          |

|-----------------|------------------------------------------------------------------------------------------------------------------|----------|-------------|-------|-----------|----------|--------|----------|------------------|-------|-----------|-----------|---|---------|---------|------------|

| ME to ME = -400 | ps M3 to M                                                                                                       | *-3      | 2rs 10 to   |       | 63.6 ms   |          |        |          |                  |       |           |           |   |         |         |            |

| Scale 1.76 rs/  | dv 🔳 🖽                                                                                                           | 1.<br>1. | Delay       | -270. | 356698 us |          | L T    | 21. H    | 1                |       |           |           |   |         |         |            |

| Bus/Signal      | Simple Tripp                                                                                                     | er.      |             |       | 63738 us  | .270     | 360218 |          | -270.35689       | Gus 1 | -270.3    | 152178 un |   | 270.349 |         | 1.1.1.1    |

| 2] timeout      |                                                                                                                  |          |             |       |           |          |        |          | 0                |       |           |           |   |         |         |            |

| EAck            | ×                                                                                                                | #        |             |       |           |          |        |          | 0                |       |           |           |   |         |         |            |

| Clock.          | x                                                                                                                | *        | 0           |       | 1         | 0        |        | 1        | 0                | 1     |           | 0         | 1 |         | 0       | 1          |

| 🖽 🖞 state       |                                                                                                                  |          | Idie        | ()E   | Start     |          | X      | Addr     |                  | D     | ata       | XC        |   | Wait    | for Ack |            |

| ⊡-∰state        | = = XX                                                                                                           |          | Ot          | KX C  | 02        | X        | ۶C     | 04       |                  |       | 6         | 11        |   |         | to      |            |

| -E state(0)     | ×                                                                                                                | æ        |             | Ĺ     |           |          |        | Plan     | e sey that again | 0     | de = 08 ( | 1.47 1942 |   |         |         |            |

| (1)             | ×                                                                                                                |          | D           |       | •         |          |        |          |                  |       | 0         |           |   |         |         |            |

| State(2)        | ×                                                                                                                | ¥        | -           |       | 0         |          |        |          |                  |       |           | 1         | 0 |         |         |            |

| atate(3)        | ×                                                                                                                | ¥.       |             |       |           | 0        |        |          |                  |       | ٩.        |           |   | 0       | i.      |            |

| state(4)        | ×                                                                                                                | 8        |             |       |           |          | 0      |          |                  |       |           |           |   |         | 1       |            |

| Time            |                                                                                                                  |          | 2 0 3668 us |       | 1111      |          | 111    | 1111     | 11               | 1111  |           |           |   |         | 111     | 270.3464 u |

| Clock (TZ)      |                                                                                                                  |          |             |       |           |          |        |          |                  |       |           |           |   |         |         | BARR D     |

| 🗈 🗐 state (77)  |                                                                                                                  |          |             |       |           |          |        |          |                  |       |           |           |   |         |         |            |

| 4 11 4          | 410.00                                                                                                           | 11       | 4           | 1     |           | 101      |        |          |                  |       |           | -         |   |         |         | •          |

Brad Frieden is a Product Planner for the Digital Debug Solutions Product Line at Keysight Technologies. He has been with Hewlett-Packard/ Agilent Technologies/Keysight

Technologies for 27 years, working in fiber optic test, pulse and data generator measurements, oscilloscopes, and logic/protocol analyzer applications. Brad graduated from Texas Tech University with a BSEE and from the University of Texas at Austin with a MSEE.

Figure 5. Identifying root cause of failure where clock rising edge not centered on state machine data

memory in the external logic analyzer, one could look far back in time to observe system operation and failure. But what about when there is no timeout signal? The answer is to create a timeout trigger, perhaps one of the most powerful debug triggers possible.

In this example, it would have been helpful to trigger the external logic analyzer if it ever saw the "Wait for Ack" state begin, but then not see the "ack" acknowledge signal returned within an expected time. Such a trigger can be set up as shown in Figure 6. The acknowledge should come within approximately 60 ns after the "Wait for Ack", so the timeout trigger is defined to trigger the external logic analyzer if more than 100 ns passes after "Wait for Ack" without an acknowledge signal coming.

#### Summary

Sometimes it's necessary to examine internal, "real" FPGA signals that are part of the system and find a way to probe those signals with an external logic analyzer. Through some basic steps, important internal nets in an FPGA can be routed out as debug signals for an external logic analyzer. State capture to view functionality of internal logic, combined with deep memory, can be very helpful to validate the design, or identify the functional problem. Timing capture, with high-speed sampling and deep memory, can also help in the search for the root cause of failure. In this case, 5 GHz timing capture, with 4M samples of depth, was able to view failing activity 500 µs prior to an external timeout flag being set. And then, the application of a user defined "timeout trigger", defined in the logic analyzer trigger interface, can be an important tool to zero in on the root cause of a failure.

Figure 6. Set up of a "Timeout" trigger to catch a missing acknowledge signal

**EECatalog** SPECIAL FEATURE

## A Few Questions on...FPGA-based Prototyping Software Tools

Did we say "a few"? Who's counting? We just know the topic range here spans everything from what designers ready to work on PCIe 4.0 projects should know to SoCs and design partitioning to whether FPGAs' reputation for being difficult to program is warranted.

#### By Anne Fisher, Managing Editor

Editor's note: Our thanks to Troy Scott, product marketing manager at Synopsys, who recently offered his insights on a number of questions. Scott is responsible for FPGA-based prototyping software tools at Synopsys. He has 20 years of experience in the EDA and semiconductor industries. His background includes HDL synthesis and simulation, SoC prototyping and IP evaluation and marketing.

**EECatalog:** What practices do you recommend for capitalizing on FPGAs' ability to address the challenges posed by concurrent hardware/software design?

**Troy Scott, Synopsys:** From an ASIC design perspective FPGAs are absolutely applied to help create a more parallel design process for hardware and software. High-performance FPGA-based prototypes make it feasible to boot an OS, develop drivers

and run a software stack. And, perhaps more important, do so with a minimum number of high-capacity FPGAs to keep prototype cost as low as possible, which is a very important consideration if the prototype will be duplicated throughout the organization.

Best practices to maximize the prototype ROI typically result from collaboration between ASIC designers, the FPGA-based prototyping specialists and the software teams who use the prototype. "Over-the-wall" RTL drops are a recipe for failure and schedule delays. Design For Prototyping (DFP) RTL coding standards maximize prototype performance and speed the schedule at which it can be brought-up. At the deployment phase the most efficient prototyping teams will work closely with and treat the software team as the internal customer. Tracking software alongside RTL changes will minimize confusion as the system is integrated. Some software routines may need to account for slower operation of the prototype versus ASIC silicon. Internal probe points relevant to the software team may need to be designed in to help during the debug phase. Rapid reset cycles designed into the prototype help improve turnaround time. All of these examples require

close collaboration between the prototyping team and the embedded software development team.

**EECatalog:** Your thoughts on some of the challenges to FPGA-based prototyping, beginning with design partitioning?

**Scott, Synopsys:** To achieve both rapid time to solution and highest performance you need super-fast partition software and a platform that can be tailored to the SoC needs. One example of this is what Synopsys calls the abstract partition flow with ProtoCompiler and HAPS-70. The combination of ProtoCompiler and HAPS-70 enables prototypers to quickly create an abstracted interconnect architecture representation, generate a partition solution, then incrementally customize the partition and the hardware based on the needs of the SoC.

A smart partition automation tool allows the prototyper to create an abstract representation of the interconnect between FPGAs. At this level of abstraction, there are no fixed traces between FPGAs nor exact connections, but rather a representation of possible I/O interconnections. From this vantage point, the prototyper can very quickly see the expected FPGA utilization and secondly, and most important, the signal-to-multiplexing ratio. A prototyping rule of thumb is: the higher the mux ratio the lower the system performance, and it's this performance that is the gating factor of overall performance in a prototype. Quick identification of bottlenecks and where to apply more physical I/O between FPGAs enables the prototyper to not only design an ideal partition scheme, but also accomplish the task quickly.

**EECatalog:** Long bring-up is another challenge.

**Scott, Synopsys:** The challenge of how to accelerate prototype bring-up remains a focus for commercial vendors of FPGA-based prototypes. FPGA logic synthesis tailored for the prototyping task, partitioning and sophisticated signal sharing schemes to maximize performance will help shorten project schedules. But even with strong

## **<u>EECatalog</u>** SPECIAL FEATURE

product roadmaps and innovations in prototyping EDA software, the most successful design teams have embraced Design for Prototyping (DFP) best practices throughout the ASIC development process. DFP adoption may require a culture change as profound to development teams as was the industry shift from an emphasis on ASIC design productivity to ASIC verification productivity. In the next two years those ASIC design teams that anticipate design best practices for both ASIC and FPGA targets will benefit most from FPGA-based prototyping methods.

**EECatalog:** What's the latest on avoiding debugging complications?

**Scott, Synopsys:** The reason debug of an FPGA-based prototype is complicated is due to at least two conditions prototyping specialists face. One, design modifications to some extent are required to fit into the architectural constraints of a multi-FPGA system where ASIC signal interconnect, reset and clocking, memory blocks, ASIC I/Os, DFT circuits, etc. may require careful replacement and budgeting by prototyping specialists. Functional equivalence checks either through a simulation regimen or formal methods help to confirm that these changes have not changed the logic of the initial RTL drop. Innovations in prototyping automation tools help accelerate this process with schemes to model these changes.

The second reason is that once the prototyping system is operational the very nature of an FPGA-based prototype may expose flaws that simulation and emulation will not expose during the RTL and IP verification phases. Because the prototype is running at multi-megahertz it makes software-driven test and real-world interface testing feasible. These tests are going to uncover problems, or perhaps better stated as "incompatibilities" that require driver and/or RTL changes. In 2015 debugging features tailored for prototyping systems provide high-capacity storage options to allow for long periods of evaluation with schemes to adjust instrumentation that minimizes disruption to the prototype implementation.

Success in prototyping is largely measured by how soon an operational prototype can be deployed. The faster the debug phase can be accomplished, the lower it will be on the prototyping community's list of priorities.

**EECatalog:** What are the top 5 things designers ready to work on the architecture of PCIe 4.0 projects should know?

#### Scott, Synopsys:

1. Keep your eye on the ball! Or in this case, the specification. The PCIe 4.0 specification draft 0.3 is out, draft 0.5 is expected around the end of 2014, and while most of the expected changes are electrical, there are some protocol changes too. Make sure your

FPGA vendor's SERDES is going to be able to meet PCIe 4.0 electrical requirements—many are extremely configurable, but the devil may be in the details as the spec finalizes.

- 2. Go big or go home! In order to keep to FPGA-friendly clock frequencies, datapaths will get very wide. That means things like 128-bit SERDES interfaces, internal datapaths, etc. Make sure your FPGAs have the capacity to handle the increased routing resources, which come with such large internal busses.

- 3. Feed the beast! Probably obvious, but if you're going to feed PCIe 4.0's 16GT/s data rate, you'll need more bandwidth in whatever your applications are doing.

- 4. Bring friends! Plan for early interoperability testing with other implementers. Even though FPGAs make logic changes "easy" it will be important to make sure your application will work with upcoming chipsets and other PCIe 4.0 devices until PCI-SIG compliance testing becomes available. Keep an eye out for early opportunities to participate in PCI-SIG "FYI" testing.

- 5. Never walk alone! Work with an IP vendor who is committed to closely tracking the PCIe 4.0 specification, is involved in the development of both the specification itself and the associated compliance tests and has PCIe 4.0 code available.

**EECatalog:** Name 5 factors that have to be involved in winning business in a case where the customer had previously designed FPGA boards in-house for an ultra-low latency application, e.g., time-sensitive financial trades.

#### Scott, Synopsys:

- 1. Shorter lead time for the prototype availability

- 2. Superior prototype flexibility across validation scenarios

- 3. Superior quality compared to low-volume system builds

- 4. Software tools tailored for system with a deep feature set for bring-up automation and debug

- 5. Support for advanced prototyping scenarios via workstation connectivity

**EECatalog:** As FPGAs get used more frequently as co-processors, accelerators, or offload engines, what are the design challenges of writing optimized code to take advantage of this/these capability (ies)?

**Scott, Synopsys:** FPGAs are becoming more powerful and power efficient over time. This is enabling more widespread use in new applications. In addition FPGAs bring to the table a very high level of processing power that can significantly speed up algorithms. In the past FPGA designers would have needed to work at optimizing their code for a specific device. However, today, synthesis tools are on the market that enable techniques developers can utilize to gain a high level of optimization for area and performance in co-processing/acceleration applications

**EECatalog:** Please comment on OpenCL and other high-level languages applied to FPGA designs.

**Scott, Synopsys:** Over the years there have been many tools developed to help make the transition from higher-level languages to the lower-level RTL, but there still remains a need for some FPGA understanding. OpenCL has been a standard in the industry for a while, and recently

both Altera and Xilinx have made announcements around OpenCL. The goal is to abstract away the traditional FPGA development flows and lower the barrier to entry for the masses. It is a difficult question to answer so broadly, but FPGAs are already being adopted more widely and in part due to the higher-level languages and abstraction they provide.

Anne Fisher is managing editor of EECatalog. com. Her experience includes being managing editor, Communications Group, at OpenSystems Media, where she had the opportunity to cover a wide range of embedded solutions in the PICMG ecosystem as well as other technologies. Anne

enjoys bringing embedded designers and developers solutions to technology challenges as described by their peers as well as insight and analysis from industry leaders. She can be reached at afisher@ extensionmedia.com

## For the Advanced SoC Design Community

- News

- Technology Trends

- Blogs

- System Design Engineering Online Community

- Semiconductor Manufacturing and Design Community

- Videos

- Expert Insight

- Technical Papers

- RF & Microwave Systems

- Resource Guides

- Valuable Newsletters

## ChipDesignMag.com

# Don't Swallow the Camel and Other FPGA Wisdom

For FPGAs, higher gate counts and fabric speeds are not all that is new.

#### By Anne Fisher, Managing Editor

Jeff Milrod, BittWare president and CEO, does not want FPGA developers to get indigestion. To prevent this problem, he recommends the three-step process you'll read about here.

**EECatalog:** Design partitioning, long bring-up, debug difficulties, performance and reusability have been named as challenges to FPGA-based prototyping. Which of these do you think has the best chance of being addressed successfully in the next couple of years, and how do you define success?

**Jeff Milrod, BittWare:** For those who either need to use, or insist on using, HDL coding, all of those are quite

challenging and will continue to be that is simply the nature of any low-level coding. However, great advancements have been made with respect to the tools, and these advancements will continue, albeit incrementally. Maybe the biggest thing that

has helped these challenges, and will continue to help, is the fact that gate counts and fabric speeds have increased tremendously, thus requiring much less code optimization and tuning.

Previous efforts at abstracting away these challenges have been underwhelming at best and have generally only been helpful for developing code components rather than complete projects. However, there are some major paradigms shifts occurring now involving high-level coding abstractions that look like they could blow this problem away. For example, Altera's SDK for OpenCL enables highlevel coding practices to implement complete complex FPGA algorithms. This does require a one-time, low-level 'boardsupport package' (BSP) to be built. But once that is done, the coding of the FPGA becomes essentially a software task with the associated ease-of-use and reusability.

**EECatalog:** Is there really any practical difference between volatile and nonvolatile FPGAs, in real practice?

**Milrod, BittWare:** The only conceptual difference I'm aware of would be boot time. Nonvolatile FPGAs are instant-on, which can be important for some applications. In practice, volatile FPGAs are so much bigger and faster that they are highly advantageous for all other applications.

On many of our boards, we use an instant-on nonvolatile FPGA to boot the board and the bigger volatile FPGA for all other FPGA-based tasks.

**EECatalog:** What's the focus of your buy versus build discussions?

Milrod, BittWare: We focus our buy vs. build discussions on low-level board support IP, SW and drivers, technical support, life cycle management, design and manufacturing quality, and technology refresh (i.e., the fact that we will continue to design similar COTS boards with future generations of FPGAs that customers will be able to easily upgrade to). The "build" option isn't simply a matter of designing and building a board (no easy task on its own). It also includes everything mentioned prior-highand low-level software, technical difficulties, possibly manufacturing issues, as well as having to deal with part sourcing, part EOL and next-generation designs. Unless a company has the capabilities to deal with all of these tasks, the decision to buy is many times the best decision not only from a cost standpoint, but also when looking at time-tomarket.

**EECatalog:** As FPGAs get used more frequently as co-processors, accelerators, or offload engines, what are the design challenges of writing optimized code to take advantage of this/these capability (ies)?

**Milrod, BittWare:** The concept of FPGA optimization is rather complicated. Unlike SW, it is not about number of cycles, nor can it be thought of as a single threaded problem. While maximum toggle rate frequency (often called Fmax) can be important for some applications, it alone doesn't necessarily indicate the FPGA performance as it neglects the inherent parallelism of FPGAs. Bus widths can be doubled, quadrupled, etc... and whole algorithmic streams can be run simultaneously, thereby resulting in far greater performance increases than improving Fmax alone. Improving performance via parallelisms often requires focusing on the FPGA's resource allocation and optimization so that buses can be widened and streams can run in parallel without overflowing the part.

### **<u>EECatalog</u>** SPECIAL FEATURE

However, it is often most important to focus on optimizing for human resources – time-to-market can often be more important than that last 10% optimization. Similarly, designing modular and structured function blocks might not yield the most optimal implementation, but can result in huge performance advantages down the road by allowing code reuse and reducing debug times. In fact, I now believe that for most applications the performance advantages of using FPGAs are compelling enough that optimization of the FPGA implementation is often not essential - but getting the system deployed is. To that end, we focus a great deal of our efforts towards getting our customers up and running quickly using our FPGA Developers Kit (FDK), board support packages, example projects, and pro-active support. For any given application, our function blocks and interfaces might not be completely optimal – but they work out of the box, and enable much quicker development and deployment.

Developers often "strain at gnats and swallow camels," which can cause huge and often unnecessary delays. FPGA development and optimization is better served by first getting the basic project functioning, then identifying bottlenecks and targeting any required optimizations with a more focused approach.

**EECatalog:** Despite their widespread use, FPGAs are inherently difficult to program due to their low-level (RTL/HDL) languages. C-to-gates, OpenCL, and other high-level languages seek to simplify the job. Do they work? Will FPGAs ever be "easy" and become a tool of the design "masses"? Please comment on OpenCL and other high-level languages applied to FPGA designs.

**Milrod, BittWare:** Except for what I call the "last micron" problem, for the most part the "guts" of FPGAs have actually been fairly easy to program for quite a while. Both major FPGA vendors, and even 3rd parties, have long had pretty good tools for high-level coding of algorithms. For example, it doesn't get much easier to implement complex processing than clicking a button to compile a Matlab/ Simulink model to RTL/HDL, and that's been widely available for many years now.

However, like the "last mile" problem of getting highspeed network backbones connected to every house, the key challenge in FPGA design is getting that algorithm developed in Matlab to connect to off-chip peripherals such as off-chip memory, network interfaces, and PCIe ports. Since those don't exist on an FPGA, they need to be developed. Even with those in place, it becomes an iterative problem as the peripheral interfaces need to then be integrated with the algorithm and, since its actually programming hardware rather than coding software, the timing must be "closed." I believe that this 'last micron' problem—the peripheral implementation and integration—generally takes at least as long as the algorithm development, and often far longer.

Great strides have been, and are being made, to generally simplify these peripheral implementation and integration challenges with better tools such as Xilinx's IP Integrator and Altera's Qsys. Altera's SDK for OpenCL takes a more extreme approach: it first requires the development of a locked down, low-level hardware peripheral implementation, called a Board Support Package (BSP), that interfaces to the compiler. The development of the BSP requires special expertise and is quite hardware centric, thus we provide several standard versions to our customers along with optional customization services. Once the BSP is implemented, the OpenCL compiler then completely abstracts the FPGA, enabling it to be coded like a processor and allowing the "masses" to have "easy" access to performance of FPGAs.

Anne Fisher is managing editor of EECatalog. com. Her experience includes being managing editor, Communications Group, at OpenSystems Media, where she had the opportunity to cover a wide range of embedded solutions in the PICMG ecosystem as well as other technologies. Anne

enjoys bringing embedded designers and developers solutions to technology challenges as described by their peers as well as insight and analysis from industry leaders. She can be reached at afisher@ extensionmedia.com

## **The FPGA Advantage for Beamforming**

The argument for adaptive beamforming that relies on FPGAs to make mil aero and 4G applications possible—realizing "look ma!" power reductions in the process.

#### By Jason Cella, 4DSP, LLC

Beamforming can be switched or adaptive. In switched beamforming, a mobile telecommunications base station, for instance, chooses from a predefined selection of beams that each target a specific direction based on the strength of the received signal. As a user moves in relation to the array of antennas, the signal is switched to other elements in the array that are better positioned to provide a stronger signal in a particular direction. Adaptive beamforming differs from switched beamforming in that adaptive beamforming employs real-time computations that make it possible for the base station to transmit more focused beams in the direction of target users—at the same time reducing output in other directions to substantially lower interference between elements.

#### A Means to Avoid Overburdening DSPs

Adaptive beamforming designs call for very high processing bandwidth—billions of multiply and accumulate operations must be performed each second—a pace that makes it essential for receiving systems to suppress noise sources and interference. Meanwhile, real-time directional control of each element in the antenna array must be maintained. To accomplish this, it is necessary to digitally process the signal received by each antenna element individually and simultaneously using element-level processing. Because of the heavy computational load required, traditional CPUs and DSPs can be rapidly overburdened in adaptive beamforming applications. FPGAs, however, bring to this heavy computational task the needed features and tools, including embedded DSP blocks, parallel processing architecture, and enhanced memory capabilities.

The ever-growing global demand for mobile broadband data and voice services continually drives wireless network operators to expand and upgrade their networks in order to deliver more capacity. Operators are simultaneously trying to maximize the number of users that each wireless base station can support to lower their infrastructure costs while maintaining an attractive price point for subscribers.

Complicating this effort is the limit on the amount of available wireless spectrum. The limit means increased traffic generates more interference, and call quality suffers partly because of the limitations of antenna technology. One approach is to use omnidirectional antennas to transmit and receive on cellular towers. However, this traditional method, in which the antennas act as transducers, converting electromagnetic energy into electrical energy, is not efficient. Another drawback to this method is that it suffers from a high degree of interference that diminishes overall connectivity due to the multiplicity of signals present at a single tower.

#### **Brainier Antennas**

Using directional sector antennas grouped together on the same tower can mitigate this interference. Telecommunications networks are increasingly using these adaptive array antennas, or smart antennas, to improve wireless connection quality and boost overall capacity. This is achieved with beamforming techniques that direct beams from the base station at individual users through the use of advanced digital signal processing. Beamforming adjusts the power and phase of every incoming and outgoing signal to create a beam that travels in a specific direction while decreasing non-essential output. This reduces the amount of

Figure 1. One example of an FPGA card that designers can now opt to employ for applications that benefit from a close integration of FPGA cards and high-performance analog transceivers is a Xilinx Virtex-7 based card from 4DSP, the FM788.

## **EECatalog** SPECIAL FEATURE

interference that individual signals inflict upon one another and increases the quality of all connections.

The emergence of innovative adaptive beamforming algorithms has led to an increase in the use of floating-point arithmetic in signal processing to minimize interference and boosted radar capacity by enabling real-time tracking of targets. This is achieved by creating multiple spot beams simultaneously using algorithms such as QR decomposition (QRD) and weight back substitution (WBS). These algorithms facilitate the adaptive formation of beams while reducing noise and interference, but they require a large number of floating point operations per second.

Because of the size, weight and power limitations of many radar systems, the use of legacy CPU or GPU options is not the best approach because of the increased amount of hardware required to perform the floating-point calculations. Demanding more memory, power and space, the use of multiple CPUs has a major impact on radar system design. Higher cost, more complex system design, and extended integration time also come into play. A CPUbased design is further constrained by a limited choice of memory and interface options.

As compared to CPU and GPU options in radar systems employing advanced digital beamforming techniques, FPGAs lower cost and complexity, while shrinking power consumption and shortening time to market. With their ability to process highly parallel floating-point operations in adaptive beamforming applications, FPGAs can increase algorithmic performance while dramatically reducing power consumption.

#### **Single Device Efficiency**

An FPGA is also a much more efficient choice because a single device is used to receive and process large amounts of data over such I/O standards as PCIe and Serial RapidIO from signals captured by each element in an antenna array. Able to carry out higher performance processing, such a system also eliminates the need for numerous, power-hungry, multicore CPU boards housed in a VPX chassis requiring more than 1000 watts of power. A streamlined, single-FPGA design also benefits from external memory and other additional functions present on a single board that draws less than 80 watts.

Although adaptive beamforming and smart antennas have figured in defense applications for a number of years, it's only recently that commercial cellular networks have begun to use this technology extensively. At the time of the emergence of low-cost FPGAs and DSPs, 3G mobile networks began capitalizing on the advantages of adaptive beamforming, a technology that is now seeing broad acceptance in growing 4G networks. The use of high-performance analog transceivers that are tightly coupled with FPGA cards such as 4DSP's Xilinx Virtex-7-based FM788 (Figure 1) opens up new opportunities for hardware and firmware designers to hone beamforming techniques for in commercial as well as defense use.

Jason Cella is a technical writer for 4DSP, LLC.

## FPGA and PLD Solutions ONLINE