# **CONTENTS**

- 1. INTRODUCTION

- 2. NUMBER SYSTEM

- 3. CODE CONVERSION

- 4. BINARY CODES

- 5. BASIC LOGIC FUNCTIONS AND GATES

- 6. COMBINATIONAL LOGIC

- 7. SEQUENTIAL CIRCUITS

- 8. LATCH AND FLIP-FLOPS

# Introduction

The quantities that are to be measured, monitored, recorded, processed and controlled are analog and digital, depending on the type of system used. It is important when dealing with various quantities that we be able to represent their values efficiently and accurately. There are basically two ways of representing the numerical value of quantities: analog and digital.

### **Analog Representation**

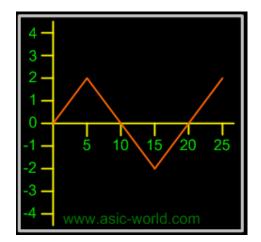

Systems which are capable of processing a continuous range of values varying with respect to time are called analog systems. In analog representation a quantity is represented by a voltage, current, or meter movement that is proportional to the value of that quantity. Analog quantities such as those cited above have an important characteristic: they can vary over a continuous range of values.

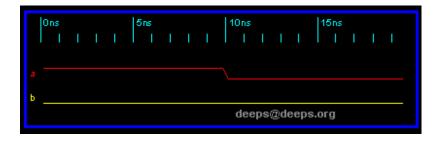

#### **Diagram of analog voltage vs time**

## **Digital Representation**

Systems which process discrete values are called digital systems. In digital representation the quantities are represented not by proportional quantities but by symbols called digits. As an example, consider the digital watch, which provides the time of the day in the form of decimal digits representing hours and minutes (and sometimes seconds). As we know, time of day changes continuously, but the digital watch reading does not change continuously; rather, it changes in steps of one per minute (or per second). In other words, time of day digital representation changes in discrete steps, as compared to the representation of time provided by an analog watch, where the dial reading changes continuously.

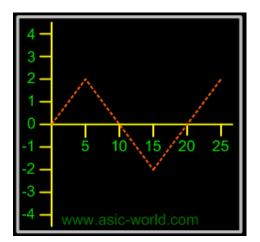

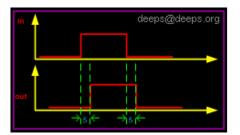

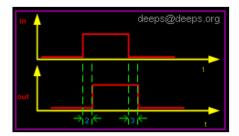

Below is a diagram of digital voltage vs time: here input voltage changes from +4 Volts to -4 Volts; it can be converted to digital form by Analog to Digital converters (ADC). An ADC converts continuous signals into samples per second. Well, this is an entirely different theory.

#### **Diagram of Digital voltage vs time**

The major difference between analog and digital quantities, then, can be stated simply as follows:

Analog = continuous

• Digital = discrete (step by step)

## **Advantages of Digital Techniques**

- Easier to design. Exact values of voltage or current are not important, only the range (HIGH or LOW) in which they fall.

- Information storage is easy.

- Accuracy and precision are greater.

- Operations can be programmed. Analog systems can also be programmed, but the available operations variety and complexity is severely limited.

- Digital circuits are less affected by noise, as long as the noise is not large enough to prevent us from distinguishing HIGH from LOW (we discuss this in detail in an advanced digital tutorial section).

- More digital circuitry can be fabricated on IC chips.

### **Limitations of Digital Techniques**

Most physical quantities in real world are analog in nature, and these quantities are often the inputs and outputs that are being monitored, operated on, and controlled by a system. Thus conversion to digital format and re-conversion to analog format is needed.

# **Numbering System**

Many number systems are in use in digital technology. The most common are the decimal, binary, octal, and hexadecimal systems. The decimal system is clearly the most familiar to us because it is a tool that we use every day. Examining some of its characteristics will help us to better understand the other systems. In the next few pages we shall introduce four numerical representation systems that are used in the digital system. There are other systems, which we will look at briefly.

- Decimal

- Binary

- Octal

- Hexadecimal

### **Decimal System**

The decimal system is composed of 10 numerals or symbols. These 10 symbols are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Using these symbols as digits of a number, we can express any quantity.

The decimal system is also called the base-10 system because it has 10 digits.

#### **Binary System**

In the binary system, there are only two symbols or possible digit values, 0 and 1. This base-2 system can be used to represent any quantity that can be represented in decimal or other base system.

# **Octal System**

The octal number system has a base of eight, meaning that it has eight possible digits: 0,1,2,3,4,5,6,7.

# Hexadecimal System

The hexadecimal system uses base 16. Thus, it has 16 possible digit symbols. It uses the digits 0 through 9 plus the letters A, B, C, D, E, and F as the 16 digit symbols.

# **Code Conversion**

Converting from one code form to another code form is called code conversion, like converting from binary to decimal or converting from hexadecimal to decimal.

## **Binary-To-Decimal Conversion**

Any binary number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

| Binary                        | Decimal          |

|-------------------------------|------------------|

| 11011 <sub>2</sub>            |                  |

| $2^4 + 2^3 + 0^1 + 2^1 + 2^0$ | =16+8+0+2+1      |

| Result                        | 27 <sub>10</sub> |

## **Decimal-To-Binary Conversion**

Convert  $25_{10}$  to binary

| Division | Remainder            | Binary                    |

|----------|----------------------|---------------------------|

| 25/2     | = 12+ remainder of 1 | 1 (Least Significant Bit) |

| 12/2     | = 6 + remainder of 0 | 0                         |

| 6/2      | = 3 + remainder of 0 | 0                         |

| 3/2      | = 1 + remainder of 1 | 1                         |

| 1/2      | = 0 + remainder of 1 | 1 (Most Significant Bit)  |

| Result   | 25 <sub>10</sub>     | = 11001 <sub>2</sub>      |

## **Binary-To-Octal / Octal-To-Binary Conversion**

| Octal Digit | 0   | 1   | 2   | 3   | <b>4</b> | 5   | 6   | 7   |

|-------------|-----|-----|-----|-----|----------|-----|-----|-----|

| Binary      | 000 | 001 | 010 | 011 | 100      | 101 | 110 | 111 |

| Equivalent  | 000 | 001 | 010 | 011 | 100      | 101 | 110 |     |

Each Octal digit is represented by three binary digits.

## Example:

$100\ 111\ 010_2 = (100)\ (111)\ (010)_2 = 4\ 7\ 2_8$

## Binary-To-Hexadecimal /Hexadecimal-To-Binary Conversion

| Hexadecimal Digit | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|-------------------|------|------|------|------|------|------|------|------|

| Binary Equivalent | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

| al Digit          | Hexadecim | 8        | 9 | A        | B        | С        | D        | £        | F        |

|-------------------|-----------|----------|---|----------|----------|----------|----------|----------|----------|

| Binary Equivalent |           | 100<br>0 |   | 101<br>0 | 101<br>1 | 110<br>0 | 110<br>1 | 111<br>0 | 111<br>1 |

Each Hexadecimal digit is represented by four bits of binary digit.

# Example:

1011 0010 1111<sub>2</sub> = (1011) (0010) (1111)<sub>2</sub> = B 2  $F_{16}$

### **Decimal to octal**

This method uses repeated division by 8.

**Example**: Convert 177<sub>10</sub> to octal and binary

| Division | Result               | Binary                    |

|----------|----------------------|---------------------------|

| 177/8    | = 22+ remainder of 1 | 1 (Least Significant Bit) |

| 22/ 8    | = 2 + remainder of 6 | 6                         |

| 2 / 8    | = 0 + remainder of 2 | 2 (Most Significant Bit)  |

| Result   | 177 <sub>10</sub>    | = 261 <sub>8</sub>        |

| Binary   |                      | $= 010110001_2$           |

# Hexadecimal to Decimal/Decimal to Hexadecimal Conversion

Example:

$$2AF_{16} = 2 x (16^2) + 10 x (16^1) + 15 x (16^0) = 687_{10}$$

**Example**: convert 378<sub>10</sub> to hexadecimal and binary:

| Division | Result                | Hexadecimal                   |

|----------|-----------------------|-------------------------------|

| 378/16   | = 23+ remainder of 10 | A (Least Significant Bit)23   |

| 23/16    | = 1 + remainder of 7  | 7                             |

| 1/16     | = 0 + remainder of 1  | 1 (Most Significant Bit)      |

| Result   | 378 <sub>10</sub>     | $= 17A_{16}$                  |

| Binary   |                       | = 0001 0111 1010 <sub>2</sub> |

### **Octal-To-Hexadecimal Hexadecimal-To-Octal Conversion**

- Convert Octal (Hexadecimal) to Binary first.

- Regroup the binary number by three bits per group starting from LSB if Octal is required.

- Regroup the binary number by four bits per group starting from LSB if Hexadecimal is required.

## Example:

Convert  $5A8_{16}$  to Octal.

| Hexadecimal | Binary/Octal                             |

|-------------|------------------------------------------|

| 5A816       | = <b>0101</b> 1010 <b>1000</b> (Binary)  |

|             | = <b>010</b> 110 <b>101</b> 000 (Binary) |

| Result      | = 2650 (Octal)                           |

# **Binary Codes**

Binary codes are codes which are represented in binary system with modification from the original ones. Below we will be seeing the following:

- Weighted Binary Systems

- Non Weighted Codes

## Weighted Binary Systems

Weighted binary codes are those which obey the positional weighting principles, each position of the number represents a specific weight. The binary counting sequence is an example

| Decimal | 8421 | 2421 | 5211 | Excess-3 |

|---------|------|------|------|----------|

| 0       | 0000 | 0000 | 0000 | 0011     |

| 1       | 0001 | 0001 | 0001 | 0100     |

| 2       | 0010 | 0010 | 0011 | 0101     |

| 3       | 0011 | 0011 | 0101 | 0110     |

| 4       | 0100 | 0100 | 0111 | 0111     |

| 5       | 0101 | 1011 | 1000 | 1000     |

| 6       | 0110 | 1100 | 1010 | 1001     |

| 7       | 0111 | 1101 | 1100 | 1010     |

| 8       | 1000 | 1110 | 1110 | 1011     |

| 9       | 1001 | 1111 | 1111 | 1100     |

#### 8421 Code/BCD Code

The BCD (Binary Coded Decimal) is a straight assignment of the binary equivalent. It is possible to assign weights to the binary bits according to their positions. The weights in the BCD code are 8,4,2,1.

**Example:** The bit assignment 1001 can be seen by its weights to represent the decimal 9 because:

1x8+0x4+0x2+1x1 = 9

### 2421 Code

This is a weighted code; its weights are 2, 4, 2 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 2 + 4 + 2 + 1 = 9. Hence the 2421 code represents the decimal numbers from 0 to 9.

#### 5211 Code

This is a weighted code; its weights are 5, 2, 1 and 1. A decimal number is represented in 4-bit form and the total four bits weight is 5 + 2 + 1 + 1 = 9. Hence the 5211 code represents the decimal numbers from 0 to 9.

#### **Reflective Code**

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

#### **Sequential Codes**

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

#### **Non Weighted Codes**

Non weighted codes are codes that are not positionally weighted. That is, each position within the binary number is not assigned a fixed value.

#### **Excess-3** Code

Excess-3 is a non weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

**Example:** 1000 of 8421 = 1011 in Excess-3

#### **Gray Code**

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a unit-distance code. In digital Gray code has got a special place.

| Decimal Number | Binary Code | Gray Code |

|----------------|-------------|-----------|

| 0              | 0000        | 0000      |

| 1              | 0001        | 0001      |

| 2              | 0010        | 0011      |

| 3              | 0011        | 0010      |

| 4              | 0100        | 0110      |

| 5              | 0101        | 0111      |

| 6              | 0110        | 0101      |

| 7              | 0111        | 0100      |

| 8              | 1000        | 1100      |

| 9              | 1001        | 1101      |

| 10             | 1010        | 1111      |

| 11             | 1011        | 1110      |

| 12             | 1100        | 1010      |

| 13             | 1101        | 1011      |

| 14             | 1110        | 1001      |

| 15             | 1111        | 1000      |

## **Binary to Gray Conversion**

- Gray Code MSB is binary code MSB.

- Gray Code MSB-1 is the XOR of binary code MSB and MSB-1.

- MSB-2 bit of gray code is XOR of MSB-1 and MSB-2 bit of binary code.

- MSB-N bit of gray code is XOR of MSB-N-1 and MSB-N bit of binary code.

# **Basic Logical Functions and Gates**

While each logical element or condition must always have a logic value of either "0" or "1", we also need to have ways to combine different logical signals or conditions to provide a logical result.

For example, consider the logical statement: "If I move the switch on the wall up, the light will turn on." At first glance, this seems to be a correct statement. However, if we look at a few other factors, we realize that there's more to it than this. In this example, a more complete statement would be: "If I move the switch on the wall up and the light bulb is good and the power is on, the light will turn on."

If we look at these two statements as logical expressions and use logical terminology, we can reduce the first statement to:

#### Light = Switch

This means nothing more than that the light will follow the action of the switch, so that when the switch is up/on/true/1 the light will also be on/true/1. Conversely, if the switch is own/off/false/0 the light will also be off/false/0.Looking at the second version of the statement, we have a slightly more complex expression:

#### Light = Switch and Bulb and Power

Normally, we use symbols rather than words to designate the and function that we're using to combine the separate variables of Switch, Bulb, and Power in this expression. The symbol normally used is a dot, which is the same symbol used for multiplication in some mathematical expressions. Using this symbol, our three-variable expression becomes:

#### Light = Switch •Bulb •Power

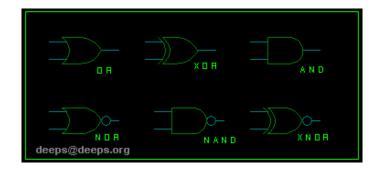

When we deal with logical circuits (as in computers), we not only need to deal with logical functions; we also need some special symbols to denote these functions in a logical diagram. There are three fundamental logical operations, from which all other functions, no matter how complex, can be derived. These functions are named and, or, and not.

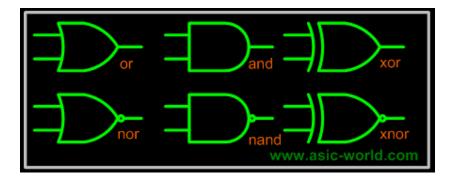

A logic gate is an electronic circuit/device which makes the logical decisions. To arrive at this decisions, the most common logic gates used are OR, AND, NOT, NAND, and NOR gates. The NAND and NOR gates are called universal gates. The exclusive-OR gate is another logic gate which can be constructed using AND, OR and NOT gate.

# **AND Gate**

The AND gate performs logical multiplication, commonly known as AND function. The AND gate has two or more inputs and single output. The output of AND gate is HIGH only when all its inputs are HIGH (i.e. even if one input is LOW, Output will be LOW).

If X and Y are two inputs, then output F can be represented mathematically as F = X.Y, Here dot (.) denotes the AND operation. Truth table and symbol of the AND gate is shown in the figure below.

### Symbol

### **Truth Table**

| X | Y | $\mathbf{F}=(\mathbf{X}.\mathbf{Y})$ |

|---|---|--------------------------------------|

| 0 | 0 | 0                                    |

| 0 | 1 | 0                                    |

| 1 | 0 | 0                                    |

| 1 | 1 | 1                                    |

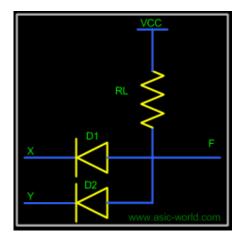

Two input AND gate using "diode-resistor" logic is shown in figure below, where X, Y are inputs and F is the output.

#### Circuit

If X = 0 and Y = 0, then both diodes D1 and D2 are forward biased and thus both diodes conduct and pull F low.

If X = 0 and Y = 1, D2 is reverse biased, thus does not conduct. But D1 is forward biased, thus conducts and thus pulls F low.

If X = 1 and Y = 0, D1 is reverse biased, thus does not conduct. But D2 is forward biased, thus conducts and thus pulls F low.

If X = 1 and Y = 1, then both diodes D1 and D2 are reverse biased and thus both the diodes are in cut-off and thus there is no drop in voltage at F. Thus F is HIGH.

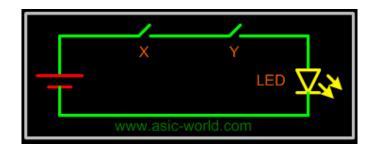

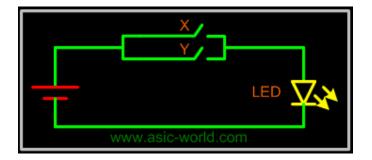

#### Switch Representation of AND Gate

In the figure below, X and Y are two switches which have been connected in series (or just cascaded) with the load LED and source battery. When both switches are closed, current flows to LED.

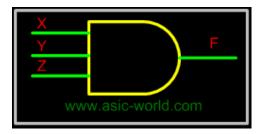

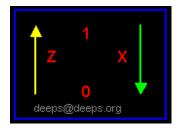

# Three Input AND gate

Since we have already seen how a AND gate works and I will just list the truth table of a 3 input AND gate. The figure below shows its symbol and truth table.

# Circuit

# **Truth Table**

| X | Y | Z | F=X.Y.Z |

|---|---|---|---------|

| 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 0       |

| 0 | 1 | 0 | 0       |

| 0 | 1 | 1 | 0       |

| 1 | 0 | 0 | 0       |

| 1 | 0 | 1 | 0       |

| 1 | 1 | 0 | 0       |

| 1 | 1 | 1 | 1       |

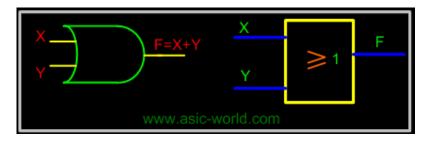

## **OR** Gate

The OR gate performs logical addition, commonly known as OR function. The OR gate has two or more inputs and single output. The output of OR gate is HIGH only when any one of its inputs are HIGH (i.e. even if one input is HIGH, Output will be HIGH).

If X and Y are two inputs, then output F can be represented mathematically as F = X+Y. Here plus sign (+) denotes the OR operation. Truth table and symbol of the OR gate is shown in the figure below.

Symbol

### **Truth Table**

| X | Y | $\mathbf{F} = (\mathbf{X} + \mathbf{Y})$ |

|---|---|------------------------------------------|

| 0 | 0 | 0                                        |

| 0 | 1 | 1                                        |

| 1 | 0 | 1                                        |

| 1 | 1 | 1                                        |

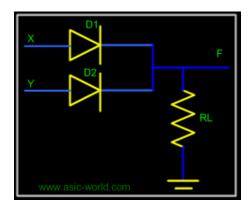

Two input OR gate using "diode-resistor" logic is shown in figure below, where X, Y are inputs and F is the output.

Circuit

If X = 0 and Y = 0, then both diodes D1 and D2 are reverse biased and thus both the diodes are in cut-off and thus F is low.

If X = 0 and Y = 1, D1 is reverse biased, thus does not conduct. But D2 is forward biased, thus conducts and thus pulling F to HIGH.

If X = 1 and Y = 0, D2 is reverse biased, thus does not conduct. But D1 is forward biased, thus conducts and thus pulling F to HIGH.

If X = 1 and Y = 1, then both diodes D1 and D2 are forward biased and thus both the diodes conduct and thus F is HIGH.

#### Switch Representation of OR Gate

In the figure, X and Y are two switches which have been connected in parallel, and this is connected in series with the load LED and source battery. When both switches are open, current does not flow to LED, but when any switch is closed then current flows.

#### **Three Input OR gate**

Since we have already seen how an OR gate works, I will just list the truth table of a 3-input OR gate. The figure below shows its circuit and truth table.

| X | Y | Z | F=X+Y+Z |

|---|---|---|---------|

| 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 1       |

| 0 | 1 | 0 | 1       |

| 0 | 1 | 1 | 1       |

| 1 | 0 | 0 | 1       |

| 1 | 0 | 1 | 1       |

| 1 | 1 | 0 | 1       |

| 1 | 1 | 1 | 1       |

### **Truth Table**

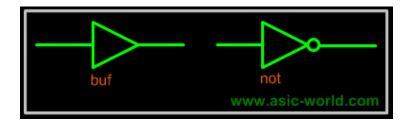

## **NOT Gate**

The NOT gate performs the basic logical function called inversion or complementation. NOT gate is also called inverter. The purpose of this gate is to convert one logic level into the opposite logic level. It has one input and one output. When a HIGH level is applied to an inverter, a LOW level appears on its output and vice versa.

If X is the input, then output F can be represented mathematically as F = X', Here apostrophe (') denotes the NOT (inversion) operation. There are a couple of other ways to represent inversion, F=! X, here! represents inversion. Truth table and NOT gate symbol is shown in the figure below.

### Symbol

### **Truth Table**

| X | Y=X' |

|---|------|

| 0 | 1    |

| 1 | 0    |

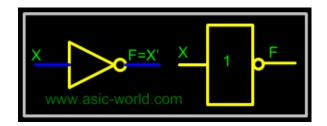

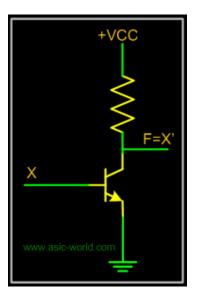

NOT gate using "transistor-resistor" logic is shown in the figure below, where X is the input and F is the output.

## Circuit

When X = 1, the transistor input pin 1 is HIGH, this produces the forward bias across the emitter base junction and so the transistor conducts. As the collector current flows, the voltage drop across RL increases and hence F is LOW.

When X = 0, the transistor input pin 2 is LOW: this produces no bias voltage across the transistor base emitter junction. Thus Voltage at F is HIGH.

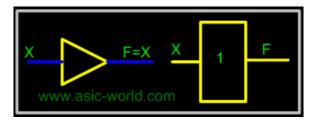

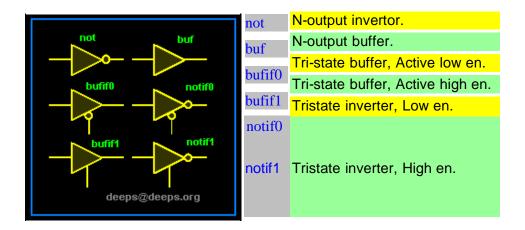

Buffer or BUF is also a gate with the exception that it does not perform any logical operation on its input. Buffers just pass input to output. Buffers are used to increase the drive strength or sometime just to introduce delay. We will look at this in detail later.

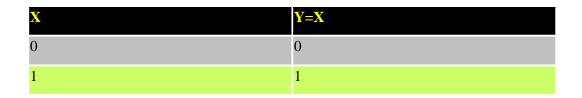

If X is the input, then output F can be represented mathematically as F = X. Truth table and symbol of the Buffer gate is shown in the figure below.

#### Symbol

### **Truth Table**

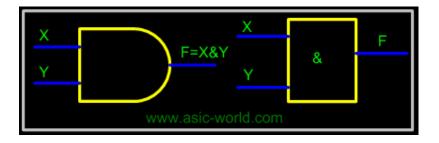

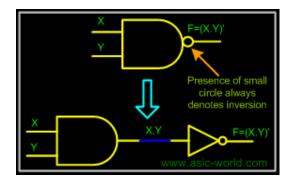

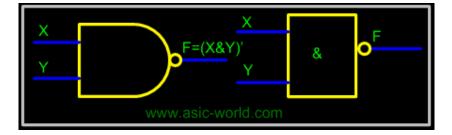

### NAND Gate

NAND gate is a cascade of AND gate and NOT gate, as shown in the figure below. It has two or more inputs and only one output. The output of NAND gate is HIGH when any one of its input is LOW (i.e. even if one input is LOW, Output will be HIGH).

### NAND From AND and NOT

If X and Y are two inputs, then output F can be represented mathematically as F = (X.Y)', Here dot (.) denotes the AND operation and (') denotes inversion. Truth table and symbol of the N AND gate is shown in the figure below.

# Symbol

### **Truth Table**

| X | Y | $\mathbf{F} = (\mathbf{X}, \mathbf{Y})'$ |

|---|---|------------------------------------------|

| 0 | 0 | 1                                        |

| 0 | 1 | 1                                        |

| 1 | 0 | 1                                        |

| 1 | 1 | 0                                        |

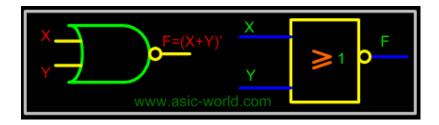

# **NOR Gate**

NOR gate is a cascade of OR gate and NOT gate, as shown in the figure below. It has two or more inputs and only one output. The output of NOR gate is HIGH when any all its inputs are LOW (i.e. even if one input is HIGH, output will be LOW).

# Symbol

If X and Y are two inputs, then output F can be represented mathematically as F = (X+Y)'; here plus (+) denotes the OR operation and (') denotes inversion. Truth table and symbol of the NOR gate is shown in the figure below.

#### **Truth Table**

| X | Y | <b>F</b> =( <b>X</b> + <b>Y</b> )' |

|---|---|------------------------------------|

| 0 | 0 | 1                                  |

| 0 | 1 | 0                                  |

| 1 | 0 | 0                                  |

| 1 | 1 | 0                                  |

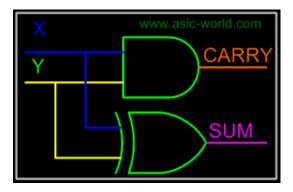

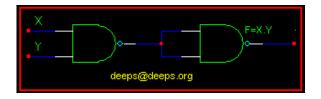

# **XOR Gate**

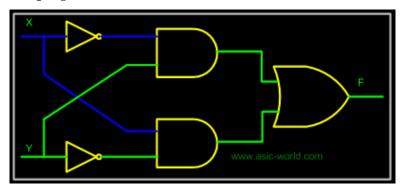

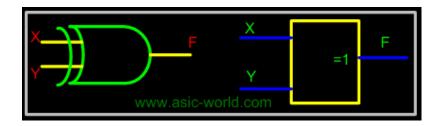

An Exclusive-OR (XOR) gate is gate with two or three or more inputs and one output. The output of a two-input XOR gate assumes a HIGH state if one and only one input assumes a HIGH state. This is equivalent to saying that the output is HIGH if either input X or input Y is HIGH exclusively and LOW when both are 1 or 0 simultaneously.

If X and Y are two inputs, then output F can be represented mathematically as  $F = X \bigoplus Y$ , Here  $\bigoplus$  denotes the XOR operation.  $X \bigoplus Y$  and is equivalent to X.Y' + X'.Y. Truth table and symbol of the XOR gate is shown in the figure below.

**XOR from Simple gates**

### Symbol

## **Truth Table**

| X | Y | $\mathbf{F}=(\mathbf{X}  \mathbf{Y})$ |

|---|---|---------------------------------------|

| 0 | 0 | 0                                     |

| 0 | 1 | 1                                     |

| 1 | 0 | 1                                     |

| 1 | 1 | 0                                     |

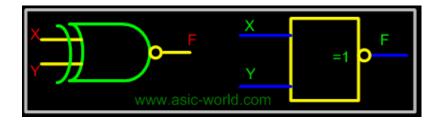

# **XNOR** Gate

An Exclusive-NOR (XNOR) gate is gate with two or three or more inputs and one output. The output of a two-input XNOR gate assumes a HIGH state if all the inputs assumes same state. This is equivalent to saying that the output is HIGH if both input X and input Y is HIGH exclusively or same as input X and input Y is LOW exclusively, and LOW when both are not same.

If X and Y are two inputs, then output F can be represented mathematically as  $F = X \oplus Y$ , Here  $\oplus$  denotes the XNOR operation.  $X \oplus Y$  and is equivalent to X.Y + X'.Y'. Truth table and symbol of the XNOR gate is shown in the figure below.

# Symbol

# **Truth Table**

| X | Y | $\mathbf{F}=(\mathbf{X}  \mathbf{Y})'$ |

|---|---|----------------------------------------|

| 0 | 0 | 1                                      |

| 0 | 1 | 0                                      |

| 1 | 0 | 0                                      |

| 1 | 1 | 1                                      |

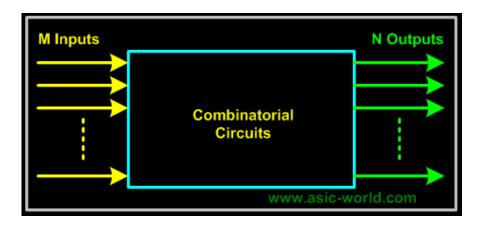

# **Combinational Logic**

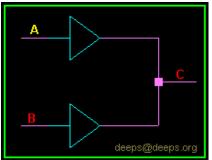

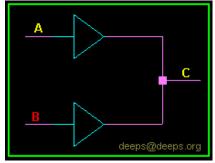

Combinatorial Circuits are circuits which can be considered to have the following generic structure.

Whenever the same set of inputs is fed in to a combinatorial circuit, the same outputs will be generated. Such circuits are said to be stateless. Some simple combinational logic elements that we have seen in previous sections are "Gates".

All the gates in the above figure have 2 inputs and one output; combinational elements simplest form are "not" gate and "buffer" as shown in the figure below. They have only one input and one output.

# Decoders

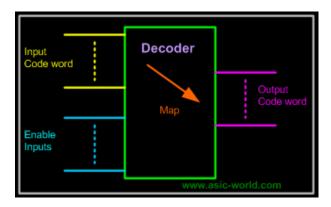

A decoder is a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different; e.g. n-to-2n, BCD decoders. Enable inputs must be on for the decoder to function, otherwise its outputs assume a single "disabled" output code word.

Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding. Figure below shows the pseudo block of a decoder.

# **Binary n-to-2<sup>n</sup> Decoders**

A binary decoder has n inputs and  $2^n$  outputs. Only one output is active at any one time, corresponding to the input value. Figure below shows a representation of Binary n-to- $2^n$  decoder

# Encoders

An encoder is a combinational circuit that performs the inverse operation of a decoder. If a device output code has fewer bits than the input code has, the device is usually called an encoder. e.g.  $2^{n}$ -to-n, priority encoders.

The simplest encoder is a  $2^{n}$ -to-n binary encoder, where it has only one of  $2^{n}$  inputs = 1 and the output is the n-bit binary number corresponding to the active input.

| 2 <sup>n</sup> Inputs |                                          | n Outputs       |

|-----------------------|------------------------------------------|-----------------|

| <u>]</u>              | 2 <sup>n</sup> to n<br>Binary<br>Encoder |                 |

|                       | WWW                                      | .asic-world.com |

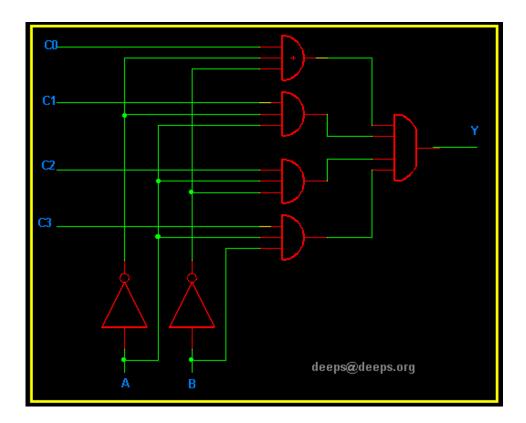

# Multiplexer

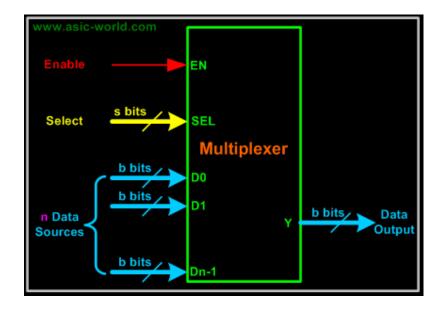

A multiplexer (MUX) is a digital switch which connects data from one of n sources to the output. A number of select inputs determine which data source is connected to the output. The block diagram of MUX with n data sources of b bits wide and s bits wide select line is shown in below figure.

MUX acts like a digitally controlled multi-position switch where the binary code applied to the select inputs controls the input source that will be switched on to the output as shown in the figure below. At any given point of time only one input gets selected and is connected to output, based on the select input signal.

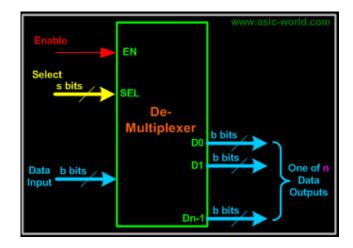

# **De-multiplexers**

They are digital switches which connect data from one input source to one of n outputs. Usually implemented by using  $n-to-2^n$  binary decoders where the decoder enable line is used for data input of the de-multiplexer.

The figure below shows a de-multiplexer block diagram which has got s-bitswide select input, one b-bits-wide data input and n b-bits-wide outputs.

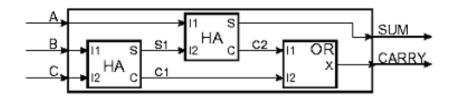

# Adders

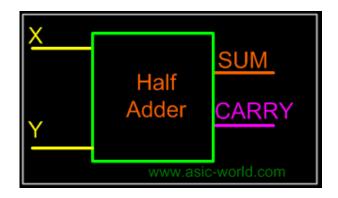

Adders are the basic building blocks of all arithmetic circuits; adders add two binary numbers and give out sum and carry as output. Basically we have two types of adders.

- Half Adder.

- Full Adder.

# Half Adder

Adding two single-bit binary values X, Y produces a sum S bit and a carry out C-out bit. This operation is called half addition and the circuit to realize it is called a half adder.

# **Truth Table**

| X | Y | SUM | CARRY |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

Symbol

Circuit

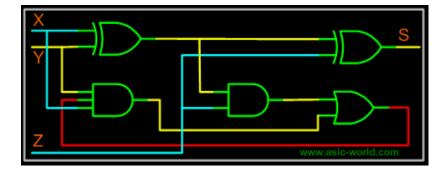

### **Full Adder**

Full adder takes a three-bits input. Adding two single-bit binary values X, Y with a carry input bit C-in produces a sum bit S and a carry out C-out bit.

# **Truth Table**

| X | Y | Z | SUM | CARRY |

|---|---|---|-----|-------|

| 0 | 0 | 0 | 0   | 0     |

| 0 | 0 | 1 | 1   | 0     |

| 0 | 1 | 0 | 1   | 0     |

| 0 | 1 | 1 | 0   | 1     |

| 1 | 0 | 0 | 1   | 0     |

| 1 | 0 | 1 | 0   | 1     |

| 1 | 1 | 0 | 0   | 1     |

| 1 | 1 | 1 | 1   | 1     |

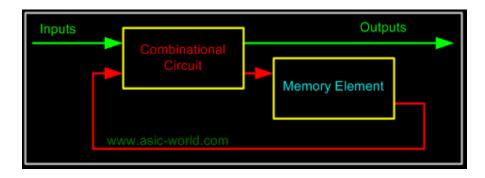

# **Sequential Circuits**

Digital electronics is classified into combinational logic and sequential logic. Combinational logic output depends on the inputs levels, whereas sequential logic output depends on stored levels and also the input levels.

The memory elements are devices capable of storing binary info. The binary info stored in the memory elements at any given time defines the state of the sequential circuit. The input and the present state of the memory element determine the output. Memory elements next state is also a function of external inputs and present state. A sequential circuit is specified by a time sequence of inputs, outputs, and internal states.

There are two types of sequential circuits. Their classification depends on the timing of their signals:

- Synchronous sequential circuits

- Asynchronous sequential circuits

# Asynchronous sequential circuit

This is a system whose outputs depend upon the order in which its input variables change and can be affected at any instant of time. Gate-type asynchronous systems are basically combinational circuits with feedback paths. Because of the feedback among logic gates, the system may, at times, become unstable. Consequently they are not often used.

## **Synchronous sequential circuits**

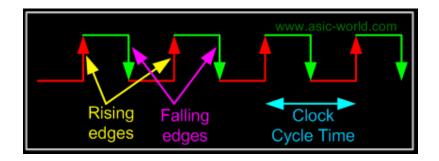

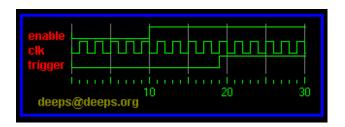

This type of system uses storage elements called flip-flops that are employed to change their binary value only at discrete instants of time. Synchronous sequential circuits use logic gates and flip-flop storage devices. Sequential circuits have a clock signal as one of their inputs. All state transitions in such circuits occur only when the clock value is either 0 or 1 or happen at the rising or falling edges of the clock depending on the type of memory elements used in the circuit.

Synchronization is achieved by a timing device called a clock pulse generator. Clock pulses are distributed throughout the system in such a way that the flip-flops are affected only with the arrival of the synchronization pulse. Synchronous sequential circuits that use clock pulses in the inputs are called clocked-sequential circuits. They are stable and their timing can easily be broken down into independent discrete steps, each of which is considered separately.

A clock signal is a periodic square wave that indefinitely switches from 0 to 1 and from 1 to 0 at fixed intervals. Clock cycle time or clock period: the time interval between two consecutive rising or falling edges of the clock.

Clock Frequency = 1 / clock cycle time (measured in cycles per second or Hz)

**Example:** Clock cycle time = 10ns clock frequency = 100 MHz

# **Latches and Flip-Flops**

Latches and Flip-flops are one and the same with a slight variation: Latches have level sensitive control signal input and Flip-flops have edge sensitive control signal input. Flip-flops and latches which use this control signals are called synchronous circuits. So if they don't use clock inputs, then they are called asynchronous circuits.

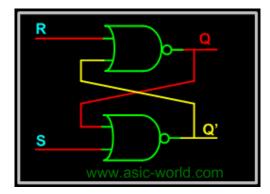

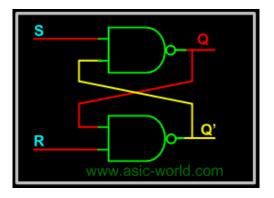

#### **RS** Latch

RS latch have two inputs, S and R. S is called set and R is called reset. The S input is used to produce HIGH on Q (i.e. store binary 1 in flip-flop). The R input is used to produce LOW on Q (i.e. store binary 0 in flip-flop). Q' is Q complementary output, so it always holds the opposite value of Q. The output of the S-R latch depends on current as well as previous inputs or state, and its state (value stored) can change as soon as its inputs change. The circuit and the truth table of RS latch is shown below.

| S | R | Q | <b>Q</b> + |

|---|---|---|------------|

| 0 | 0 | 0 | 0          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | Х | 0          |

| 1 | 0 | Х | 1          |

| 1 | 1 | Х | 0          |

The operation has to be analyzed with the 4 inputs combinations together with the 2 possible previous states.

- When S = 0 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. So it is clear that when both S and R inputs are LOW, the output is retained as before the application of inputs. (i.e. there is no state change).

- When S = 1 and R = 0: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 1 and Q' = (S + Q)' = 0. So in simple words when S is HIGH and R is LOW, output Q is HIGH.

- When S = 0 and R = 1: If we assume Q = 1 and Q' = 0 as initial condition, then output Q after input is applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. Assuming Q = 0 and Q' = 1 as initial condition, then output Q after the input applied would be Q = (R + Q')' = 0 and Q' = (S + Q)' = 1. So in simple words when S is LOW and R is HIGH, output Q is LOW.

- When S = 1 and R =1: No matter what state Q and Q' are in, application of 1 at input of NOR gate always results in 0 at output of NOR gate, which results in both Q and Q' set to LOW (i.e. Q = Q'). LOW in both the outputs basically is wrong, so this case is invalid.

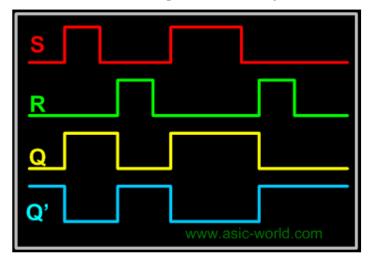

The waveform below shows the operation of NOR gate based RS Latch.

It is possible to construct the RS latch using NAND gates (of course as seen in Logic gates section). The only difference is that NAND neither is NOR gate dual form (Did I say that in Logic gates section?). So in this case the R = 0 and S = 0 case becomes the invalid case. The circuit and Truth table of RS latch using NAND is shown below.

| S | R | Q | <b>Q</b> + |

|---|---|---|------------|

| 1 | 1 | 0 | 0          |

| 1 | 1 | 1 | 1          |

| 0 | 1 | Х | 0          |

| 1 | 0 | Х | 1          |

| 0 | 0 | Х | 1          |

If you look closely, there is no control signal (i.e. no clock and no enable), so these kinds of latches or flip-flops are called asynchronous logic elements. Since all the sequential circuits are built around the RS latch, we will concentrate on synchronous circuits and not on asynchronous circuits.

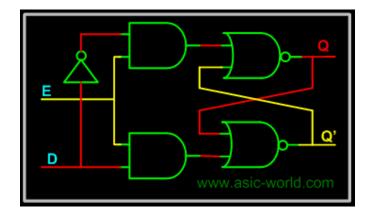

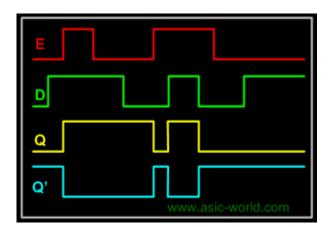

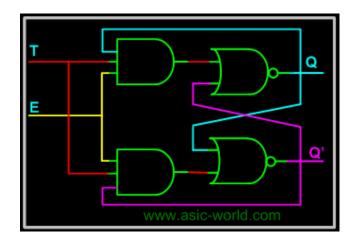

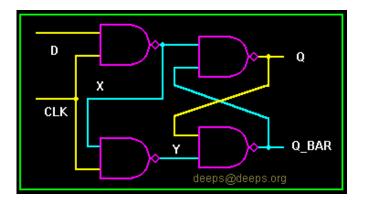

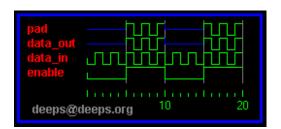

#### **D** Latch

The RS latch seen earlier contains ambiguous state; to eliminate this condition we can ensure that S and R are never equal. This is done by connecting S and R together with an inverter. Thus we have D Latch: the same as the RS latch, with the only difference that there is only one input, instead of two (R and S). This input is called D or Data input. D latch is called D transparent latch for the reasons explained earlier. Delay flip-flop or delay latch is another name used. Below is the truth table and circuit of D latch.

In real world designs (ASIC/FPGA Designs) only D latches/Flip-Flops are used.

| D | Q | <b>Q</b> + |

|---|---|------------|

| 1 | Х | 1          |

| 0 | Х | 0          |

Below is the D latch waveform, which is similar to the RS latch one, but with R removed.

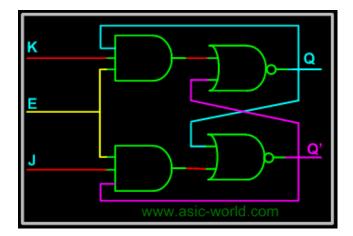

#### JK Latch

The ambiguous state output in the RS latch was eliminated in the D latch by joining the inputs with an inverter. But the D latch has a single input. JK latch is similar to RS latch in that it has 2 inputs J and K as shown figure below. The ambiguous state has been eliminated here: when both inputs are high, output toggles. The only difference we see here is output feedback to inputs, which is not there in the RS latch.

| J | K | Q |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 1 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 0 |

#### T Latch

When the two inputs of JK latch are shorted, a T Latch is formed. It is called T latch as, when input is held HIGH, output toggles.

| Τ | Q | <b>Q</b> + |

|---|---|------------|

| 1 | 0 | 1          |

| 1 | 1 | 0          |

| 0 | 1 | 1          |

| 0 | 0 | 0          |

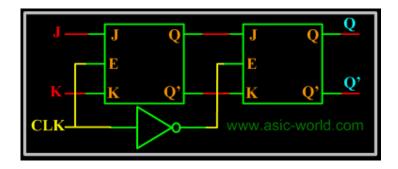

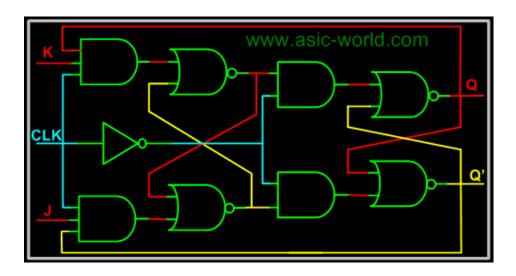

#### JK Master Slave Flip-Flop

All sequential circuits that we have seen in the last few pages have a problem (All level sensitive sequential circuits have this problem). Before the enable input changes state from HIGH to LOW (assuming HIGH is ON and LOW is OFF state), if inputs changes, then another state transition occurs for the same enable pulse. This sort of multiple transition problem is called racing. If we make the sequential element sensitive to edges, instead of levels, we can overcome this problem, as input is evaluated only during enable/clock edges.

In the figure above there are two latches, the first latch on the left is called master latch and the one on the right is called slave latch. Master latch is positively clocked and slave latch is negatively clocked.

# VHDL

# CONTENTS

# 1. INTRODUCTION TO VLSI

- 2. BASIC COMPONENTS OF A VHDL MODEL

- **3. BASIC LANGUAGE ELEMENTS**

- **4. MODELING TYPES**

- **5. GENERICS AND CONFIGURATIONS**

- 6. SUBPROGRAMS AND PACKAGES

- 7. ADVANCED FEATURES

# **CHAPTER 1**

# **INTRODUCTION TO VLSI**

#### Introduction

Integrated circuits were made possible by experimental discoveries which showed that semiconductor devices could perform the functions of vacuum tubes, and by mid-20th-century technology advancements in semiconductor device fabrication. The integration of large numbers of tiny transistors into a small chip was an enormous improvement over the manual assembly of circuits using discrete electronic components. The integrated circuit's mass production capability, reliability, and building-block approach to circuit design ensured the rapid adoption of standardized ICs in place of designs using discrete transistors. There are two main advantages of ICs over discrete circuits - cost and performance. Cost is low because the chips, with all their components, are printed as a unit by photolithography and not constructed a transistor at a time. Performance is high since the components switch quickly and consume little power, because the components are small and close together. As of 2006, chip areas range from a few square mm to around 250 mm<sup>2</sup>, with up to 1 million transistors per mm<sup>2</sup>.

#### **Advances in Integrated circuits**

Among the most advanced integrated circuits are the microprocessors, which control everything from computers to cellular phones to digital microwave ovens. Digital memory chips are another family of integrated circuit that is crucially important to the modern information society. While the cost of designing and developing a complex integrated circuit is quite high, when spread across typically millions of production units the individual IC cost is minimized. The performance of ICs is high because the small size allows short traces, which in turn allows low power logic (such as CMOS) to be used at fast switching speeds. ICs have consistently migrated to smaller feature sizes over the years, allowing more circuitry to be packed on each chip. As the feature size shrinks, almost everything improves - the cost per unit and the switching power consumption go down, and the speed goes up. However, IC's with nanometer-scale devices are not without their problems, principal among which is leakage current, although these problems are not insurmountable and will likely be solved or at least ameliorated by the introduction of high-k dielectrics. Since these speed and power consumption gains are apparent to the end user, there is fierce competition among the manufacturers to use finer geometries. This process, and the expected progress over the next few years, is well described by the International Technology Roadmap for Semiconductors, or ITRS.

#### SSI, MSI, LSI

The first integrated circuits contained only a few transistors. Called "**Small-Scale Integration**" (**SSI**), they used circuits containing transistors numbering in the tens.SSI circuits were crucial to early aerospace projects, and vice-versa. Both the Minuteman missile and Apollo program needed lightweight digital computers for their inertially-guided flight computers; the Apollo guidance computer led and motivated the integrated-circuit technology, while the Minuteman missile forced it into mass-production.These programs purchased almost all of the available integrated circuits from 1960 through 1963, and almost alone provided the demand that funded the production improvements to get the production costs from \$1000/circuit (in 1960 dollars) to merely \$25/circuit (in 1963 dollars).

The next step in the development of integrated circuits, taken in the late 1960s, introduced devices which contained hundreds of transistors on each chip, called "**Medium-Scale Integration**" (**MSI**). They were attractive economically because while they cost little more to produce than SSI devices, they allowed more complex systems to be produced using smaller circuit boards, less assembly work, and a number of other advantages. Further development, driven by the same economic factors, led to "**Large-Scale Integration**" (**LSI**) in the mid 1970s, with tens of thousands of transistors per chip. LSI circuits began to be produced in large quantities around 1970, for computer main memories and pocket calculators.

#### VLSI

The final step in the development process, starting in the 1980s and continuing on, was "Very Large-Scale Integration" (VLSI), with hundreds of thousands of transistors, and beyond (well past several million in the latest stages). For the first time it became possible to fabricate a CPU on a single integrated circuit, to create a microprocessor. In 1986 the first one megabit RAM chips were introduced, which contained more than one million transistors. Microprocessor chips produced in 1994 contained more than three million transistors. This step was largely made possible by the codification of "design rules" for the CMOS technology used in VLSI chips, which made production of working devices much more of a systematic endeavor.

#### ULSI, WSI, SOC

To reflect further growth of the complexity, the term **ULSI** that stands for "**Ultra-Large Scale Integration**" was proposed for chips of complexity more than 1 million of transistors. However there is no qualitative leap between VLSI and ULSI, hence normally in technical texts the "VLSI" term covers ULSI as well, and "ULSI" is reserved only for cases when it is necessary to emphasize the chip complexity, e.g. in marketing.

The most extreme integration technique is **wafer-scale integration** (**WSI**), which uses whole uncut wafers containing processors as well as memory. Attempts to take this step commercially in the 1980s (e.g. by Gene Amdahl) failed, mostly because of defect-free manufacturability problems, and it does not now seem to be a high priority for industry. The WSI technique failed commercially, but advances in semiconductor manufacturing allowed for another attack on the IC complexity, known as **System-on-Chip** (**SOC**) design. In this approach, components traditionally manufactured as separate chips to be wired together on a printed circuit board are designed to occupy a single chip that contains memory, microprocessor, peripheral interfaces, Input/Output logic control, data converters, and other components, together composing the whole electronic system.

#### Other developments

In the 1980s programmable integrated circuits were developed. These devices contain circuits whose logical function and connectivity can be programmed by the user, rather than being fixed by the integrated circuit manufacturer. This allows a single chip to be programmed to implement different LSI-type functions such as logic gates, adders, and registers. Current devices named FPGAs (Field Programmable Gate Arrays) can now implement tens of thousands of LSI circuits in parallel and operate up to 400 MHz. The techniques perfected by the integrated circuits industry over the last three decades have been used to create microscopic machines, known as MEMS. These devices are used in a variety of commercial and defense applications, including projectors, ink jet printers, and accelerometers used to deploy the airbag in car accidents. In the past, radios could not be fabricated in the same low-cost processes as microprocessors. But since 1998, a large number of radio chips have been developed using CMOS processes. Examples include Intel's DECT cordless phone, or Atheros's 802.11 card.

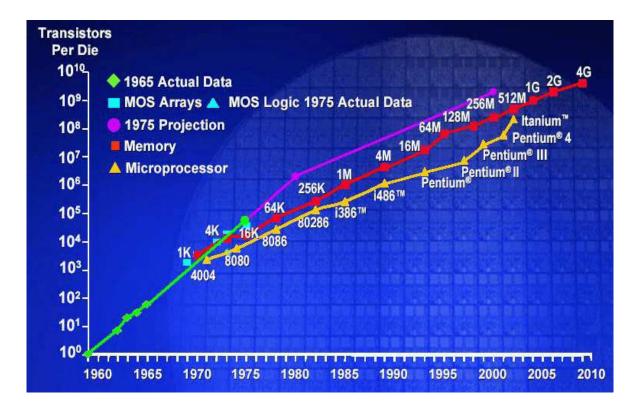

#### Moore's Law

The growth of complexity of integrated circuits follows a trend called "Moore's Law", first observed by Gordon Moore of Intel. Moore's Law in its modern interpretation states that the number of transistors in an integrated circuit doubles every two years. By the year 2000 the largest integrated circuits contained hundreds of millions of transistors. It is difficult to say whether the trend will continue.

# **Popularity of ICs**

Only a half century after their development was initiated, integrated circuits have become ubiquitous. Computers, cellular phones, and other digital appliances are now inextricable parts of the structure of modern societies. That is, modern computing, communications, manufacturing and transport systems, including the Internet, all depend on the existence of integrated circuits. Indeed, many scholars believe that the digital revolution brought about by integrated circuits was one of the most significant occurrences in the history of mankind.

#### Why VLSI?

Integration improves the design:

- Lower parasitic = higher speed.

- Lower power.

- Physically smaller.

- Integration reduces manufacturing cost-no manual assembly.

#### **Challenges in VLSI Design**

- Multiple levels of abstraction: transistors to CPUs.

- Multiple and conflicting constraints: low cost and high performances are often at odds.

- Short design time: Late products are often irrelevant.

# **Dealing with Complexity**

Divide-and-conquer: limit the number of components you deal with at any one time.

Group several components into larger components:

- transistors form gates;

- gates form functional units;

- Functional units form processing elements, etc.

# **Top-down vs. Bottom-up Design**

- Top-down design adds functional detail. Create lower levels of abstraction from upper levels.

- Bottom-up design creates abstractions from low-level behavior.

- Good design needs both top-down and bottom-up efforts.

#### **Design Strategies**

IC design productivity depends on the efficiency with which the design may be converted from concept to architecture, to logic and memory, to circuit and hence to a physical layout. A good design strategy with a good design system should provide for consistent descriptions in various abstraction levels. The role of good design strategies is to reduce complexity, increase productivity, and assure working product.

Design is a continuous trade-off to achieve adequate results for:

- Performance speed, power, function, flexibility

- Size of die (hence cost of die)

- Time to design

- Ease of test generation and testability

# Hardware Description Languages (HDLs)

IEEE standardized Language

# • VHDL

• VerilogHDL

#### What is VHDL?

- VHDL: VHSIC Hardware Description Language -VHSIC: Very High Speed Integrated Circuit

- Developed originally by DARPA -for specifying digital systems

- International IEEE standard (IEEE 1076-1993)

- Hardware Description, Simulation, Synthesis

- Practical benefits:

- -a mechanism for digital design and reusable design documentation

- -Model interoperability among vendors

- -Third party vendor support

-Design re-use.

# VHDL vs. C/Pascal

#### C/Pascal:

- -Procedural programming languages.

- -Typically describe procedures for computing a math's function or manipulation of data.

- (e.g., sorting, matrix computing)

- -A program is a recipe or a sequence of steps for how to perform a computation or

manipulate data.

#### VHDL:

- A language to describe digital systems.

-Purposes: simulation and synthesis of digital systems.

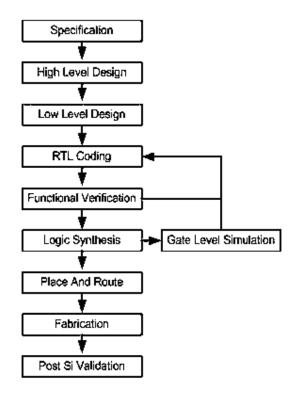

#### **Design Flow**

#### > SPECIFICATION

This is the stage at which we define what are the important parameters of the system/design that you are planning to design. A simple example would be: I want to design a counter; it should be 4 bit wide, should have synchronous reset, with active high enable; when reset is active, counter output should go to "0".

#### HIGH LEVEL DESIGN

This is the stage at which you define various blocks in the design and how they communicate. Let's assume that we need to design a microprocessor: high level design means splitting the design into blocks based on their function; in our case the blocks are registers, ALU, Instruction Decode, Memory Interface, etc.

#### MICRO DESIGN/LOW LEVEL DESIGN

Low level design or Micro design is the phase in which the designer describes how each block is implemented. It contains details of State machines, counters, Mux, decoders, internal registers. It is always a good idea to draw waveforms at various interfaces. This is the phase where one spends lot of time.

#### > RTL CODING

In RTL coding, Micro design is converted into Verilog/VHDL code, using synthesizable constructs of the language. Normally we like to lint the code, before starting verification or synthesis.

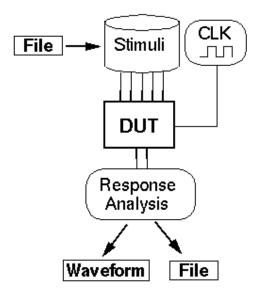

#### > SIMULATION

Simulation is the process of verifying the functional characteristics of models at any level of abstraction. We use simulators to simulate the Hardware models. To test if the RTL code meets the functional requirements of the specification, we must see if all the RTL blocks are functionally correct. To achieve this we need to write a **test bench**, which generates clk, reset and the required test vectors. We use the waveform output from the simulator to see if the DUT (Device Under Test) is functionally correct.

#### > SYNTHESIS

Synthesis is the process in which synthesis tools like design compiler or Synplify take RTL in Verilog or VHDL, target technology, and constrains as input and maps the RTL to target technology primitives. Synthesis tool, after mapping the RTL to gates, also do the minimal amount of timing analysis to see if the mapped design is meeting the timing requirements. (Important thing to note is, synthesis tools are not aware of wire delays, they only know of gate delays).

- **Formal Verification:** Check if the RTL to gate mapping is correct.

- Scan insertion: Insert the scan chain in the case of A.

#### > PLACE & ROUTE

The gate level net list from the synthesis tool is taken and imported into place and route tool in Verilog net list format. All the gates and flip-flops are placed; clock tree synthesis and reset is routed. After this each block is routed. The P&R tool output is a GDS file, used by foundry for fabricating the ASIC.

#### > GATE LEVEL SIMULATION (OR) SDF/TIMING SIMULATION

There is another kind of simulation, called **timing simulation**, which is done after synthesis or after P&R (Place and Route). Here we include the gate delays and wire delays and see if DUT works at rated clock speed.

#### > POST SILICON VALIDATION

Once the chip (silicon) is back from fab, it needs to put in real environment and tested before it can be released into Market. Since the speed of simulation with RTL is very slow (number clocks per second), there is always possibility to find a bug in Post silicon validation.

**Note**: As design becomes complex, we write **SELF CHECKING TESTBENCH**, where test bench applies the test vector, then compares the output of DUT with expected values.

# **CHAPTER 2**

# **BASIC COMPONENTS OF A VHDL MODEL**

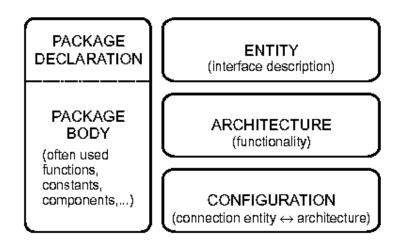

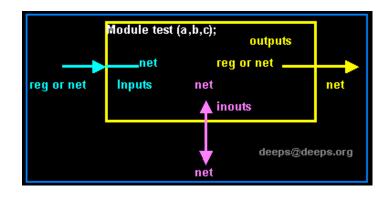

The purpose of VHDL descriptions is to provide a model for digital circuits and systems. This abstract view of the real physical circuit is referred to as entity. An entity normally consists of five basic elements, or design units.

In VHDL one generally distinguishes between the external view of a module and its internal description. The external view is reflected in the entity declaration, which represents an interface description of a 'black box'. The important part of this interface description consists of signals over which the individual modules communicate with each other.

The internal view of a module and, therefore, its functionality is described in the architecture body. This can be achieved in various ways. One possibility is given by coding a behavioral description with a set of concurrent or sequential statements. Another possibility is a structural description, which serves as a base for the hierarchically designed circuit architectures. Naturally, these two kinds of architectures can also be combined. The lowest hierarchy level, however, must consist of behavioral descriptions. One of the major VHDL features is the capability to deal with multiple different architectural bodies belonging to the same entity declaration.

Being able to investigate different architectural alternatives permits the development of systems to be done in an efficient top-down manner. The ease of switching between different architectures has another advantage, namely, quick testing. In this case, it is necessary to bind one architecture to the entity in order to have a unique hierarchy for simulation or synthesis. Which architecture should be used for simulation or synthesis in conjunction with a given entity is specified in the configuration section. If the architecture body consists of a structural description, then the binding of architectures and entities of the instantiated submodules, the so-called components, can also be fixed by the configuration statement.

The package is the last element mentioned here. It contains declarations of frequently used data types, components, functions, and so on. The package consists of a package declaration and a package body. The declaration is used, like the name implies, for declaring the above-mentioned objects. This means, they become visible to other design units. In the package body, the definition of these objects can be carried out, for example, the definition of functions or the assignment of a value to a constant. The partitioning of a package into its declaration and body provides advantages in compiling the model descriptions.

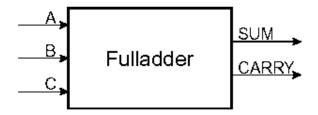

#### **Entity Declaration**

An entity declaration specifies the name of an entity and its interface. This corresponds to the information given by the symbols in traditional design methods based on drawing schematics. Signals that are used for communication with the surrounding modules are called ports.

Interface of a full-adder module

#### Example:

entity FULLADDER is

port (A, B, C: in bit;

SUM, CARRY : out bit );

end FULLADDER;

The module FULLADDER has five interface ports. Three of them are the input ports A, B and C indicated by the VHDL keyword **in**. The remaining two are the output ports SUM and CARRY indicated by **out**. The signals going through these ports are chosen to be of the type bit. This is one of the predefined types besides integer, real and others types provided by VHDL. The type bit consists of the two characters '0' and '1' and represents the binary logic values of the signals.

Every port declaration implicitly creates a signal with the name and type specified. It can be used in all architectures belonging to the entity in one of the following port modes:

in: The port can only be read within the entity and its architectures.

out: This port can only be written.

inout: This port can be read and written. This is useful for modeling bus systems.

buffer: The port can be read and written. Each port must have only one driver.

Syntax :

entity entity name is

[generics]

[ports]

[declarations (types, constants, signals)]

[definitions (functions, procedures)]

[ begin -- normally not used

statements ]

end [ entity name ];

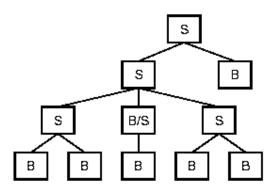

#### Architecture

The second important component of a VHDL description is the architecture. This is where the functionality and the internal implementation of a module are described. In general, a complex hierarchically structured system may have the topology.

#### Hierarchical circuit design

S: structural description

B: behavioral description

B/S: mixed description

In order to describe such a system both behavioral and structural descriptions are required. A behavioral description may be of either concurrent or sequential type. Overall, VHDL architectures can be classified into the three main types:

- Data flow modeling.

- Behavioral modeling.

- Structural modeling.

Syntax :

architecture architecture name of entity name is

[ arch declarative part ]

begin

[ arch statement part ]

end [ architecture name ];

The architecture specifies the implementation of the entity entity name. A label architecture name must be assigned to the architecture. In case there are multiple architectures associated with one entity this label is then used within a configuration Statement to bind one particular architecture to its entity. The architecture block consists of two parts: the arch declarative part before the keywords **begin** and the arch statement part after the keywords **begin**. In the declaration part local types, signals, components etc. are declared and subprograms are defined. The actual model description is done in the statement part. In contrast to programming languages like C, the major concern of VHDL is describing hardware which primary works in parallel and not in a sequential manner. Therefore, a special simulation algorithm is used to achieve a virtual concurrent processing. This algorithm is explained in the following section.

#### **Configuration :**

It is used to create a configuration for an entity. To binding of components used in the selected architecture body to other entities.

#### **Package Declaration :**

It contains a set of declarations that may possibly be shared by many design units.

#### Package Body :

It contains the behavior of the subprogram and the values of the deferred constants declared in a package declaration.

# CHAPTER 3

# **BASIC LANGUAGE ELEMENTS**

This describes the facilities in VHDL, which are drawn from the familiar programming language repertoire. If you are familiar with the Ada programming language, you will notice the similarity with that language. This is both a convenience and a nuisance. The convenience is that you don't have much to learn to use these VHDL facilities. The problem is that the facilities are not as comprehensive as those of Ada, though they are certainly adequate for most modeling purposes.

#### **Lexical Elements**

#### Comments

Comments in VHDL start with two adjacent hyphens ('--') and extend to the end of the line. They have no part in the meaning of a VHDL description.

#### Identifiers

Identifiers in VHDL are used as reserved words and as programmer-defined names. They must conform to the rule:

Letter { [ underline ] letter\_or\_digit }

Note that case of letters is not considered significant, so the identifiers cat and Cat are the same. Underline characters in identifiers are significant, so This\_Name and ThisName are different identifiers.

#### Numbers

Literal numbers may be expressed either in decimal or in a base between two and sixteen. If the literal includes a point, it represents a real number, otherwise it represents an integer. Decimal literals are defined by:

integer [ integer ] [ exponent ]

Example :

| 0   | 1   | 123_456_789 | 987E6   | integer literals |

|-----|-----|-------------|---------|------------------|

| 0.0 | 0.5 | 2.718_28    | 12.4E-9 | real literals    |

Based literal numbers are defined by:

base # based\_integer [ based\_integer ] # [ exponent ]

The base and the exponent are expressed in decimal. The exponent indicates the power of the base by which the literal is multiplied. The letters A to F (upper or lower case) are used as extended digits to represent 10 to 15.

Example :

2#1100\_0100# 16#C4# 4#301#E1 -- the integer 196

2#1.1111\_1111\_111#E+11 16#F.FF#E2 -- the real number 4095.0

#### Characters

Literal characters are formed by enclosing an ASCII character in single-quote marks.

#### Example :

'A' '\*' ''' ' '

#### Strings

Literal strings of characters are formed by enclosing the characters in doublequote marks. To include a double-quote mark itself in a string, a pair of double-quote marks must be put together. A string can be used as a value for an object which is an array of characters.

#### Example :

"A string"

пп

-- empty string

"A string in a string: ""A string"". " -- contains quote marks

#### **Bit Strings**

VHDL provides a convenient way of specifying literal values for arrays of type bit.

Syntax :

base\_specifier " bit\_value "

Base specifier B stands for binary, O for octal and X for hexadecimal.

#### Examples :

| B"1010110" | length is 7                               |

|------------|-------------------------------------------|

| 0"126"     | length is 9, equivalent to B"001_010_110" |

| X"56"      | length is 8, equivalent to B"0101_0110"   |

# **Data Types and Objects**

VHDL provides a number of basic, or *scalar*, types, and a means of forming *composite* types. The scalar types include numbers, physical quantities, and enumerations and there are a number of standard predefined basic types. The composite types provided are arrays and records. A data type can be defined by a type declaration:

type identifier is type\_definition ;

Type\_definition :

scalar\_type\_definition

composite\_type\_definition

Scalar\_type\_definition :

integer\_type\_definition physical\_type\_definition

floating\_type\_definition

enumeration\_type\_definition

#### Composite\_type\_definition :

array\_type\_definition

record\_type\_definition

#### **Integer Types**

An integer type is a range of integer values within a specified range.

#### Syntax :

type identifier is range range\_constraint;

The expressions that specify the range must of course evaluate to integer numbers. Types declared with the keyword **to** are called *ascending* ranges, and those declared with the keyword **downto** are called *descending* ranges. The VHDL standard allows an implementation to restrict the range, but requires that it must at least allow the range –2147483647 to +2147483647.

#### Example :

type byte\_int is range 0 to 255;

type signed\_word\_int is range -32768 to 32767;

type bit\_index is range 31 downto 0;

There is a predefined integer type called integer. The range of this type is implementation defined, though it is guaranteed to include -2147483647 to +2147483647.

#### **Physical Types**

A physical type is a numeric type for representing some physical quantity, such as mass, length, time or voltage. The declaration of a physical type includes the specification of a base unit, and possibly a number of secondary units, being multiples of the base unit.

Syntax :

type identifier is range range\_constraint

units

base\_unit\_declaration

{ secondary\_unit\_declaration }

end units

Example :

type length is range 0 to 1E9 units um; mm = 1000 um; cm = 10 mm; m = 1000 mm; in = 25.4 mm; ft = 12 in; yd = 3 ft; rod = 198 in; chain = 22 yd; furlong = 10 chain;

end units;

type resistance is range 0 to 1E8

units

ohms;

kohms = 1000 ohms;

Mohms = 1E6 ohms;

end units;

The predefined physical type time is important in VHDL, as it is used extensively to specify delays in simulations. Its definition is:

type time is range implementation\_defined

units

fs;

ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 us; sec = 1000 ms; min = 60 sec; hr = 60 min;

end units;

#### **Floating Point Types**

A floating point type is a discrete approximation to the set of real numbers in a specified range. The precision of the approximation is not defined by the VHDL language standard, but must be at least six decimal digits. The range must include at least -1E38 to +1E38.

#### Syntax :

type identifier is range range\_constraint;

#### Examples :

type signal\_level is range -10.00 to +10.00;

type probability is range 0.0 to 1.0;

There is a predefined floating point type called real. The range of this type is implementation defined, though it is guaranteed to include -1E38 to +1E38.

#### **Enumeration Types**

An enumeration type is an ordered set of identifiers or characters. The identifiers and characters within a single enumeration type must be distinct, however they may be reused in several different enumeration types.

Syntax :

type identifier is ( enumeration\_literal );

#### Example :

type logic\_level is (unknown, low, undriven, high);

type alu\_function is (disable, pass, add, subtract, multiply, divide);

type octal\_digit is ('0', '1', '2', '3', '4', '5', '6', '7');

There are a number of predefined enumeration types, defined as follows:

type severity\_level is (note, warning, error, failure);

type boolean is (false, true);

type bit is ('0', '1');

type character is (NUL, SOH, STX, ETX, EOT, ENQ, ACK, BEL, BS,

HT, LF, VT, FF, CR, SO, SI, DLE, DC1, DC2, DC3, DC4, NAK, SYN, ETB, CAN,EM, SUB, ESC, FSP, GSP, RSP, USP, ' ', '!', '''', '#', '\$', '%', '&', ''', '(', ')', '\*', '+', ',', '-', '.', '/', '0', '1', '2', '3', '4', '5', '6', '7', '8', '9', ':', ';', '<', '=', '>', '?', '@', 'A', 'B', 'C', 'D', 'E', 'F', 'G', 'H', 'I', 'J', 'K', 'L', 'M', 'N', 'O', 'P', 'Q', 'R', 'S', 'T', 'U', 'V', 'W', 'X', 'Y', 'Z', '[', '\', ']', 'A', '\_\_, '`, 'a', 'b', 'c', 'd', 'e', 'f', 'g', 'h', 'i', 'j', 'k', 'I', 'm', 'n', 'o', 'p', 'q', 'r', 's', 't', 'u', 'v', 'w', 'x', 'y', 'z', '{', '|', '}, 'A', 'EL);

Note that type character is an example of an enumeration type containing a mixture of identifiers and characters. Also, the characters '0' and '1' are members of both bit and character . Where '0' or '1' occur in a program, the context will be used to determine which type is being used.

#### Arrays

An array in VHDL is an indexed collection of elements all of the same type. Arrays may be one-dimensional (with one index) or multidimensional (with a number of indices). In addition, an array type may be constrained, in which the bounds for an index are established when the type is defined, or unconstrained, in which the bounds are established subsequently.

## Syntax :

type identifier is array index\_constraint of element\_subtype\_indication;

#### Example :

type word is array (31 downto 0) of bit;

type memory is array (address) of word;

type transform is array (1 to 4, 1 to 4) of real;

type register\_bank is array (byte range 0 to 132) of integer;

An example of an unconstrained array type declaration:

type vector is array (integer range <>) of real;

The symbol '<>' (called a box) can be thought of as a place-holder for the index range, which will be filled in later when the array type is used. For example, an object might be declared to be a vector of 20 elements by giving its type as:

vector(1 to 20)

There are two predefined array types, both of which are unconstrained. They are defined as:

type string is array (positive range <>) of character;

type bit\_vector is array (natural range <>) of bit;

The types positive and natural are subtypes of integer. The type bit\_vector is particularly useful in modeling binary coded representations of values in simulations of digital systems. An element of an array object can referred to by indexing the name of the object. For example, suppose a and b are one and two-dimensional array objects respectively. Then the indexed names a(1) and b(1, 1) refer to elements of these arrays. Furthermore, a contiguous slice of a one-dimensional array can be referred to by using a range as an index. For example a (8 to 15) is an eight-element array which is part of the array. Sometimes you may need to write a literal value of an array type. This can be done using an array aggregate, which is a list of element values. Suppose we have an array type declared as:

type a is array (1 to 4) of character;

and we want to write a value of this type containing the elements 'f', 'o', 'o', 'd' in that order. We could write an aggregate with *positional* association as follows:

In this case, the index for each element is explicitly given, so the elements can be in any order. Positional and named association can be mixed within an aggregate, provided all the positional associations come first. Also, the word **others** can be used in place of an index in a named association, indicating a value to be used for all elements not explicitly mentioned. For example, the same value as above could be written as:

$$('f', 4 => 'd', others => 'o')$$

#### Records

VHDL provides basic facilities for records, which are collections of named elements of possibly different types.

Syntax :

type identifier is

record

element\_declaration

{ element\_declaration }

end record

Example :

type instruction is

record

op\_code : processor\_op ;

address\_mode : mode ;

operand1, operand2: integer range 0 to 15;

end record;

When you need to refer to a field of a record object, you use a selected name. For example, suppose that r is a record object containing a field called f. Then the name r.f refers to that field. As for arrays, aggregates can be used to write literal values for records. Both positional and named association can be used, and the same rules apply, with record field names being used in place of array index names.

#### Subtypes

The use of a subtype allows the values taken on by an object to be restricted or constrained subset of some base type.

## Syntax :

subtype identifier is [ resolution\_function\_name ] range [ constraint ] ;

There are two cases of subtypes. Firstly a subtype may constrain values from a scalar type to be within a specified range.

## Example :

subtype pin\_count is integer range 0 to 400;

subtype digits is character range '0' to '9';

Secondly, a subtype may constrain an otherwise unconstrained array type by specifying bounds for the indices.

#### Example :

subtype id is string(1 to 20);

subtype word is bit\_vector(31 downto 0);

There are two predefined numeric subtypes, defined as:

subtype natural is integer range 0 to highest\_integer ;

subtype positive is integer range 1 to highest\_integer ;

#### **Object Declarations**

An object is a named item in a VHDL description which has a value of a specified type. There are three classes of objects:

- Constants

- Variables

- Signals

## Constants

Declaration and use of constants and variables is very much like their use in programming languages. A constant is an object which is initialised to a specified value when it is created, and which may not be subsequently modified.

## Syntax :

```

constant identifier_list : subtype_indication [ := expression ] ;

```

Constant declarations with the initialising expression missing are called deferred constants, and may only appear in package declarations. The initial value must be given in the corresponding package body.

#### Example :

constant e : real := 2.71828;

constant delay : Time := 5 ns;

constant max\_size : natural;

### Variables

A variable is an object whose value may be changed after it is created.

#### Syntax :

The initial value expression, if present, is evaluated and assigned to the variable when it is created. If the expression is absent, a default value is assigned when the variable is created. The default value for scalar types is the leftmost value for the type, that is the first in the list of an enumeration type, the lowest in an ascending range, or the highest in a descending range. If the variable is a composite type, the default value is the composition of the default values for each element, based on the element types.

#### Example :

```

variable count : natural := 0;

```

variable trace : trace\_array;

Assuming the type trace\_array is an array of boolean, then the initial value of the variable trace is an array with all elements having the value false.

## **Signals**

Signals represent wires in a logic circuit. Signals can be declared in all declarative regions in VHDL except for functions and procedures. Assignments to signals are not immediate, but scheduled to be executed after a delta delay.

#### Syntax :

signal identifier\_list : subtype\_indication [ := expression ] ;

## Example :

```

signal foo : bit_vector (0 to 5) := B"000000" ;

```

signal aux : bit ;

signal max\_value : integer ;

The declaration assigns a name to the signal foo ; a type, with or without a range restriction (bit\_vector(0 to 5)); and optionally an initial value. Initial values on signals are usually ignored by synthesis. Signals can be assigned values using an assignment statement (e.g., aux <= '0' ;). If the signal is of an array type, elements of the signal's array can be accessed and assigned using indexing or slicing methods.

## **Expressions and Operators**

Expressions in VHDL are much like expressions in other programming languages. An expression is a formula combining primaries with operators. Primaries include names of objects, literals, function calls and parenthesized expressions.

| Туре          | Operators |     |      |     |     | Precedence |         |

|---------------|-----------|-----|------|-----|-----|------------|---------|

| Logical       | and       | or  | nand | nor | xor | xnor       | Lowest  |

| Relational    | =         | /=  | <    | <=  | >   | >=         |         |

| Adding        | +         | -   | &    |     |     |            |         |

| Unary (sign)  | +         | -   |      |     |     |            |         |

| Multiplying   | *         | 1   | mod  | rem |     |            |         |

| Miscellaneous | **        | abs | not  |     |     |            | Highest |

## **Operators and precedence**

The logical operators **and**, **or**, **nand**, **nor**, **xor** and **not** operate on values of type bit or Boolean, and also on one-dimensional arrays of these types. For array operands, the operation is applied between corresponding elements of each array, yielding an array of the same length as the result. For bit and Boolean operands, **and**, **or**, **nand**, and **nor** are 'short-circuit' operators, that is they only evaluate their right operand if the left operand does not determine the result. So **and** and **nand** only evaluate the right operand if the left operand is true or '1', and **or** and **nor** only evaluate the right operand if the left operand is false or '0'. The relational operators =, /=, <, <=, > and >= must have both operands of the same type, and yield Boolean results. The equality operators (= and /=) can have operands of any type. For composite types, two values are equal if all of their corresponding elements are equal. The remaining operators must have operands which are scalar types or one-dimensional arrays of discrete types.