## 디자인 코너

# ISSP — 중간 물량 위한 새로운 고성능 ASIC 기술

#### By Christoph Hecker

Product Marketing Engineer

NEC Electronics-Europe

E-mail: christoph.hecker@vdma.org

이제까지 주문형 회로의 개발을 위한 주된 접근 방법은 스탠다드 셀 IC, FPGA 및 게이트 어레이의 세 가지였다. 이세 기술은 저마다 특정 애플리케이션에 있어서 장단점을 가지므로 개별적인 개발 프로젝트마다 이러한 장단점들을 신중하게 가늠해야 한다.

#### ISSP의 등장

스탠다드 셀 IC는 예컨대 최적의 면적 효율로 최고의 성능을 달성할 수 있도록 해준다. 이러한 결과는 상당한 개발 자원을 투자해야만 얻을 수 있다. 스탠다드 셀 IC의 설계에서는 기능성을 확보하는 것만으로는 부족하다. 공정 기술에 대한 요구도 끊임없이 증가하고 있기 때문이다. DSM(deep sub-micron) 성능 클래스(디자인 물 0.25 ㎞ 이하의)에서 디자이너가 맞닥뜨리게 되는 효과들은 엄청난 노력을 추가적으로 기울여야만 처리할 수 있다. 이러한 DSM 효과들(예컨대 이주, 안테나 효과 같은)은 끊임없이 더 작아지는 구조물들의 물리적 특성 때문에 일어난다. 이 효과들

그림 1: ISSP는 0.13 m 기술로 최대 300 MHz의 높은 시스템 주파수를 제공한다.

을 설계 과정의 백엔드에서 특수한 개발 툴들로 처리하는 것은 이 때문이다. 이러한 툴들을 다루려면 세부적인 노하우가 필요하므로 NEC사에서는 고객들을 대신하여 이러한 일들을 수행하고 있다. 그러나이같은 지원을 제공한다 해도 개발자 자신이 이 분야에 대해 깊은 노하우를 가질수록 최적의 디자인(면적 최소화와 성능 최적화라는 면에서)을 얻게 될확률은 당연히 더 높아질 수 밖에 없다.

수반되는 노력 때문에 디자인 턴어라운드 시간 (TAT)은 프로젝트 계획의 성공을 결정 짓는 요소들 가운데 하나가 된다. 또 하나 고려하지 않으면 안될점은 스탠다드 셀 IC와 관련된 일회성 혹은 비경상성 엔지니어링(NRE) 비용이다. 주로 포토리소그래피 마스크의 제작을 위한 이러한 비용은 디자인 룰인.18 ㎞ 이하의 마스크일 경우 손쉽게 수십만 유로를 넘을 수 있다. 이를 벌충하는 길은 그에 해당하는 만큼 많은 칩들을 파는 것 뿐이다.

FPGA (field programmable gate array) 제조업체가 등장하는 것은 바로 이 장면이다. 이들은 일견 훨씬 저렴해 보이는 솔루션들을 제공한다. 스탠다드 셀IC와 게이트 어레이에 비해 FPGA는 프로그램할 수있다는 이점이 있어 마스크 비용이 절감된다. 이는 개발 단계나 시스템 테스트 단계에서는 이점이 된다. 이 단계에서도 별다른 추가 비용 없이 디자인을 수

정할 수 있기 때문이다. 그러나 FPGA 역시 매우 복잡한 디자인들을 집적시키기 위해서는 상당한 노력이 요구된다. 게다가 스탠다드 셀 IC에서 일반적으로 달성할 수 있는 높은 시스템 주파수를 FPGA로는 거의 얻기가 힘들다. FPGA가 자랑해 마지 않는 비용상의 이점도 일단 대량 생산에 착수하게 되면 사라지고 만다. 처음에는 그토록 매력적으로 보이던 FPGA의 여러 면들이 이 때부터는 심각한 단점들을 드러내기 시작한다. 프로그램이 가능하다는 것은 더 넓은 실리콘 면적을 사용해야 하고, 전력 소모가 더 크며 더 많은 수의 핀들을 수용하기 위해 더 크고 비싼 패키지를 사용하지 않으면 안됨을 뜻한다. 비교적 적은 물량일 경우라 해도 마스크 프로그래머블 ASIC 솔루션이 대량 생산에 있어서는 보다 저렴한 기술임이 입증되고 있다.

스탠다드 셀 IC에 비해 게이트 어레이 기술은 디자이너들에게 기성품 게이트 구조, 예컨대 금속배선층을 제외하고는 완성되어 있는 "시-오브-케이트" 아키택처의 웨이퍼를 제공한다. 할 일이라곤 단지 금속배선층에서 게이트들을 배선함으로써 주문형 회로를 구현하는 것뿐이다. 이 기술은 스탠다드 셀 IC에 비해 면적 효율과 성능이 낮다는 단점이 있다. 반면에, 게이트 어레이의 개발 비용은 스탠다드 셀 IC의 경우보다 훨씬 적다. 회로 구현에 필요한 것이라곤 금속배선층을 추가하는 것 뿐이기 때문이다. 따라서 설계 단계도 크게 줄어든다. 게이트 어레이의 개발 노력도 매우 적게 든다. 그 대부분을 자동화할 수 있기 때문이다. 예를 들어, NEC의 경우에는 "시-오브-케이트" 아키택처를 토대로 한 디자인 물 0.25 ㎞까지의 게이트 어레이 기술들을 제공하고 있다. 이 기술들은 제품이 대량 생산에 들어가는 순간 FPGA보다 명백한 비용상의 이점들을 보여 준다. 이 기술들은 특히 FPGA 디자인들을 게이트 어레이 기술들로 전환시키는 것을 목표하고 있기도 하다. 게이트 어레이로 달성할 수 있는 시스템 주파수는 현재의 FPGA 기술로 가능한 정도를 상회한다.

그럼에도 불구하고 최근까지는 고객이 높은 시스템 주파수(150 MHz 정도부터)의 ASIC을 신속하게 원할 경우 스

탠다드 셀 IC 말고는 비용 효율적인 다른 대안이 사실상 없었다.

### 고성능, 저비용의 ISSP

NEC의 ISSP(Instant Silicon Solution Platform)는 이러한 갭을 메워준다. ISSP는 0.13 때 기술로 최고 300 MHz의 시스템 주파수라는 높은 시스템 성능을 제공한다. 그 비경상성 비용은 스탠다드 셀 IC를 이용한 유사한 디자인에 비해 십분의 일 밖에 안 된다. 이와 동시에 단위 비용도 유사한 FPGA보다 몇 배나 더 저렴하다. 0.13 때 ASIC 디자인에서 전형적으로 보게 되는 여러 공정 관련 문제들도 새로운 접근 방법을 통해 피할 수 있으므로, 디자이너는 실제 회로의 구현에만 신경 쓰면 된다. 게다가 ISSP 디자인은 대량생산 단계로 극히 신속하게 옮겨갈 수 있다. 설계 턴어라운드 시간이 첫 샘플에 약 일 주일, 대량 생산에 추가로 한 달 밖에 걸리지 않는 것이다!

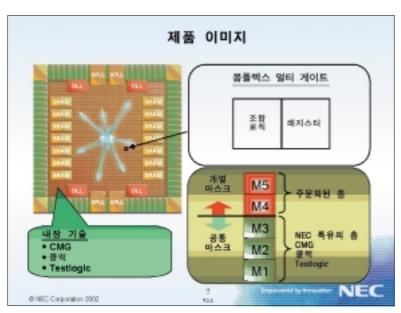

ISSP는 NEC의 CB-12 스탠다드 셀 ASIC 기술에 사용되는 것과 동일한 공정을 토대로 하고 있다. 이 솔루션이 제공하는 디자인 룰 0.13 ㎜의 기술은 소량 생산의 경우에도 대량 생산의 경우와 동일한 비용 효율성을 제공할 수 있다. ISSP제품 시리즈는 현재 집적 밀도가 서로 다른 세 가지 크기의 마스터들을 포함하고 있다(그림 2).

새로운 ISSP 접근 방법을 위해 NEC는 조합 및 순차적 부분으로 구성되어 있는 CMG(complex multi gates)를 개발했다. CMG를 이용하여 DSM 효과의 제약 없이 실제 회로를 보다 높은 추상화 수준에서 구현할 수 있다. 복잡한

마스터 라인업

Type1

미스터 라인업

N스타 사용가는 해당 SRAM PRG 등에 등록을 다 (1964)

A 227K 16 233

B 538K 49 233

C 1,168K 64 233

C 1,168K 64 233

그림 2: 이 제품 시리즈에 포함되어 있는 세 가지 크기의 마스터들

게이트 구조를 이런 식으로 사전정의하므로, DSM 효과는 더 이상 디자인의 구현에 영향을 미치지 않는다.

CMG 외에도 ISSP는 사전통합되어 있으며 고객이 구성할 수 있는 최대 1 메가비트의 SRAM을 ISSP 마스터 하나에 포함하고 있다. 각각의 마스터들은 최고 400 MHz의 출력 주파수를 갖는 네 개의 아날로그 PLL(phase-locked loo)과 최대 16 개의 DDL(digital-locked loops)을 갖추고 있는데, 이것은 DDR 인터페이스의 슬레이브로 사용할 수 있다.

#### DFT, DSM도 문제 없어

오늘날의 FPGA 기술들은 100 MHz 이상의 시스템 수준에서는 사실상 사용할 수가 없다. 이 정도 수준의 성능을 필요로 하는 고객들이 스탠다드 셀 ASIC 기술을 사용할 수밖에 없었던 것은 이 때문이다. 스탠다드 셀 ASIC 개발 기술을 사용할 때 최초의 기능 검증은 대개 매우 고가의 FPGA 기반 하드웨어 에뮬레이터나 FPGA 개발 보드를 이용하여 실행하게 된다. 그리고 나서 하드웨어 기술 내용을스탠다드 셀 IC로 옮긴다. 이러한 접근 방법은 대개 회로의기능 검증은 수행하지만 실시간 검증은 아니므로 그 성능수준이 최종적인 스탠다드 셀 IC에 의해서만 확정된다는

위험부담을 본질적으로 안고 있다. ISSP는 클럭 배선을 위한 새로운 개념을 제공한다. 클럭은 사전 배선되어 있으며 매우 균형이 잘 잡혀 있으므로 최고 300 MHz(전역적)와 최고 400 MHz(국부적)의 시스템 주파수를 달성할 수 있다. 최대 두 개의 전역 클럭과 여덟 개의 국부적 클럭들을 이 클럭 시스템에 연결할 수 있다. 따라서 ISSP는 고 성능 ASIC의 설계에 무엇보다도 적합하다.

또 다른 중요한 문제는 테스트를 고려한 설계(DFT)이다. 이는 회로 개발의 초반부터 포괄적인 테스트 방법들을 구현한다는 뜻이다. ISSP는 사전 구현한 주사 기술을 통해서 백 퍼센트에 가까운 테스트성을 달성한다. 아울러, 기존의 프리디퓨즈(prediffused) SRAM을 위한 BIST(built-in self test) 방법과 입력 및 출력 신호를 위한 경계주사 로직을 제공한다. 따라서 ISSP 기반의 회로 디자인은 완전한 테스트를 마친 ASIC을 제공하며, 그 실제적인 작업은 모두 NEC가 수행한다. 테스트 로직 전체는 ISSP 마스터 상에 통합 및 프리디퓨즈된다.

ISSP는 필연적으로 스탠다드 셀 IC보다 넓은 칩 면적을 사용할 수 밖에 없는데, 이는 모든 CMG가 항상 전부 사용되는 것은 아니기 때문이다. 반면에, ISSP는 CB-12 스탠다드 셀 ASIC 기술을 토대로 개발되었기 때문에, 주문 물량이 늘어나고 면적이 절대적으로 최적화된 디자인이 요구될 경우 디자인을 스탠다드 셀 IC 기술로 옮기기가 비교적 간단하다.

NEC는 처음에는 TBGA(tape-automated bonding ball grid array) 패키지를 제공하지만, 가까운 장래에 QFP(quad flat package)는 물론 플립칩 BGA와 같은 다른 BGA 패키지들을 포함하도록 포트폴리오를 확장할 예정이다.

NEC의 ISSP가 등장함으로써 고객들은 높은 개발 비용을 만회하기에는 물량이 너무 적어 제외하던 애플리케이션들에 고성능 ASIC을 사용할 수 있게 되었다. ISSP는 고성능 ASIC을 원하지만 그 물량이 적거나 중간 정도에 그치는 고객들에게 이상적인 솔루션인 것이다. □