## **Prescaled Counters**

in FLEX 8000 Devices

June 2000, ver. 1.01

**Application Brief 124**

## **Summary**

Prescaled counters are counters that are specifically designed for high-frequency counting. Prescaled counters achieve their high performance because only the least significant bits (LSBs) transition at higher frequencies, while the most significant bits (MSBs) have more time to prepare for their transitions. FLEX 8000 devices can implement prescaled counters at frequencies of up to 142.9 MHz for counters of up to 16 bits. Design techniques described in this application brief can be used to create design files optimized for the following characteristics:

| Design | Design Goals: |              | Design Results: |             |             |

|--------|---------------|--------------|-----------------|-------------|-------------|

| Arch   | itecture      | Optimization | Width           | Logic Cells | Speed (MHz) |

| ✓ L00  | k-Up Table    | Routability  | 8 Bits          | 37          | 142.9       |

| Prod   | duct Term     | ✓ Speed      | 16 Bits         | 101         | 142.9       |

|        |               | Area         | 32 Bits         | -           | _           |

## Prescaled Counters

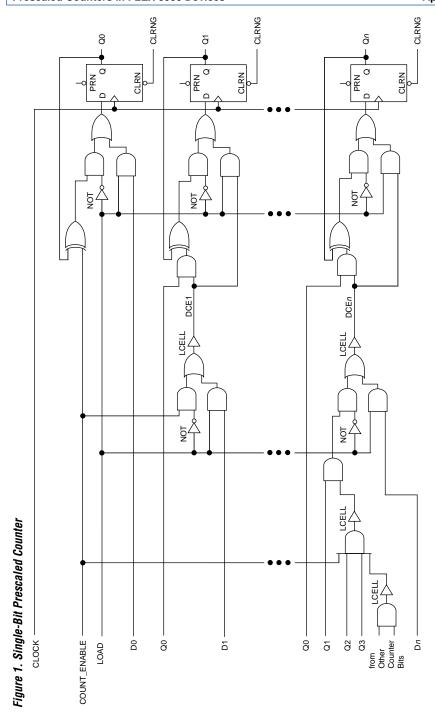

Figure 1 shows a single bit of a prescaled counter implemented in a FLEX 8000 device. When binary counters are clocked, each counter bit is driven low if all of its LSBs are high. However, since all but the LSB will have been high in the previous Clock cycle, the performance-critical path is from the LSBs (Q0) to all other register bits. In fact, the MSBs will have been high for several Clock cycles.

To achieve the maximum possible counting frequencies, the loading of prescaled counters occurs outside of the speed-critical path. With this implementation, synchronous loading of a prescaled counter requires multiple Clock cycles. Loading functions are typically not required but are frequently used to divide very-high-speed incoming Clocks.

To achieve the highest performance, the two LSBs (Q0 and Q1) are repeated in each Logic Array Block (LAB) of this counter. By replicating these bits, the only interconnect delay in the performance-critical path is the local LAB interconnect of 1 ns. Thus, the speed-critical path for each bit requires only 7 ns (or 142.9 MHz). When fast Clock speed is the most important consideration, you can use additional logic resources to ensure the maximum possible performance.

## Revision History

Revision 1.01 of *Application Brief 124: Prescaled Counters in FLEX 8000 Devices* supersedes all other previous versions. In this revision, references to the Altera BBS were removed.

Altera Corporation Page 151

Copyright © 1995, 1996, 1997, 1998, 1999, 2000 Altera Corporation, 101 Innovation Drive, San Jose, CA 95134, USA, all rights reserved.

By accessing this information, you agree to be bound by the terms of Altera's Legal Notice.