# 高速動作ボードの設計

1998年1月 ver.2 Application Note 75

# イントロダク ション

高速で動作するプリント基板 (PCB)を正常動作させるためには、デバイス、PCB、その他のエレメントを適切に集積化しなければなりません。アルテラのデバイスは、1~3 ns以下の立ち下がり時間となる高速のI/Oピンを持っています。こうした高速のスルー・レートはノイズの生成、信号の反射、クロストーク、グランド・バウンスなどを引き起こす可能性があるため、ボードの設計にあたっては以下のような対策が必要になります。

- すべてのデバイスに均等に電源を供給し、フィルタリングを行ってノイズを低減する。

- 信号線と伝送線を終端し、信号の反射を低減する。

- 平行した配線パターン間のクロストークを最小に抑える。

- グランド・バウンスの影響を減少させる。

# 電源のフィル タリングと分 配

すべてのボードとデバイスに対して均等に分配されたクリーンな電源を供給することにより、システム・ノイズを大幅に低減することができます。

## ノイズのフィルタリング

電源によって生成される低周波(<1kHz)ノイズを低減するため、PCBと電源が接続される箇所、および各デバイスと電源が接続される各箇所で、ノイズをフィルタリングする必要があります。アルテラは、電源供給ラインがPCBに接続される地点の近傍に100-μFの電解コンデンサを配置することを推奨しています。電圧レギュレータを使用している場合は、デバイスにV<sub>CC</sub>を供給している最終段の近傍にキャパシタを配置して下さい。キャパシタは電源から低周波ノイズを取り除くだけでなく、回路上における出力信号の同時多動作スイッチング時の過電流の対策にもなります。

PCB上の部品はプリント基板の電源プレーンに高周波ノイズを重畳させる可能性があります。アルテラでは、デバイスの各V<sub>CC</sub>とGNDペアのできるだけ近くにデカップリング・キャパシタを接続して、高周波ノイズをフィルタリングすることを推奨しています。

バイパス・キャパシタについては、このデータブックの「Operating Requirements for Altera Devices Data Sheet (日本語版「アルテラ・デバイスの使用上の注意」)を参照してください。

### 電源の分配

電源の分配方法もシステムのノイズに影響を与えます。電源は電源プレーン または電源のバス・ラインのいずれかを通じてPCB上に分配されます。

もっとも経済的な方法は、通常の 2 倍またはそれ以上の幅のメタル・ラインの配線パターンでデバイスの $V_{CC}$ およびグランドを接続する電源用のバス・ラインのネットワークを構成することです。通常、このバス・ラインで電源を供給する方法は 2 層のPCBに採用され、低コスト化を実現することができます。このときの配線幅は可能な限り広くしなければなりませんが、これはPCBの実装密度によって制限されます。電源のバス・ラインは大きなDC抵抗を持っており、バスの最終段に接続されているデバイスに供給される $V_{CC}$ の値が最大0.5-V程度低下する可能性があります。

アルテラは専用のプレーンを使用して電源の分配を行うことを推奨しています。電源専用のプレーンを設ける方法は多層基板で使用され、デバイスと接続されるV<sub>CC</sub>とグランドのプレーンは2層またはそれ以上のメタル層で構成されます。電源プレーンはPCB全面に引き詰められるため、そのDC抵抗は非常に低い値となります。電源のプレーンは一定したV<sub>CC</sub>の値を保つことができ、すべてのデバイスに均等に電源を分配することができるだけでなく、同時に非常に高い電流シンク能力、耐ノイズ特性、PCB上のロジック信号のシールド効果も実現します。

# 信号線と伝送 線の終端

PCBの電源の供給方法を確定した時点で、次にデバイスと配線のレイアウトを考慮しなければなりません。PCBの材質によっては、信号の高速エッジ・レートによってノイズやクロストーク、グランド・バウンスなどが発生する可能性があります。

各PCBの材質には相対誘電定数(Er)が与えられており、これは1対の伝導素子のキャパシタンスにおける絶縁体の効果を真空状態の場合と比較して測定した値となっています。使用される各PCBの材質によって、伝送路として取り扱わなければならない信号配線の長さが決定されます。表1は多様な誘電材質に対するErの値を表示したものです。

| 表 1 相対誘電定数      |                |

|-----------------|----------------|

| 材 料             | E <sub>r</sub> |

| Air             | 1.0            |

| PTFE/glass      | 2.2            |

| Rogers RO 2800  | 2.9            |

| CE/goreply      | 3.0            |

| BT/goreply      | 3.3            |

| CE/glass        | 3.7            |

| Silicon dioxide | 3.9            |

| BT/glass        | 4.0            |

| Polymide/glass  | 4.1            |

| FR-4/glass      | 4.1            |

| Glass cloth     | 6.0            |

| Alumina         | 9.0            |

Page 2 Altera Corporation

下記の式は、各材質の相関誘電定数 $(E_r)$ によって、信号の流れる速度  $(V_P)$  がどのように決定されるかを示しています。定数(C)は3  $\times$  108 m/sまたは30 cm/nsです。

$$V_{_{P}} = \frac{C}{\sqrt{E_{_{r}}}}$$

信号線の双方向伝搬遅延(PD)は、与えられた信号線の長さ(l)に対して下記の式で計算されます。

$$PD = \frac{l}{V_p}$$

信号があるラインをドライブしている場合、その回路は集中定数回路または分布定数回路のいずれかとみなすことができます。そして、そのどちらの回路になるかは、信号のエッジ・レート(t<sub>R</sub>)がPDの4倍を超えるかどうかで決定されます。

集中定数回路(Lumped):  $t_p < 4 \times PD$

分布定数回路(Distributed): tp>4×PD

分布定数回路はリンギング、オーバシュート、アンダシュートのある伝送路としてモデリングされます。これに対して、集中定数回路は伝送路上の電圧が同じ値になるとモデリングされます。ただし、特定ポイント間の配線に大きなインダクタンスが存在するような場合は、集中定数回路にモデリングされるシステムでもリンギングが発生することがあります。

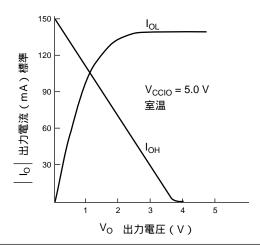

各信号の立ち上がりエッジにおけるアルテラ・デバイスのシグナル・エッジ・レートは、デバイスがドライブするキャパシタンスの値に影響されます。デバイスの容量負荷の値が判明していれば、シグナル・エッジ・レートを予測することができます。アルテラの各デバイス・ファミリのデータシートには、出力ドライブの電圧対電流の関係を示した出力ドライブ特性のグラフが含まれています。これらの出力ドライブ特性のグラフを使って、立ち上がリエッジにおけるシグナル・エッジ・レートの式をキャパシタンスの関数として導くことができます。図1はMAX®7000ファミリのデバイスの出力ドライブ特性を示しており、この図から信号のエッジ・レートを決定することができます。

### 図 1 MAX 7000デバイスの出力ドライブ特性

$I_{OL}$ のカーブで表される立ち下がりエッジはより急峻となっており、伝送路により大きな影響を及ぼします。 $I_{OL}$ の10%から90%までの領域はほぼ直線とみなすことができます。この直線部分は下記の式に近似できます。

$$I_{OL} = 0.06 V_{O}$$

キャパシタンスをチャージする時間 (t)を求める式は、下記のようになります。

$$\frac{\partial V}{\partial t} = \frac{I_O}{C}$$

$$\partial t = \frac{C}{I_{\scriptscriptstyle O}} \big( \partial V \big)$$

これにIoLの式を代入すると、下記のようになります。

$$\partial t = \frac{C}{(0.06V)} (\partial V)$$

10%から90%の領域を積分することで、立ち下がりエッジにおける信号のエッジ・レート ( $t_F$ ) が下記の式で算出できます。

$$\mathbf{t_F} = C \frac{1}{0.06} \times \ln(0.06 \text{V})|_{0.2}^{2.1} = -34.52 - (-73.71) = 39.19 \times C$$

出力の遅延時間を計算する場合は、まず最初に規定された負荷での立ち下がり時間を決定する必要があります。35pFの負荷をドライブしている場合の立ち下がり時間は、次のようになります。

$$\mathbf{t_F} = 39.19 \times (35 \times 10^{-12}) \text{sec} = 1.37 \,\text{ns}$$

Page 4 Altera Corporation

前述の通り、伝搬遅延時間 (PD) は配線長 (l)を速度 ( $V_P$ )で除算した値になります。

$$PD = \frac{l}{V_P}$$

伝送路として取り扱う必要がある線の長さ(1)は、下記の式を使用して算出できます。

$$l > \frac{t_R \times C_O}{4\sqrt{E_R}} = \frac{\left(1.37 \times 10^{-9}\right)\left(3 \times 10^8\right)}{4\sqrt{4.1}} = 5.07 \, \text{cm}$$

例えば、MAX 7000デバイスが4.96cm以上の長さとなっているガラス繊維入りのサブストレート・ラインを通じて35pFの負荷をドライブしている場合は、このラインをリンギング、オーバシュート、アンダシュートが発生する可能性がある伝送路として取扱う必要があります。 $I_{OL}$ のカーブは $I_{OH}$ よりも高速のエッジ・レートを持っており、 $I_{OL}$ が伝送路に影響を与える傾向が強くなっています。ただし、 $I_{OH}$ のほうがさらに高速のエッジ・レートとなっている場合は、 $I_{OH}$ のエッジ・レートが伝送路に与える影響の方が大きくなり、長さ(I)の計算には直線近似が使用されます。

上記の例は、MAX 7000デバイスの出力を通常のスルー・レートに設定し、 $V_{CCIO}$ を5.0-Vに接続していることを前提にしています。ここで、低速のスルー・レートにするオプションをオンに設定したり、 $V_{CCIO}$ を3.3-Vに接続することによって、MAX 7000デバイスのエッジ・レートを低下させることができます。 $V_{CCIO}$ を3.3-Vに接続した場合は、 $t_F$ の算出に3.3-Vでの出力ドライブ特性を示すグラフを使用する必要があります。

出力を低速のスルー・レートにするオプションがオンに設定されている場合は、 $t_F$ の値が増加し、新しい $t_F$ の値が下記の式から算出されます。

$\mathbf{t}_{\mathbf{F}} = (t_{OD3} - t_{OD1}) + \mathbf{t}_{\mathbf{F}}$  (上記の式で算出された通常のスルー・レートでの値)

例えば、MAX 7000Sの - 10のスピード・グレードのデバイスでは、 $t_{OD3}$ が5.5nsで、 $t_{OD1}$ が1.5nsとなっており、 $(t_{OD3}$  -  $t_{OD1}$ ) = (5.5ns - 1.5ns) = 4nsから、低速のスルー・レートでの $t_F$ の値が下記のように計算されます。

4 ns + 1.37 ns = 5.37 ns

低速のスルー・レートにするオプションをオンに設定すると、伝送路の長さを決定する (l) の値は19.89cmになります。

低速スルー・レートの設定が各デバイスの立ち上がりと立ち下がりのエッジ・レートに与える影響については、各デバイス・ファミリのデータシートで確認して下さい。

# インピーダン ス整合と終端 の方法

不整合状態にあるインピーダンスは、信号線上で前後左右に信号の反射を引き起こし、負荷でリンギングを発生させる要因となります。反射を取り除くためには、ソースのインピーダンス( $Z_0$ )が配線インピーダンス( $Z_0$ )および負荷インピーダンス( $Z_0$ )に等しくなるようにする必要があります。

通常、負荷インピーダンスは配線インピーダンスよりもかなり高くなっており、配線インピーダンスはソースのインピーダンスよりも高くなっています。不整合状態の伝送路上では、信号が負荷100%の反射を引き起こし、ソースでは約80%の反射が発生して信号が収束するまで前後にバウンドし続けます。信号の反射を低減するためには、負荷( $Z_L$ )またはソース( $Z_S$ )のどちらかのインピーダンスを配線インピーダンス( $Z_0$ )に整合させなければなりません。負荷側で並列インピーダンスを追加することによって、この入力インピーダンスを低下させ、整合を取ることができます。

並列の終端は、負荷インピーダンスを配線インピーダンスに整合させることによって最初の反射を取り除く方法です。以下に4種類の並列終端回路を示します。アルテラはテブナン並列終端または直列RC方式のいずれかを採用することを推奨します。何らかのインピーダンスの不整合が存在すると、必ず信号の反射が発生するため、各負荷に応じた終端を行って効果的な整合を実現する必要があります。

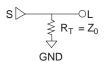

### シンプルな並列終端

シンプルな並列終端は、終端する抵抗 $(R_T)$ を配線インピーダンスに等しくなるようにする方法です。終端抵抗は負荷の近傍に配置して効率的な整合が得られるようにします。この終端による負荷電流は、Highレベルの出力で最大になります。下記に示す式により、このときの負荷電流  $(I_L)$ を推定することができます。

$$I_{L} = \frac{V_{O}}{R_{T}}$$

ドライプ電圧 ( $V_O$ ) は $I_{OH}$ の特性カーブ (4ページの図1を参照)から算出できます。 $I_{OH}$ の直線近似式から、 $V_O$ は下記のように計算されます。

$$I_{OH} = 0.15 - (0.038) \times V_{O}$$

$$V_{O} = \frac{(0.15 - I_{OH})}{0.038}$$

したがって、1.0k の終端抵抗に対する負荷電流は下記のように計算されます。

$$I_L = \frac{0.15 - I_{OH}}{0.038 \times 1,000} = \frac{0.15 - I_{OH}}{38}$$

Highレベルをドライブしている場合は、 $I_L = I_{OH}$ となるため、 $I_L$ の値は下記のようになります。

$$I_{L} = \frac{0.15}{39} = 3.85 \text{mA}$$

Page 6 Altera Corporation

負荷電流は、 $I_{OH}$ に対して4mA、 $I_{OL}$ に対して12mAとなって13mAX7000デバイスのDC特性で規定されて13mA000の出力ピン当たりの13mA00の場合、13mA0の限の限分の場合、13mA0の目の限の限の場合、13mA0のの限の限の限の表も13mA0のの限の限の表も13mA0のの限の限の表も13mA0のの限の限の表も13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うに対して13mA0のの思うになって13mA0のの思うに対して13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0の思うになって13mA0の思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0のの思うになって13mA0の思うになって13mA0のの思うになって13mA0のの思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うになって13mA0の思うなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなって13mA0の思うなのでなってなって13mA0の思うなのでなってなって13mA0の思うなのでなって13mA0の思うなのでなってなってなってなってなってなってなってなってなってなっ

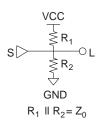

### テブナン並列終端

もう1つの並列終端方式は、テブナンの電圧分配器を使う方式です。この方式では、終端レジスタを $R_1$ と $R_2$ に分割し、結合したときの値が配線インピーダンスと等しくなるようにします。この方式はソースのデバイスから引き出す電流を減少させることができますが、 $V_{CC}$ とグランドとの間が抵抗によって結合されるため、電源からの電流が増加してしまいます。

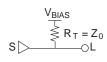

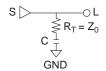

## アクティブ並列終端

アクティブ並列終端方式では、終端する抵抗  $(R_T=Z_0)$  にバイアス電圧  $(V_{BIAS})$  を接続します。このバイアス電圧は、出力ドライバが信号のHigh Lowレベルから電流を引き出せるようになる値に設定されます。ただし、この方式では、出力の伝達レートに適合した電流のシンクと電流供給を可能にするために別の電源が必要になります。

### 直列RC並列終端

並列終端方式では、抵抗とキャパシタ(直列RC)のネットワークがインピーダンスの終端に使用されます。終端抵抗 $(R_T)$ は $Z_0$ に等しくし、キャパシタは100pFよりも大きい値にする必要があります。このキャパシタは高周波信号を通過させ、低周波信号をブロックする働きをします。このため、 $R_T$ による直流負荷はドライバに影響を与えることがありません。

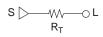

## 直列終端

直列終端方式では、各負荷でインピーダンス整合を行うのではなく、信号 ソース側でインピーダンスの整合を行います。アルテラ・デバイスの出力イ ンピーダンスは低い値となっているため、信号ソースとラインのインピーダ ンスを整合する場合は、直列のインピーダンスを付加しなければなりませ ん。

不整合状態のライン上では、信号ソースが反射を最終的に減少させて行きますが、付加された直列終端抵抗によって、2次的な反射が低減される効果があります。ライン・インピーダンスの値は負荷の分配方法によって異なります。このため、すべての条件に適合した1つの抵抗値を選択することはできません。アルテラは、ほとんどのインピーダンスに対応できる33 の直列抵抗を使用することを推奨しています。この方法は各負荷に対しての複数の部品を必要とせず、信号ソースに単一の部品だけが必要になります。ただし、この方法はRCの時定数を増加させるため、信号パスの遅延も増加させます。

# クロストーク

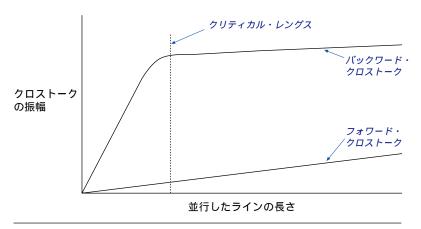

クロストークとは平行して配線された信号が、不必要な結合を起こしてしまう現象です。クロストークには2種類あり、これらはフォワード・クロストーク(キャパシティブ)とバックワード・クロストーク(インダクティブ)と呼ばれます。図2は並行する線の長さに応じて発生するそれぞれのクロストークの量を表したものです。

### 図2 並行する線の長さに対するクロストークの発生量

2本の配線パターン間で発生するフォワード・クロストークの影響は、 バックワード・クロストークの場合よりも小さくなっています。2本の長い配線パターンを平行して走らせることによって、この2線間に結合容量が生成されます。そして、一方の配線パターン上で電圧変化が生じると、この容量がもう一方の配線パターンに影響を与え、発生した電圧変化から小さな正のパルスがもう一方の配線パターンで生成されます。

バックワード・クロストークはフォワード・クロストークよりも大きな影響を与えるものであり、これは平行している配線パターンの一方の磁場がもう一方の配線パターンに信号を誘起させたときに発生します。ロジック・システムでは、信号がスイッチングしているか、またはスタティック状態でないときに配線パターンへ大きな電流が流れます。スイッチング電流によって生成される磁場は過渡的に信号の結合を引き起こします。

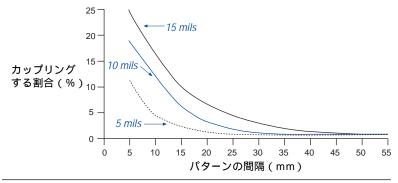

多層プリント基板のグランド・プレーンからその上の信号の配線パターンまでの間隔を10ミルに制限することによって、クロストークを大幅に低減することができます。図3はグランド・プレーンから信号プレーンまでの距離によって、パターン間の結合が変わる効果を表しています。

Page 8 Altera Corporation

# グランド・ バウンス

ディジタル・デバイスがより高速になると共に、出力のスイッチング時間はさらに短くなっていきます。さらに高速のスイッチング時間によって出力にはより大きな電流の遷移が引き起こされ、負荷のキャパシタンスがディスチャージされます。複数のデバイス出力がHighレベルからLowレベルへ同時に変化したときに発生する高電流は、グランド・バウンスとして知られている基板レベルでの現象を引き起こす可能性があります。

グランド・バウンスには多くの要因が関係しています。このため、すべてのPCBの環境における影響を予測できるような標準的なテスト方法は存在しません。デバイス自身、および各条件下での関連した相対的な要因を判断できるような環境でのみ、デバイスのグランド・バウンスをテストすることができます。プログラマブル・ロジック・デバイスでは、負荷容量、ソケットのインダクタンス、同時にスイッチングする出力の本数が、グランド・バウンスの大きさに影響を与える有力な要因となります。

### 推奨設計方法

グランド・バウンスを低減するため、アルテラは以下の対策を実行すること を推奨します。

- FLEX® 10K、FLEX 800Q FLEX 600Q MAX 900Q MAX 7000A、MAX 7000でのデザインでは、低速スルー・レートのロジック・オプションをオンに設定する。

- 74244のような バス・ドライバのICを外付けのバッファとして使用するか、バスをドライブするデバイスの数を減少させることで負荷の容量を制限する。

- 可能な限り、ソケットを取り除く。

- 同時にスイッチングする可能性のある出力信号の本数を減らす。あるい はデバイスの全体にこれらの出力ピンを均等に分配して配置する。

- スイッチングする出力をパッケージのグランド・ピンの近傍に移動させる。

- スイッチングする出力の隣にプログラマブルなグランド・ピンを設ける。

- プルアップ・レジスタを取り除くか、あるいはプルダウン・レジスタを 使用する。

- V<sub>CC</sub>、GNDのプレーンが分離されている多層基板を使用する。

- 各出力に10~30 の直列抵抗を挿入して、スイッチングする各出力に 流れる電流を制限する。

- 瞬間的にスイッチングするピンからの影響を受けないような同期設計を 行う。

「スルー・レート」のロジック・オプションをオンにしたときの詳細については、 $MAX+PLUS^8$  IIのオンライン・ヘルプを使い、"Slow Slew Rate"の項目をサーチして確認して下さい。

これらの推奨設計方法は、このアプリケーション・ノートの後半の部分で詳細に記述されており、様々なPCBの条件で高速のロジックをデザインする場合に役に立つようになっています。

### グランド・バウンスの解析

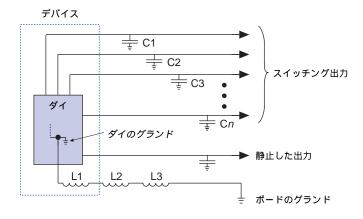

図4はグランド・バウンス解析を行うための単純なモデルを示したものです。デバイスによってドライブされる外付け部品が負荷容量(C1~Cn)としてデバイスから見えるとき、これらの負荷容量には以下の式による電荷がチャージされます。

電荷(Q)=[電圧(V) x 負荷容量(C)]

このように電圧、負荷容量が増えると、電荷量が増加します。

### 図4 グランド・バウンスのモデル

Page 10 Altera Corporation

デバイスのグランド・パスとその環境は、基本的にインダクタンス(図4のL1、L2、L3を参照)を持っています。L1は、デバイスのピンそのものと、ダイからパッケージ・ピンまでのボンディング・ワイヤによるインダクタンスです。L2は、デバイスのグランド・ピンとPCBの接続部のインダクタンスです。このL2のインダクタンス値は、デバイスがソケットを通じてPCBと接続されている場合に、もっとも大きくなります。L3は、電源に関連したグランドが接続されているプリント基板上の地点とデバイス間を接続する配線パターンのインダクタンスです。

グランド・バウンスは複数の出力信号がHighからLowに変化したときに発生します。この過渡状態では、負荷のキャパシタンスにストアされた電荷がデバイスに流れ込みます。このときデバイスに瞬間的に流れる電流( $\partial i/\partial t$ )は、 $V=L\times(\partial i/\partial t)$ によって得られる電圧(V)と基板のグランドに対するインダクタンス(L)によって表されます。基板のグランド・レベルとデバイスのグランド・レベル間の電圧差は、ロジックLowの相対的なグランド・レベルに影響を与えたり、静止している出力が一時的に立ちあがったり、バウンスする現象となって現われます。瞬間的な電流の流れは短時間ですが、このバウンスがPCB上の他のデバイスのトリガとなる大きな振幅になることがあります。

同期化されたデザインでは、同期出力が次のクロック・エッジの前で十分に 安定するため、グランド・バウンスはあまり問題になりません。また、同期 回路では静止した出力に発生するスパイクが与えられた場合でも、それがト リガとなって誤動作するようなこともありません。

グランド・バウンスはスイッチング出力と静止した出力の負荷容量によって、それぞれ異なる影響を受けます。

### スイッチング出力

スイッチング出力の負荷容量が増加すると、瞬間的なスイッチングに伴う電荷量も増加し、グランド・バウンスの振幅を増加させることになります。デバイスによって異なりますが、グランド・バウンスはデバイスの出力当たりの負荷が約100pFになるまで負荷容量を増加させます。この時点で、デバイスの出力バッファは電流を流せる最大能力に達し、誘導係数が影響する状態になります。

負荷容量を低減させ、結果的にグランド・バウンスを低減させる方法の1つは、デバイスのスイッチング出力をバス・ドライバ用のICに接続してしまうことです。バス・ドライバICの出力は十分大きな負荷容量を持っているため、デバイスの負担を軽減し、静止した出力に対するグランド・バウンスを最小にします。

バスのアプリケーションによっては、バスのデフォルト状態をHighにするためにプルアップ抵抗が使われることがあります。これらの抵抗は最大電圧までの電荷の蓄積を引き起こす原因となり、結果的にデバイスをドライブすることによってさらに大きなレベルのグランド・バウンスが生成されることになります。このため、グランド・バウンスが問題になるようなアプリケーションでは、プルアップ抵抗を取り除くか、またはプルダウン抵抗を使用したバスのロジックを構成する必要があります。

スイッチングする出力の本数もグランド・バウンスに影響を与えます。スイッチングする出力の本数が増加すると、蓄積されるトータルな電荷量も増加します。このトータルの電荷量は各スイッチング出力に蓄積される電荷の合計に等しくなります。したがって、スイッチングする出力本数の増加に応じて、グランドへシンクする必要のある電流の量も増加することになります。グランド・バウンスは、スイッチングしている出力の電圧レベルを40mV~50mV程度まで増加させます。

これらの影響を減少させるため、アルテラのデバイスには複数のペアになったVCCとGNDのピンが提供されています。グランド・バウンスを低減するため、スイッチングする出力をパッケージのGNDピンの近傍に配置して下さい。そして、同時にスイッチングする出力ピンがデバイス全体に均一に配置されるように割り当てて下さい。

スイッチングするピンがグランド・ピンの隣りに配置されるようにする場合、出力ピンがグランドのみをドライブするようにしたプログラマブルなグランド・ピンをデザイン内に作成することも可能です。この出力ピンをボード上のグランド・ピンに接続することによって、デバイスのグランドがボード上のグランドとさらに別の接続個所を持つようになり、グランド・バウンスがさらに改善されます。

多くのアルテラのデバイスには、出力ドライバのスルー・レートをコントロールすることができるオプションが提供されています。すべての出力、または低速にできる出力に対して、低速のスルー・レート・オプションをオンに設定することによって、ði/ðtを減少させ、グランド・バウンスを低減することができます。

さらにグランド・バウンスを低減するためには、デザイン内で同時にスイッチングする出力信号の本数を制限することが必要です。カウンタのような機能では、バイナリ・コードのカウンタの代わりにグレイ・コード・カウンタを用いることによって単位時間当たり1ビットだけのスイッチングにすることが可能です。

極端な例では,高速ロジック・デバイスの各スイッチング出力にそれぞれ 直列に抵抗(通常10 ~30 で十分)を挿入することによって各出力の電 流量を制限し、グランド・バウンスを許容範囲以下にすることができま す。

Page 12 Altera Corporation

### 静止した出力

静止した出力の負荷容量が増加すると、ローパス・フィルタのような動作が行われ、グランド・バウンスが軽減されます。静止した出力の負荷容量は、グランド・バウンスを200mV~300mV程度まで減少させます。ただし、静止した出力負荷容量の増加によって、容量負荷のピンがスイッチングしたときに他の静止した出力のノイズが増加することもあります。

## リード・インダクタンスの最小化

ソケットの使用とPCB上の配線パターンの長さは、10ページの図4で示されているPCBとデバイスのグランド・ピン間の結合インダクタンス、L2の値を決定する2つの要因となります。ソケットの使用はグランド・パウンスの電圧を最大100%程度まで増加させる原因となります。このため、ソケットをPCBから取り除くことによって、グランド・パウンスを大幅に低減することが可能になります。PCB上の配線パターンの長さがグランド・パウンスに与える影響は、ソケットの使用よりも小さくなります。専用のグランド・プレーンのある多層基板では、他のデバイスが接続されるシステムのリファレンス・グランドとなるPCBの位置とデバイス間を結ぶ配線パターンのインダクタンス(L3)によって生じる電圧降下が、無視できる程小さな値になります。これは、L3がL2よりもはるかに小さい値になるためです。3インチの長さの配線パターンのインダクタンスは、静止した出力に対して約100mVのグランド・バウンスを増加させます。このため、配線パターンをできるだけ短くすることが必要になります。配線パターンが長くなると、伝送線路に他のノイズを発生させる原因にもなります。

また、 $V_{CC}$ のレイヤとグランドの専用レイヤを持った多層基板を採用することによって、グランド・バウンスを低減することができます。 $V_{CC}$ とグランドをワイヤ・ラッピングしている場合は、一般的にグランド・バウンスが大きくなります。パッケージの $V_{CC}$ ピンと基板のグランド・プレーンとの間に低インダクタンスのバイパス・キャパシタを挿入することによって、不必要なインダクタンス分を低減することができます。この場合、キャパシタはパッケージの $V_{CC}$ ピンの近くに配置する必要があります。高周波特性を持ったデカップリング・キャパシタ(470PFが標準値)と標準的なデカップリング・キャパシタ(0.02 $\mu$ F $^{-}$ 0.2 $\mu$ F $^{-}$ )を並列に使用することによって、最良の結果を得ることができます。

# 参考文献

Knack, Kella. *Debunking High-Speed PCB Design Myths*. ASIC & EDA, Los Altos: James C. Uhl, July 1993.

## 日本アルテラ株式会社

〒163-0436

東京都新宿区西新宿2-1-1 新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487

http://www.altera.com/japan/

## 本社 Altera Corporation

101 Innovation Drive, San Jose, CA 95134 TEL: (408) 544-7000 http://www.altera.com

この資料はアルテラが発行した英文の資料を日本語化したものです。アルテラが各デバイスに対して保証する仕様、規格は英文オリジナルの内容です。なお、本資料に記載された内容は予告なく変更される場合があります。最新の情報はアルテラのワールド・ワイド・ウェップ・サイト(http://www.altera.com) でご確認下さい。