# APEX 20Kデバイスの プロダクト・ターム・ ロジック実現方法

1999年 4月 ver. 1.0

**Application Note 112**

# イントロダク ション

アルテラのAPEX<sup>TM</sup> 20Kデバイスはプロダクト・ターム、ルック・アップ・テーブル(LUT)、エンベデッド・メモリを 1 チップ上に統合した MultiCore<sup>TM</sup>アーキテクチャによって実現されており、System-on-a-Programmable-Chip<sup>TM</sup>の集積化を可能にしています。このMultiCoreアーキテクチャでは、プロダクト・タームによるアーキテクチャが組み合わせ回路のファンクション(アドレス・デコーダや複雑なステート・マシンなど)に対してより高い性能を提供し、一方LUTによるアーキテクチャがレジスタ付きのデータ・パス・ファンクションを優れた性能で実現します。このアーキテクチャは、プロダクト・ターム・ベースのデバイスとLUTベースのデバイスを別個に接続した場合に発生するオフ・チップ遅延を解消します。

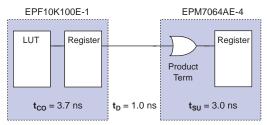

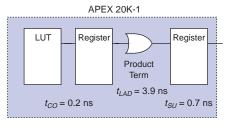

図1は、分離されたプロダクト・ターム・ベースのデバイスとLUTベースのデバイスを接続した場合のシステム性能を示したもので、ここにはボード上で発生する標準的な配線の遅延時間も含まれています。これに対して、図2はプロダクト・タームとLUTを同一チップに統合した場合のシステム性能を示したものです。

### 図1 2種類のPLDを使用した場合のシステム性能

Critical Path = 3.7 ns + 1.0 ns + 3.0 ns = 7.7 ns

### 図2 MultiCoreアーキテクチャのシステム性能

Critical Path = 0.2 ns + 3.9 ns + 0.7 ns = 4.8 ns

APEX 20Kデバイスの詳細については、APEX 20K Programmable Logic Device Familyのデータシートを参照してください。

このアプリケーション・ノートは、APEX 20Kのアーキテクチャとプロダクト・ターム・ロジックの実現方法について解説したものです。

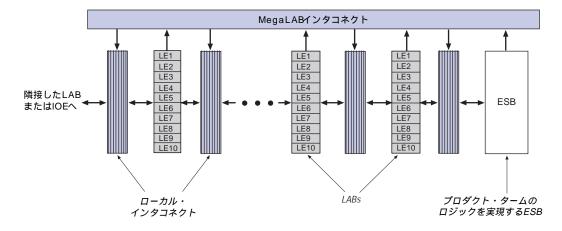

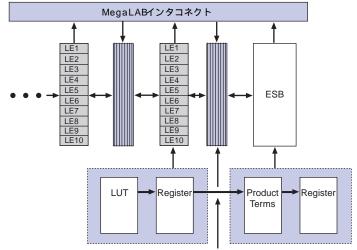

## MegaLAB構造

APEX 20Kファミリの基本ビルディング・ブロックは、MegaLAB<sup>TM</sup>と呼ばれる構造となっています。各MegaLABには、10個のロジック・エレメント(LE)で構成されるロジック・アレイ・ブロック(LAB)が16個含まれており、各LEのアーキテクチャはFLEX $^{\otimes}$ 6000デバイスのLEと等価となっています。また、APEXのMegaLAB構造にはエンベデッド・システム・ブロック(ESB)も含まれており、各ESBは2,048ビットのデュアル・ポートRAM、ROM、CAM(Content-Addressable-Memory)、または16個のプロダクト・ターム・マクロセルのいずれかにコンフィギュレーションすることができます。

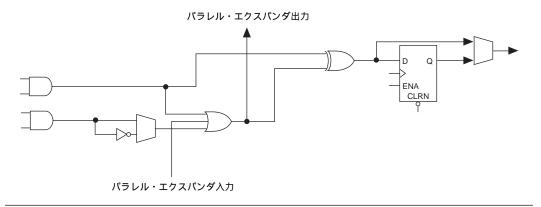

各マクロセルには、ORゲートまたはXORゲートで結合される 2 本のプロダクト・ターム、多入力のORゲート・ファンクションを実現するためのプログラマブルなインバータが内蔵されています。各マクロセルの出力はレジスタを通すことができ、各レジスタにはクロック・イネーブルと非同期クリアの機能が提供されます。また、Quartus  $^{\text{IM}}$  ソフトウェアの $^{\text{NOT-gate}}$   $^{\text{push-back}}$  のオプションを使用して、このレジスタに非同期プリセットと同じ機能を実現することもできます。さらに、ESBのマクロセルにはパラレル・エクスパンダも含まれており、隣接したマクロセルとの間でこのパラレル・エクスパンダの接続が可能になっています。パラレル・エクスパンダの接続が可能になっています。パラレル・エクスパンダウト・タームは多入力のマルチプレクサ機能や大きなファン・インを持つアプリケーションの実現にも最適なアーキテクチャとなっています。図 3 は MegaLABの構造を示したものです。

### 図3 MegaLABの構造

Page 2 Altera Corporation

### ESBにおけるプロダクト・ターム

MegaLABアーキテクチャのプロダクト・ターム部は、ESBによって実現されます。各ESBは、1つのマクロセルのブロックとして動作するように各ESBごとに個別にコンフィギュレーションすることができます。各ESBには隣接したローカル・インタコネクトから32本の入力が提供され、MegaLABインタコネクトまたは隣接したLABからESBをドライブすることができます。また、さらに高い性能を実現できるようにするため、9個のESBマクロセルの出力はローカル・インタコネクトを通じて、そのESB内にフィードバックできるようになっています。クロック専用ピンからの信号、グローバル信号、ローカル・インタコネクトからの入力信号がESBのコントロール信号として使用できます。

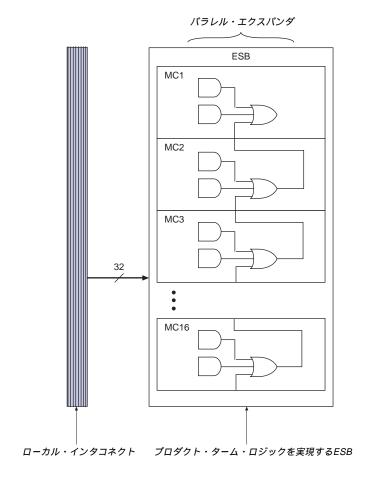

プロダクト・ターム・モードになった各ESBには、16個のマクロセルが提供されます。そして、各マクロセルは2本のプロダクト・タームと1個のプログラマブル・レジスタで構成されます。このプログラマブル・レジスタは、D、T、JK、またはSRタイプのフリップフロップが構成できます。パラレル・エクスパンダが使用できるESBのプロダクト・タームは、多入力のマルチプレクサ機能や大きなファン・インを持つアプリケーションの実現にも最適な構造となっています。図4はAPEX ESBのマクロセル構造を示したものです。

### 図4 APEXデバイスのESBマクロセル

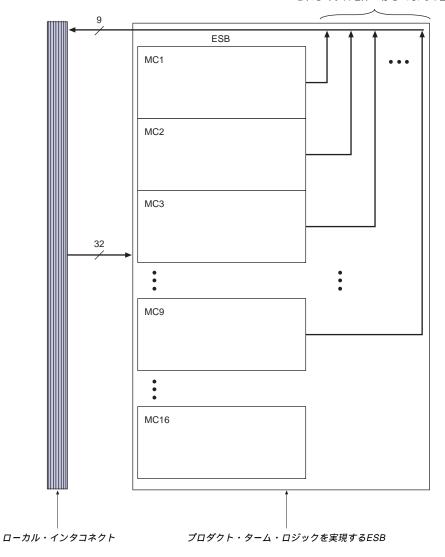

パラレル・エクスパンダを使用することで、1個のマクロセルで最大32本までのプロダクト・タームが使用可能になるため、ESBのプロダクト・タームは多入力のマルチプレクサ機能や大きなファン・インを持つアプリケーションの実現に最適な構造となっています。図5と図6は、APEX ESBのパラレル・エクスパンダとフィードバックを示したものです。

### 図5 APEX ESBのパラレル・エクスパンダ

Page 4 Altera Corporation

### 図 6 APEX ESBのフィードバック

ローカル・インタコネクトを通じてフィードバック されるマクロセル-1から-9までの出力

# プロダクト・ タームを使用 して性能を改 善する方法

MultiCoreアーキテクチャでは、プロダクト・タームをベースにしたアーキテクチャがアドレス・デコーダやステート・マシンのような組み合わせ回路のファンクションにより高い性能を提供し、一方LUTをベースにしたアーキテクチャがレジスタ付きのデータ・パス・ファンクションに対して優れた性能を提供してシステム性能を改善します。多入力のファンクションやステート・マシンのようなサブ・デザインはプロダクト・タームを使用することで、より効率的に実現できるため、2種類のアーキテクチャを同一デバイス上に統合化することによって、より高い性能とデバイス使用効率が得られます。

表1は、標準的なアプリケーションをプロダクト・タームをベースにしたアーキテクチャとLUTをベースにしたアーキテクチャで実現した場合の性能とデバイス使用効率を比較したものです。32本のプロダクト・タームを実現するためには、シリコン上に50個のLEに相当する面積が必要になります。多入力のANDゲートやステート・マシンはプロダクト・タームのアーキテクチャでより高速にまた効率的に実現することができ、またマルチプライヤやマルチプレクサはLUTで実現したほうが高速で効率的になります。

APEX ESBのプロダクトタームの遅延時間は約3.9nsで、ESBのパラレル・エクスパンダの遅延時間は約0.7nsです。

Page 6 Altera Corporation

| 表1 APEXアーキテクチャに標準的なアプリケーションを実現したときの性能と効率                |              |                                                           |              |                        |               |     |                      |

|---------------------------------------------------------|--------------|-----------------------------------------------------------|--------------|------------------------|---------------|-----|----------------------|

| ファンクション                                                 | プロダクト・ターム    |                                                           | LUT          |                        | 理想的なソリューション   |     |                      |

|                                                         | 性 能<br>(MHz) | 使用リソース                                                    | 性 能<br>(MHz) | 使用リソース                 | プロダクト・<br>ターム | LUT | 実現できる<br>性能<br>(MHz) |

| 入出カレジスタ付き32ビットAND<br>ゲート                                | 192          | 1本のプロダ<br>クト・9のLE<br>(1.6個のLE<br>に相当するダ<br>イ・サイズ)<br>注(1) | 172          | 8個のLE<br>注(1)          | <b>&gt;</b>   |     | 192                  |

| 8 ステート、 6 入<br>カ / 11出力、148<br>の 遷 移 が あ る ス<br>テート・マシン | 76           | 204本のプロ<br>ダクト・ター<br>ム (319個の<br>LEに相当する<br>ダイ・サイズ)       | 66           | 366個のLE                | <b>&gt;</b>   |     | 76                   |

| 16対 1 の入出カレ<br>ジスタ付きマルチ<br>ブレクサ                         | 149          | 20本のプロダ<br>クト・ターム<br>(30個のLEに<br>相当するダ<br>イ・サイズ)<br>注(1)  | 185          | 10個のLE<br>注 <i>(1)</i> |               | >   | 185                  |

| 8 × 8 の入出カレ<br>ジスタ付きマルチ<br>プライヤ                         | 52           | 702本のプロダクト・ターム(1,097個のLEに相当するダイ・サイズ)注(1)                  | 188          | 135個のLE<br><i>注(1)</i> |               | >   | 188                  |

#### 注:

(1) 入力のレジスタは使用されるリソースに含まれていません。

### 最適な性能を得るためのレジスタの配置

プロダクト・ターム・モードで最適な性能を得るため、プロダクト・タームをドライブするレジスタをそのESBに隣接したLAB内に配置することができます。このLABはESBと接続されるローカル・インタコネクトをダイレクトにドライブすることができるため、MegaLABインタコネクトによる配線遅延が解消されます。Quartusソフトウェアのタイミング・ドリブン・コンパイレーション機能は、ユーザが規定したタイミング要求を満足させるときにこの配置を使用します。図7を参照してください。

# 図7 ロジックの最適配置

隣接したローカル・インタコネクト

### ターボ・モードの使用

APEXのESBには、ESBに実現されたロジックの性能を改善する"ターボ"モードが提供されています。Quartusソフトウェアでは、ユーザがこのターボ・モードのオプションをオンに設定して性能を改善することができるようになっており、このオプションをオフに設定して消費電力を低減させることもできます。Quartusソフトウェアでは、このAPEX ESBのターボ・モードのオプションを各ESBごとに個別に設定することができます。

# Quartusソフトウェアを使用してプロダクト・ターム・ロジック を実現する方法

APEX 20KデバイスのデザインをサポートしているアルテラのQuartusソフトウェアでは、 ロジックの特定のブロックをプロダクト・ターム・モードのESBで実現したり、各ESBごとにプロダクト・ターム・モードを実現することができます。 QuartusソフトウェアのAssignment Organizerのダイアログ・ボックス(11ページの図11を参照)を使用して、ESBにプロダクト・ターム、LUT、RAMまたはROMを構成することができます。RAM、ROM、CAMのデザインはメガファンクションを通じて実現されます。

Page 8 Altera Corporation

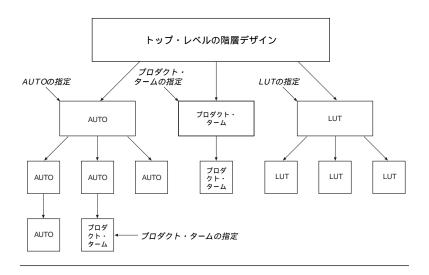

Quartusソフトウェアはプロダクト・ターム・モードのロジックを複数の方法で実現することができます。例えば、ターゲットとなる特定の階層レベルのロジックをプロダクト・ターム・モードで実現することができます。特定の階層レベルをプロダクト・ターム・モードに指定した場合、その階層レベルおよびそれより下のすべての階層レベルがプロダクト・ターム・モードを使用して実現されます。また、Quartusソフトウェアを使用して、特定の階層レベルにAUTOの指定を行うこともできます。AUTOの指定を行うと、Quartusソフトウェアは、エリア使用効率のアルゴリズム(area utilization algorithm)にしたがって、ロジックをプロダクト・タームで実現したほうが良いか、LUTで実現したほうが良いかを自動的に判断します。また、ある特定の階層より下のレベルに上の階層レベルとは異なるロジックの実現方法を指定することもできます(上の階層がLUTまたはAUTOに設定されている場合に限る)。

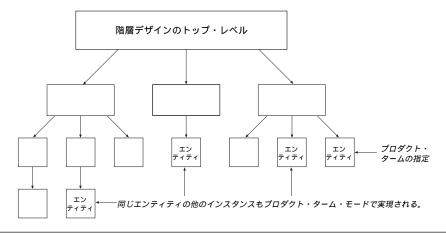

図8は、Quartusソフトウェアがプロダクト・ターム・モードを各階層にどのように実現できるかを示したものです。

### 図8 階層単位での指定

プロダクト・ターム・モードにするロジックは、グローバルまたは各エンティティごとに指定することができます。ある特定のエンティティに対してプロダクト・ターム・モードを指定することもできます。デザイン内でプロダクト・ターム・モードに指定されたエンティティがインスタンス化されている場合は、Quartusソフトウェアが他のインスタンスもプロダクト・ターム・モードで実現されるようにするオプションを提供します。

図9は、Quartusソフトウェアがプロダクト・ターム・モードのロジックを 各エンティティごとにどのように実現できるかを示したものです。

### 図9 エンティティ単位での指定

Quartusソフトウェアを使用して、特定の階層レベルに対してプロダクト・ターム・モードを指定するときは、以下の手順で行います。

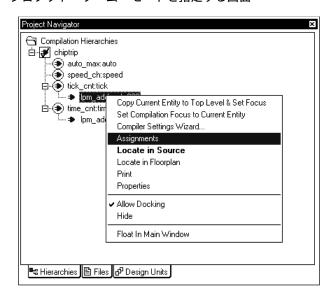

- 1. QuartusソフトウェアのProject Navigatorをオープンします。

- 2. 目的の階層レベルを右クリックし、Assignmentsを選択します。 図10を参照してください。

### 図10 プロダクト・ターム・モードを指定する画面

Page 10 Altera Corporation

- 3. Options for Entities Onlyにあるファイルのリストをオープンし、Assignment Organizerのダイアログ・ボックスでTechnology Mapperの項目を選択します。この選択でロジックが指定されたモードにマッピングされます(図11を参照)。

- 4. Settingのドロップ・ダウン形式のリスト・ボックスから、Ptermを選択し、Add/Changeをクリックします。

- 5. Applyをクリックしてアサインメントの調整を継続するか、OKをクリックして終了します。

### 図11 Assignment Organizerのダイアログ・ボックス

### サード・パーティのソフトウェア・サポート

Quartusソフトウェアは、エグゼンプラ・ロジック、シノプシス、シンプリ シティ、ビューロジックの各社の合成ツールで作成されたプロダクト・ ターム・ロジックをサポートしています。Quartusソフトウェアは真の WYSIWYG (What-You-See-Is-What-You-Get) オプション機能を提供して おり、サード・パーティのツールを使用してプロダクト・タームのロジッ クをAPEXのESBアーキテクチャに合成することができます。合成された各 ロジックのブロックはさらに合成されることなくQuartusのコンパイラに受 け渡されるため、最適化されたデザインが確保されます。WYSIWYGによる プロダクト・ターム構造はサード・パーティ・ツールからVerilog HDL、 EDIFおよびVHDLのファイルを通じてQuartusソフトウェアに受け渡されま す。また、プロダクト・ターム・モードのESBだけでなく、LUTによるロ ジック、ESB RAMおよびROMもサード・パーティのツールからアクセスす ることができます。

### まとめ

アルテラのAPEX 20Kデバイスは、プロダクト・ターム、LUT、エンベデッ ド・メモリの各アーキテクチャを1チップに集積したMultiCoreアーキテク チャを実現しています。MultiCoreアーキテクチャを使用することで、デザ インを1デバイス上に集積化することができるため、システム性能を大幅 に改善することができます。

APEX 20KデバイスおよびQuartusソフトウェアの詳細については、 「APEX 20K Programmable Logic Device」、「Quartus Programmable Logic Development System & Software」の各データシートをご覧ください。

Altera、APEX、APEX 20K、EPF10K100E、EPM7064S、FLEX、FLEX、6000、MegaLAB、MultiCore、Quartus、System-on-a-Programmable-Chipは、Altera Corporationの米国および該当各国におけるtrademarkまたはservice markです。この資料に記載されているその他の製品名、商標は該当各社 のtrademarkです。 Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard NSY warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Copyright © 1999 Altera Corporation. All rights reserved.

### 日本アルテラ株式会社

〒163-0436

東京都新宿区西新宿2-1-1 新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487 http://www.altera.com/japan/

E-mail: japan@altera.com

### 本社 Altera Corporation

101 Innovation Drive. San Jose, CA 95134 TEL: (408) 544-7000 http://www.altera.com

この資料に記載された内容は予告なく変更されることがあります。最新の情報は、アルテラのウェッブ・サイト(http://www.altera.com)でご 確認ください。この資料はアルテラが発行した英文のアプリケーション・ノートを日本語化したものであり、アルテラが保証する規格、仕様は英文 オリジナルのものです。