## **FLEX 10KE**

エンベデッド・プログラマブル・ ロジック・ファミリ

1999年 5 月 ver. 2 Data Sheet

# 特長

# Preliminary Information (暫定仕樣)

シングル・デバイス内にSystem-on-a-Programmable-Chip<sup>TM</sup>の集積化を実現するエンベデッド・プログラマブル・ロジック・デバイス(PLD)ファミリ

- 拡張強化されたエンベデッド・アレイにより、効率的なメモリや特殊な論理機能などのメガファンクションを実現

- エンベデッド・アレイ・ブロック (EAB) あたり最大16ビットまで のデータ幅が実現可能なデュアル・ポート構造

- 汎用ロジック機能を実現するためのロジック・アレイ

#### ■ 高集積

- 30,000から200,000標準ゲート(表1と表2を参照)

- EABあたり4,096ビット、最大98,304ビットまでのRAMをロジック のリソースを減少させることなく使用可能

#### ■ システム・レベルの機能

- MultiVolt<sup>TM</sup> I/Oピン機能により、2.5V、3.3V、5.0Vデバイスとの インタフェースをサポート

- 低消費電力

- 最高250MHzまでの高性能を実現する双方向 $I/O(t_{SU} \geq t_{CO})$

- Peripheral Component Interconnect Special Interest Group (PCI SIG)のPCI Local Bus Specification, Revision 2.2で規定されている33MHzまたは66MHzの3.3V動作仕様に完全準拠

- -1スピード・グレードのデバイスは、*PCI Local Bus Specification,* Revision 2.2で規定されている5.0V動作仕様に完全準拠

- IEEE Std. 1149.1-1990仕様に準拠したJoint Test Action Group (JTAG)のバウンダリ・スキャン・テスト(BST)回路を内蔵 し、デバイス内のロジック・リソースを使用することなくJTAG BST回路が使用可能

| 表1 FLEX 10KEデバイスの機能 |           |                        |            |  |  |

|---------------------|-----------|------------------------|------------|--|--|

| 機能                  | EPF10K30E | EPF10K50E<br>EPF10K50S | EPF10K100B |  |  |

| 標準ゲート数 注(1)         | 30,000    | 50,000                 | 100,000    |  |  |

| 最大システム・ゲート数         | 119,000   | 199,000                | 158,000    |  |  |

| ロジック・エレメント ( LE ) 数 | 1,728     | 2,880                  | 4,992      |  |  |

| EAB数                | 6         | 10                     | 12         |  |  |

| トータルRAMビット数         | 24,576    | 40,960                 | 24,576     |  |  |

| 最大ユーザI/Oピン数         | 220       | 254                    | 191        |  |  |

| 表 2 FLEX 10KEデバイスの機能 |            |            |                          |

|----------------------|------------|------------|--------------------------|

| 機能                   | EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |

| 標準ゲート数 注(1)          | 100,000    | 130,000    | 200,000                  |

| 最大システム・ゲート数          | 257,000    | 342,000    | 513,000                  |

| ロジック・エレメント (LE)数     | 4,992      | 6,656      | 9,984                    |

| EAB数                 | 12         | 16         | 24                       |

| トータルRAMビット数          | 49,152     | 65,536     | 98,304                   |

| 最大ユーザI/Oピン数          | 338        | 413        | 470                      |

#### 注:

(1) IEEE Std. 1149.1のJTAGパウンダリ・スキャン・テストを必要とするデザインには、内蔵のJTAG回路により、最大31,250ゲート分の集積度が上記の標準ゲート数に追加されることになります。

5.0VのFLEX 10Kまたは3.3VのFLEX 10KAデバイスに関する情報については、「FLEX 10K Embedded Programmable Logic」のデータシート(日本語版有り)をご覧ください。

# さらに多くの 特長

- 2.5Vの内部電源電圧で動作する最先端プロセスを採用

- 外部のコンフィギュレーション・デバイス、インテリジェント・コントローラ、またはJTAGポートを通じたイン・サーキット・リコンフィギュラビリティ(ICR)をサポート

- ClockLock<sup>TM</sup>とClockBoost<sup>TM</sup>のオプションにより、クロックの遅延 とスキューを最小に抑え、クロック周波数の逓倍機能を提供

- 低スキューのクロック分配ツリーを内蔵

- すべてのデバイスに100%実施されるファンクション・テストにより、テスト・ベクタやスキャン・チェインの作成が不要

- コンフィギュレーション実行前および実行時におけるI/Oピンのプルアップ機能

#### 柔軟性の高いインタコネクト

- 連続した配線構造により、高速で予測可能な配線遅延を実現する FastTrack<sup>®</sup> インタコネクト

- アダー、カウンタ、コンパレータのような演算機能を高速で実現する専用キャリー・チェイン (ソフトウェア・ツールやメガファンクションが自動的に使用)

- 高ファン・インの高速論理機能を実現する専用カスケード・チェイン(ソフトウェア・ツールやメガファンクションが自動的に使用)

- 内部でトライ・ステートのネットが実現できるトライ・ステート・ エミュレーション機能

- 最大6本までのグローバル・クロック信号と4本のグローバル・ク リア信号

#### ■ パワフルなI/Oピン

- 各ピンごとに設定可能なトライ・ステート出力イネーブル・コント ロール

- 各I/Oピンごとに設定可能なオープン・ドレイン出力オプション

Page 2 Altera Corporation

- スイッチング・ノイズを低減することができるプログラマブルな出 カのスルー・レート・コントロール

- ピンごとにユーザ・セレクタブルとなっている $V_{CCIO}$ へのクランプ

- 活線挿抜をサポート

- WindowsベースのPC、Sun SPARCstation、HP 9000シリーズ700/800、IBM RISC System/6000の各ワークステーション上で動作するアルテラのMAX+PLUS® II 開発システム、およびWindowsベースのPC、Sun SPARCstation、HP 9000シリーズ700のワークステーション上で動作するQuartus<sup>™</sup>開発システムによるソフトウェア・デザイン・サポートと自動配置配線

- 柔軟性に富んだパッケージ・オプションを提供

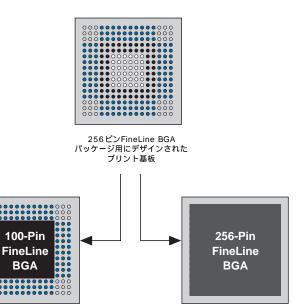

- 革新的なFineLine BGA<sup>TM</sup>パッケージを含む144ピンから672ピンまでの豊富なパッケージ・オプション(表3と表4を参照)

- デバイス集積度とピン数の異なるFLEX 10KAおよびFLEX 10KEデバイスとの間でSameFrame<sup>TM</sup>ピン互換機能を提供

- EDIF (Electronic Design Interchange Format) 2 0 0 および3 0 0 ホットリスト・ファイル、LPM (Library of Parameterized Modules)、DesignWare コンポーネンツ、Verilog HDL、VHDLなどとのインタフェースにより、デザインの入力とシミュレーションにはケイデンス、エグゼンプラ・ロジック、メンター・グラフィックス、OrCAD、シノプシス、シンプリシティ、ベリベスト、ビューロジックなどの各ベンダから供給される業界標準のEDAツールが使用可能

| 表3 FLE     | 表 3 FLEX 10KEのパッケージ・オプションとI/Oピン数 注(1)、(2)、(3) |                 |                         |                            |                |                            |                |                |                            |

|------------|-----------------------------------------------|-----------------|-------------------------|----------------------------|----------------|----------------------------|----------------|----------------|----------------------------|

| デバイス名      | 144-Pin<br>TQFP                               | 208-Pin<br>PQFP | 240-Pin<br>PQFP<br>RQFP | 256-Pin<br>FineLine<br>BGA | 356-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 599-Pin<br>PGA | 600-Pin<br>BGA | 672-Pin<br>FineLine<br>BGA |

| EPF10K30E  | 102                                           | 147             |                         | 176                        |                | 220                        |                |                | 220 (4)                    |

| EPF10K50E  | 102                                           | 147             | 189                     | 191                        | 220            | 254                        |                |                | 254 (4)                    |

| EPF10K50S  | 102                                           | 147             | 189                     | 191                        | 220            | 254                        |                |                | 254 (4)                    |

| EPF10K100B |                                               | 147             | 189                     | 191                        |                |                            |                |                |                            |

| EPF10K100E |                                               | 147             | 189                     | 191                        | 274            | 338                        |                |                | 338 (4)                    |

| EPF10K130E |                                               |                 | 186                     |                            | 274            | 369                        |                | 424            | 413                        |

| EPF10K200E |                                               |                 |                         |                            |                |                            | 470            | 470            | 470                        |

| EPF10K200S |                                               |                 | 182                     |                            | 274            | 369                        | 470            | 470            | 470                        |

#### 注:

- (1) 各パッケージの供給状況については、日本アルテラまたは販売代理店へお問い合わせください。

- (2) FLEX 10KEデバイスには、薄型クワッド・フラット・パック(TQFP)、プラスチック・クワッド・フラット・パック(PQFP)、ピン・グリッド・アレイ(PGA)、およびボール・グリッド・アレイ(BGA)の各パッケージが提供されています。

- (3) 同じパッケージのデバイスでもI/Oピン数が異なる場合がありますが、これらはピン互換で提供されます。使用デバイスを変更する可能性がある場合は、すべてのデバイスに共通になっているI/Oピンを使用してください。MAX+PLUS IIのパージョン9.1以降のソフトウェアでは、共通になっているI/Oピンのみを優先的に使用する機能がサポートされています。

- (4) このオブションは484ピンのFineLine BGAパッケージでサポートされる予定です。SameFrameマイグレーション機能を利用することによって、すべてのFineLine BGAパッケージにピン互換機能が提供されます。例えば、1種類のレイアウトで、256ピン、484ピン、または672ピンのFineLine BGAパッケージが使用できるポードのデザインが作成可能です。QuartusおよびMAX+PLUS II のソフトウェアは、将来のパッケージ変更のオブションが設定されたときに、自動的にピンの競合が発生しないようにピンを配置します。

| 表 4 FLEX 10KEデバイスのパッケージ・サイズ |                 |                 |                         |                            |                |                            |                |                |                            |

|-----------------------------|-----------------|-----------------|-------------------------|----------------------------|----------------|----------------------------|----------------|----------------|----------------------------|

| デバイス名                       | 144-Pin<br>TQFP | 208-Pin<br>PQFP | 240-Pin<br>PQFP<br>RQFP | 256-Pin<br>FineLine<br>BGA | 356-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 599-Pin<br>PGA | 600-Pin<br>BGA | 672-Pin<br>FineLine<br>BGA |

| ピッチ (mm)                    | 0.50            | 0.50            | 0.50                    | 1.0                        | 1.27           | 1.0                        | -              | 1.27           | 1.0                        |

| 面積 (mm²)                    | 484             | 936             | 1,197                   | 289                        | 1,225          | 529                        | 3,904          | 2,025          | 729                        |

| 長さ×幅<br>(mm×mm)             | 22 × 22         | 30.6 × 30.6     | 34.6 × 34.6             | 17 × 17                    | 35 × 35        | 23 × 23                    | 62.5 × 62.5    | 45 × 45        | 27 × 27                    |

## 概要

アルテラのFLEX 10KEデバイスは、従来のFLEX 10Kデバイスの機能をさらに拡張強化した製品です。リコンフィギュラブルなCMOSのSRAMエレメントをベースにしたFlexible Logic Element MatriX (FLEX)アーキテクチャは、一般的なゲートアレイ用メガファンクションの実現に必要なすべての機能を持っています。最大200,000ゲートの集積度を持つFLEX 10KEファミリは、複数の32ビット・バスを含むシステム全体の機能を1個のデバイスで実現するために必要な集積度、スピードそして回路機能を提供しています。

FLEX 10KEデバイスはリコンフィギュラブルとなっており、出荷前に100% テストされています。このため、設計者が故障検出用のテスト・ベクタを作成する必要がなく、デザインのシミュレーションと検証に注力できるようになります。また、FLEX 10KEデバイスでは要求される個々の機能をボード上でリコンフィギュレーションできるため、ゲートアレイの場合のようにデザインの異なるデバイスごとに在庫を管理する必要がありません。

表 5 は代表的なアプリケーションを実現したときのFLEX 10KEデバイスの性能を示したものです。すべての性能値はシノプシスのDesignWareまたはLPMファンクションを使用して得られたものです。各アプリケーションの実現には特別なデザイン・テクニックを必要とせず、使用するファンクションをVerilog HDL、VHDL、アルテラ・ハードウェア記述言語(AHDL)、または回路図デザイン・ファイル内でインスタンス化するか、記述するだけです。

Page 4 Altera Corporation

| 表 5 FLEX 10KEデバイスの性能                      |     |      |     |         |     |     |

|-------------------------------------------|-----|------|-----|---------|-----|-----|

| アプリケーション                                  | 使用リ | ソース  |     | 性 能     |     | 単位  |

|                                           | LE数 | EAB数 | ス   | ピード・グレー | ۴   |     |

|                                           |     |      | -1  | -2      | -3  |     |

| 16ビット ローダブル・カウンタ                          | 16  | 0    | 200 | 188     | 128 | MHz |

| 16ビット アキュムレータ                             | 16  | 0    | 200 | 188     | 128 | MHz |

| 16対1マルチプレクサ <i>注(1)</i>                   | 10  | 0    | 3.2 | 4.3     | 5.5 | ns  |

| 3 段パイプライン付き16 ビット・<br>マルチプライヤ <i>注(2)</i> | 544 | 0    | 93  | 86      | 64  | MHz |

| 256×16 RAMのリード・サイク<br>ル・スピード <i>注(2)</i>  | 0   | 1    | 212 | 181     | 131 | MHz |

| 256×16 RAMのライト・サイク<br>ル・スピード <i>注(2)</i>  | 0   | 1    | 142 | 128     | 94  | MHz |

注:

- (1) このアプリケーションは入出力に組み合わせ回路を使用しています。

- (2) このアプリケーションは入出力にレジスタ付き回路を使用しています。

表 6 は、FLEX 10KEデバイスをさらに複雑なデザインに使用した場合の性能を示したものです。これらのデザインはアルテラの $MegaCore^{TM}$ ファンクションとして提供されています。

| 表 6 複雑なデザインに使用された場合のFLEX 10KEデバイスの性能                                          |       |           |      |      |      |

|-------------------------------------------------------------------------------|-------|-----------|------|------|------|

| アプリケーション                                                                      | LE数   | 性能        |      |      | 単位   |

|                                                                               |       | スピード・グレード |      | ۴    |      |

|                                                                               |       | -1        | -2   | -3   |      |

| 16ピット、8TAP (Test Access Port) のパ<br>ラレルFIR (Finite Impulse Response) フィ<br>ルタ | 420   | 185       | 175  | 122  | MSPS |

| 8 ビット、512ポイントのFFT (Fast                                                       | 1,854 | 47.4      | 57.8 | 76.5 | μs   |

| Fourier Transform) ファンクション                                                    |       | 100       | 82   | 62   | MHz  |

| a16450 UART (Universal Asynchronous Receiver/Transmitter)                     | 342   | 66        | 57   | 44   | MHz  |

FLEX 10KEのアーキテクチャは、ゲートアレイ市場で急速に普及しているエンベデッド・ゲートアレイに近い構造となっています。エンベデッド・ゲートアレイに近い構造となっています。エンベデッド・ゲートアレイでは、汎用ロジックが標準的なゲートアレイと同じように一般的な"シー・オブ・ゲート"アーキテクチャの中で実現されます。また、エンベデッド・ゲートアレイは、大規模で特殊な論理機能を実現するためにダイの一部に専用のエリアを持っています。エンベデッドに実現されたアレイでは、こうした論理機能がシリコン上にエンベデッドに実現されるため、一般的なゲートアレイに比較してそのダイ・サイズが縮小され、スピードが改善されます。ただし、エンベデッドに実現されたメガファンションをカスタマイズすることは一般的に不可能ですが、FLEX 10KEデバイスはプログラマブルとなっているため、設計者はデバッグの段階で設計変更を行いながら、エンベデッド・メガファンクションと汎用ロジックの双方をフルにカスタマイズすることができます。

FLEX 10KEの各デバイスには、エンベデッド・アレイとロジック・アレイとが内蔵されています。エンベデッド・アレイは多様なメモリ機能、ディジタル信号処理(DSP)、マイクロコントローラ、多ビット幅のデータ・パス操作、データ変換などのような複雑な論理機能を実現するときに使用されます。これに対して、ロジック・アレイはゲートアレイの"シー・オブ・ゲート"と同じ機能を持っており、カウンタ、アダー、ステート・マシン、マルチプレクサなどのような汎用のロジックを実現するときに使用されます。このエンベデッド・アレイとロジック・アレイを組み合わせることによって、FLEX 10KEデバイスにはエンベデッド・ゲートアレイと同じ高い性能と集積度が提供され、システム全体を1個のデバイスで実現することができます。

FLEX 10KEデバイスはシステム電源の投入時にアルテラのシリアル・コン フィギュレーション・デバイスにストアされたデータ、またはシステム・ コントローラから供給されるデータによってコンフィギュレーションされ ます。アルテラはFLEX 10KEデバイスをシリアルのデータ・ストリームで コンフィギュレーションするためのコンフィギュレーション・デバイスと して、EPC1、EPC2およびEPC1441の各製品を供給しています。コンフィ ギュレーション・データはシステム内のRAM、アルテラのBitBlaster™、 ByteBlaster<sup>TM</sup>またはByteBlasterMV<sup>TM</sup>ダウンロード・ケーブルからダウン ロードすることもできます。(ByteBlasterケーブルは製造中止となり、 2.5V、3.3V、5.0Vの各デバイスをコンフィギュレーションおよびプログラ ムできるByteBlasterMVで代替されています。) FLEX 10KEデバイスをコ ンフィギュレーションした後、デバイスをリセットして新しいデータを ロードすることによって、イン・サーキットでリコンフィギュレーション することができます。リコンフィギュレーションに要する時間は276ms以 内であるため、システムの動作中にリアルタイムの変更を行うことができ ます。

FLEX 10KEデバイスには、マイクロプロセッサからFLEX 10KEデバイスをコンフィギュレーションするための最適化されたインタフェースが提供されており、マイクロプロセッサからシリアルまたはパラレル、同期または非同期でコンフィギュレーションすることが可能です。また、このインタフェースにより、マイクロプロセッサはFLEX 10KEデバイスをメモリとし

Page 6 Altera Corporation

て扱うことができ、バーチャルなメモリ・アドレスにデータを書き込むことによってFLEX 10KEデバイスをコンフィギュレーションすることができるため、デバイスのリコンフィギュレーションが容易に行えます。

詳細については下記の資料を参照してください。

- 「Configuration Devices for APEX & FLEX Devices」のデータシート(日本語版有り)

- 「BitBlaster Serial Download Cable」のデータシート

- 「ByteBlasterMV Parallel Port Download Cable」のデータシート

FLEX 10KEデバイスのデザインはアルテラのQuartusおよびMAX+PLUS II 開発システムによってサポートされています。これらの開発ツール は、回路図、アルテラ・ハードウェア記述言語(AHDL)を含むテキストおよび波形の各デザイン入力、コンパイレーション、論理合成、完全なシミュレーション、ワースト・ケースのタイミング解析、そしてデバイス・コンフィギュレーションまでの機能を1パッケージに統合した開発ツールです。QuartusとMAX+PLUS IIのソフトウェアはPCおよびUNIX上で動作する業界標準のEDAツールを使用したデザイン入力やシミュレーションをサポートするために、EDIF 2 0 0 および 3 0 0、LPM、VHDL、Verilog HDLなどのインタフェースも提供しています。

QuartusとMAX+PLUS II のソフトウェアは論理合成やシミュレーションに使用されるゲートアレイ用のEDAツールとも簡単にインタフェースすることができます。例えば、MAX+PLUS IIのソフトウェアはケイデンスのVerilog-XLなどのツールでシミュレーションを行うためのVerilog HDLファイルを生成することができます。また、QuartusとMAX+PLUS II には、高速のカウンタや演算機能を実現するときに使用されるキャリー・チェインのような各デバイス固有の機能を使用したEDAライブラリも含まれています。例えば、QuartusとMAX+PLUS IIと共に供給されるシノプシスのDesign Compilerのライブラリには、FLEX 10KEのアーキテクチャに最適化されたDesignWareファンクションが含まれています。

MAX+PLUS II開発システムは、WindowsベースのPC、およびSun SPARCstation、HP 9000シリーズ700/800、IBM RISC System/6000の各ワークステーション上で動作します。また、Quartus開発システムは、WindowsベースのPC、およびSun SPARCstation、HP 9000シリーズ700のワークステーション上で動作します。

詳細については、「MAX+PLUS II Programmable Logic Develop-ment System & Software」および「Quartus Programmable Logic Development System & Software」のデータシートを参照してください。

## 機能の説明

FLEX 10KEの各デバイスは、メモリや特別な論理機能を実現するための機能強化されたエンベデッド・アレイと汎用のロジックを実現するためのロジック・アレイによって構成されています。

エンベデッド・アレイは複数のEABによって構成されています。エンベデッド・アレイにメモリの機能を実現する場合は、各EABに提供されている4,096ビット分のメモリ・エレメントを使用して、RAM、ROM、デュアル・ポートRAM、またはFIFO (First-In First-Out)を構成することができます。また、ロジックを実現する場合は、各EABに提供される100ゲートから600ゲートに相当するロジックのリソースを使用して、マルチプライヤ、マイクロコントローラ、ステート・マシン、DSP機能などの複雑なロジックを構成することができます。各EABは個別に独立して使用することができ、また大規模な論理機能を実現する場合には複数のEABを結合させて使用することもできます。

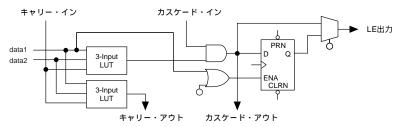

ロジック・アレイは複数のロジック・アレイ・ブロック(LAB)によって構成され、各LABは8個のLEとローカル・インタコネクトによって構成されています。1個のLEには4入力のルック・アップ・テーブル(LUT)、プログラマブルなフリップフロップが各1個含まれており、またキャリーとカスケードの機能を実現するための専用パスも含まれています。8ビットのカウンタ、アドレス・デコーダ、ステート・マシンなどのような中規模の論理ブロックは8個のLEで構成することができ、複数のLABを使用してさらに大規模な論理ブロックを構成することもできます。1個のLABは約96ユーザブル・ゲートに相当する集積度を持っています。

FLEX 10KEデバイスの内部、およびデバイス・ピンとデバイス内部との信号の接続は、デバイス全体を縦方向および横方向に走っている高速で連続したロウ・チャネルとカラム・チャネルの配線パス、FastTrackインタコネクトによって行われます。

各I/Oピンは、ロウおよびカラムのFastTrackインタコネクトの先端に配置されているI/Oエレメント(IOE)と接続されます。各IOEは双方向のI/Oバッファと入力レジスタまたは出力レジスタとして使用できるフリップフロップを持っており、デバイスの入出力信号および双方向の信号に使用することができます。専用のクロック入力ピンを使用することにより、IOEのレジスタには高い性能が提供されます。入力レジスタとして使用された場合には、2.5nsまでのセットアップ・タイムと0nsのホールド・タイムが提供されます。また、出力レジスタとして使用された場合には、3.7nsまでの「Clock-to-Output」遅延が提供されます。また、IOEにはJTAG BSTのサポート、スルー・レート・コントロール、トライ・ステート・バッファ、オープン・ドレイン出力などの多様な機能が提供されています。

Page 8 Altera Corporation

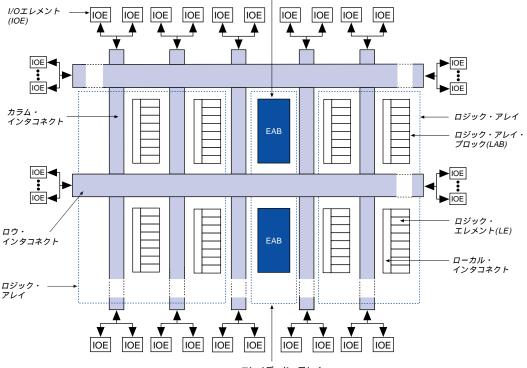

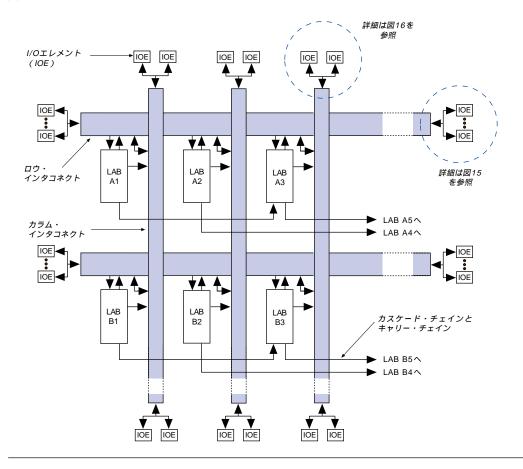

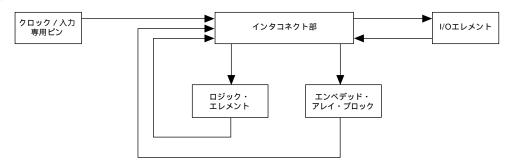

図1はFLEX 10KEのアーキテクチャをブロック図で示したものです。ここで、複数のLEのグループが1個のLABを構成しており、各LABはロウおよびカラム方向の各位置に配置されています。そして各ロウの位置には1個のEABが配置されています。LABおよびEAB間はFastTrackインタコネクトによって相互に接続されます。また、ロウとカラムのFastTrackインタコネクトの先端には複数のIOEが配置されています。

#### 図1 FLEX 10KEデバイスのブロック図

エンベデッド・アレイ・ブロック(EAB)

エンベデッド・アレイ

FLEX 10KEデバイスにはフリップフロップのコントロール入力信号をドライブすることができる6本の入力専用ピンが提供されており、高速でスキューの小さい(1.5ns以下)コントロール信号をデバイス全体に効率的に供給することができます。これらのコントロール信号の接続にはFastTrackよりも遅延が短くスキューの小さな専用の高速配線チャネルが使用されます。入力専用ピンのうちの4本はグローバル信号をドライブします。また、これら4本のグローバル信号は内部のロジックからもドライブすることができるようになっており、クロック・デバイダやデバイス内の多数のレジスタを非同期にクリアする信号の内部生成に理想的なソリューションが提供されています。

## エンベデッド・アレイ・ブロック

EABは入力と出力のポートにレジスタを持った柔軟性の高いRAMとなっており、一般的なゲートアレイ用メガファンクションを構成する場合にも使用されます。EABの提供するサイズと高い柔軟性は、マルチプライヤ、ベクタ・スケーラ、エラー・コレクション回路などのような回路機能の構成にも最適となっています。これらの回路機能はディジタル・フィルタやマイクロコントローラなどのアプリケーションに使用できます。

これらの論理機能はコンフィギュレーションの期間にリード・オンリのパターンをEABにプログラミングして1個の大きなLUTを形成することによって実現されます。LUTを使用することにより、組み合わせ回路の機能は論理演算によってではなく、このLUTの出力によって実現されます。この組み合わせ回路を実現する方法は通常のロジックの実現に使用されるアルゴリズムよりも高速となり、この高い性能はEABの高速アクセス・タイムによってさらに強化されています。また、EABの高い集積度により、FPGA(Field Programmable Gate Array)のRAMブロックや複数のLEをリンクさせた場合のような配線遅延を発生させることなく、複雑な機能を1段のロジック・レベルで実現することができます。例えば、1個のEABで8入力/16出力の任意のファンクションを実現することができます。LPMファンクションのようなパラメータ化されたファンクションは、EABの提供する利点を自動的に活用することができます。

FLEX 10KEのEABは、デバイス全体に分散した小規模なRAMブロックによってオン・ボードRAMを実現するFPGAよりもすぐれた特長を持っています。これらの小規模なFPGAのRAMブロックは、使用可能なサイズにするときに相互に接続される必要があります。そして、FPGAの複数のRAMブロックの接続にはマルチプレクサが使用されるため、さらに多くのロジック・リソースが必要となります。これらの追加されるマルチプレクサは遅延を発生させるため、RAMブロックの性能を低下させます。また、FPGAでは、大きなサイズのメモリを構成する場合に複数の小規模なRAMブロック間を接続する必要があるため、配線の問題が生じがちです。これに対してFLEX 10KEデバイスでは、大規模な専用のRAMブロックの構成にEABが使用できるため、配線やタイミングに関連した問題が解消されます。

機能が強化されたFLEX 10KEのEABには、従来のEAB構造にデュアル・ポートの動作モードが追加されています。このデュアル・ポート構造は、シングルまたはデュアル・クロックで動作するFIFOバッファの実現に最適です。また、FLEX 10KEのEABは、最大16ビット幅までのRAMブロックをサポートしており、既存のFLEX 10KのEABを使用したデザインとの互換性も実現しています。FLEX 10KEのEABは、デュアル・ポートまたはシングル・ポートのモードで動作することができます。デュアル・ポートのモードでは、EABへのライトとリードにそれぞれ別個の独立したクロックが使用され、EABに対するリードとライトの動作を異なるレートで実行することができます。また、この構造では、リードとライトが実行されるEABのセクションに対して、別個の同期クロック・イネーブル信号が提供されており、それぞれのセクションを個別にコントロールすることができます。

Page 10 Altera Corporation

また、EABは、2つのポートでリードまたはライトの動作が同時に実行される双方向のデュアル・ポート・メモリのアプリケーションにも使用できます。このようなデュアル・ポート・メモリを実現するときは、2つのポートでのリードまたはライトの同時動作をサポートするために2個のEABが使用されます。

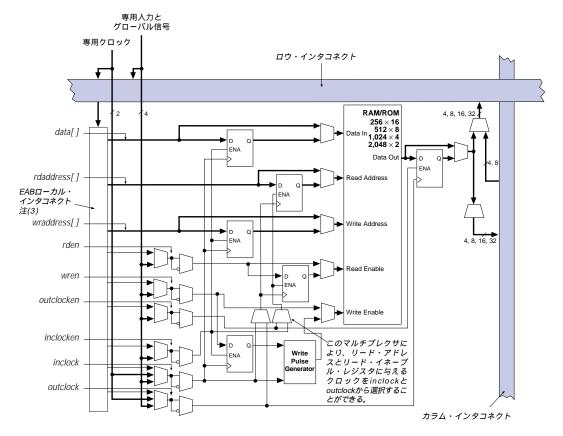

さらに、1本のクロックとクロック・イネーブル信号を使用してEABの入力 レジスタをコントロールしながら、別のクロックとクロック・イネーブル信 号で出力のレジスタをコントロールすることも可能です(図2を参照)。

## 図 2 FLEX 10KEデバイスのデュアル・ポートRAMモード 注(1)、(2)

#### 注:

- (1) すべてのレジスタは、EABローカル・インタコネクト信号、グローバル信号、またはチップ全体のリセット信号により、非同期でクリアできます。

- (2) EPF10K100Bには、デュアル・ポートRAMモードが提供されていません。

- (3) EPF10K30EとEPF10K50Eは88本のEABローカル・インタコネクト・チャネルを、EPF10K100E、 EPF10K130E、EPF10K200Eの各デバイス は104本のEABローカル・インタコネクト・チャネルを持っています。

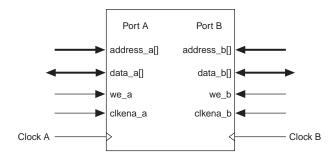

FLEX 10KEのEABは、図 3 に示す双方のポートでリードまたはライトの動作が行えるようにしたデュアル・ポートRAMのアプリケーションを実現するアルテラのメガファンクションにも使用できます。

## 図3 デュアル・ポートRAMモードにしたときのFLEX 10KEのEAB

Page 12 Altera Corporation

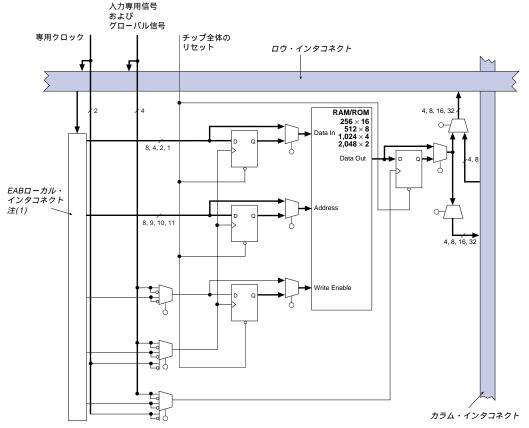

FLEX 10KEのEABは、 FLEX 10Kのデザインと互換性を持たせるときに便利となるシングル・ポートのモードもサポートしています(図 4 を参照)。

### 図4 シングル・ポートRAMモードにしたときのFLEX 10KE

注:

(1) EPF10K30E、EPF10K50E、EPF10K50Sは88本のEABローカル・インタコネクト・チャネルを、EPF10K100E、EPF10K100B、EPF10K130E、EPF10K200E、EPF10K200Sの各デバイスは104本のEABローカル・インタコネクト・チャネルを持っています。

EABは同期型のRAMの構成にも使用することができ、これは非同期型のRAMよりも簡単に実現することができます。非同期型RAMの回路ではライト・イネーブル(WE)信号を生成する必要があり、アドレスとデータの信号はこのWEに対して規定されたセットアップ・タイムとホールド・タイムを守る必要があります。これに対してEABを使用した同期型RAMは自分自身のWE信号を生成し、対応する入力またはライト・クロックに対するタイミングが取られます。セルフ・タイミング機能を持つEABのRAMでは、守られる必要があるタイミングは、グローバル・クロックに対して規定されているセットアップ・タイムとホールド・タイムのみとなります。

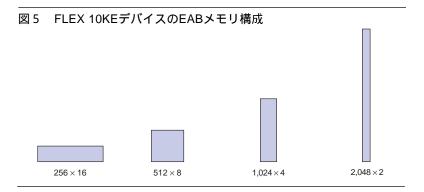

EABをRAMとして使用した場合、そのメモリ構成を $256 \times 16$ 、 $512 \times 8$ 、 $1,024 \times 4$ 、または $2,048 \times 2$ のいずれかに設定することができます(図 5 を参照)。

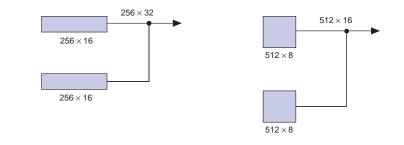

複数のEABを接続することによって、さらに大規模なメモリを構成することができます。例えば、2個の256×16のRAMを接続して256×32の構成にしたり、2個の512×8のRAMを接続して512×16の構成にすることもできます(図6を参照)。

### 図 6 FLEX 10KEデバイスの複数のEABを接続した例

必要に応じて、デバイス内のすべてのEABをカスケード接続して1個のRAMを構成することも可能です。タイミングに影響を与えることなく、すべてのEABをカスケード接続して、最大2,048ワードまでのRAMを構成することができます。QuartusとMAX+PLUS IIのソフトウェアは指定されたRAMを実現するために必要となる複数のEABを自動的に接続します。

Page 14 Altera Corporation

EABはクロックのドライブとコントロールのために柔軟性の高いオプションを提供しています。EABへのリードとライトの動作には異なるクロックとクロック・イネーブル信号を使用することができます。データの入力、EABの出力、ライト・アドレス、ライト・イネーブル信号、リード・アドレス、およびリード・イネーブル信号には、個別にレジスタを挿入することができます。グローバル信号とEABのローカル・インタコネクトはWE、RE、クロック・イネーブルの各信号をドライブすることができます。また、EABのクロック信号は、専用のクロック入力ピン、グローバル信号、またはEABのローカル・インタコネクトからドライブすることができます。LEはEABのローカル・インタコネクトをドライブするようになっているため、LEでWE、RE、クリア、クロック、クロック・イネーブルの各信号をコントロールすることができます。

各EABの入力はロウ・インタコネクトと接続されており、出力はロウ・インタコネクトとカラム・インタコネクトをドライブすることができます。各EABの出力は最大2本までのロウ・チャネルとカラム・チャネルをドライブすることができ、使用されていないロウ・チャネルは他のLEからドライブすることができます。この機能はEABの出力に対する配線のリソースを増加させています(詳細については図2と図4を参照)。EABに隣接したカラム・インタコネクトには、デバイス内の他のカラム・インタコネクトの2倍にあたる配線チャネルが提供されています。

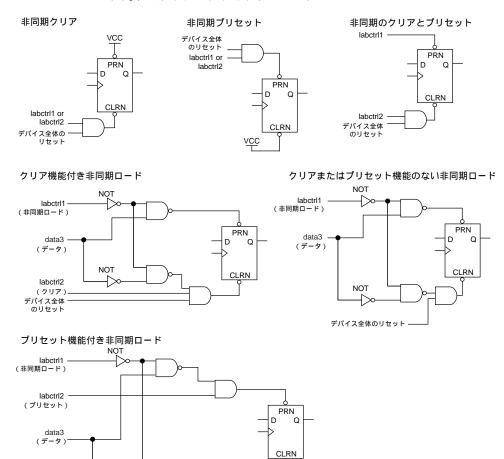

## ロジック・アレイ・ブロック

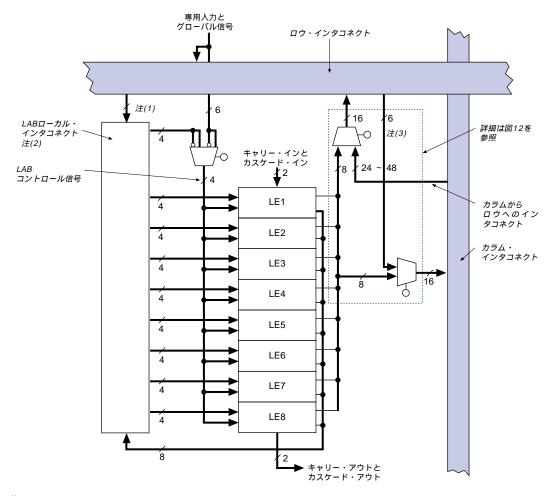

LABは8個のLE、関連するキャリー・チェインとカスケード・チェイン、LABのコントロール信号、そしてLABローカル・インタコネクトによって構成されています。LABはFLEX 10KEのアーキテクチャに対してコース・グレインの構造を提供しており、デバイス使用効率の最適化と高い性能を実現します(図7を参照)。

### 図7 FLEX 10KEデバイスのLAB

- 注:

- (1) EPF10K30E、EPF10K50E、EPF10K50Sの各デバイスはロウ・インタコネクトからLABローカル・インタコネクト・チャネルへの入力を22 本持っており、EPF10K100E、EPF10K100B、EPF10K100B、EPF10K130E、EPF10K200E、EPF10K200Sの各デバイスは26本の入力を持っています。

- (2) EPF10K30E、EPF10K50E、EPF10K50Sの各デバイスは30チャネルのLABローカル・インタコネクトを持っており、EPF10K100E、EPF10K100B、EPF10K100E、EPF10K200Sの各デバイスは34チャネル持っています。

- (3) EPF10K100Bデバイスでは、4本のロウ・チャネルが各交差ポイントでカラム・チャネルをドライブすることができます。

Page 16 Altera Corporation

各LABには極性反転が可能な4本のコントロール信号が提供されており、これらは8個すべてのLEで使用することができます。このうちの2本の信号はクロックとして使用することができます。LABのクロックは、専用のクロック入力ピン、グローバル信号、I/O信号、またはLABのローカル・インタコネクトを経由した内部信号によってドライブすることができます。また、LABのプリセットとクリアのコントロール信号は、グローバル信号、I/O信号、またはLABローカル・インタコネクトを経由した内部信号によってドライブすることができます。グローバル・コントロール信号はデバイス全体で非常にスキューの小さい非同期のコントロール信号となるため、通常はグローバル・クロック、クリアまたはプリセットの信号として使用されます。コントロール信号の生成にロジックが必要となる場合は、任意のLAB内の1個または複数のLEを使用して生成し、ターゲットとなるLABのローカル・インタコネクトをドライブすることができます。また、LEの出力からグローバルなコントロール信号を生成することもできます。

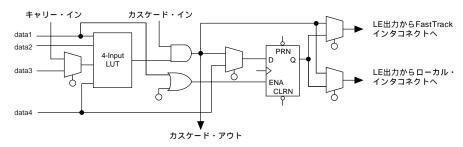

## ロジック・エレメント

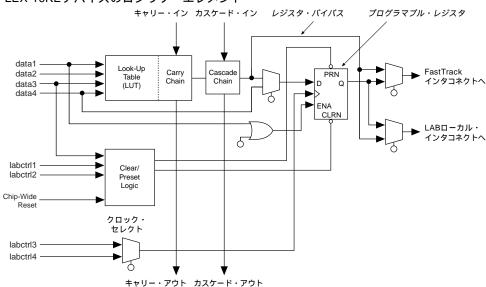

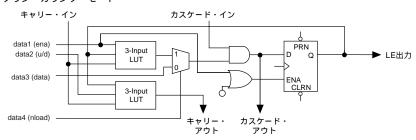

ロジック・エレメント(LE)はFLEX 10KEアーキテクチャが提供するロジックの最小単位となっており、高いデバイス使用効率を実現するコンパクトなサイズとなっています。各LEには4変数によるあらゆる論理演算が高速で実行できる4入力のLUTが含まれています。さらに、各LEには同期クロック・イネーブル機能を持ったプログラマブルなフリップフロップ、キャリー・チェイン、カスケード・チェインが含まれています。各LEは、ローカル・インタコネクトおよびFastTrackインタコネクトの双方をドライブするようになっています(図8を参照)。

#### 図8 FLEX 10KEデバイスのロジック・エレメント

LE 内のプログラマブル・フリップフロップは、D、T、JKまたはSRタイプの動作を行うようにコンフィギュレーションすることができます。フリップフロップのクロック、クリア、プリセットの各信号は、グローバル信号、汎用のI/Oピン、または任意の内部ロジックからドライブすることができます。組み合わせ回路を構成する場合はフリップフロップがバイパスされ、LUTの出力がLEの出力を直接ドライブします。

LEはインタコネクトをドライブする2本の出力を持っています。このうちの1本はローカル・インタコネクトをドライブし、もう1本はロウまたはカラムのFastTrackインタコネクトをドライブします。この2本のLEの出力はそれぞれ個別にコントロールすることができます。例えば、LUTが一方の出力をドライブしているときに、レジスタがもう一方の出力をドライブするように設定することができます。この機能はレジスタ・パッキングと呼ばれ、LUTとレジスタをそれぞれ独立した機能に使用できるため、LEの使用効率を改善することができます。

FLEX 10KEのアーキテクチャには、ローカル・インタコネクトを使用することなく隣接したLE間を接続する高速の専用データ・パスとして、キャリー・チェインとカスケード・チェインが提供されています。キャリー・チェインは高速のカウンタとアダーを構成するときに使用され、カスケード・チェインは多入力の論理機能を最小の遅延時間で実現するときに使用されます。カスケード・チェインとキャリー・チェインはLAB内のすべてのLE、およびデバイス内の同じロウの位置に配置されているすべてのLAB間を接続することができます。ただし、このキャリーとカスケードのチェインが多数使用された場合には、配線の柔軟性が低下することがあります。したがって、これらのチェインはデザイン内でスピードがクリティカルとなる部分に限定して使用する必要があります。

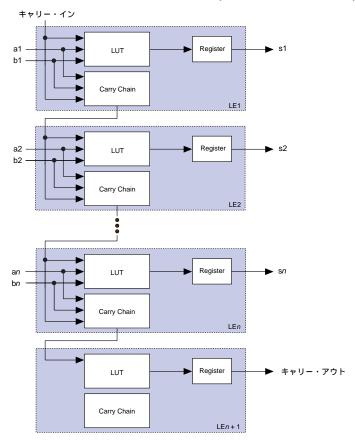

### キャリー・チェイン

キャリー・チェインはキャリーをLE間で非常に高速(最高速バージョンで 0.2ns以下)で転送します。下位ビットからのキャリー・イン信号はキャリー・チェインを通って上位ビットに転送され、上位ビットのキャリー・チェインとLUTの双方に入力されます。この機能を使用することによって、FLEX 10KEアーキテクチャはカウンタやアダー、指定したビット幅のコンパレータを高速で実現することができます。キャリー・チェインのロジックはデザインを処理する段階でQuartusとMAX+PLUS IIのコンパイラによって自動的に生成され、またデザインの入力時にマニュアルで指定することもできます。LPMやDesignWareのようなパラメータ化されたファンクションはキャリー・チェインの利点を自動的に活用します。

複数のLABをリンクさせることによって、8個以上のLEで接続される長いキャリー・チェインが自動的に生成されます。フィッティング機能を強化するため、長いキャリー・チェインは同じ口ウのLABを1個おきにスキップするようになっています。このため、複数のLABを通る長いキャリー・チェインは、偶数番号のLABから偶数番号へのLABへ、あるいは奇数番号のLABから奇数番号のLABへとスキップして接続されます。例えば、最初のLABの最後のLEは同じ口ウにある3番目のLABの最初のLEにキャリーを

Page 18 Altera Corporation

転送するようになっています。また、キャリー・チェインは各口ウの中央に 位置しているEABを越えて接続することはできません。例えば、 EPF10K50Eデバイスでは、キャリー・チェインが18番目のLABでストップ し、新しいキャリー・チェインが19番目のLABからスタートします。

図9はn+1個のLEとキャリー・チェインを使ったnビットのフル・アダーがどのように実現されるかを示したものです。ここで、LUTの一部を使用して入力信号とキャリー・イン信号から2ビットのサム(和)を生成します。そして、このサムはLEの出力に接続されます。単純なアダーを構成する場合は、レジスタが通常バイパスされますが、レジスタを使用してアキュムレータの機能を構成することもできます。LUTの他の部分とキャリー・チェインのロジックはキャリー・アウトの信号を生成し、この信号は次の上位ビットのキャリー・インに直接、接続されます。最後のキャリー・アウト信号はLEに接続され、この最後のLEで通常の信号と同じように使用できるようになります。

## 図 9 FLEX 10KEのキャリー・チェイン動作 (nビットのフル・アダー)

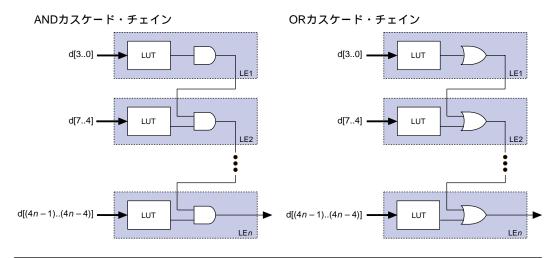

### カスケード・チェイン

FLEX 10KEのアーキテクチャは、カスケード・チェインを使用することによって非常に大きなファン・インを持った回路機能を実現できるようになっています。隣接している複数のLUTをパラレルに動作させ、その間の中間値をカスケード・チェインを使ってシリアルに転送させることによって論理機能の 1 部を実現することができます。このカスケード・チェインは隣接したLEの出力を接続して論理積(Logical AND)またはドモルガンの反転定理による論理和(Logical OR)を実現することができます。追加される各LEは要求される回路機能の入力ビット幅をLEあたり0.6nsの遅延時間で 4 ビットずつ効率的に拡張します。カスケード・チェインのロジックはデザインの処理の段階でMAX+PLUS IIのコンパイラによって自動的に生成され、またデザインの入力時にマニュアルで指定することもできます。

複数のLABをリンクさせることによって、8ビット以上の長さのカスケード・チェインが自動的に生成されます。配線を容易にするため、長いカスケード・チェインは同じ口ウに配置された隣のLABをスキップして接続されます。複数のLABを通る長いカスケード・チェインは、偶数番号のLABから偶数番号のLABへ、あるいは奇数番号のLABから奇数番号のLABへとスキップして接続されます。(最初のLAB内の最後のLEは同じ口ウにある3番目のLAB内の最初のLEにカスケード接続される。)カスケード・チェインは各口ウの中央部分を越えて接続することはできません。(EPF10K50Eデバイスでは、カスケード・チェインが18番目のLABでストップし、新しいカスケード・チェインが19番目のLABからスタートします。)これは各口ウの中央部にEABが配置されているためです。

図10は大きなファン・インを持つ回路機能を実現するときにカスケード・チェインが隣接したLE間でどのように接続されるかを示したものです。この例はn個のLEで4n個の変数を持つ論理機能が実現できることを示しています。最高速バージョンのデバイスでは、LEの遅延が1.3ns以下で、カスケード・チェインの遅延が0.6ns以下となっています。カスケード・チェインを使用した場合、16ビット・アドレスのデコードを約3.1nsのスピードで実現できます。

Page 20 Altera Corporation

### 図10 FLEX 10KEデバイスのカスケード・チェイン動作

### LEの動作モード

FLEX 10KEデバイスのLEは次の4種類のモードのいずれかで動作します。

- ノーマル・モード

- 演算モード

- アップ / ダウン・カウンタ・モード

- クリアブル・カウンタ・モード

これらの各モードでは、LEのリソースをそれぞれ異なる形で使用します。LEには各モードで、計7本の入力が提供されており(LABローカル・インタコネクトからの4本とプログラマブル・レジスタからのフィードバック、前段のLEからのキャリー・インとカスケード・インの計7本)、要求される論理機能を実現するためにこれらの入力はそれぞれ異なるリソースに接続されます。LEのレジスタのクロック、およびクリアとプリセットのコントロールには3本の入力が提供されています。QuartusとMAX+PLUS IIのソフトウェアはLPMやDesignWareファンクションのようなパラメータ化されたファンクションと共にカウンタやアダー、マルチプライヤなどのような標準的なアプリケーションに適切な動作モードを自動的に選択します。また、必要に応じて、ユーザが性能が最適化されるLEの動作モードを選択して、特定用途のファンクションを作成することもできます。

このFLEX 10KEデバイスのアーキテクチャでは、4種類すべてのモードでレジスタに対する同期クロック・イネーブルの機能が提供されています。QuartusとMAX+PLUS IIのソフトウェアはDATA1を使用してレジスタに同期イネーブル機能を設定することができるため、完全な同期型の設計が簡単に行えます。

## 図11はLEの各動作モードを示したものです。

## 図11 FLEX 10KEデバイスのLE動作モード

### ノーマル・モード

#### 演算モード

## アップ / ダウン・カウンタ・モード

## クリアブル・カウンタ・モード

Page 22 Altera Corporation

## ノーマル・モード

ノーマル・モードは汎用のロジック・アプリケーションや、カスケード・チェインの長所が活用できる多入力のデコーダなどに適しています。ノーマル・モードでは、LABのローカル・インタコネクトからの4本のデータ入力とキャリー・インが4入力のLUTの入力になります。MAX+PLUS IIのコンパイラはDATA3とキャリー・インのいずれかをLUTの入力として自動的に選択します。LUTの出力をカスケード・インの信号と組み合わせることによって、カスケード・アウトの信号を持つカスケード・チェインを構成することができます。レジスタまたはLUTを使用して、ローカル・インタコネクトとFastTrackインタコネクトの双方を同時にドライブすることができます。

LE内のLUTとレジスタはそれぞれ個別に独立させた状態で使用することができ、この機能はレジスタ・パッキングと呼ばれています。このレジスタ・パッキングの機能をサポートするため、LEには2本の出力が提供されています。一方の出力はローカル・インタコネクトをドライブし、もう一方の出力はFastTrackインタコネクトをドライブします。DATA4の信号はレジスタを直接ドライブすることができ、LUTがレジスタされた信号から独立した状態で論理演算を行うことができます。この場合、LUTでは3入力の論理演算が行われ、4番目の独立した信号がレジスタに入力されます。また、LUTに4入力の論理関数を生成させ、このうちの1本の入力信号でレジスタをドライブするように設定することもできます。レジスタ・パッキングされたLEでも、クロック・イネーブル、クリア、プリセットの各信号をLE内のレジスタに使用することができます。レジスタ・パッキングされたLEでは、LUTにローカル・インタコネクトをドライブさせながらレジスタからFastTrackをドライブする状態にすることができ、またこの逆の設定を行うこともできます。

#### 演算モード

演算モードでは、アダー、アキュムレータ、コンパレータの構成に最適な3入力のLUTが2個提供されます。このうち1個のLUTは3入力の論理関数を実現し、もう1個のLUTがキャリー・アウトを生成します。22ページの図11に示されているように、最初のLUTはキャリー・インとLABローカル・インタコネクトからの2本の入力を使用して組み合わせ出力またはレジスタ出力の論理を生成します。アダーを構成した場合は、この出力がaとbとキャリー・イン信号による3ビットのサム(和)となります。そして、2番目のLUTは同じ3本の信号からキャリー・アウト信号を生成して、キャリー・チェインを構成します。演算モードでは、同時にカスケード・チェインを使用することもサポートされています。

#### アップ / ダウン・カウンタ・モード

アップ/ダウン・カウンタ・モードでは、カウンタ・イネーブル、クロック・イネーブル、同期アップ/ダウン・コントロールの各信号と、データ・ロードのオプション機能用の信号が提供されます。これらのコントロール信号はLABローカル・インタコネクトからのデータ入力、キャリー・イン信号、プログラマブル・レジスタの出力からのフィードバック信号によって生成されます。このモードでは3入力のLUTが2個使用され、このうちの1個がカウンタ・データを生成し、もう1個が高速のキャリー・ビットを生成します。2対1のマルチプレクサにより、データの同期ロード機能が提供されています。また、LUTのリソースを使用することなく、クリアとプリセットのレジスタ・コントロール信号を使用した非同期のデータ・ロードを行うこともできます。

#### クリアブル・カウンタ・モード

クリアブル・カウンタ・モードはアップ / ダウン・カウンタ・モードと類似していますが、アップ / ダウン・コントロールの代わりに同期クリアの機能がサポートされています。このモードでは、アップ / ダウン・カウンタ・モードのカスケード入力の代わりにクリア入力が使用されます。このモードでも3入力のLUTが2個使用され、このうちの1個がカウンタ・データを生成し、もう1個が高速のキャリー・ビットを生成します。また、2対1マルチプレクサを使用した同期ロードの機能がサポートされています。このマルチプレクサの出力は同期クリアの信号とANDされるようになっています。

### インターナル・トライ・ステート・エミュレーション

FLEX 10KEデバイスには、インターナル・トライ・ステート・エミュレーション機能が提供されており、実際のトライ・ステート・バスのような制限を受けることなく、デバイス内部にトライ・ステートを実現することができます。実際のトライ・ステート・バスでは、トライ・ステート・バッファの出力イネーブル(OE)信号がバスをドライブする信号を選択します。ただし、複数の出力イネーブル(OE)がアクティブになったときには、競合する複数の信号がバスをドライブすることになります。逆に言えば、どの出力イネーブル信号もアクティブにならない場合には、バスがコーティングの状態となります。インターナル・トライ・ステート・バッファをLowの値に、フローティング状態のバスをHighの値にしてこれらの問題を解消します。MAX+PLUS II のソフトウェアはマルチプレクサを使用してトライ・ステート・バスの機能を自動的に実現します。

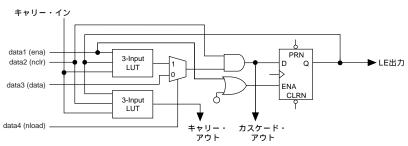

### クリアおよびプリセット・ロジック・コントロール

プログラマブル・レジスタのクリアとプリセットの機能を実現するロジックは、LEの入力となっているDATA3、LABCTRL1、LABCTRL2の信号によって構成することができます。LEのクリアとプリセットの機能はレジスタに非同期でデータをロードするときにも使用されます。また、LABCTRL1またはLABCTRL2を使用して、非同期クリアの機能を実現することもできます。 さらに、LABCTRL1によってコントロールされる非同期データ・ロード機能を持つレジスタの設定も行うことができます。この場合、レジスタにロードされるデータはDATA3から入力され、LABCTRL1がアクティブとなったときにレジスタへDATA3の信号がロードされます。

QuartusとMAX+PLUS II のコンパイラは、コンパイル時に最も適切なコントロール信号を自動的に生成します。クリアとプリセットの信号はアクティブLowとなっているため、コンパイラは未使用のクリアとプリセットのノードを自動的にHighレベルにセットします。

クリアとプリセットのロジックは、デザインの入力時に次の6種類のモードからいずれかひとつを選択することによって実現できます。

- 非同期クリア

- 非同期プリセット

- 非同期のクリアとプリセット

- クリア機能付き非同期ロード

- プリセット機能付き非同期ロード

- クリアまたはプリセット機能のない非同期ロード

前記の6種類のクリアとプリセットのモードに加え、FLEX 10KEデバイスにはデバイス内のすべてのレジスタをリセットすることができるデバイス全体のリセット・ピンが提供されており、デザインの入力時に指定することができます。クリアとプリセットのいずれのモードにおいても、デバイス全体のリセットの信号は他のすべての信号よりも優先されます。チップ全体のリセット信号がアサートされたときに非同期のプリセット機能を持ったレジスタが、プリセットされるようにすることもできます。極性反転機能を使用して、非同期のプリセット機能を実現することもできます。図12は要求されるクリアとプリセット機能を実現する場合のデザインの入力方法の例を示したものです。

### 図12 FLEX 10KEのLEに対するクリアとプリセットのモード

NOT

デバイス全体のリセット

#### 非同期クリア

フリップフロップはLABCTRL1またはLABCTRL2のいずれかでクリアされます。このモードではプリセット信号がVCCに接続され、非アクティブとなります。

#### 非同期プリセット

非同期プリセットは非同期のデータ・ロードとしての機能か、非同期クリアの機能付きのいずれかで実現されます。 DATA3がVCCに接続された状態でLABCTRL1がアサートされると、非同期でレジスタに 1 がロードされます。また、MAX+PLUS II のソフトウェアがレジスタの入力と出力の極性反転とクリア機能を使用して、プリセット・コントロール機能が実現されるようにすることもできます。 LEとIOEの入力には極性反転の機能が提供されています。このため、 2 本のLABCTRL信号のいずれか 1 本でレジスタがプリセットされる場合は、DATA3の入力が不要となり、これをLEのいずれかの動作モードで使用することができるようになります。

#### 非同期のクリアとプリセット

非同期のクリアとプリセットを実現する場合は、LABCTRL1でプリセットを、LABCTRL2でクリアをコントロールします。このとき、DATA3はVCCに接続され、LABCTRL1がアサートされるとレジスタに1が非同期でロードされ、レジスタがプリセットされたことになります。また同様にLABCTRL2をアサートすることによって、レジスタがクリアされます。

#### クリア機能付き非同期ロード

クリア機能付きの非同期ロードを実現する場合は、LABCTRL1でレジスタのプリセットとクリアをコントロールし、DATA3の信号を非同期でレジスタへロードします。また、LABCTRL2はレジスタのクリア端子をコントロールしてレジスタのクリア機能を実現し、LABCTRL2をプリセットの回路に接続する必要はありません。

#### プリセット機能付き非同期ロード

プリセット機能付きの非同期ロードを実現する場合は、MAX+PLUS IIのソフトウェアがレジスタの入力と出力の極性を反転させ、クリア信号を使ったプリセット機能を実現します。LABCTRL2がアサートされるとレジスタがプリセットされ、LABCTRL1がアサートされると、レジスタにデータがロードされます。MAX+PLUS IIのソフトウェアはレジスタの出力が反転されていることを考慮して、DATA3をドライブする信号の極性を反転させます。

#### クリアまたはプリセット機能のない非同期ロード

クリアまたはプリセット機能のない非同期ロードを実現する場合は、LABCTRL1でレジスタのプリセットとクリアをコントロールし、DATA3の信号が非同期でレジスタへロードされるようにします。

Page 26 Altera Corporation

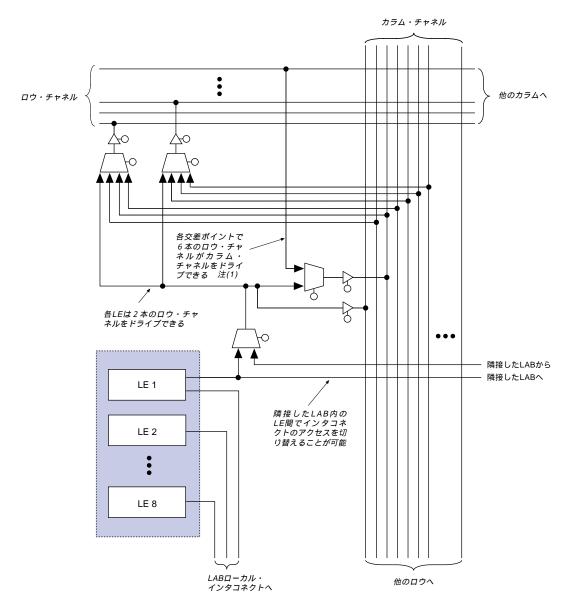

## FastTrackインタコネクトの配線構造

FLEX 10KEのアーキテクチャでは、デバイス全体を縦横に走っている連続した配線チャネル、FastTrackインタコネクトによって、LE、EABおよびデバイスI/Oピン間の接続が行われます。FLEX 10KEデバイスでは、このデバイス全体をカバーするグローバルな配線構造により、複雑なデザインにおいてもその性能が予測可能となっています。これに対してFPGAでは配線領域が分割されているため、一定しない複数のパスを接続するためのスイッチ・マトリックスが必要となり、ロジック・リソース間のディレイが大きくなって性能が低下します。

FastTrackインタコネクトはデバイス全体をカバーしているロウとカラムのインタコネクト・チャネルによって構成されています。各口ウに配置されているLAB間の接続は専用のロウ・インタコネクトによって行われます。ロウ・インタコネクトはI/Oピンをドライブすることができ、同じロウにある他のLABに信号を供給します。また、カラム・インタコネクトは異なるロウの間の信号を接続し、またI/Oピンをドライブすることができます。

口ウ側の配線チャネルはLABまたはEABのローカル・インタコネクトをドライブします。ロウ側からの信号は各LABまたはEABでバッファされ、ファンアウトによる遅延の影響が低下されています。1個のLE、または3本のカラム・チャネルのうちのいずれか1本によってドライブすることができます。これら4本の信号は、特定の2本のロウ・チャネルに接続されている2個の4対1マルチプレクサの入力となっています。これらのマルチプレクサは各LEに接続されており、LAB内にある8個すべてのLEがロウ・インタコネクトをドライブしている場合でも、カラム・チャネルがロウ・チャネルをドライブすることができます。

各カラムに配置されているLABまたはEABとの接続は専用のカラム・インタコネクトによって行われます。各EABに対応したカラム・インタコネクトには他のカラム・インタコネクトの2倍にあたる配線チャネルが提供されています。カラム・インタコネクトはI/Oピンをドライブすることができ、またデバイス内の異なるロウにあるLABまたはEABの信号を接続します。LEの出力またはI/Oピンからの入力となっているカラム・インタコネクトからの信号は、LABまたはEAB入力される前にロウ・インタコネクトを通らなければなりません。IOEまたはEABによってドライブされる各ロウ・チャネルは指定された1本のカラム・チャネルをドライブすることができます。

ロウとカラムのチャネルへのアクセスを隣接した2つのLAB内のLE間で切り替えることができます。例えば、LAB内の特定のLEが、同じロウの隣接したLAB内の特定のLEによってドライブされているロウおよびカラム・チャネルをドライブするように設定することができ、またその逆の設定も行えます。このような柔軟性の高い配線構造によって、配線のリソースをより効率的に使用することができます(図13を参照)。

## 図13 FLEX 10KEデバイスのLABとロウおよびカラム・インタコネクトの接続

注:

(1) EPF10K100Bでは、4本のロウ・チャネルが各交差ポイントでカラム・チャネルをドライブすることができます。

Page 28 Altera Corporation

ロウ・インタコネクトは、配線の能力を改善するためにフル・レングスのチャネルとハーフ・レングスのチャネルの配線リソースとを組み合わせたものになっています。フル・レングスのチャネルは同じロウのすべてのLAB間を接続することができます。これに対して、ハーフ・レングスのチャネルはひとつのロウの半分のLAB間を接続します。EABはフル・レングスのチャネルはなってドラインされます。また、EABはフル・レングスのチャネルによってドラインされます。また、EABはフル・レングスのチャネルをドライブしています。このアーキテクチャでは、性能の予測を可能にする配線構造やロウ全体をカバーした配線リソースが提供できる特長に加え、さらに多くの配線リソースが提供されています。2つの隣接したLAB間はハーフ・レングスのロウ・チャネルで接続できるようになっており、このハーフ・レングスのチャネルを活用することによって、同じロウのもう半分には別のハーフ・レングスのチャネルが使用できるようになります。

表 7 は各FLEX 10KEデバイスに提供されているFastTrackインタコネクトのリソースの数をまとめたものです。

| 表7 FLEX 10KEデバイスのFastTrackインタコネクトのリソース |      |                 |       |                  |  |

|----------------------------------------|------|-----------------|-------|------------------|--|

| デバイス名                                  | ロウの数 | ロウあたりの<br>チャネル数 | カラムの数 | カラムあたりの<br>チャネル数 |  |

| EPF10K30E                              | 6    | 216             | 36    | 24               |  |

| EPF10K50E<br>EPF10K50S                 | 10   | 216             | 36    | 24               |  |

| EPF10K100B<br>EPF10K100E               | 12   | 312             | 52    | 24               |  |

| EPF10K130E                             | 16   | 312             | 52    | 32               |  |

| EPF10K200E<br>EPF10K200S               | 24   | 312             | 52    | 48               |  |

FLEX 10KEデバイスには、汎用のI/Oピンに加えて、スキューの小さな信号をデバイス全体に供給できる6本の入力専用ピンが提供されています。これら6本の入力は、グローバルなクロック、クリア、プリセット、ペリフェラルの出力イネーブル、クロック・イネーブルのコントロール信号などに使用することができます。これらのピンからの入力は、デバイス内のすべてのLABとIOEをコントロールする信号としても使用することができます。これらの入力専用ピンからの信号はデバイス内の各LABのローカル・インタコネクトにも接続されるようになっているため、汎用のデータ入力としても使用できます。

図14は、隣接した複数のLABとEABの接続関係を、ロウおよびカラム・インタコネクト、ローカル・インタコネクト、関連したカスケード・チェイン、キャリー・チェインによって示したものです。ここで、各LABの名前は、デバイス内のロウ(1,2,3...)、およびカラム(A,B,C...)の物理的な位置を表わしたものになっています。例えば、B3のLABはロウ-B、カラム-3の位置にあることを示しています。

#### 図14 FLEX 10KEデバイスのインタコネクト・リソース

### 1/0エレメント

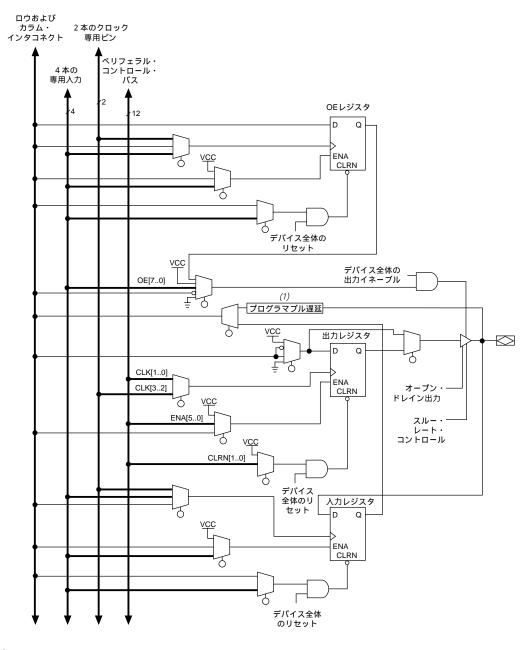

各I/Oエレメント(IOE)には双方向のI/Oバッファとレジスタが1個ずつ含まれています。このレジスタは高速のセットアップ・タイムを必要とする外部データの入力レジスタとして、あるいは高速の「Clock-to-Output」性能を必要とするデータの出力レジスタとして使用することができます。LE内のレジスタを入力レジスタとして使用したほうが、IOEのレジスタを使用した場合よりも高速のセットアップ・タイムが提供されることもあります。I/Oエレメントは入力、出力、または双方向のピンとして使用することができます。QuartusとMAX+PLUS II のコンパイラは必要に応じて、ロウおよびカラム・インタコネクトからの信号の極性をプログラマブルな反転オプションを使って自動的に反転させます。FLEX 10KEのIOEの構造が図15に示されています。

Page 30 Altera Corporation

## 図15 FLEX 10KEデバイスの双方向I/Oレジスタ

注:

<sup>(1)</sup> 一部のFLEX 10KEデバイスには、入力パスにプログラマブルな遅延機能が提供されています。

EPF10K50EとEPF10K200Eを除くすべてのFLEX 10KEデバイスには、I/O パッドからFastTrackインタコネクトへの入力パスにプログラマブルな遅延エレメントが提供されており、これを使用してOnsのホールド・タイムを実現することができます。EPF10K50SとEPF10K200Sの各デバイスは、この機能をサポートしています。信号をデバイス内部にドライブしているIOEの相対的な位置に応じて、設計者はこのプログラマブルな遅延コントロール機能をオンにしてOnsのホールド・タイムを確保したり、またはオフに設定して最小のセットアップ・タイムを実現することができます。この機能は、ピンからレジスタまでの複雑なパスに対するセットアップ・タイムを減少させるときに使用されます(例:PCIのデザイン)。

各IOEに対するクロック、クリア、クロック・イネーブル、および出力イネーブル・コントロールの各信号は、ペリフェラル・コントロール・バスと呼ばれるI/Oコントロール信号のネットワークから選択されます。このペリフェラル・コントロール・バスにはデバイス全体で信号のスキューを最小にする高速ドライバが使用されており、下記のペリフェラル・コントロール信号を最大12本まで使用できます。

- 最大8本までの出力イネーブル信号

- 最大6本までのクロック・イネーブル信号

- 最大2本までのクロック信号

- 最大2本までのクリア信号

6本を超えるクロック・イネーブル信号や8本を超える出力イネーブル信号が必要になる場合は、特定のLEからドライブされているクロック・イネーブルと出力イネーブルの信号を使用してデバイス内の各IOEをコントロールすることができます。各IOEにはペリフェラル・コントロール・バスに提供されている2本のクロックに加え、2本のクロック専用ピンからの信号のうちのいずれか1本を使用することができます。各ペリフェラル・コントロール信号は入力専用ピン、または特定のロウの位置に配置されたLABの最初のLEからドライブすることができます。異なるロウのLEからはカラム・インタコネクトをドライブされるようになっているため、ペリフェラル・コントロール信号はロウ・インタコネクトからドライブされることになります。デバイス全体のリセット信号は、他のコントロール信号よりも優先してすべてIOEレジスタをリセットします。

専用のクロック入力ピンからIOEのレジスタをドライブする場合、デバイス内のすべてのIOEに対して、このクロックの極性を反転させて使用することが可能です。ただし、この場合は、すべてのIOEがこのクロックを同じ手法で使用する必要があります。例えば、あるIOEに極性反転されたクロックを使用した場合は、他のすべてのIOEにも同じ極性反転されたクロックを使用する必要があり、どのIOEでも非反転のクロックを使用することはできません。しかしながら、この場合でもLEにはLABごとに反転または非反転のクロックが使用可能です。

入力される信号をクロック専用ピンで極性反転させ、すべてのIOEに供給させることもできます。IOEのドライブに極性反転されたクロックと非反転の

Page 32 Altera Corporation

クロックを使用する場合は、2本のグローバル・クロック・ピンを使用し、 1本のグローバル・クロック・ピンからは非反転のクロックを、もう1本の ピンから極性反転されたクロックを供給します。

入力専用ピンからの極性反転されたクロックと非反転のクロックでIOEをドライブしていて、ペリフェラル・コントロール・バスで2本の信号が使用されている場合は、それぞれ1本のコントロール信号が一方のクロック信号に対応したものとなります。

入力専用ピンから極性反転および非反転のペリフェラル・クリア、クロック・イネーブル、出力イネーブルをドライブする場合は、ペリフェラル・コントロール・バスの2本の信号が使用されます。

表 8 と表 9 は各ペリフェラル・コントロール信号のソースをまとめたものです。これらの表は12本あるペリフェラル・コントロール信号から、出力イネーブル信号、クロック・イネーブル信号、クロック信号、クリア信号をどのように実現するかを示しており、各グローバル信号をドライブできるロウの位置を示しています。

| 表 8 EPF10K30E、EPF10K50E、EPF10K50Sのペリフェラル・<br>バス・ソース |           |                        |  |  |  |

|-----------------------------------------------------|-----------|------------------------|--|--|--|

| ペリフェラル・<br>コントロール信号                                 | EPF10K30E | EPF10K50E<br>EPF10K50S |  |  |  |

| OE0                                                 | Row A     | Row A                  |  |  |  |

| OE1                                                 | Row B     | Row B                  |  |  |  |

| OE2                                                 | Row C     | Row D                  |  |  |  |

| OE3                                                 | Row D     | Row F                  |  |  |  |

| OE4                                                 | Row E     | Row H                  |  |  |  |

| OE5                                                 | Row F     | Row J                  |  |  |  |

| CLKENA0/CLK0/GLOBAL0                                | Row A     | Row A                  |  |  |  |

| CLKENA1/OE6/GLOBAL1                                 | Row B     | Row C                  |  |  |  |

| CLKENA2/CLR0                                        | Row C     | Row E                  |  |  |  |

| CLKENA3/OE7/GLOBAL2                                 | Row D     | Row G                  |  |  |  |

| CLKENA4/CLR1                                        | Row E     | Row I                  |  |  |  |

| CLKENA5/CLK1/GLOBAL3                                | Row F     | Row J                  |  |  |  |

| 表 9 | EPF10K100B、 | EPF10K100E、 | EPF10K130E、 | EPF10K200EおよびEPF10K200Sの |

|-----|-------------|-------------|-------------|--------------------------|

|     | ペリフェラル・     | ・バス・ソース     |             |                          |

| ペリフェラル・コントロール信号      | EPF10K100B<br>EPF10K100E | EPF10K130E | EPF10K200E<br>EPF10K200S |

|----------------------|--------------------------|------------|--------------------------|

| OE0                  | Row A                    | Row C      | Row G                    |

| OE1                  | Row C                    | Row E      | Row I                    |

| OE2                  | Row E                    | Row G      | Row K                    |

| OE3                  | Row L                    | Row N      | Row R                    |

| OE4                  | Row I                    | Row K      | Row O                    |

| OE5                  | Row K                    | Row M      | Row Q                    |

| CLKENA0/CLK0/GLOBAL0 | Row F                    | Row H      | Row L                    |

| CLKENA1/OE6/GLOBAL1  | Row D                    | Row F      | Row J                    |

| CLKENA2/CLR0         | Row B                    | Row D      | Row H                    |

| CLKENA3/OE7/GLOBAL2  | Row H                    | Row J      | Row N                    |

| CLKENA4/CLR1         | Row J                    | Row L      | Row P                    |

| CLKENA5/CLK1/GLOBAL3 | Row G                    | Row I      | Row M                    |

ペリフェラル・コントロール・バス上の信号は表8と表9でGLOBAL0から GLOBAL3までの名前で表示されている4本のグローバル信号をドライブすることもできます。また、内部で生成された信号でグローバル信号をドライブすることもでき、1本の入力ピンからドライブされる信号と同じようにスキューと遅延の小さな特性を得ることができます。ペリフェラル・バスをドライブしているロウ側の配線チャネルをLEからドライブすることによって、LEからグローバル信号をドライブすることができます。この機能は、ファンアウトの大きいクリア信号やクロック信号を内部生成するときに最適です。ただし、内部生成されたグローバル信号が、データ信号の配線を行うための汎用インタコネクトの使用効率を高めることにはなりません。

デバイス全体の出力イネーブル・ピンはアクティブLowで動作し、デバイスのすべてのピンをトライ・ステートにすることができます。このオプションはQuartusとMAX+PLUS IIのソフトウェアで設定することができます。EPF10K50EとEPF10K200Eデバイスでは、デバイス全体の出力イネーブル・ピンがアクティブになると内蔵のI/Oピン用プルアップ抵抗がアクティブになります(コンフィギュレーション時もアクティブ)。また、デバイス全体のリセット・ピンによってIOE内のレジスタをリセットすることもできます。

Page 34 Altera Corporation

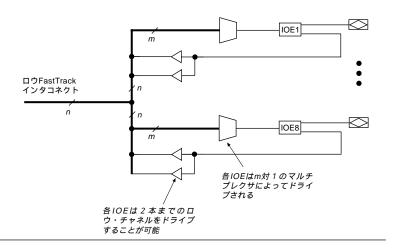

## ロウ・チャネルとIOEの接続

IOEを入力として使用した場合は、IOEから分離された2本のロウ・チャネルをドライブすることができます。この信号は同じロウに配置されているすべてのLEによってアクセス可能になります。また、IOEが出力として使用された場合は、IOEが各ロウ・チャネルの信号から1本の信号を選択するマルチプレクサによってドライブされます。各ロウ・チャネルの両端には最大8個までのIOEが接続されています(図16を参照)。

### 図16 FLEX 10KEデバイスのロウ・チャネルとIOEの接続

この図で表示されているmとnの値は表10の通りです。

表10はFLEX 10KEデバイスにおけるロウ・チャネルからIOEに接続するときのリソースの数を示したものです。

| 表10 FLEX 10KEデバイスのロウ・チャネルからIOEへのインタ<br>コネクト・リソース |                         |                            |  |  |

|--------------------------------------------------|-------------------------|----------------------------|--|--|

| デバイス名                                            | ロウあたりのチャネル数( <i>n</i> ) | ピンあたりのロウ・チャネル数( <i>m</i> ) |  |  |

| EPF10K30E                                        | 216                     | 27                         |  |  |

| EPF10K50E<br>EPF10K50S                           | 216                     | 27                         |  |  |

| EPF10K100B<br>EPF10K100E                         | 312                     | 39                         |  |  |

| EPF10K130E                                       | 312                     | 39                         |  |  |

| EPF10K200E<br>EPF10K200S                         | 312                     | 39                         |  |  |

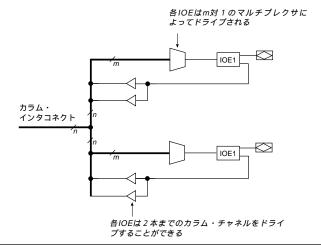

## カラム・チャネルとIOEの接続

IOEを入力として使用した場合、IOEから分離された2本までのカラム・チャネルをドライブすることができます。また、IOEが出力として使用された場合は、IOEは各カラム・チャネルの信号から1本の信号を選択するマルチプレクサによってドライブされます。各カラム・チャネルの両端には2個のIOEが接続されています。各IOEはマルチプレクサを介してカラム・チャネルからドライブできます。IOEがアクセスできるカラム・チャネル信号の組み合わせは、デバイスごとに異なります(図17を参照)。

### 図17 FLEX 10KEデバイスのカラム・チャネルとIOEの接続

この図で示されているmとnの値は表11の通りです。

表11はFLEX 10KEデバイスにおけるカラム・チャネルからIOEに接続すると きのリソースの数を示したものです。

| 表11 FLEX 10KEデバイスのカラム・チャネルからIOEへのインタ<br>コネクト・リソース |                          |                             |  |  |

|---------------------------------------------------|--------------------------|-----------------------------|--|--|

| デバイス名                                             | カラムあたりのチャネル数( <i>n</i> ) | ピンあたりのカラム・チャネル数( <i>m</i> ) |  |  |

| EPF10K30E                                         | 24                       | 16                          |  |  |

| EPF10K50E<br>EPF10K50S                            | 24                       | 16                          |  |  |

| EPF10K100B<br>EPF10K100E                          | 24                       | 16                          |  |  |

| EPF10K130E                                        | 32                       | 24                          |  |  |

| EPF10K200E<br>EPF10K200S                          | 48                       | 40                          |  |  |

Page 36 Altera Corporation

# SameFrame ピン配置機能

FLEX 10KEデバイスはFineLine BGAパッケージによるSameFrameピン配置機能をサポートしています。このSameFrameピン配置機能は、ボール数の少ないFineLine BGAパッケージのボールが、ボール数の多いFineLine BGAパッケージのボールの位置と互換性を持つように配列したものです。このSameFrameピン配置機能により、集積度の異なる同じパッケージのデバイスへの移行だけでなく、パッケージと集積度の異なるデバイスへの移行も可能にする高い柔軟性が提供されます。このため、一定のプリント基板(PCB)のレイアウトで、パッケージや集積度の異なる複数デバイスの使用が可能になります。例えば、256ピンFineLine BGAパッケージのEPF10K30Eから、672ピンFineLine BGAパッケージのEPF10K200Sへの移行が1種類のボード・レイアウトでサポートされます。

QuartusとMAX+PLUS IIのソフトウェアは、このSameFrameピン配置機能を持つデバイスを使用するPCBのレイアウトをサポートしています。これらのソフトウェアでは、現在および将来使用するデバイスを定義することができます。この設定を行うと、QuartusとMAX+PLUS IIのソフトウェアは、このマイグレーション機能の利点を活用したボード・レイアウトになるピン配置を生成します(図18を参照)。

### 図18 SameFrameピン配置機能の例

100 ピンFineLine BGAパッケージ

256 ピンFineLine BGAパッケージ

(1/0数またはロジック・エレメ

(1/0数またはロジック・エレメ

ント数を減少させた場合)

ント数を増加させた場合)

# ClockLockと ClockBoostの 機能

高速のデザインをサポートするため、FLEX 10KEデバイスは、 Phase-Locked Loop (PLL)を使用して、デザイン・スピードの高速化や使用デバイス・リソースの減少を実現するClockLockとClockBoostのオプションを提供しています。ClockLock回路はクロック信号をPLLに同期して動作させ、クロックの遅延とデバイス内の信号スキューを低減させます。この低減により、0nsのレジスタ・ホールド・タイムを維持しながら、セットアップ・タイムと「Clock-to-Output」遅延が最小に抑えられます。ClockBoost回路はクロック周波数の逓倍機能を実現しており、この機能を使用してロジックの一部を時分割で動作させることによって、デバイスのエリア効率を改善することができます。また、ClockBoostの機能を使用することにより、ボード上に低速のクロックを分配し、デバイス内部でのクロック周波数の逓倍を実現することが可能になります。ClockLockとClockBoostの機能を併用することで、システムの性能と帯域幅が大幅に改善されます。

EPF10K50Eを除くすべてのFLEX 10KEデバイスはClockLockとClockBoost の機能をサポートしています。また、EPF10K50SとEPF10K200Sの両デバイスもClockLockとClockBoostの機能をサポートしています。 ClockLockと ClockBoostの機能をサポートしているデバイスは、そのオーダ・コードの末尾に"X"のサフィックスが追加されます。例えば、EPF10K200EFC672-1Xは、これらの機能をサポートしています。

FLEX 10KEデバイス内のClockLockとClockBoostの機能は、Quartusおよび MAX+PLUS II のソフトウェアによってイネーブルにされます。これらの機能の使用には、外部デバイスを必要としません。 ClockLockおよび ClockBoost回路の出力をデバイスのピンに取り出すことはできません。

ClockLockとClockBoostの回路は入力クロックの立ち上がりエッジにロックします。この回路の出力はレジスタのクロック入力をドライブすることができ、生成されたクロックの極性を反転させることはできません。

ClockLockとClockBoostの回路へのクロックはクロック専用ピン(GCLK1)から供給されます。このクロック専用ピンがClockLockまたはClockBoostの回路をドライブしている場合は、デバイスの他の回路をドライブすることはできません。

周波数が逓倍されたクロックと逓倍されないクロックの双方を必要とするデザインでは、ボード上のクロックの配線パターンをGCLK1ピンに接続することができます。 MAX+PLUS IIのソフトウェアでは、GCLK1をClockLockとClockBoostの双方の回路に接続することができますが、双方の回路が使用された場合は、もう一方のクロック専用ピンを使用することはできません。

Page 38 Altera Corporation

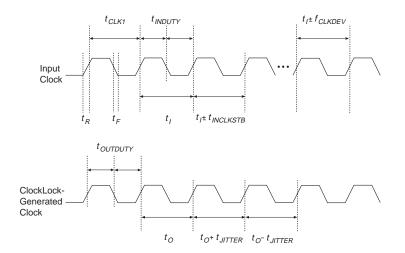

### ClockLockとClockBoostのタイミング・パラメータ

ClockLockとClockBoostの回路を適切に動作させるためには、入力のクロックが要求されるタイミング規格に適合している必要があります。これらの規格が満足されない場合は、これらの回路が入力されたクロックにロックせず、デバイス内に不適切なクロックが生成されます。ClockLockとClockBoostの回路によって生成されたクロックも一定の規格を満足している必要があります。コンフィギュレーション時に入力されたクロックがこれらの要求を満足している場合には、コンフィギュレーション時にClockLockとClockBoostの回路が入力のクロックにロックするようになります。そして、コンフィギュレーション完了後に回路が使用可能な状態になります。図19は入力されるクロックと生成されるクロックのタイミング規格を示したものです。

### 図19 入力クロックと生成クロックの規格

$t_l$  のパラメータは入力クロック期間、 $t_0$  のパラメータは出力クロック期間として参照されます。

表12は、ClockLockとClockBoostのタイミング・パラメータの規格を示したものです。

| シンボル                  | パラメータ                                            | 最小 | 標準 | 最大                   | 単位  |

|-----------------------|--------------------------------------------------|----|----|----------------------|-----|

| $t_R$                 | 入力立ち上がり時間                                        |    |    | 5                    | ns  |

| $t_F$                 | 入力立ち下がり時間                                        |    |    | 5                    | ns  |

| t <sub>INDUTY</sub>   | 入力デューティ・サイクル                                     | 40 |    | 60                   | %   |

| f <sub>CLK1</sub>     | 入力クロック周波数(ClockBoostの逓倍指数が1の場合)                  | 30 |    | 140                  | MHz |

| f <sub>CLK2</sub>     | 入力クロック周波数(ClockBoostの逓倍指数が2の場合)                  | 16 |    | 70                   | MHz |

| f <sub>CLKDEV</sub>   | MAX+PLUS IIソフトウェアで指定した値からの入力誤差 (1)               |    |    | 25,000<br><i>(2)</i> | PPN |

| t <sub>INCLKSTB</sub> | 入力クロック安定度 (隣接したクロック間で測定)                         |    |    | 100                  | ps  |

| t <sub>LOCK</sub>     | ClockLockまたはClockBoostがロックするまでに要する時間 (3)         |    |    | 10                   | μs  |

| t <sub>JITTER</sub>   | ClockLockまたはClockBoostから生成されたクロックのジッタ (4)        |    |    | 250 (4)              | ps  |

| t <sub>OUTDUTY</sub>  | ClockLockまたはClockBoostから生成されたクロックのデューティ・<br>サイクル | 40 | 50 | 60                   | %   |

#### 注:

- (1) MAX+PLUS IIソフトウェアでClockLockとClockBoostの使用を設定する場合は、入力の周波数を定義する必要があります。MAX+PLUS II のソフトウェアは、ClockLockとClockBoostの回路のPLLをこの周波数に設定します。fCLKDEVのパラメータは、入力クロックがデバイスの動作中に規定した周波数とどの程度異なっても良いかを表しています。シミュレーションにおいて、このパラメータが反映されることはありません。

- (2) 25,000PPM (Parts Per Million)は、入力クロック期間の2.5%に相当します。

- (3) デバイス・コンフィギュレーションにおいて、ClockLockとClockBoostの回路はデバイス内の他の部分よりも先にコンフィギュレーションされます。 $t_{LOCK}$ の値はコンフィギュレーションに要する時間よりも短いため、コンフィギュレーションの期間中に入力クロックが供給された場合でも、ClockLockとClockBoostの回路がコンフィギュレーション期間にロックします。

# I/Oの構成

このセクションでは、FLEX 10KEデバイスに提供されている、PCI (Peripheral Component Interconnect) プルアップ・クランピング・ダイオード・オプション、スルー・レート・コントロール、オープン・ドレイン出力オプション、MultiVolt I/Oインタフェース機能について解説します。 PCIプルアップ・クランピング・ダイオード、スルー・レート・コントロール、オープン・ドレイン出力の各オプションは、MAX+PLUS IIのlogicオプションを通じて、ピンごとに個別に設定することができます。また、MultiVolt I/Oインタフェースは、 $V_{CCIO}$ を $V_{CCINT}$ と異なる電源電圧に接続することによってコントロールすることができます。これらの設定の影響は、MAX+PLUS II のGlobal Project Device Optionsのダイアログ・ボックス (Assignメニュー)を使用してシミュレーションすることができます。

### PCIプルアップ・クランピング・ダイオード・オプション

FLEX 10KEデバイスは、各I/Oピン、入力専用ピン、およびクロック専用ピンにプルアップ・クランピング・ダイオードを内蔵しています。PCIクランピング・ダイオードは信号をVCCIOの値にクランプする働きをするもので、この機能は3.3VのPCI仕様に準拠させるときに必要となります。また、この

Page 40 Altera Corporation

クランピング・ダイオードは、他のシステムへのオーバシュートを制限する 目的にも使用することができます。

### スルー・レート・コントロール

各IOEの出力バッファには出力のスルー・レートを調整する機能が提供されており、各出力バッファを低ノイズのモード、または高速性能のモードのいずれかにコンフィギュレーションすることができます。低速スルー・レートのモードではシステムのノイズが低減されますが、最大の遅延時間が約4.3ns増加します。高速スルー・レートのモードは、ノイズに対する適切な対策が行われているシステムでスピードがクリティカルとなる出力のみに使用して下さい。スルー・レートはデザインの入力時に各ピンごとに指定することができ、すべてのピンにデフォルトのスルー・レートを指定することも可能です。低速スルー・レートの設定は出力の立ち下がりと立ち上がりエッジの双方に影響を与えます。

### オープン・ドレイン出力オプション

FLEX 10KEデバイスには、各I/Oピンごとにオープン・ドレイン出力(電気的にオープン・コレクタ出力と等価)の指定を行うことができるオプションが提供されています。このオープン・ドレイン出力を使用することによって、システム・レベルのコントロール信号(インタラプト信号やライト・イネーブル信号)を複数のデバイスで使用できるようになります。また、これを使用して追加のワイヤード-ORのプレーンを構成することもできます。

### MultiVolt I/Oインタフェース

FLEX 10KEデバイスのアーキテクチャはMultiVolt I/Oインタフェース機能をサポートしており、すべてのパッケージのFLEX 10KEデバイスは異なる電源電圧を使用しているシステムとインタフェースすることができます。これらのデバイスは、内部のロジックの動作と入力バッファに使用される $V_{CC}$ ピン(VCCINT)のセットとI/Oピンの出力ドライバに使用される $V_{CC}$ ピン(VCCIO)のセットを持っています。

VCCINTのピンは常に2.5Vの電源に接続する必要があります。 $V_{CCINT}$ が2.5Vの条件では、2.5V、3.3V、5.0Vの各入力電圧の信号に対する互換性が提供さ

れます。このとき、VCCIOピンは要求される出力レベルに応じて3.3Vあるいは2.5Vのいずれかの電源に接続することができます。VCCIOピンを2.5Vの電源に接続した場合は、出力電圧が2.5Vのシステムと互換性を持つようになります。また、VCCIOピンを3.3Vの電源に接続した場合は、出力のHighレベルが3.3Vとなり、3.3Vまたは5.0Vのシステムとの互換性を持つようになります。 $V_{CCIO}$ が3.0V以上の電圧で動作するデバイスでは、 $t_{ODI}$ よりも高速となる $t_{OD2}$ のタイミング遅延が実現されます。

表13はFLEX 10KEデバイスでサポートされているMultiVolt I/O機能をまとめたものです。

| 表13 FLEX 10KEデバイスのMultiVolt I/Oサポート |     |              |              |              |          |          |

|-------------------------------------|-----|--------------|--------------|--------------|----------|----------|

| V <sub>CCIO</sub> (V)               | )   |              |              |              |          |          |

|                                     | 2.5 | 3.3          | 5.0          | 2.5          | 3.3      | 5.0      |

| 2.5                                 | ~   | <b>√</b> (1) | <b>✓</b> (1) | ~            |          |          |

| 3.3                                 | ~   | ~            | <b>✓</b> (1) | <b>✓</b> (2) | <b>/</b> | <b>/</b> |

#### 注:

- (1)  $V_{\text{CCIO}}$ より高い電圧の信号で入力をドライブするときは、PCIクランピング・ダイオードをディセーブルする必要があります。

- (2)  $V_{\rm CCIO}$ =3.3 $\rm V$ の場合、FLEX 10 $\rm KE$ デバイスは3.3 $\rm V$ の入力電圧にも対応している2.5 $\rm V$ デバイスをドライブすることができます。

FLEX 10KEのオープン・ドレイン出力ピンは(5.0Vの電源に対するプルアップ抵抗を接続)、3.5Vの $V_{IH}$ を必要とする5.0VのCMOS入力ピンをドライブすることができます。オープン・ドレイン・ピンがアクティブになると、このピンはLowレベルをドライブします。このピンがインアクティブになると、このピンと接続されている配線パターンは抵抗により5.0Vにプルアップされます。オープン・ドレイン・ピンはLowレベルをドライブするかトライ・ステートになるだけでHighレベルをドライブすることはありません。このときの信号の立ち上がり時間はプルアップ抵抗と負荷インピーダンスに依存します。プルアップ抵抗を使用する場合は、 $I_{OL}$ の規格に注意する必要があります。

### 電源のシーケンスと活線挿抜

FLEX 10KEデバイスは複数の電源電圧がある環境で使用されることがあるため、可能性のある任意の電源投入シーケンスに対応できるように設計されています。 $V_{CCIO}$ と $V_{CCINT}$ のプレーンには、任意の順番で電源を供給することができます。

電源の投入前および投入中でも、FLEX 10KEデバイスに対する信号のドライブをデバイスにダメージを与えることなく行えます。また、FLEX 10KEデバイスは、電源の投入時に信号を外部にドライブしません。FLEX 10KEデバイスは動作条件に達すると、ユーザの指定した動作を行います。

Page 42 Altera Corporation

IEEE Std. 1149.1(JTAG) バウンダリ・ スキャンの サポート FLEX 10KEファミリのすべてのデバイスは、IEEE Std. 1149.1-1990の標準規格に準拠したJTAG BSTをサポートしています。また、FLEX 10KEファミリのすべてのデバイスは、JTAGピンを使用して、BitBlasterまたはByteBlasterMVダウンロード・ケーブル、あるいはプログラミング/テスト用言語である $Jam^{TM}$ を採用したハードウェアからコンフィギュレーションすることができます。JTAGバウンダリ・スキャン・テストはコンフィギュレーションの前か後で実行できますが、コンフィギュレーションの期間中には実行できません。FLEX 10KEデバイスは下記の表14に示されているJTAGインストラクションをサポートしています。

| 表14 FLEX 10KE5     | デバイスがサポートするJTAGインストラクション                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG インストラクション     | 内 容                                                                                                                                                                               |

| SAMPLE/PRELOAD     | 動作中のデバイスのピンから信号を取り込んでテストすることができる。また、最初の<br>データ・パターンをデバイス・ピンに出力させることができる。                                                                                                          |

| EXTEST             | 出力ピンにテスト・パターンを強制的に与え、入力ピンのデータを取り込んでテスト結果を比較することによって外部回路との接続とボードレベルの配線がテストできる。                                                                                                     |

| BYPASS             | TDIピンとTDOピンの間に1ビットのバイパス・レジスタを配置することによって、デバイスに通常の動作をさせながらBSTデータが指定したデバイスをバイパスして隣接したデバイスに同期転送されるようにすることができる。                                                                        |

| USERCODE           | ユーザ定義の電子署名レジスタであるUSERCODEレジスタを選択し、これをTDIとTDOのピン間に配置することによって、TDOにUSERCODEをシリアルにシフト・アウトさせることができる。                                                                                   |

| IDCODE             | IDCODEレジスタを選択し、これをTDIとTDOのピン間に配置することによって、<br>TDOにIDCODEをシリアルにシフト・アウトさせることができる。                                                                                                    |

| ICR関連<br>インストラクション | これらのインストラクションは、JTAGポートを使用して、BitBlasterまたは<br>ByteBlasterMVの各ダウンロード・ケーブル、あるいはJamファイル(.jam)または<br>Jam Byte-Codeファイル(.jbc)を採用したエンベデッド・プロセッサからFLEX<br>10KEデバイスをコンフィギュレーションするときに使用される。 |

FLEX 10KEのインストラクション・レジスタの長さは、10ビットです。また、FLEX 10KEデバイスのUSERCODEレジスタの長さは32ビットとなっており、このうち7ビットがユーザによって定義され、25ビット分はあらかじめ定義されています。表15と表16は各FLEX 10KEデバイスのバウンダリ・スキャン・レジスタの長さとデバイスIDCODEを示したものです。

| 表15 FLEX 10KEデバイスのバウンダリ・スキャン・レジスタの長さ |                    |  |  |  |

|--------------------------------------|--------------------|--|--|--|

| デバイス名                                | バウンダリ・スキャン・レジスタの長さ |  |  |  |

| EPF10K30E                            | 690                |  |  |  |

| EPF10K50E<br>EPF10K50S               | 798                |  |  |  |

| EPF10K100B                           | 873                |  |  |  |

| EPF10K100E                           | 1,050              |  |  |  |

| EPF10K130E                           | 1,308              |  |  |  |

| EPF10K200E<br>EPF10K200S             | 1,446              |  |  |  |

| 表16 FLEX 10KEデバイスの32ビットIDCODE 注(1) |                 |                |      |              |      |                      |                 |

|------------------------------------|-----------------|----------------|------|--------------|------|----------------------|-----------------|

| デバイス名                              |                 | IDCODE (32ビット) |      |              |      |                      |                 |

|                                    | バージョン<br>(4ビット) |                |      | ・ナン/<br>゚ット) | "    | 製造業者IDコード<br>(11ビット) | 1 (1ビット)<br>(2) |

| EPF10K30E                          | 0001            | 0001           | 0000 | 0011         | 0000 | 00001101110          | 1               |

| EPF10K50E<br>EPF10K50S             | 0001            | 0001           | 0000 | 0101         | 0000 | 00001101110          | 1               |

| EPF10K100B                         | 0001            | 0000           | 0001 | 0000         | 0000 | 00001101110          | 1               |

| EPF10K100E                         | 0010            | 0000           | 0001 | 0000         | 0000 | 00001101110          | 1               |

| EPF10K130E                         | 0001            | 0000           | 0001 | 0011         | 0000 | 00001101110          | 1               |

| EPF10K200E<br>EPF10K200S           | 0001            | 0000           | 0010 | 0000         | 0000 | 00001101110          | 1               |

注:

- 左側がMSBです。

- (2) すべてのJTAG IDCODEのLSBは1になっています。

FLEX 10KEデバイスのJTAGピンにはウィーク・プルアップ抵抗が内蔵されています。

JTAGの動作に関する詳細については、下記の資料を参照してください。

- アプリケーション・ノート、AN 39「IEEE Std. 1149.1(JTAG) Boundary-Scan Testing in Altera Devices」(日本語版「アルテラ・デバイスのJTAG バウンダリ・スキャン・テスト」)

- 「BitBlaster Serial Download Cable」のデータシート

- 「ByteBlasterMV Parallel Port Download Cable」のデータシート

- 「Jam Programming & Test Language Specification」

Page 44 Altera Corporation

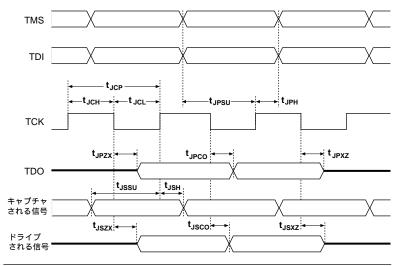

図20はJTAG信号に対するタイミングの規格を示したものです。

図20 FLEX 10KEデバイスのJTAG信号波形

表17はFLEX 10KEデバイスのJTAG信号に関連したタイミング・パラメータとその値を示したものです。

| 表17 FLEX 10KEのJTAGタイミング・パラメータと値 |                                    |     |    |    |  |

|---------------------------------|------------------------------------|-----|----|----|--|

| シンボル                            | パラメータ                              | 最小  | 最大 | 単位 |  |

| t <sub>JCP</sub>                | TCKクロックの期間                         | 100 |    | ns |  |

| t <sub>JCH</sub>                | TCKクロックのHigh時間                     | 50  |    | ns |  |

| t <sub>JCL</sub>                | TCKクロックのLow時間                      | 50  |    | ns |  |

| t <sub>JPSU</sub>               | JTAGポートのセットアップ・タイム                 | 20  |    | ns |  |

| t <sub>JPH</sub>                | JTAGポートのホールド・タイム                   | 45  |    | ns |  |

| t <sub>JPCO</sub>               | JTAGポートの「Clock-to-Output」遅延        |     | 25 | ns |  |

| t <sub>JPZX</sub>               | JTAGポートのハイ・インピーダンスから有効出力まで         |     | 25 | ns |  |

| t <sub>JPXZ</sub>               | JTAGポートの有効出力からハイ・インピーダンスまで         |     | 25 | ns |  |

| t <sub>JSSU</sub>               | キャプチャ・レジスタのセットアップ・タイム              | 20  |    | ns |  |

| t <sub>JSH</sub>                | キャプチャ・レジスタのホールド・タイム                | 45  |    | ns |  |

| t <sub>JSCO</sub>               | アップデート・レジスタの「Clock-to-Output」遅延    |     | 35 | ns |  |

| t <sub>JSZX</sub>               | アップデート・レジスタのハイ・インピーダンスから有<br>効出力まで |     | 35 | ns |  |

| t <sub>JSXZ</sub>               | アップデート・レジスタの有効出力からハイ・インピー<br>ダンスまで |     | 35 | ns |  |

# デバイスの テスト

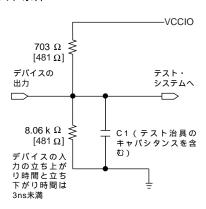

FLEX 10KEの各デバイスにはファンクション・テストが実施されており、その動作が保証されています。コンフィギュレーションされる各SRAM(Static Random Access Memory)ビットとすべての論理機能は完全にテストされており、100%のコンフィギュレーションが保証されています。FLEX 10KEデバイスのACテストは、図21に等価な条件で行われています。デバイスのコンフィギュレーションとテストには、生産フローの中のあらゆる工程で複数のテスト・パターンが使用されています。

### 図21 FLEX 10KEデバイスのACテスト条件

電源のトランジェントがAC特性の測定 に影響を及ぼすことがあります。正確な 測定を行うため、複数の出力を同時に変 化させることは避けてください。スレッ ショルドのテストはACの測定条件では 行わないでください。デバイスの出力が 負荷のキャパシタンスをディスチャージ するときに、大振幅で高速なグランド電 流のトランジェントが発生し、これらの トランジェントがグランド・ピンとテス ト・システムのグランドとの間に存在す る寄生インダクタンスに流れると、ノイ ズ・マージンが著しく低下します。[] 内の数値は2.5V出力に対してのもので す。[]のない数値は3.3V出力に対す るものです。

# 動作条件

表18から表21は2.5V動作のFLEX 10KEデバイスの絶対最大定格、推奨動作条件、DC特性、およびキャパシタンスを示したものです。

| 表18 FLEX 10KE 2.5Vデバイスの絶対最大定格 <i>注(1)</i> |              |                                |       |      |    |  |

|-------------------------------------------|--------------|--------------------------------|-------|------|----|--|

| シンボル                                      | パラメータ        | 条件                             | 最小    | 最大   | 単位 |  |

| V <sub>CCINT</sub>                        | 供給電圧         | GNDに対して <i>注(2)</i>            | - 0.5 | 3.6  | V  |  |

| V <sub>CCIO</sub>                         |              |                                | - 0.5 | 4.6  | V  |  |

| VI                                        | DC入力電圧       |                                | - 2.0 | 5.75 | V  |  |

| I <sub>OUT</sub>                          | ピンあたりのDC出力電流 |                                | - 25  | 25   | mA |  |

| T <sub>STG</sub>                          | 保存温度         | バイアスなし                         | - 65  | 150  |    |  |

| T <sub>AMB</sub>                          | 動作周囲温度       | バイアス時                          | - 65  | 135  |    |  |

| T <sub>J</sub>                            | 接合温度         | PQFP、TQFPおよびBGAパッケージ、<br>バイアス時 |       | 135  |    |  |

|                                           |              | セラミックPGAパッケージ、バイアス時            |       | 150  |    |  |

Page 46 Altera Corporation

| 表19 FLEX 10KE 2.5Vデバイスの推奨動作条件 |                         |          |             |                   |    |  |

|-------------------------------|-------------------------|----------|-------------|-------------------|----|--|

| シンボル                          | パラメータ                   | 条件       | 最小          | 最大                | 単位 |  |

| V <sub>CCINT</sub>            | 内部ロジックと入力バッファ用<br>供給電圧  | 注(3)、(4) | 2.30 (2.30) | 2.70 (2.70)       | >  |  |

| V <sub>CCIO</sub>             | 出力バッファ用供給電圧、<br>3.3V動作時 | 注(3)、(4) | 3.00 (3.00) | 3.60 (3.60)       | >  |  |

|                               | 出力バッファ用供給電圧、<br>2.5V動作時 | 注(3)、(4) | 2.30 (2.30) | 2.70 (2.70)       | V  |  |

| VI                            | 入力電圧                    | 注(5)     | - 0.5       | 5.75              | ٧  |  |

| Vo                            | 出力電圧                    |          | 0           | V <sub>CCIO</sub> | V  |  |

| T <sub>A</sub>                | 動作周囲温度                  | 一般用      | 0           | 70                |    |  |

|                               |                         | 工業用      | - 40        | 85                |    |  |

| TJ                            | 動作接合温度                  | 一般用      | 0           | 85                |    |  |

|                               |                         | 工業用      | - 40        | 100               |    |  |

| t <sub>R</sub>                | 立ち上がり時間                 |          |             | 40                | ns |  |

| t <sub>F</sub>                | 立ち下がり時間                 |          |             | 40                | ns |  |

| シンボル              | パラメータ                        | 条件                                                                                               | 最小                                   | 標準 | 最大                                   | 単位 |

|-------------------|------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|----|--------------------------------------|----|

| V <sub>IH</sub>   | High レベル入力電圧                 |                                                                                                  | 1.7, 0.5 × V <sub>CCIO</sub><br>注(8) |    | 5.75                                 | ٧  |

| V <sub>IL</sub>   | Lowレベル入力電圧                   |                                                                                                  | - 0.5                                |    | 0.8, 0.3 × V <sub>CCIO</sub><br>注(8) | ٧  |

| V <sub>OH</sub>   | 3.3V High レベルTTL出力電圧         | I <sub>OH</sub> = -8mA DC,<br>V <sub>CCIO</sub> = 3.00V <i>注(9)</i>                              | 2.4                                  |    |                                      | V  |

|                   | 3.3V High レベルCMOS出力電圧        | I <sub>OH</sub> = - 0.1mA DC,<br>V <sub>CCIO</sub> = 3.00V <i>注(9)</i>                           | V <sub>CCIO</sub> - 0.2              |    |                                      | V  |

|                   | 3.3V High レベルPCI出力電圧         | $I_{OH}$ = - 0.5mA DC,<br>$V_{CCIO}$ = 3.00 to 3.60V<br>$ \pm (9) $                              | 0.9 × V <sub>CCIO</sub>              |    |                                      | V  |

|                   | 2.5V High レベル出力電圧            | I <sub>OH</sub> = - 0.1mA DC,<br>V <sub>CCIO</sub> = 2.30V <i>注(9)</i>                           | 2.1                                  |    |                                      | V  |

|                   |                              | I <sub>OH</sub> = - 1mA DC,<br>V <sub>CCIO</sub> = 2.30V <i>注(9)</i>                             | 2.0                                  |    |                                      | ٧  |

|                   |                              | I <sub>OH</sub> = - 2mA DC,<br>V <sub>CCIO</sub> = 2.30V <i>注(9)</i>                             | 1.7                                  |    |                                      | V  |

| V <sub>OL</sub>   | 3.3V LowレベルTTL出力電圧           | I <sub>OL</sub> = 12mA DC,<br>V <sub>CCIO</sub> = 3.00V <i>注(9)</i>                              |                                      |    | 0.45                                 | ٧  |

|                   | 3.3V LowレベルCMOS出力電圧          | I <sub>OL</sub> = 0.1mA DC,<br>V <sub>CCIO</sub> = 3.00V <i>注(10)</i>                            |                                      |    | 0.2                                  | V  |

|                   | 3.3V LowレベルPCI出力電圧           | $I_{OL} = 1.5 \text{mA DC},$<br>$V_{CCIO} = 3.00 \text{ to } 3.60 \text{V}$<br>$\not\equiv (10)$ |                                      |    | 0.1 × V <sub>CCIO</sub>              | V  |

|                   | 2.5V Lowレベル出力電圧              | $I_{OL} = 0.1 \text{mA DC},$<br>$V_{CCIO} = 2.30 \text{V}$ $\not\equiv (10)$                     |                                      |    | 0.2                                  | V  |

|                   |                              | I <sub>OL</sub> = 1mA DC,<br>V <sub>CCIO</sub> = 2.30V <i>注(10)</i>                              |                                      |    | 0.4                                  | V  |

|                   |                              | $I_{OL}$ = 2mA DC,<br>$V_{CCIO}$ = 2.30V  注(10)                                                  |                                      |    | 0.7                                  | V  |

| I                 | 入力ピン・リーク電流                   | $V_1 = 5.3 \text{ to } -0.3 \text{V}$                                                            | - 10                                 |    | 10                                   | μА |

| l <sub>OZ</sub>   | トライ・ステートI/Oピン・リーク<br>電流      | $V_0 = 5.3 \text{ to } -0.3 \text{V}$                                                            | - 10                                 |    | 10                                   | μА |

| I <sub>CC0</sub>  | V <sub>CC</sub> 供給電流(スタンバイ時) | V <sub>i</sub> =ground、無負荷、入<br>力のトグルなし                                                          |                                      | 5  |                                      | mA |

|                   |                              | V <sub>I</sub> =ground、無負荷、入<br>力のトグルなし <i>注(11)</i>                                             |                                      | 10 |                                      | mA |

| R <sub>CONF</sub> | コンフィギュレーション前および              | V <sub>CCIO</sub> = 3.0V 注(12)                                                                   | 20                                   |    | 50                                   | kΩ |

|                   | 実行時のI/Oピンのプルアップ抵抗<br>値       | V <sub>CCIO</sub> = 2.3V 注(12)                                                                   | 30                                   |    | 80                                   | kΩ |

Page 48 Altera Corporation

| 表21                | 表21 FLEX 10KEデバイスのキャパシタンス 注(13) |                                   |    |    |    |  |

|--------------------|---------------------------------|-----------------------------------|----|----|----|--|

| シンボル               | パラメータ                           | 条件                                | 最小 | 最大 | 単位 |  |

| C <sub>IN</sub>    | 入力キャパシタンス                       | V <sub>IN</sub> = 0 V, f = 1.0MHz |    | 10 | pF |  |

| C <sub>INCLK</sub> | クロック専用ピンの入力キャパシタンス              | V <sub>IN</sub> = 0 V, f = 1.0MHz |    | 12 | pF |  |

| C <sub>OUT</sub>   | 出力キャパシタンス                       | $V_{OUT} = 0 V, f = 1.0MHz$       |    | 10 | pF |  |

### 注:

- (1) 絶対最大定格については、「Operating Requirements for Altera Devices」(日本語版「アルテラ・デバイス使用上の注意」)を参照してくだ

- (2) 最低DC入力電圧は 0.5Vです。無負荷で入力電流が100mA以下で20ns以下の幅の条件であれば、過渡状態の期間に入力が 2.0Vまでアンダシュート、または5.75Vまでオーバシュートしても構いません。

- (3) カッコ内の数値は工業用温度範囲の製品の場合です。

- (4) V<sub>CC</sub>の立ち上がりは最大100msです。V<sub>CC</sub>は一定の比率で上昇する必要があります。

- (5) V<sub>CCIO</sub>およびV<sub>CCINT</sub>に電源を供給する前に、入力専用ピン、クロック専用ピン、I/Oピン、JTAGピンを含むすべてのピンをドライブすることが可能です。

- (6) 標準値はT<sub>A</sub>=25 、V<sub>CCINT</sub>=2.5V、V<sub>CCIO</sub>=2.5Vまたは3.3Vの条件のときのものです。

- (7) これらの値は47ページに記載されている表19の「FLEX 10KE 2.5Vデバイスの推奨動作条件」をベースに規定されています。

- (8) FLEX 10KEデバイスの入力パッファは2.5V、3.3VのLVTTLとLVCMOS、5.0VのTTLおよびCMOS信号と互換性があります。また、V<sub>CCIO</sub>とV<sub>CCINT</sub>の関係が図22に示されている条件に適合している場合は、入力パッファが3.3VのPCI仕様準拠となります。

- (9) I<sub>OH</sub>のパラメータはHighレベルTTL、PCIまたはCMOS出力電流として参照されます。

- (10) I<sub>OL</sub>のパラメータはLowレベルTTL、PCIまたはCMOS出力電流として参照されます。このパラメータは出力ピンと同じようにオープン・ドレイン・ピンにも適用されます。

- (11) このパラメータは、一般用温度範囲の-1スピード・グレード製品と工業用温度範囲の-2スピード・グレード製品に適用されます。

- (12) ピンが外部ソースからV<sub>CCIO</sub>よりも高い電圧でドライブされる場合は、ブルアップ抵抗の値が低下します。

- (13) キャパシタンスはサンプル・テストのみです。

図22は3.3VのPCI仕様に準拠した $V_{CCIO}$ と $V_{CCINT}$ の関係を示したものです。

V<sub>CCINT</sub> (V) 2.5 2.3 2.3 2.3 2.3 V<sub>CCIO</sub> (V)

図22 3.3VのPCI仕様の準拠範囲となるV<sub>CCIO</sub>とV<sub>CCINT</sub>の関係

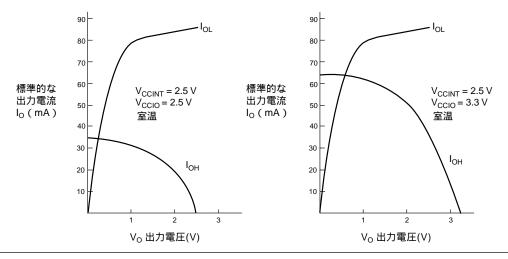

図23は、 $V_{CCIO}$ を2.5 V および3.3 V に設定したときのFLEX 10KEデバイスの標準的な出力ドライブ特性を示したものです。出力ドライバは3.3 V の PCI Local Bus Specification, Revision 2.2 の規格と互換性があります(VCCIOが3.3 V に接続された場合)。また、-1スピード・グレードのFLEX 10KEデバイスは、PCI Local Bus Specification, Revision 2.2 で要求される Drive Strengthの 仕様にも準拠しています(VCCINTピンに最小供給電圧である2.375 V が供給されていて、VCCIOピンが3.3 V に接続されていた場合)。これらのデバイスは、オープンな5.0 V PCIシステムにも使用可能となります。

Page 50 Altera Corporation

### 図23 FLEX 10KEデバイスの出力ドライブ特性

# タイミング・ モデル

FLEX 10KEデバイスでは、連続した高性能な配線リソースとなっている FastTrackインタコネクトによって、予測可能な性能、正確なシミュレーションとタイミング解析が確保されています。この予測可能な性能は、セグメント化された配線構造を使用しているために性能が予測不可能となる FPGAと大きく異なる点です。

デバイス性能は、ソースから、配線を通ってデスティネーションに至る信号パスをトレースすることで推定可能になります。例えば、同じロウに位置する2つのLE間のレジスタ性能は、下記のパラメータを加算することで算出できます。

- LEレジスタの「Clock-to-Outout」遅延(t<sub>CO</sub>)

- 配線遅延(t<sub>SAMEROW</sub>)

- LEルック・アップ・テーブルの遅延( $t_{LUT}$ )

- LEレジスタのセットアップ・タイム ( $t_{SII}$ )

配線遅延は、ソースとデスティネーションとなるLEの位置によって決定されます。さらに複雑なレジスタ間のパスには、ソースとデスティネーションとなるLEの間に複数の組み合わせ回路が含まれることがあります。

タイミング・シミュレーションと遅延時間予測の機能は、MAX+PLUS IIのシミュレータおよびタイミング・アナライザ、業界標準の複数のEDAツールによってサポートされています。MAX+PLUS IIのシミュレータはロジック・デザインの正確さを評価するために論理合成前に実行されるファンクショナル・シミュレーション、および合成後のタイミング・シミュレーションを0.1nsの分解能で実行できます。また、タイミング・アナライザは任意のポイント間の遅延時間情報、セットアップ・タイムとホールド・タイムの解析、デバイス全体の性能解析などの機能を提供しています。

図24は全体のタイミング・モデルを示したもので、ここではFLEX 10KEデバイス内で使用される可能性のある多様なエレメント間のパスが示されています。

## 図24 FLEX 10KEのタイミング・モデル

Page 52 Altera Corporation

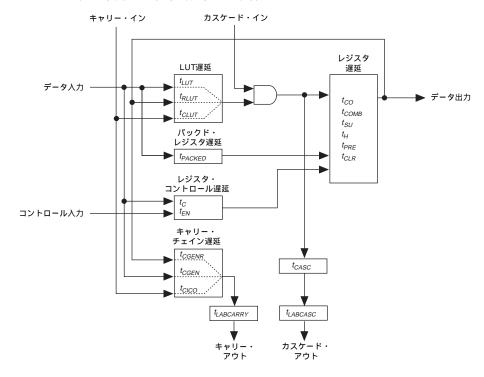

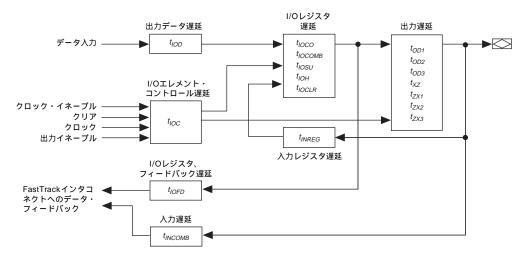

図25から図28は、LE、IOEおよびEAB内の多様なパスに対応した遅延と双方向のタイミング・モデルを示したものです。

## 図25 FLEX 10KEデバイスのLEタイミング・モデル

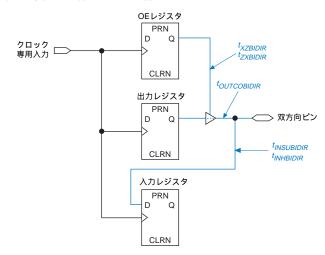

### 図26 FLEX 10KEデバイスのIOEタイミング・モデル

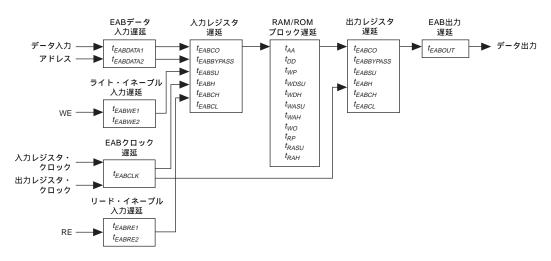

### 図27 FLEX 10KEデバイスのEABタイミング・モデル

Page 54 Altera Corporation

図28 同期双方向ピンの外部タイミング・モデル

表22から表26は、FLEX 10KEデバイスの内部タイミング・パラメータを解説しています。表27から表29は、FLEX 10KEデバイスの外部タイミング・パラメータとそのシンボルを示したものです。これらのデバイスの詳細なタイミング情報は確定次第、リリースされる予定です。

| 表22 LEタイミング・マイクロパラメータ (1/2) 注(1) |                                                                       |    |  |  |

|----------------------------------|-----------------------------------------------------------------------|----|--|--|

| シンボル                             | パラメータ                                                                 | 条件 |  |  |

| t <sub>LUT</sub>                 | データ入力のLUT遅延                                                           |    |  |  |

| t <sub>CLUT</sub>                | キャリー入力のLUT遅延                                                          |    |  |  |

| t <sub>RLUT</sub>                | LEレジスタ・フィードバックのLUT遅延                                                  |    |  |  |

| t <sub>PACKED</sub>              | データ入力からパックド・レジスタへの遅延                                                  |    |  |  |

| t <sub>EN</sub>                  | LEレジスタのイネーブル遅延                                                        |    |  |  |

| t <sub>CICO</sub>                | キャリー・インからキャリー・アウトまでの遅延                                                |    |  |  |

| t <sub>CGEN</sub>                | データ入力からキャリー・アウトまでの遅延                                                  |    |  |  |

| t <sub>CGENR</sub>               | LEレジスタのフィードバックからキャリー・アウトまでの遅延                                         |    |  |  |

| t <sub>CASC</sub>                | カスケード・インからカスケード・アウトまでの遅延                                              |    |  |  |

| $t_C$                            | LEレジスタのコントロール信号遅延                                                     |    |  |  |

| t <sub>CO</sub>                  | LEレジスタの「Clock-to-Output」遅延                                            |    |  |  |

| t <sub>COMB</sub>                | 組み合わせ回路の遅延                                                            |    |  |  |

| t <sub>SU</sub>                  | LEレジスタのデータ、イネーブル信号のセットアップ・タイム。非同期クリア、<br>プリセットまたはロード後のLEレジスタ、リカバリ・タイム |    |  |  |

| t <sub>H</sub>                   | LEレジスタのデータおよびイネーブル信号ホールド・タイム                                          |    |  |  |

| t <sub>PRE</sub>                 | LEレジスタのプリセット遅延                                                        |    |  |  |

| 表22 LEタイミング・マイクロパラメータ (2/2) 注(1) |                        |    |  |  |

|----------------------------------|------------------------|----|--|--|

| シンボル                             | パラメータ                  | 条件 |  |  |

| t <sub>CLR</sub>                 | LEレジスタのクリア遅延           |    |  |  |

| t <sub>CH</sub>                  | クロック・ピンからのクロックHigh最小期間 |    |  |  |

| t <sub>CL</sub>                  | クロック・ピンからのクロックLow最小期間  |    |  |  |

| シンボル                | パラメータ                                                                       | 条件             |  |

|---------------------|-----------------------------------------------------------------------------|----------------|--|

| t <sub>IOD</sub>    | IOEデータ遅延                                                                    |                |  |

| t <sub>IOC</sub>    | IOEレジスタのコントロール信号遅延                                                          |                |  |

| t <sub>IOCO</sub>   | IOEレジスタの「Clock-to-Output」遅延                                                 |                |  |

| $t_{IOCOMB}$        | IOE組み合わせ回路出力遅延                                                              |                |  |

| t <sub>IOSU</sub>   | IOEレジスタのデータおよびイネーブル信号セットアップ・タイム<br>非同期クリア入力後のIOEレジスタ、リカバリ・タイム               |                |  |

| t <sub>IOH</sub>    | IOEレジスタのデータおよびイネーブル信号ホールド・タイム                                               |                |  |

| t <sub>IOCLR</sub>  | IOEレジスタのクリア・タイム                                                             |                |  |

| t <sub>OD1</sub>    | 出力バッファとパッドの遅延 Slow Slew Rate= off、 V <sub>CCIO</sub> =V <sub>CCINT</sub>    | C1 = 35pF 注(2) |  |

| t <sub>OD2</sub>    | 出力バッファとパッドの遅延 Slow Slew Rate= off、 V <sub>CCIO</sub> =Low Voltage           | C1 = 35pF 注(3) |  |

| t <sub>OD3</sub>    | 出力バッファとパッドの遅延 Slow Slew Rate= on                                            | C1 = 35pF 注(4) |  |

| $t_{XZ}$            | IOE出力パッファのディセーブル遅延                                                          |                |  |

| $t_{ZX1}$           | IOE出力パッファのイネーブル遅延 Slow Slew Rate= off、V <sub>CCIO</sub> =V <sub>CCINT</sub> | C1 = 35pF 注(2) |  |

| $t_{ZX2}$           | IOE出力バッファのイネーブル遅延 Slow Slew Rate= off、V <sub>CCIO</sub> =Low Voltage        | C1 = 35pF 注(3) |  |

| $t_{ZX3}$           | IOE出力パッファのイネーブル遅延 Slow Slew Rate= on                                        | C1 = 35pF 注(4) |  |

| t <sub>INREG</sub>  | IOE入力パッドとバッファからIOEレジスタまでの遅延                                                 |                |  |

| t <sub>IOFD</sub>   | IOEレジスタのフィードバック遅延                                                           |                |  |

| t <sub>INCOMB</sub> | IOEの入力パッドとバッファからFastTrackインタコネクトまでの遅延                                       |                |  |

Page 56 Altera Corporation

| シンボル                   | パラメータ                              | 条件   |

|------------------------|------------------------------------|------|

| t <sub>EABDATA1</sub>  | EABの組み合わせ入力に対するデータまたはアドレスの遅延       |      |

| t <sub>EABDATA2</sub>  | EABのレジスタ入力に対するデータまたはアドレスの遅延        |      |

| t <sub>EABWE1</sub>    | EABの組み合わせ入力に対するライト・イネーブルの遅延        |      |

| t <sub>EABWE2</sub>    | EABのレジスタ入力に対するライト・イネーブルの遅延         |      |

| t <sub>EABRE1</sub>    | EABの組み合わせ入力に対するリード・イネーブルの遅延        |      |

| t <sub>EABRE2</sub>    | EABのレジスタ入力に対するリード・イネーブルの遅延         |      |

| t <sub>EABCLK</sub>    | EABレジスタのクロック遅延                     |      |

| t <sub>EABCO</sub>     | EABレジスタの「Clock-to-Output」遅延        |      |

| t <sub>EABBYPASS</sub> | レジスタ・バイパス遅延                        |      |

| t <sub>EABSU</sub>     | EABレジスタのセットアップ・タイム                 |      |

| t <sub>EABH</sub>      | EABレジスタのホールド・タイム                   |      |

| t <sub>EABCLR</sub>    | EABレジスタ出力の非同期クリア時間                 |      |

| t <sub>EABCH</sub>     | クロック、High期間                        |      |

| t <sub>EABCL</sub>     | クロック、Low期間                         |      |

| $t_{AA}$               | アドレス・アクセス遅延(リード・イネーブルから出力までの遅延を含む) |      |

| t <sub>WP</sub>        | ライト・パルス幅                           |      |

| $t_{RP}$               | リード・パルス幅                           |      |

| t <sub>WDSU</sub>      | ライト・パルスの立ち下がり前のデータ・セットアップ・タイム      | 注(5) |

| t <sub>WDH</sub>       | ライト・パルスの立ち下がり後のデータ・ホールド・タイム        | 注(5) |

| t <sub>WASU</sub>      | ライト・パルスの立ち上がりエッジ前のアドレス・セットアップ・タイム  | 注(5) |

| $t_{WAH}$              | ライト・パルスの立ち下がりエッジ後のアドレス・ホールド・タイム    | 注(5) |

| t <sub>WASU</sub>      | ライト・パルスの立ち上がりエッジ前のアドレス・セットアップ・タイム  |      |

| t <sub>WAH</sub>       | ライト・パルスの立ち下がりエッジ後のアドレス・ホールド・タイム    |      |

| t <sub>RASU</sub>      | リード・パルスの立ち上がり前のアドレス・セットアップ・タイム     |      |

| t <sub>RAH</sub>       | リード・パルスの立ち下がり後のアドレス・ホールド・タイム       |      |

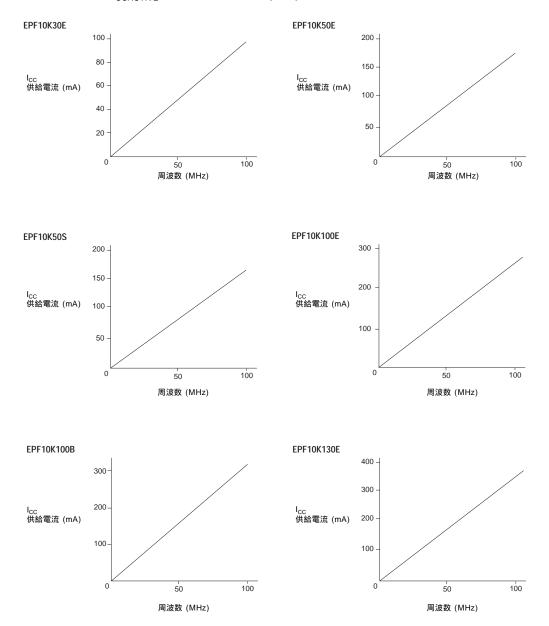

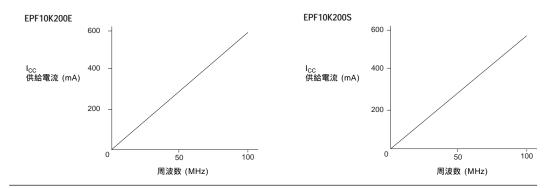

| $t_{WO}$               | ライト・イネーブルからデータ出力確定までの遅延            |      |