# SignalTap エンベデッド・ロジック・ アナライザ・メガファンクション

1999年 4月 ver. 1 Data Sheet

## 特長

- Quartus<sup>TM</sup>ソフトウェアの一部として提供

- デザインをシステム・スピードで動作させながら、内部ノードの観測が 可能

- パラメータ化されたロジック・アナライザのメガファンクション

- プログラマブル・ロジック・デバイス(PLD)の内部信号をキャプ チャ

- マルチ・レベルのトリガ機能

- ロジック・アナライザ・メガファンクションの使用には、デザイン・ファイルの変更が不要

- APEX<sup>TM</sup> 20Kデバイスに最適化

- BGA (Ball-Grid Array)パッケージのピンに対しても効果的なプロービング機能を提供

- Quartus開発システムの環境でロジック・アナライザのコントロール機能を提供

- 信号の選択

- トリガ条件の設定

- メモリの構成

- 波形表示機能

## 概要

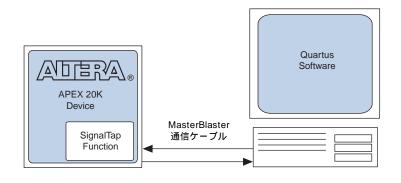

System-on-a-Programmable-Chip $^{\rm TM}$ の集積化が、新しいSignal $^{\rm TM}$ ロジック・アナライザ・メガファンクションと共にサポートされるようになりました。信号の選択、ロジック・アナライザのコントロール、信号の表示機能などは、Quartus開発システム内から設定することができます。APEX  $^{\rm 20}$ KデバイスとQuartusソフトウェア間のデータ転送は、MasterBlaster $^{\rm TM}$ 通信ケーブルによってサポートされています。ユーザは、このデータを使用してデザインの解析と検証を行うことができます。

# 機能の説明

SignalTapメガファンクションは、APEX 20Kデバイスの内部信号へのアクセスを可能にするパラメータ化されたエンベデッド・ロジック・アナライザです。SignalTapのアーキテクチャはスケーラブルなロジック・アナライザのプリミティブで構成されるようになっており、複数の入力チャネルにマルチ・レベルのトリガ・シーケンスが設定できます。SignalTapメガファンクションは、キャプチャしたデータのストアにAPEX 20Kデバイスに内蔵されているエンベデッド・システム・ブロック(ESB)のRAMを使用することができます。

Quartusソフトウェアは作成したデザイン機能に変更を加えることなく、 SignalTapロジック・アナライザをデザイン・ファイルに自動的にインスタ ンス化することができます。作成したデザインにこのロジック・アナライザ を追加した場合でも、インクリメンタルなコンパイルの実行後にデザイン性 能が低下することはありません。

ロジック・アナライザでキャプチャされたデータは、MasterBlaster通信ケーブルにより、USB (Universal Serial Bus) ポートまたはシリアル・ポートを通じてホスト・コンピュータに転送できます。図 1 を参照してください。

### 図1 SignalTapロジック・アナライザ

### トリガの条件

任意の入力信号チャネルに対して、多様なトリガ条件を設定することができます。表1は、各入力信号に対する設定可能なトリガ条件を示したものです。

| 表 1 各チャネルに対するトリガ条件 |                                                |  |  |  |  |

|--------------------|------------------------------------------------|--|--|--|--|

| トリガ条件              | 説明                                             |  |  |  |  |

| ドント・ケア             | ディフォルトのトリガ条件。このチャネルはトリガ・イベントの検<br>出に使用されない。    |  |  |  |  |

| Low                | このチャネルがLowになったときに、アナライザがトリガする。                 |  |  |  |  |

| High               | このチャネルがHighになったときに、アナライザがトリガする。                |  |  |  |  |

| 立ち下がり              | このチャネルに立ち下がりが発生したときに、アナライザがトリガする。              |  |  |  |  |

| 立ち上がり              | このチャネルに立ち上がりが発生したときに、アナライザがトリガする。              |  |  |  |  |

| 立ち上がり、<br>または立ち下がり | このチャネルに立ち上がり、または立ち下がりが発生したときに、<br>アナライザがトリガする。 |  |  |  |  |

#### 時間とカウント

トリガ・イベントの検出には、2種類の時間条件(タイム・フィルタとイベント)が設定できます。

タイム・フィルタは、HighおよびLowのロジック・レベルで構成されるトリガ・パターンをモニタします。タイム・フィルタには指定したパターン

Page 2 Altera Corporation

が発生する期間を指定することができ、これを同期アクイジション用クロックのサイクル数で表現することができます。また、タイム・フィルタには、指定したクロック・サイクル数でのトリガ、イベントが指定したクロック数を超えたとき、または下回ったときのトリガ条件を設定することができます。

イベント・カウンタはエッジ条件(立ち上がり、または立ち下がり)を含むトリガ・パターンに対して適用することができ、指定したパターンの発生回数を規定することができます。

#### シーケンス

このエンベデッド・ロジック・アナライザには4段階のトリガ・レベルが提供されており、さらに高い柔軟性が実現されています。トリガ・レベルが規定された条件(パターン、オプションの時間/イベント認識)になると、ロジック・アナライザは次のレベルに移行するか、トリガ動作を行います。また、オプションのタイム・アウト機能も提供されており、要求されるイベントが規定された時間内に発生しなかった場合にトリガ・シーケンスをリセットすることができます。

#### 遅延

トリガ条件が発生したときに、特定の値を入力して指定された動作を規定の クロック数だけ遅延させることができます。

#### トリガ 1/0

未使用のI/Oピンを使用して、トリガ・イベントが発生したことを示す外部 出力を設けることができます。この出力パルスの極性は、HighまたはLow のいずれかに設定できます。

未使用のI/Oピンを使用して、シーケンス内の任意のトリガ・レベルに対するトリガ入力を設定することもできます。これにより、このトリガ入力が発生するまで、そのレベルでトリガ条件が評価されないようにすることが可能になります。この入力パルスの極性は、HighまたはLowに設定できます。

#### アクイジションRAM

構成方法によっては、キャプチャしたデータをRAMにストアすることができます。このデータのストアは選択可能となっており、アクイジションRAMの使用効率を上げることができます。

データのストアは複数のトリガ・レベルに対して設定できるようになっており、ユーザは各レベルごとにデータをセーブするか、しないかを指定することができます。

### デバイス・リソースの使用

このロジック・アナライザの構成に使用されるロジック・エレメント (LE)の数は、使用されるチャネル数によって決定されます。表 2 は、このロジック・アナライザの構成に必要となるLE数を示したものです。

| 表 2 ロジック・アナライザに使用されるLE数 |          |  |  |  |  |

|-------------------------|----------|--|--|--|--|

| 使用されるチャネル数              | 使用されるLE数 |  |  |  |  |

| 1                       | 136      |  |  |  |  |

| 2                       | 144      |  |  |  |  |

| 4                       | 160      |  |  |  |  |

| 8                       | 192      |  |  |  |  |

| 16                      | 256      |  |  |  |  |

| 32                      | 384      |  |  |  |  |

| 64                      | 640      |  |  |  |  |

| 128                     | 1,152    |  |  |  |  |

このエンベデッド・ロジック・アナライザでは、アクイジション・データのストレージにデバイス内部のメモリ(ESB)を使用することができます。この場合、内蔵されているメモリ・ブロックのサイズと数は各デバイスによって異なるため、ロジック・アナライザを実現するときはこれらの値を考慮しておく必要があります。ロジック・アナライザの構成に使用されるRAMのビット数は、チャネル数とサンプル数によって決定されます。表3は、各構成方法に応じてデータのストレージに必要となるESB数を示したものです。

| 表 3 APEX 20KのESBメモリの深さ |            |     |     |       |       |  |  |

|------------------------|------------|-----|-----|-------|-------|--|--|

| チャネル数・                 | バッファ・サンプル数 |     |     |       |       |  |  |

|                        | 128        | 256 | 512 | 1,024 | 2,048 |  |  |

| 1                      |            |     |     |       | 1     |  |  |

| 2                      |            |     |     | 1     | 2     |  |  |

| 4                      |            |     | 1   | 2     | 4     |  |  |

| 8                      |            | 1   | 2   | 4     | 8     |  |  |

| 16                     | 1          | 2   | 4   | 8     | 16    |  |  |

| 32                     | 2          | 4   | 8   | 16    | 32    |  |  |

| 64                     | 4          | 8   | 16  | 32    | 64    |  |  |

| 128                    | 8          | 16  | 32  | 64    | 128   |  |  |

Page 4 Altera Corporation

# ロジック・アナ ライザの構成

このSignalTapファンクションは、複数の構成方法でロジック・アナライザの機能を実現することができます。このアナライザは下記の3種類の構成をサポートしており、情報をデバイスのRAMにストアして解析を行う構成や、I/Oピンを通じて情報を外部のシステム・アナライザに転送する構成で使用できます。

- エンベデッド・ロジック・アナライザ

- デバッギング・ポート

- トリガ出力

### エンベデッド・ロジック・アナライザ

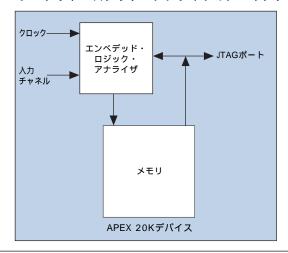

エンベデッド・ロジック・アナライザの構成では、キャプチャされるデータの入力チャネルにI/Oピンと内部ノードを接続することができます。アナライザのクロック信号は内部のグローバル・クロックから供給され、キャプチャされたデータがRAMにストアされます。そして、データがIEEE Std. 1149.1のJTAG ( Joint Test Action Group ) インタフェースを通じてデバイス外部に転送されます。図 2 を参照してください。

### 図 2 エンベデッド・ロジック・アナライザのアーキテクチャ

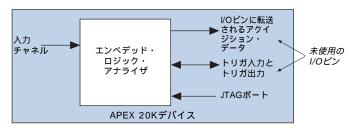

### デバッギング・ポート

このロジック・アナライザはカスタマイズが可能になっており、デバッギング・ポートの構成でも使用できます。この構成では、トリガが内部の信号データによって行われます。データが受信されると、アナライザは信号データをフィルタし、I/Oピンに出力します。このSignalTapファンクションと外部のロジック・アナライザは、オプションのトリガ入力信号とトリガ出力信号を使用することによって相互に「クロス・トリガ」の機能を実現することができます。図3を参照してください。

#### 図3 デバッギング・ポートの構成

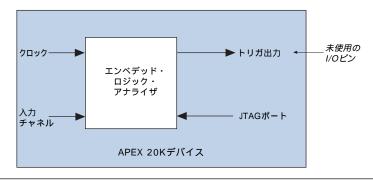

### トリガ出力

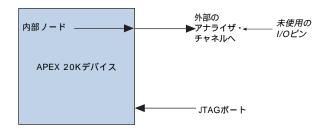

このロジック・アナライザをイベント・アナライザとして使用して、イベントの複雑なシーケンスを減少させることもできます。この場合、アナライザはデータをキャプチャし、トリガ出力を未使用のI/Oピンに転送します。トリガ出力はオシロスコープ、またはBoulder Creek Engineering 社のSignalTap Plusシステム・アナライザのような外部のシステム・アナライザでモニタすることができます。図4を参照してください。

SignalTap Plusシステム・アナライザの詳細については、 Boulder Creek Engineering社のwebサイト、http://www.bcreek.comをご覧ください。

#### 図4 ロジック・アナライザをイベント・アナライザとして使用する構成

# 内部信号のI/O ピンへの配線

SignalTapインタフェースにより、内部信号と未使用のI/Oピンとの接続はデザイン・ファイルを変更することなく行うことができます。デザインのデバイスへのダウンロードには、JTAGインタフェースが使用されます。したがって、ここで使用されるのは未使用となっているピンと内部配線リソースのみです。図5を参照してください。

Page 6 Altera Corporation

#### 図 5 内部信号のI/Oピンへの配線

# Quartusと MasterBlaster によるサポート

SignalTapアナライザのすべてのセットアップ、コントロールおよび表示の 各機能は、Quartus開発ソフトウェアに組み込まれています。内部ノードの 信号はMasterBlaster通信ケーブルを通じてQuartusソフトウェアに転送さ れ、Quartusのウェーブフォーム・エディタのウィンドウ上に表示されま す。

MasterBlaster通信ケーブルは、アルテラのAPEX 20Kデバイスに信号を高速でダウンロードします。ホスト側のUSBインタフェースを通じたターゲット・デバイスへのダウンロードが、最高8Mbits/secまでのビット・ストリーム・レートでサポートされています。また、RS-232ポートを通じたダウンロードは、最高115,000bit/secのレートでサポートされています。デザイン・データのターゲット・デバイスへのダウンロードとアクイジション・バッファの構築/解消はJTAGインタフェースを通じて行われます。MasterBlaster通信ケーブルは、アルテラの全デバイスで使用されるI/O電圧をサポートしています。

詳細については、「MasterBlaster Serial/USB Communications Cable」のデータシート(日本語版有り)をご覧ください。

# SignalTap Plus のサポート

SignalTap Plusシステム・アナライザはデバイス外部のロジック解析機能も サポートしています。このシステム・アナライザでは、ボード・レベルでの 解析を行えるようにするため、デバイス外部の信号のキャプチャ用にさらに 32チャネルが追加されています。SignalTap Plusシステム・アナライザは、 Boulder Creek Engineering社から供給されています。詳細については、同 社のwebサイト、http://www.bcreek.comをご覧ください。

## まとめ

SignalTapエンベデッド・アナライザのメガファンクションを使用することによって、デバイス性能に影響を与えることなく、デバイス内部の信号を多様な方法でモニタすることができます。トリガ、システム・リソースの管理およびコンフィギュレーションは、 MasterBlaster通信ケーブルを通じてQuartusソフトウェアによってコントロールされます。データは、未使用のI/OピンまたはJTAGポートを通じて外部に接続することが可能です。解析されたデータは、デザインのデバッグやシステム性能の最適化に役立ちます。

Altera、APEX、APEX 20K、MasterBlaster、Quartus、SignalTap、SignalTap Plus、System-on-a-Programmable-ChipはAltera Corporationの米国 および該当各国におけるtrademarkまたはservice markです。この資料に記載されているその他の製品名などは該当各社のtrademarkです。Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001

Copyright © 1999 Altera Corporation. All rights reserved.

## 日本アルテラ株式会社

〒163-0436

東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487

http://www.altera.com/japan/ E-mail: japan@altera.com

### 本社 Altera Corporation

101 Innovation Drive, San Jose, CA 95134 TEL: (408) 544-7000 http://www.altera.com

この資料に記載された内容は予告なく変更されることがあります。最新の情報は、アルテラのwebサイト(http://www.altera.com)でご確認ください。この資料はアルテラが発行した英文のデータ・シートを日本語化したものであり、アルテラが保証する規格、仕様は英文オリジナルのものです。