# Using FLEX Devices as DSP Coprocessors

### TECHNICAL BRIEF 4

FEBRUARY 1996

Multiplier, accumulator, and adder functions can create a performance bottleneck in programmable DSP processors that are used for high-performance DSP applications. You can use Altera FLEX devices as DSP coprocessors to dramatically increase system performance in applications such as video convolution, RF-rate communication systems for cable networks, and direct-sequence spread-spectrum modems. FLEX DSP coprocessors perform computationally intensive, high-rate arithmetic functions, leaving the programmable DSP processor free to perform other functions.

## Example: FLEX DSP in Direct-Sequence Spread-Spectrum Data Communications

Direct-sequence spread-spectrum modems are used in cellular and cordless communication, as well as in wireless LANs. In spread-spectrum applications, the original signal is convolved with a pseudorandom number at the transmitter; then, at the receiver, a filter correlates the signal with the same random number.

For example, a wireless LAN manufacturer used a 16-bit, 40-MHz programmable DSP processor to perform these correlation and differential quadrature-amplitude data-demodulation functions. In this case, the overall system performance was only 10 MHz because the system used most of its bandwidth for correlation. This system sustained a 10-MHz system speed for a 15-bit pseudo-random number (PN) sequence, which corresponds to a data rate of less than 1 Megabit per second (Mbps).

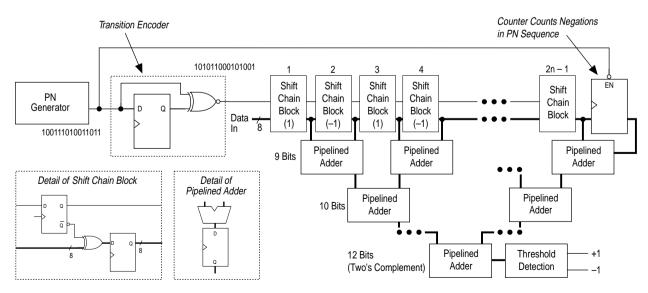

When a FLEX device was added to handle correlation while the programmable DSP processor was dedicated to data demodulation, the system performed at 60 MHz. A FLEX DSP device implemented the correlation function through a FIR filter with pipelined addition and subtraction, as shown in the figure below.

### Spread-Spectrum Receiver-Matched Filter Implemented in a FLEX Device

**Note**: Negations are handled by simple inversions through a shift chain. Two's complement representation is maintained by adding ones into the adder tree for each negation, according to the following relation: a + b - c - d = a + b + (!c + 1) + (!d + 1) = a + b + !c + !d + 2

Increasing the width of the PN sequence while implementing both the correlation and demodulation functions would have required much higher performance in the single programmable DSP processor. In contrast, when the same functions were implemented with a programmable DSP processor and a FLEX device, the PN width was increased by adding parallel resources in the FLEX device. Increasing this function to a 31-bit PN sequence required that the design use an EPF8636A device rather than an EPF8452A device; however, the system speed remained at 60 MHz without any changes to the programmable DSP processor. Thus, using the FLEX device dramatically increased the system performance.

Performance Comparison for Direct-Sequence Spread-Spectrum Communication System

| Devices Used                                  | Functions<br>Implemented         | Filter Size        | Performance | Size            |

|-----------------------------------------------|----------------------------------|--------------------|-------------|-----------------|

| Fixed-point programmable DSP processor        | Correlation & data demodulation  | 15-bit PN sequence | 10 MHz      | 1               |

| Altera EPF8452A device                        | Correlation<br>(15-bit sequence) | 15-bit PN sequence | 60 MHz      | 266 logic cells |

| & fixed-point programma-<br>ble DSP processor | Data demodulation                |                    |             |                 |

| Altera EPF8636A device                        | Correlation<br>(31-bit sequence) | 31-bit PN sequence | 60 MHz      | 553 logic cells |

| & fixed-point programma-<br>ble DSP processor | Data demodulation                |                    |             |                 |

# **DSP Design Kit**

FLEX devices provide higher performance than programmable DSP solutions without sacrificing flexibility. Altera offers a DSP Design Kit that includes customizable building blocks for implementing DSP functions. These building blocks include fully parallel 8-, 16-, 24-, 32-, and 64-tap FIR filters with user-customizable data coefficient widths, full serial filters for larger tap widths, and floating-point arithmetic functions. The DSP Design Kit optimizes these functions for Altera FLEX architectures so that designers can easily customize functions to fit specific design parameters.

The documents listed below provide more detailed information. Part numbers are in parentheses.

### **Product Information Bulletins**

### **Application Notes**

PIB 23 Digital Signal Processing in FLEX Devices (A-PIB-023-01)

AN 73 Implementing FIR Filters in FLEX Devices (A-AN-073-01)

You can request these documents from:

- Altera Express fax service at (800) 5-ALTERA

- World-Wide Web at http://www.altera.com

- Your local Altera sales representative