# **MAX 7000AE Performance Comparison**

Technical Brief 62 January 2000, ver. 1

https://websupport.altera.com

### Introduction

The Altera® MAX® 7000 device family is the industry's fastest and most preferred product-term solution. Now, with MAX 7000AE devices, performance is enhanced even more to help designers meet today's high-performance demands in a variety of systems.

To show the high performance of MAX 7000AE devices, Altera conducted a benchmark test that compared the MAX 7000AE device to the Xilinx XC9500XL device and the Lattice ispLSI2000VE device. This technical brief describes the results of the benchmark test.

## Performance Estimates Using Data Sheet Numbers

Performance estimates can help you determine the maximum device performance for most designs. You can easily calculate the performance of a device by using the internal timing parameters found in the device family data sheet.

Generally, device vendors use a maximum internal clock frequency,  $f_{CNT}$ , to measure performance. In most designs, this  $f_{CNT}$  represents the highest performance a device can achieve. To calculate  $f_{CNT}$ , four timing delay elements must be known: the register delay  $(t_{RD})$ , the programmable interconnect delay  $(t_{PIA})$ , the logic array delay  $(t_{LAD})$ , and the register setup time  $(t_{SU})$ . Figure 1 shows these timing delays and the equation used to calculate the  $f_{CNT}$ .

Figure 1. Timing Delays & f<sub>CNT</sub> Equation Note (1)

Internal

$$f_{CNT} = \frac{1}{t_{RD} + t_{PIA} + t_{LAD} + t_{SL}}$$

#### Note.

(1) To calculate the  $f_{CNT}$ , device vendors use the register-to-register feedback path of a standard 16-bit counter.

Table 1 shows the delay elements and  $f_{CNT}$  for the Altera EPM7128AE device, the Xilinx XC95144XL device, and the Lattice ispLSI2128VE device.

| Table 1. Delay Elements & f <sub>CNT</sub> Comparison Note (1), (2) |                  |                         |                          |                          |                         |                     |                                    |  |  |

|---------------------------------------------------------------------|------------------|-------------------------|--------------------------|--------------------------|-------------------------|---------------------|------------------------------------|--|--|

| Vendor                                                              | Device           | t <sub>RD</sub><br>(ns) | t <sub>PIA</sub><br>(ns) | t <sub>LAD</sub><br>(ns) | t <sub>SU</sub><br>(ns) | Total Delay<br>(ns) | Internal f <sub>CNT</sub><br>(MHz) |  |  |

| Altera                                                              | EPM7128AE-5      | 0.8                     | 1.4                      | 1.6                      | 1.4                     | 5.2                 | 192                                |  |  |

| Xilinx                                                              | XC95144XL-5      | 0.4                     | 1.9                      | 1.0                      | 2.3                     | 5.6                 | 179                                |  |  |

| Lattice                                                             | ispLSI2128VE-180 | 0.3                     | 0.6                      | 3.4                      | 1.2                     | 5.5                 | 182                                |  |  |

#### Notes:

- (1) The delay element names differ for each device. The timing delays  $t_{RD}$ ,  $t_{PLA}$ ,  $t_{LAD}$ , and  $t_{SU}$  are names used by Altera. Equivalent delay names for each device are as follows: Xilinx XC95144XL-5:  $t_{CO1}$ ,  $t_F$ ,  $t_{LOGI}$ ,  $t_{SU}$ , and Lattice ispLSI2128VE-180:  $t_{GCO}$ ,  $t_{GRP}$ ,  $t_{IPTXOR}$ , and  $t_{GSU}$ .

- (2) All values were taken directly from each device's respective data sheet.

Table 1 shows that the Altera EPM7128AE device has the highest  $f_{CNT}$  at 192 MHz. This data sheet result suggests that the EPM7128AE device provides the highest performance for most designs.

## **Benchmark Experiment**

Although device data sheets provide a good source of information about the general performance of a device, benchmark tests that implement real customer designs remain the most reliable measurement of performance. Customer designs are normally complex in nature, exercising both the logic resources of a device and the compilation software. The data sheet  $f_{CNT}$  calculation result does not adequately represent the complexity of customer designs.

In a recent benchmark study of 23 customer VHDL designs, Altera Applications compared the performance of the Altera EPM7128AE device to the Xilinx XC95144XL device and the Lattice ispLSI2128VE device. All designs were compiled in the fastest speed grade for each device. Table 2 provides a brief description of the resources used in each design.

| Design | Average Macrocells Used | I/O Pins Used |

|--------|-------------------------|---------------|

| 1      | 115                     | 72            |

| 2      | 126                     | 61            |

| 3      | 108                     | 72            |

| 4      | 128                     | 49            |

| 5      | 128                     | 70            |

| 6      | 114                     | 49            |

| 7      | 115                     | 66            |

| 8      | 118                     | 73            |

| 9      | 128                     | 35            |

| 10     | 126                     | 73            |

| 11     | 114                     | 80            |

| 12     | 120                     | 59            |

| 13     | 90                      | 73            |

| 14     | 110                     | 66            |

| 15     | 91                      | 78            |

| 16     | 70                      | 51            |

| Table 2. Customer VHDL Designs Used in Benchmark Test (Part 2 of 2) |                         |               |  |  |  |  |

|---------------------------------------------------------------------|-------------------------|---------------|--|--|--|--|

| Design                                                              | Average Macrocells Used | I/O Pins Used |  |  |  |  |

| 17                                                                  | 106                     | 75            |  |  |  |  |

| 18                                                                  | 96                      | 94            |  |  |  |  |

| 19                                                                  | 93                      | 55            |  |  |  |  |

| 20                                                                  | 126                     | 62            |  |  |  |  |

| 21                                                                  | 121                     | 78            |  |  |  |  |

| 22                                                                  | 105                     | 81            |  |  |  |  |

| 23                                                                  | 108                     | 39            |  |  |  |  |

Table 3 shows the synthesis and place-and-route tools used for the test.

| Table 3. Tools Used in the Benchmark Test Note (1), (2) |                                         |                                 |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------|---------------------------------|--|--|--|--|

| Device                                                  | Synthesis                               | Place & Route                   |  |  |  |  |

| EPM7128AE-5                                             | Synopsys FPGA Compiler II version 3.2.0 | Altera MAX+PLUS II version 9.4  |  |  |  |  |

| XC95144XL-5                                             | Synopsys FPGA Compiler II version 3.2.0 | Xilinx WebPack version 2.1WP2.x |  |  |  |  |

| ispLSI2128VE-180                                        | Synopsys FPGA Compiler II version 3.2.0 | Lattice ispEXPERT version 7.1   |  |  |  |  |

#### Notes:

- (1) All designs were compiled using the fastest synthesis settings.

- (2) If a design did not fit, optimization settings were applied.

## EPM7128AE & XC95144XL Device Results

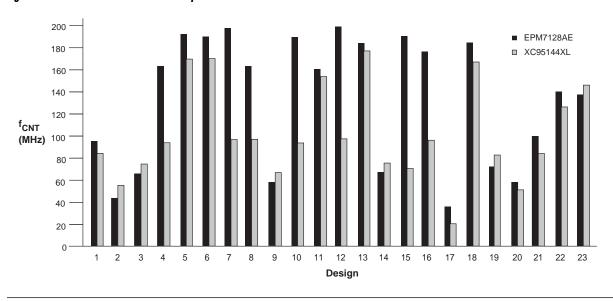

Figure 2 shows the performance comparison between the Altera EPM7128AE device and the Xilinx XC95144XL device. Both devices successfully fit all 23 customer designs; however, the EPM7128AE device outperformed the XC95144XL device in 17 customer designs. Overall, the EPM7128AE device performed 30% faster than the XC95144XL device.

Figure 2. EPM7128AE & XC95144XL Comparison

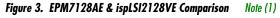

## EPM7128AE & ispLSI2128VE Device Results

Figure 3 compares the performance of the Altera EPM7128AE device and the Lattice ispLSI2128VE device. The ispLSI2128VE device successfully fit only 16 of the 23 customer designs. The EPM7128AE device outperformed the ispLSI2128VE device in 14 of those 16 designs. Overall, the EPM7128AE device performed approximately 40% faster than the ispLSI2128VE device.

#### Note:

(1) If a gray bar is missing from the graph, the Lattice ispLSI2128VE device failed to fit that design.

## The Industry's Fastest Product-Term Solution

MAX 7000AE devices continue to lead the industry with the fastest product-term solution. When comparing performance estimates of the Altera EPM7128AE device to the Xilinx XC95144XL device and the Lattice ispLSI2128VE device, the EPM7128AE device has the highest internal  $f_{CNT}$ . This result indicates that the EPM7128AE device provides the highest performance for most designs.

For a thorough performance comparison between the devices, Altera Applications conducted a benchmark study of 23 customer designs. The results of the benchmark test showed that the Altera EPM7128AE device performed, on average, 30% faster than the Xilinx XC95144XL device and 40% faster than the Lattice ispLSI2128VE device. The EPM7128AE device clearly outperforms its competition by providing the highest performance solution to today's complex designs.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Copyright © 2000 Altera Corporation. Altera, MAX+PLUS, MAX+PLUS II, EPM7128AE, MAX, MAX 7000, MAX 7000A, and MAX 7000AE are trademarks and/or service marks of Altera Corporation in the United States and other countries. Other brands or products are trademarks of their respective holders. The specifications contained herein are subject to change without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.