# System-on-a-Programmable-Chip Development Board

July 2000, ver. 1.1 User Guide

# **Features**

- Powerful development board for system-on-a-programmable-chip (SOPC) designs

- Features an APEX<sup>TM</sup> EP20K400E 652-pin device

- Supports microprocessor intellectual property (IP)-based design

- Industry-standard interconnects

- 10/100 Ethernet with full and half duplexing

- Peripheral component interconnect (PCI) mezzanine connector

- High- and low-speed universal serial bus (USB) host supporting the *Universal Serial Bus Specification*, Revision 1.0

- IEEE Std. 1394a at 100, 200, and 400 megabits per second (Mbps)

- IEEE Std. 1284 parallel interface

- Two RS-232 ports (DCE and DTE)

- Two PS/2 ports for mouse and keyboard

- Memory subsystem

- Two banks of 1-Mbyte cache memory

- 64-Mbyte SDRAM in a DIMM socket

- 4-Mbyte Flash memory

- 256-Kbyte EPROM

- Multiple clocks for communications systems design

- Multiple debugging ports

- SignalTap™ embedded logic analyzer

- IEEE Std. 1149.1 Joint Test Action Group (JTAG)

- Extended JTAG (EJTAG)

- Supports 50 user I/O lines

- Additional features

- VGA monitor interface

- Four user-defined switches and six LEDs

- Liquid crystal display

- Application LEDs

- Applications

- Embedded systems prototyping

- Communications systems design

- IP development and debugging

# Introduction

This user guide provides information on the development board and includes the following topics:

| General Description                     |    |

|-----------------------------------------|----|

| APEX Device                             | 5  |

| Power                                   | 6  |

| Environmental Requirements              | 7  |

| Clocks                                  | 8  |

| Memory                                  | 8  |

| Interfaces                              | 8  |

| General Information                     | 9  |

| Initial Setup                           | 10 |

| Functional Overview                     | 13 |

| APEX Device                             | 13 |

| Memory Interfaces                       | 15 |

| Design Considerations                   | 21 |

| Clock Generation & Distribution         | 21 |

| Configuration Interface                 | 22 |

| Configuration Interfaces                | 22 |

| Serial I/O Interface                    |    |

| Mezzanine Interfaces                    | 29 |

| Display & Switch Interfaces             | 32 |

| Test & Debug Features                   | 35 |

| Jumper Configuration                    |    |

| Clock Distribution                      | 38 |

| JTAG Configuration                      | 41 |

| IEEE 1284 Parallel Interface            |    |

| Interface Specifications                | 43 |

| Analog I/O Interface                    |    |

| Power Conditioning Interface            | 51 |

| EJTAG Interface                         | 52 |

| Configuration Interface                 |    |

| Memory Interface                        | 54 |

| APEX Pin Assignments                    | 56 |

| Configuration                           |    |

| General-Purpose Memory Interface        |    |

| PMC Interface                           |    |

| Connector Pin Assignments               |    |

| JTAG/MasterBlaster Configuration Header | 78 |

| EJTAG Connector                         |    |

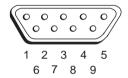

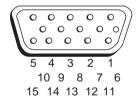

| RS-232 DTE Connector                    |    |

| RS-232 DCE Connector                    |    |

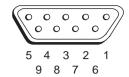

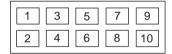

| PS/2 Connectors                         |    |

| USB Connector                           |    |

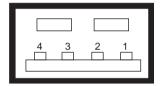

| IEEE-1394 (FireWire) Connector          |    |

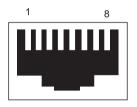

| Ethernet Connector                      |    |

| Parallel Port Connector                 |    |

| VGA Connector                           | 83 |

# System-on-a-Programmable-Chip Development Board User Guide

| Test Connectors          | 84 |

|--------------------------|----|

| General Usage Guidelines | 88 |

| SDRAM Data Bus           | 88 |

| Parallel Port Jumpers    | 88 |

| Unused APEX Device Pins  | 89 |

| Power Consumption        | 89 |

| Testing Software         | 89 |

| Test Core Functionality  | 89 |

| Mix Test 1 Core          | 90 |

| Mix_Test_2 Core          | 91 |

| Mix_Test_3 Core          | 92 |

| Mix_Test_4 Core          | 94 |

| Mix_Test_5 Core          | 95 |

| SDRAM_top                |    |

| LCD top                  | 96 |

# General Description

The Altera® system-on-a-programmable-chip board is a development and prototyping platform that provides system designers with an economical solution for hardware verification. The system-on-a-programmable chip board supports a variety of microprocessor-based designs, incorporating memory, debugging, and interface resources.

The development board is primarily designed for implementing microprocessor functions and other standard IP functions in the on-board APEX device. The board includes physical interfaces for widely used standard interconnects. Control logic for the interconnects can be implemented in the device. Some of the available IP solutions include:

- Processor cores (MIPS, RISC, and Harvard)

- Peripheral and I/O cores (PCI, SDRAM controllers, UART, USB, ethernet, IEEE1394, IEEE 1284)

- Other cores developed by Altera and Altera Megafunction Partners Program (AMPP<sup>TM</sup>) partners

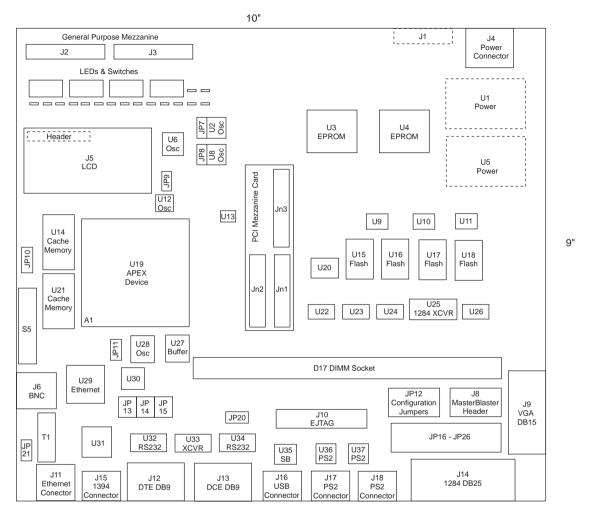

The board also supports EJTAG for development and debugging of MIPS-like microprocessor functions, as well as JTAG for system testing. For additional analysis, the JTAG port can be used with the SignalTap embedded logic analyzer available with the Quartus<sup>TM</sup> development software. Figure 1 shows a layout diagram of the development board.

Figure 1. System-on-a-Programmable-Chip Board Layout Diagram

# **APEX Device**

The EP20K400E device features 423,000 ASIC-equivalent gates in a 652-pin FineLine BGA<sup>TM</sup> package. The device has 16,640 logic cells and 212,992 RAM bits.

# **Power**

The eight-layer development board has four signal layers: a full 3.3-V power plane, and a split 2.5-V, 5.0-V power plane. The APEX device's core power is driven at 2.5 V, and the IEEE Std. 1394 physical layer is driven at 3.3 V. An external 5.0-V power supply provides power to the board and regulates the 3.3-V and 2.5-V supplies.

Tables 1 through 3 list the estimated power requirements for the development board.

| Table 1. 12.0-V Supply Requirements      |     |           |             |

|------------------------------------------|-----|-----------|-------------|

| Module mA (12.0 V) mA (-12.0 V) Power (W |     | Power (W) |             |

| PMC                                      | 100 | 100       | 2.5 Maximum |

| General Purpose Mezzanine                | 100 | 100       | 2.5 Maximum |

| Table 2. 5.0-V Supply Requirements |            |             |             |

|------------------------------------|------------|-------------|-------------|

| Module                             | mA (5.0 V) | mA (-5.0 V) | Power (W)   |

| PMC                                | 1,000      | _           | 5.0 Maximum |

| General Purpose Mezzanine          | 1,000      | _           | 5.0 Maximum |

| P/S2 Keyboard                      | 50         | _           | 0.25        |

| P/S2 Mouse                         | 50         | _           | 0.25        |

| DTE UART                           | 50         | _           | 0.25        |

| DCE UART                           | 50         | _           | 0.25        |

| USB                                | 100        | _           | 0.5         |

| Ethernet                           | _          | _           | _           |

| Parallel                           | 70         | _           | 0.4         |

| VGA                                | _          | _           | _           |

| Configuration                      | 20         | _           | 1.0         |

| LCD                                | 20         | 20          | 0.2         |

| Two red LEDs                       | 10         | _           | 0.1         |

| Two yellow LEDs                    | 10         | _           | 0.1         |

| Two green LEDs                     | 10         | _           | 0.1         |

| Table 3. 3.3-V Supply Requirements |            |             |

|------------------------------------|------------|-------------|

| Module                             | mA (3.3 V) | Power (W)   |

| APEX DC current for VCCIO          | 1,500      | 5.0         |

| PMC                                | 1,500      | 5.0 Maximum |

| General Purpose Mezzanine          | 1,500      | 5.0 Maximum |

| SSRAM A                            | 600        | 2.0         |

| SSRAM B                            | 600        | 2.0         |

| SDRAM                              | 600        | 2.0         |

| Flash                              | 300        | 1.0         |

| EPROM                              | 300        | 1.0         |

| FireWire (1394)                    | 115        | 0.4         |

| Ethernet                           | 150        | 0.5         |

| Configuration                      | 0          | 0           |

| Table 4. 2.5-V Supply      |            |           |

|----------------------------|------------|-----------|

| Module                     | mA (1.8 V) | Power (W) |

| APEX DC current for VCCINT | 6,000      | 15        |

The total power requirement for the development board is about 60 W. The 5.0-V, 12.0-V, and -12.0-V supplies are provided externally, while the 1.8-V and 3.3-V supplies are derived from the board. Only the 5.0-V supply needs to be provided unless you are using mezzanines that require a 12.0-V or -12.0-V supply.

The board includes reverse voltage and status LEDs. Connectors are also included to support both laboratory bench supplies and commercially available PC-style power supplies.

# **Environmental Requirements**

The development board must be stored between 40 °C and 100 °C. Operational temperatures must fall between 0 °C and 55 °C. The development board also requires commercial grade components and must be convection cooled.

## Clocks

The board supports up to six unique clocks that can be selected by the designer for a total of ten. The board has two BNC connectors to support communications systems design. The APEX global clock input is driven by a 66-MHz oscillator or by an external clock via a BNC connector. The second global clock signal is connected to an oscillator that can drive a PCI function at either 33 or 66 MHz.

# Memory

To support processor functions implemented in the APEX device, the board includes a memory system consisting of the following:

- Volatile memory: 64 Mbytes of synchronous DRAM, organized as 8 Mbytes × 64 Mbytes

- Non-volatile memory: 4 Mbytes Flash memory and a 256-Kbyte EPROM memory

- Pipelined cache memory with burst SRAM organized as 256 Kbytes × 32 Kbytes

## Interfaces

Table 5 describes the interfaces supported by the board.

| Table 5. Development                          | Board Interfaces                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface                                     | Description                                                                                                                                                                                                                                                                                                 |

| PCI PMC IEEE Std.<br>1386 connector           | This mezzanine connector supports 32 and 64 bits and operates at 33 and 66 MHz. It is compliant with the <i>PCI Local Bus Specification, Revision 2.1</i> . The connector can be used by designers to build an interface to PCI functions in the APEX device.                                               |

| 10/100 ethernet with full- and half-duplexing | The 10/100 ethernet interface consists of a transceiver and associated discrete devices and allows implementation of an ethernet media access controller (MAC) in the APEX device.                                                                                                                          |

| IEEE Std. 1394a interface                     | The IEEE Std. 1394a FireWire interface consists of a transceiver/arbiter and associated discrete devices. The physical interface provides an IEEE Std. 1394a-compliant cable port at 100, 200, and 400 Mbits per second for a link layer controller (LLC) implemented as a function inside the APEX device. |

| USB host interface                            | The USB host interface consists of a single host connection with a type A socket. The interface supports both low-speed and high-speed operation without changing the configuration.                                                                                                                        |

| User I/O pins                                 | The general-purpose mezzanine interface provides 50 user I/O pins that connect directly to the APEX device, supporting custom interfaces.                                                                                                                                                                   |

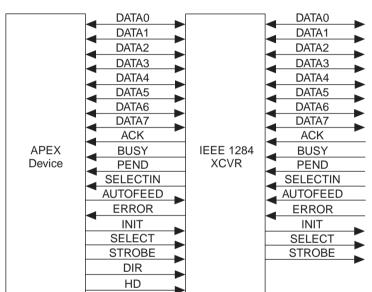

| IEEE Std. 1284 parallel interface             | The parallel interface is a IEEE Std. 1284-compatible transceiver. The transceiver has eight bidirectional data buffers and can be used in extended capabilities port (ECP) mode. The designer can implement the IEEE Std. 1284 control logic in the APEX device.                                           |

| Debugging ports                               | The board supports in-circuit debugging with the SignalTap embedded logic analyzer, which can be configured in the APEX device and the MasterBlaster <sup>TM</sup> communications cable. The board also has a 50-pin EJTAG header for debugging MIPS-like processors implemented in the APEX device.        |

# General Information

Once power is applied to the board, the LCD display reads "SOPC DEMO BOARD." This message indicates that the EP20K400E device has successfully configured itself and is functional. The development board status program is contained within the EPC2 Flash PROM devices provided on the development board.

Before handling the card, you should take proper anti-static precautions. The board can be easily damaged without proper anti-static handling.

# **Initial Setup**

To begin using the board, a complete initial setup must be performed by following these steps:

- 1. Complete the assembly and inspect the board.

- 2. Apply power.

- 3. Program the APEX device.

- 4. Reset the board.

# Inspecting the Board

Place the board on an anti-static surface and inspect the board to ensure that it has not been damaged during shipping. Make sure that all components are on the board and appear intact. To complete the board assembly, insert the SDRAM module (shipped separately) into the DIMM slot.

## Applying Power

You can apply power to the board using either the eight-pin power supply connector (J22) or the terminal block (J1) with a bench power supply. If you choose to power the board using the terminal block, you must provide a 5.0-V supply and a ground connection. All of the board components are powered directly from the 5.0-V supply. The 12.0-V and –12.0-V inputs are used to provide the required voltages to the PMC mezzanine as required by the specification.

If you apply power through the terminal block (J1), use a power supply, which is capable of providing 5.0 A to the 5.0-V input. This value meets the typical maximum requirements for the board. To ensure that adequate power is provided, monitor the input current and voltage using the power supply or a digital multimeter.

If you apply power through the 8-pin power supply connector (J4), then you must purchase the power cord. You can directly connect the Total Power International Inc. HES100-30 power supply to the board at J4. The supply is capable of providing the maximum required power.

Depending on testing conditions, the maximum power required by the board is 100 W. This condition occurs if both mezzanine interfaces are used at the same time, in addition to the devices on the board.

## Programming the APEX Device

The APEX 20K device is programmed via the JTAG interface. During initial power up, the APEX 20K device receives configuration data from the EPC2 configuration devices if the configuration devices contain data. If the configuration devices are not programmed, the APEX device will remain unconfigured.

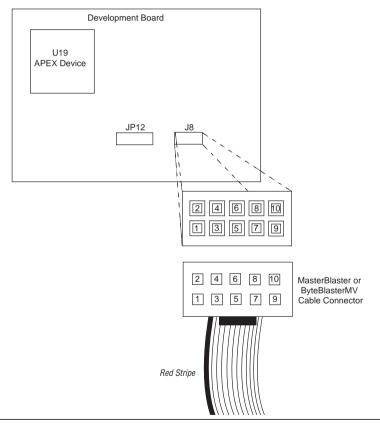

You can program the APEX device directly using the Quartus software version 2000.02 and higher or the MAX+PLUS® II software version 9.5 and higher using either the MasterBlaster or ByteBlasterMV cable. Figure 2 shows how to connect the MasterBlaster or ByteBlasterMV cable to the development board.

Figure 2. Connecting the MasterBlaster & ByteBlasterMV Cables

The development board may be damaged if the MasterBlaster or ByteBlasterMV cables are not plugged in correctly.

Refer to Quartus Help for instructions on how to configure devices using the MasterBlaster cable.

The green LED D2 will illuminate after the APEX 20K device is successfully configured indicating that the configuration is complete. At this point, press the Reset switch. If an error occurred during configuration, the red LED D1 will illuminate, indicating that the APEX 20K device was not successfully configured. The APEX 20K device must be reprogrammed each time the board is powered down, but retains its programming information if the board is reset.

The EPC2 configuration device may also be programmed using the MAX+PLUS II software and a MasterBlaster, ByteBlasterMV, or BitBlaster™ download cable. EPC2 configuration devices are accessible using the JTAG interface. The APEX 20K device only attempts to load configuration data from an EPC2 device on initial power up. If configuration data is changed while the board is turned on, new data is not loaded into the APEX 20K device until the board is turned off and on.

EPC2 configuration devices contain a small program that configures the LCD display to read "SOPC DEMO BOARD" on power up.

## Resetting the Board

A master reset switch (S1) resets the APEX 20K device through the DEV\_CLRn input signal. This is not a board-level reset. Any devices that need to be reset are driven from the APEX device, and the signals must be connected to the reset switch internally. This allows devices on the board to be reset independently from the global reset without requiring additional hardware to prevent contention.

A second switch (S2) is connected to a dedicated low-skew input pin (B17) and is provided as an alternative reset option if the DEV\_CLRn input signal is not used. This may be configured internally in the APEX device.

# Functional Overview

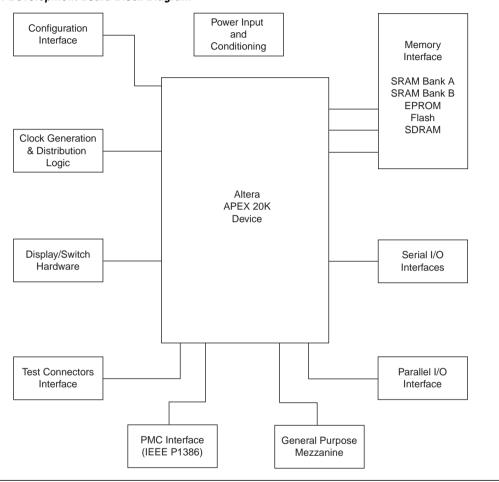

This section provides a brief overview of the development board components. Figure 3 shows a functional block diagram of the development board.

Figure 3. Development Board Block Diagram

## **APEX Device**

The main component of the development board is the EP20K400EBC652-1 device. The APEX device's package is a 652-pin FineLine BGA package. Table 6 lists the features of the APEX device and Figure 4 is a block diagram of the APEX device interface.

| Table 6. APEX 20K400E Device Features                |                    |  |

|------------------------------------------------------|--------------------|--|

| Feature                                              | Specification      |  |

| Maximum gates (logic and RAM)                        | 1,052,000          |  |

| Typical gates                                        | 213,000 to 423,000 |  |

| Logic elements (LEs)                                 | 16,640             |  |

| Embedded system blocks (ESBs)                        | 104                |  |

| Maximum RAM bits                                     | 212,992            |  |

| Maximum macrocells                                   | 1,664              |  |

| Maximum user I/O pins                                | 502                |  |

| Internal supply voltage                              | 2.5 V              |  |

| MultiVolt <sup>TM</sup> I/O interface voltage levels | 3.3, 2.5 V         |  |

| Dedicated power inputs                               | 150                |  |

| Package                                              | 652 BGA            |  |

| I/O count                                            | 496                |  |

| Dedicated clock inputs                               | 6                  |  |

For more information about the EP20K400E or other APEX devices, see the *APEX 20K Programmable Logic Device Family Data Sheet*.

Figure 4. APEX Device Block Diagram

# **Memory Interfaces**

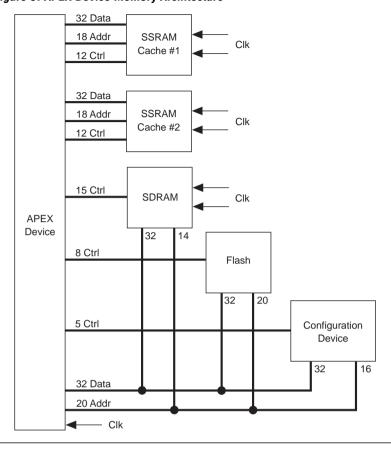

Three memory buses interface with the APEX 20K device. These interfaces include a general-purpose memory bus, a Flash memory bus, and an EPROM memory bus. Two synchronous SRAM (SSRAM) memory buses are also connected to the APEX device. The buses provide the development board with four types of memory.

Two SSRAM banks provide cache memory for a processor core, and are accessed using dedicated buses to optimize performance. The SDRAM and non-volatile memory share common general-purpose data and address buses while maintaining separate control signals. Figure 5 illustrates the architecture of the development board memory system.

Figure 5. APEX Device Memory Architecture

Table 7 lists the memory characteristics for the development board.

| Table 7. Development Board Memory Characteristics |                  |               |                  |                        |           |           |              |

|---------------------------------------------------|------------------|---------------|------------------|------------------------|-----------|-----------|--------------|

| Туре                                              | Address<br>Lines | Data<br>Lines | Control<br>Lines | Memory<br>Organization | Size      | I/Os Used | Power Budget |

| SSRAM A                                           | 18               | 32            | 14               | 256 × 32               | 1 Mbyte   | 64        | 2.0 W        |

| SSRAM B                                           | 18               | 32            | 14               | 256 × 32               | 1 Mbyte   | 64        | 2.0 W        |

| SDRAM                                             | 20               | 32            | 16               | 8Mb × 32               | 64 Mbytes | 79        | 2.0 W        |

| Flash                                             | 20               | 32            | 8                | 64k × 32               | 4 Mbytes  | 79        | 1.0 W        |

| EPROM                                             | 20               | 32            | 3                | 64k × 32               | 256K      | 79        | 1.0 W        |

## SDRAM Memory

The SDRAM memory configuration is compliant with the *PC SDRAM Unbuffered DIMM Specification, Revision 1.0*. The development board supports configuration types 8 and 9 from this specification. Refer to Table 62 on page 59 for a list of SDRAM control lines.

The address and data lines are shared by all devices connected to the general-purpose memory bus. The SDRAM module does not use all of the address lines, because memory is accessed through both a row and a column address.

SDRAM memory is connected to the general-purpose address bus, as defined in the *PC SDRAM Unbuffered DIMM Specification Revision 1.0* for 8Mbyte  $\times$  64 modules. Module address bits 0 to 11 are connected to the corresponding bits of the general-purpose address bus. Module address bit 12 is unused. Module bank address bits 0 and 1 are connected to general-purpose address bits 13 and 12, respectively.

The SDRAM module is 64 bits wide, while the general-purpose memory data bus is 32 bits wide. To accommodate this, the data bus is doubly loaded. Bit 0 of the general-purpose data bus is connected to both bit 0 and bit 32 of the module data bus, and so on.

Improper handling of the data byte mask bits during SDRAM reads can cause contention on the data bus.

The SDRAM byte-enable lines control the data bus. DQM[3..0] accesses the lower 32 bits, and DQM[7..4] accesses the upper 32 bits. Ensure that two byte lanes sharing common bits are not active at the same time. For example, if DQM[0] is enabled, DQM[4] must not be enabled. Refer to Table 60 on page 57 and Table 61 on page 58 for a list of general-purpose data and address lines.

SDRAM is clocked from the same clock source as the APEX device's processor clock for the APEX device to ensure that the interface remains synchronous. This can be either the 66-MHz clock crystal, the variable crystal, or the external input. The SDRAM interface has been tested up to 66 MHz. Table 8 shows the SDRAM module control signals.

| Table 8. SDRAM Module Control Signals |     |                       |  |

|---------------------------------------|-----|-----------------------|--|

| Signal                                | 1/0 | Description           |  |

| RAS#                                  | 1   | Row address strobe    |  |

| CAS#                                  | 1   | Column address strobe |  |

| WE#                                   | 1   | Write enable          |  |

| CS[01]#                               | 2   | Module chip selects   |  |

| DQM[07]                               | 8   | Data byte mask        |  |

| CKE                                   | 1   | Clock enable          |  |

| SDA                                   | 1   | Serial data           |  |

| SCL                                   | 1   | Serial clock          |  |

## Flash Memory

A 1Mbyte  $\times$  32 Flash memory bank is connected to the general-purpose memory bus and provides four Mbytes of memory. The bank is implemented using four 1Mbyte  $\times$  8 Flash devices. Write protection can be provided by connecting WP# to a jumper block instead of, or in addition to connecting it to the APEX device. Refer to the APEX device data sheet for detailed information on how to access this device. Table 64 on page 60 provides a list of the Flash control lines.

Because of the significant loading on shared address buses, the Flash and EPROM memory devices are separated from the other address bus by transceivers. These devices are always enabled so additional control is not required; however, the propagation delay through the transceiver should be taken into account for timing analysis. Table 9 provides information on the devices used to implement the Flash memory.

| Table 9. Flash Memory Interface Device Reference |                  |                      |                             |  |

|--------------------------------------------------|------------------|----------------------|-----------------------------|--|

| Reference<br>Designator                          | Part Number      | Manufacturer         | Description                 |  |

| U15, U16, U17,<br>U18                            | MT28F800B3WG-10T | Micron               | 1Mbyte × 32 Flash<br>Memory |  |

| U23, U22, U20                                    | SN74LV245BDW     | Texas<br>Instruments | Bus Transceiver             |  |

The 1Mbyte  $\times$  32 Flash memory is implemented using four 1Mbyte  $\times$  8 devices. Table 10 lists the Flash memory control signals.

| Table 10. Flash Control Signals |     |                   |

|---------------------------------|-----|-------------------|

| Signal                          | 1/0 | Description       |

| CS#                             | 1   | Chip select       |

| OE#                             | 1   | Output enable     |

| RP#                             | 1   | Reset pulse       |

| WP#                             | 1   | Write protect     |

| WE[03]#                         | 4   | Byte write enable |

## EPROM Memory

The 64Kbyte  $\times$  32 EPROM memory is implemented using two EPROM devices, each organized as 64Kbyte  $\times$  16. The bus transceivers used to isolate the EPROM and Flash devices must be considered for the timing of the EPROM interface. Refer to Table 63 on page 59 for a list of the EPROM control lines. Table 11 lists information on the devices used to implement the EPROM memory. The EPROM memory devices are installed in 44-pin PLCC sockets to allow for easy replacement. The EPROM devices are not configured upon delivery. Table 12 lists the EPROM control signals.

| Table 11. EPROM Memory Interface Device Reference |             |                            |                          |

|---------------------------------------------------|-------------|----------------------------|--------------------------|

| Reference<br>Designator                           | Part Number | Manufacturer               | Description              |

| U3, U4                                            | NM27LV21OV  | Fairchild<br>Semiconductor | 64K × 32 EPROM<br>Memory |

| Table 12. EPROM Control Signals |     |               |  |

|---------------------------------|-----|---------------|--|

| Signal                          | I/O | Description   |  |

| CS                              | 2   | Chip select   |  |

| OE                              | 1   | Output enable |  |

## High-Speed Memory Interface

The board contains two synchronous 256Kbyte  $\times$  32 SRAM memory banks. Each bank is implemented with one SSRAM device and is separately connected to the APEX device. Both memory devices are synchronous with the processor clock used for the APEX device, and are intended to be used as cache memory for a processor core inside the APEX device.

Tables 65 through 67 on pages 60 and 61 contain information on the address, data, and control lines for SSRAM Bank 1. Tables 68 through 70 list information on the address, data, and control lines for SSRAM Bank 2.

All possible control lines have been connected to the APEX device to allow maximum flexibility of the memory interface. Some control lines may not be required for a particular design and these signals may be left tri-stated, because all control lines are pulled inactive on the board. The parity option for the SSRAM was not connected. Table 13 provides information on the devices used to implement the two SSRAM memory banks. Table 14 lists the SSRAM module control signals.

| Table 13. SSRAM Memory Interface Device Reference         |                  |        |                              |

|-----------------------------------------------------------|------------------|--------|------------------------------|

| Reference Part Number Manufacturer Description Designator |                  |        | Description                  |

| U21                                                       | MT8L256L32DT-10  | Micron | 256Kbyte × 32<br>SRAM Bank 1 |

| U14                                                       | MT58L256L32DT-10 | Micron | 256Kbyte × 32<br>SRAM Bank 2 |

| Table 14. SSRAM Module Control Signals |     |                           |  |

|----------------------------------------|-----|---------------------------|--|

| Signal                                 | 1/0 | Description               |  |

| ADV                                    | 1   | Address advance           |  |

| ADSC                                   | 1   | Address status processor  |  |

| ADSP                                   | 1   | Address status controller |  |

| CE#                                    | 1   | Chip enable               |  |

| CE2                                    | 1   | Chip enable               |  |

| OE#                                    | 1   | Output enable             |  |

| GW#                                    | 1   | Global write              |  |

| BW[03]                                 | 4   | Byte write enable         |  |

| BWE#                                   | 1   | Byte write enable         |  |

| Mode                                   | 1   | Burst mode sequence       |  |

| ZZ                                     | 1   | Power down enable         |  |

# **Design Considerations**

Designs can be improved by following a few basic guidelines. To do this, perform a timing analysis, especially when specifying setup and hold constraints for SSRAM and SDRAM. High-fanout signals on the general-purpose memory buses may require buffering and is especially true of the address signals. It is likely that each synchronous memory bank will require two clock cycles at the core clock frequency. This yields a total of seven loads, including the APEX device. If all types of memory are not available with 3.3-V supply voltages, level translation buffers may be required.

## **Clock Generation & Distribution**

The APEX device uses four global clock inputs and one low-skew dedicated input which (used as a clock input) brings the total clock input count to five. Refer to the *Jumper Configuration* section for detailed information on configuring the clock options on the development board.

The EP20K400E device has four internal phase-locked loop (PLL) circuits, which are available for use on the development board. A jumper enables the APEX PLL circuitry. For a diagram of the jumper configuration, see Figure 8 on page 40. Table 15 shows the required development board clocks.

| Table 15. Required Development Board Clocks |                 |  |  |

|---------------------------------------------|-----------------|--|--|

| Interface                                   | Required Clocks |  |  |

| Core processor and synchronous memory       | 66 MHz External |  |  |

| 1394                                        | 24.576 MHz      |  |  |

| USB                                         | 48 MHz          |  |  |

| Ethernet (receive clock)                    | 25 MHz          |  |  |

| Ethernet (transmit clock)                   | 25 MHz          |  |  |

| PCI mezzanine                               | 33/66 MHz       |  |  |

| General-purpose mezzanine                   | External        |  |  |

| VGA                                         | 25.175 MHz      |  |  |

| EJTAG                                       | External        |  |  |

APEX 20KE devices provide four dedicated clock pins and four additional dedicated input pins available for broad, low-skew routing. Because three of the dedicated inputs are required for other interfaces, five inputs may be used for clocks. Some of these pins must be shared to support all 11 required clock signals.

# **Configuration Interface**

The APEX device may be configured using the Quartus software and the MasterBlaster download cable. Alternatively, the three EPC2 configuration devices configure the APEX device upon power-up. Table 59 on page 56 provides a list of configuration signals.

Each time power is applied to the board, the APEX device checks for configuration information stored in the EPC2 configuration devices and loads any available information. If you change the configuration device's programming information, you must turn the board off and on before new information can be loaded into the APEX device.

The EPC2 devices may be programmed through the JTAG interface. Refer to the *Jumper Configuration* section for detailed information on configuring the JTAG interface. The EPC2 device can be programmed with the Quartus software version 2000.02 or later and the MAX+PLUS II software version 9.5 or later and the using either the MasterBlaster or ByteBlasterMV communication cables.

If configuration data is targeted at the EPC2 devices, start the Quartus and MAX+PLUS II software and the EPC2 device as an output option to create the required Programmer Object Files (.pof) files. If the EPC2 devices are not targeted, the Quartus software will generate a single file required to program the APEX device directly.

# **Configuration Interfaces**

Table 16 shows the data sources for configuration that are available for the APEX device.

| Table 16. Supported Configuration Schemes |                              |  |

|-------------------------------------------|------------------------------|--|

| Configuration Scheme Data Source          |                              |  |

| Configuration devices                     | EPC2 configuration device    |  |

| JTAG                                      | MasterBlaster download cable |  |

## EPC2 Device Configuration

The EPC2 device section consists of three EPC2 devices with reprogrammable Flash memory. The devices are also a part of the onboard JTAG chain to allow in-system programming.

#### MasterBlaster Communications Cable

The MasterBlaster communications cable has a 10-pin header for use with the development board. The communications cable allows you to directly download configuration data to the APEX device. The development board supports only JTAG download mode, not passive serial download mode. The MasterBlaster cable also supports in-circuit debugging with the SignalTap embedded logic analyzer.

Two LEDs are provided on the communications cable: a green LED for use with the CONF\_DONE signal and a red LED for use with the nSTATUS signal.

The board header supply voltage is 5.0 V and supplies a maximum of 1 W.

## Serial I/O Interface

The development board contains several serial I/O interfaces. For each serial interface, the transceiver and any associated hardware are provided on the board. The logic controllers must be implemented inside the APEX device. The interfaces on the board include:

- RS-232C data terminal equipment (DTE) and data communications equipment (DCE)

- USB

- IEEE-1394a (FireWire)

- PS/2

- 10/100 Base-T ethernet

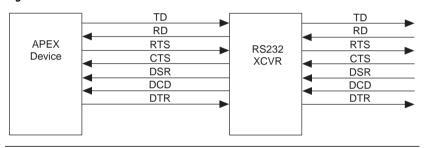

### RS-232C Interface

Two RS-232C interfaces are provided with the development board: a DTE and a DCE interface. All hardware lines are provided for each interface. Table 17 provides information on the devices used to implement the RS-232C interface.

| Table 17. RS-232C Interface Device Reference |                                               |                   |                         |  |

|----------------------------------------------|-----------------------------------------------|-------------------|-------------------------|--|

| Reference                                    | eference Part Number Manufacturer Description |                   |                         |  |

| U32                                          | SP208CT                                       | Sipex             | RS-232C DTE transceiver |  |

| U34                                          | SP208CT                                       | Sipex             | RS-232C DCE transceiver |  |

| U33                                          | SN74LV245BDW                                  | Texas Instruments | Bus transceiver         |  |

The transceiver used for both interfaces requires a 5.0-V power supply. The signals going into the APEX device are beyond the maximum 3.3-V input voltage range. A 3.3-V bus and a transceiver with 5.0-V tolerant inputs are used to shift signals going into the APEX device. This feature is always enabled so no additional control is required. Since the bus transceiver is always active, the RS-232C input pins cannot be used as outputs or contention will occur. If these pins are not used as part of a design, ensure that they remain in the high-impedance (input) state. See Table 71 on page 63 and Table 72 on page 64 for information on the RS-232C DTE and DCE signals.

### DTE UART Interface

The APEX device may use a UART core which is directly connected to a device to provide the RS232C interface levels. Table 18 shows the DTE UART interface characteristics.

| Table 18. DTE UART Interface Characteristics |   |     |        |

|----------------------------------------------|---|-----|--------|

| Features I/O Pins Voltage Power Budget       |   |     |        |

| Tx, Rx & Control                             | 7 | 5.0 | 0.25 W |

# DCE UART Interface

The APEX device may use a UART core which is connected to a device on the board to provide the RS232C interface levels.

| Table 19. DCE UART Interface Characteristics |          |         |              |

|----------------------------------------------|----------|---------|--------------|

| Features                                     | I/O Pins | Voltage | Power Budget |

| Tx, Rx & Control                             | 7        | 5.0     | 0.25 W       |

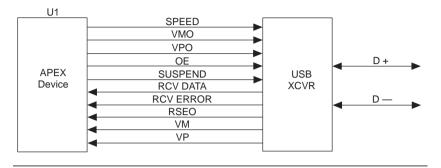

#### USB Interface

The USB interface consists of a single host connection with a type-A socket. The interface is capable of both low- and high-speed operation without changing the configuration. A jumper allows 5.0 V to be output to the cable and can be useful when connecting a passive device, such as a mouse, to the port. Do not use this feature if it is not required, because it may cause two power supplies to be connected together. Table 20 provides information on the device used to implement the USB interface.

| Table 20. USB Interface Device Reference |             |              |                 |

|------------------------------------------|-------------|--------------|-----------------|

| Reference<br>Designator                  | Part Number | Manufacturer | Description     |

| U35                                      | SP5301CN    | Sipex        | USB Transceiver |

Table 75 on page 65 provides information on USB control lines.

The APEX device may use a USB core that implements the USB Serial Interface Engine (SIE) and is connected to a device to provide the USB interface. Table 21 shows the USB interface characteristics.

| Table 21. USB Interface Characteristics |          |         |              |

|-----------------------------------------|----------|---------|--------------|

| Feature                                 | I/O Pins | Voltage | Power Budget |

| USB interface                           | 10       | 5.0 V   | 0.5 W        |

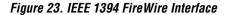

## IEEE-1394a (FireWire) Interface

The IEEE-1394a FireWire interface consists of a transceiver/arbiter and associated components. The physical interface provides an IEEE-1394a compliant cable port at 100/200/400 Mbits per second for a link layer controller (LLC) implemented as a core inside the APEX device.

The transceiver/arbiter generates the clock for the LLC inside the APEX device, which is required to synchronize the data coming from the LLC to the transceiver. Eight data lines are provided for data transfers between the LLC and the transceiver. The number of data lines required for the LLC core depends on the transmission rate used for the FireWire bus. The local bus clock always maintains the same frequency. To transfer the data to the transceiver faster for higher transmission rates, the data bus width must increase. Table 22 shows the data bus requirements for different transmission rates.

| Table 22. FireWire Data Bus Usage versus Transmission Rate |               |                                                        |  |

|------------------------------------------------------------|---------------|--------------------------------------------------------|--|

| Data Rate<br>(Mbits per Second)                            | Data Bus Pins | Comments                                               |  |

| 100                                                        | D[10]         | Minimum speed for two data pins at 49.152 MHz          |  |

| 200                                                        | D[30]         | Four data pins at 49.152 MHz to double the data rate   |  |

| 400                                                        | D[70]         | All eight data pins used to double the data rate again |  |

The power control pins for the FireWire interface are pulled low, providing a self ID of 0 because the interface cannot source power to the cable, nor does it require any power from the cable. Table 23 lists information on the device used to implement the FireWire interface.

| Table 23. FireWire Interface Device Reference             |           |                      |                                               |  |  |

|-----------------------------------------------------------|-----------|----------------------|-----------------------------------------------|--|--|

| Reference Part Number Manufacturer Description Designator |           |                      |                                               |  |  |

| U31                                                       | TSB41LV03 | Texas<br>Instruments | IEEE-1394a three port transceiver and arbiter |  |  |

The APEX device can use an IEEE 1394 core, directly connected to a device to provide the 1394 interface. Table 24 shows the FireWire interface characteristics. Table 76 on page 66 provides more information on the FireWire control interface signals.

| Table 24. FireWire Interface Characteristics       |    |       |        |       |  |  |

|----------------------------------------------------|----|-------|--------|-------|--|--|

| Feature I/O Pins Voltage Clocks (MHz) Power Budget |    |       |        |       |  |  |

| 1394 Interface                                     | 15 | 3.3 V | 24.576 | 0.4 W |  |  |

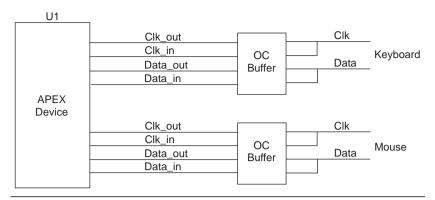

### PS/2 Interface

Two PS/2 interfaces are provided with the development board for connecting a mouse and a keyboard. The transceiver provides the correct voltage level translation for the peripheral devices. Power and ground are also provided, because the mouse and keyboard are passive devices. Table 25 provides information on the devices used to implement the PS/2 interface.

| Table 25. Keyboard & Mouse Interface Device Reference |         |                            |                           |  |  |  |

|-------------------------------------------------------|---------|----------------------------|---------------------------|--|--|--|

| Reference Part Number Manufacturer Description        |         |                            |                           |  |  |  |

| U36                                                   | DM7404M | Fairchild<br>Semiconductor | Mouse interface buffer    |  |  |  |

| U37                                                   | DM7404M | Fairchild<br>Semiconductor | Keyboard interface buffer |  |  |  |

Table 73 on page 64 provides detailed information on the PS/2 keyboard interface, and Table 74 on page 65 provides information on the PS/2 mouse interface. The APEX device may use a core, connected to a device to provide the PS/2 keyboard and mouse interfaces. Table 26 shows the keyboard and mouse interface characteristics.

| Table 26. Keyboard & Mouse Interface Characteristics |  |  |  |  |  |

|------------------------------------------------------|--|--|--|--|--|

| Feature I/O Pins Voltage Power Budget                |  |  |  |  |  |

| Keyboard and mouse 8 5.0 V 0.25 W                    |  |  |  |  |  |

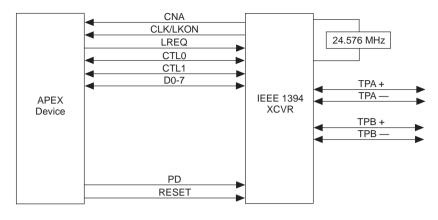

### 10/100 Ethernet Interface

The ethernet interface consists of a transceiver, or PHY, and associated discrete components. This allows you to implement an ethernet media access controller (MAC) in the APEX device. As shown in Table 77 on page 67, the connections consist of the standard media independent interface (MII) and additional signals. Table 27 provides information on the devices used to implement the ethernet interface.

| Table 27. Ethernet Interface Device Reference  |              |     |                          |  |  |

|------------------------------------------------|--------------|-----|--------------------------|--|--|

| Reference Part Number Manufacturer Description |              |     |                          |  |  |

| U29                                            | 78Q2120-64CG | TDK | Ethernet MII transceiver |  |  |

## Parallel I/O Interface

The parallel I/O interface consists of an IEEE-1284 compatible transceiver. Table 28 provides information on the device used to implement the parallel port interface.

| Table 28. IEEE-1284 Interface Device Reference |                |                           |                                             |  |  |

|------------------------------------------------|----------------|---------------------------|---------------------------------------------|--|--|

| Reference Part Number Manufacturer Description |                |                           |                                             |  |  |

| U25                                            | 74VHC161284MEA | National<br>Semiconductor | IEEE-1284<br>(parallel port)<br>transceiver |  |  |

| U24, U26                                       | SN74LV245BDW   | Texas Instruments         | Bus transceiver                             |  |  |

The parallel interface transceiver has eight bidirectional data buffers and can be used in extended capabilities port (ECP) mode. The interface provides enough buffers to connect all ECP control signals from the controller to the peripheral device. Internal pull-up resistors eliminate the need for external resistors for the high drive open drain buffers used to drive the data lines connected to the external device.

The parallel port interface uses a 5.0-V supply, with output signals set to 5.0 V. Two 3.3-V supply bus transceivers with 5.0-V tolerant inputs are used on APEX device input signals. The bidirectional data bus uses U24 and the transceiver direction is connected to the direction control for the IEEE-1284 transceiver. No additional control is required; however, the timing for the bus transceiver must be considered as part of the interface. The second transceiver is always enabled. If the signals are not used, the APEX device pins must always be left in the high-impedance (Input) state.

For further information on the parallel port control lines, see Table 78 on page 68 and Table 79 on page 70.

For the parallel port interface to operate normally, the APEX device contains the host controller and the external device serves as the peripheral. The parallel port interface can also be configured so that the APEX device can act as a peripheral device. Port direction is controlled by nine jumpers (JP19-34). Jumper positioning determines the direction of the parallel port. When all jumpers are placed in the 1-2 position, the parallel port will be in host mode, which is required for normal operation. By placing all jumpers in the 2-3 position, the directions for the control lines are reversed and the board interface operates as a peripheral. For proper operation, all jumpers must be in the same position. Table 78 on page 68 and Table 79 on page 70 provides information on the parallel port control lines. Table 29 shows the IEEE 1284 interface characteristics.

| Table 29. IEEE 1284 Interface Characteristics |    |       |       |  |  |

|-----------------------------------------------|----|-------|-------|--|--|

| Feature I/O Voltage Power Budget              |    |       |       |  |  |

| 1284 parallel port                            | 19 | 5.0 V | 0.4 W |  |  |

## **Mezzanine Interfaces**

A PCI Mezzanine Card (PMC) site is included on the board. The interface is 32 or 64-bit 33 or 66-MHz capable, operates at 3.3 V, and is *PCI Local Bus Specification*, *Revision 2.2* compliant.

See the following references for more detailed information on the PMC interface.

- PCI Local Bus Specification, Revision 2.2.

- Standard for Physical and Environmental Layers for PCI Mezzanine Cards: PMC IEEE P1386.1.

- Standard for a Common Mezzanine Card Family: CMC IEEE P1386/ Draft 2.0.

No user I/O pins are provided for the PMC interface. All user I/O pins from the PMC are provided through connectors mounted directly on the mezzanine card. Clearance is provided on the board to support a PMC with user I/O connectors as required by the CMC specification. For detailed information on the PCI interface and connector pinouts, refer to PMC and CMC specifications (IEEE-1386).

Table 81 on page 72, Table 82 on page 73, and Table 83 on page 73 list the PMC signal pin assignments.

# APEX Device Signal Definition

Table 30 shows the definitions for the APEX device signals required to implement the PMC interface.

| 32-Bit PCI        |                                        |        |            |  |  |

|-------------------|----------------------------------------|--------|------------|--|--|

| Function          | Signals                                | Number | I/O Format |  |  |

| Address and data  | AD[31:0]<br>C/BE[3:0]#<br>PAR          | 37     | 3.3-V PCI  |  |  |

| Interface control | FRAME# TRDY# IRDY# STOP# DEVSEL# LOCK# | 6      | 3.3-V PCI  |  |  |

| Error reporting   | PERR#<br>SERR#                         | 2      | 3.3-V PCI  |  |  |

| Arbitration       | REQ#<br>GNT#                           | 2      | 3.3-V PCI  |  |  |

| Interrupts        | INTA# INTB# INTC# INTD#                | 4      | 3.3-V PCI  |  |  |

| Cache support     | SBO#<br>SDONE                          | 2      | 3.3-V PCI  |  |  |

| System            | CLK<br>RST#                            | 2      | 3.3-V PCI  |  |  |

|                   | 64-Bi                                  | it PCI |            |  |  |

| Address and data  | AD[63:32]<br>C/BE[7:4]#<br>PAR64       | 37     | 3.3-V PCI  |  |  |

| Arbitration       | REQ64#<br>GNT64#                       | 2      | 3.3-V PCI  |  |  |

Some signals are not included in the above table. IDSEL is a PCI signal used as a device select for configuration cycles and is generally connected to one of the address lines. The PMC JTAG port signal can be daisy-chained with the APEX device JTAG port without using any APEX device I/Os. BUSMODE signals are defined to allow different specifications in the same mezzanine form factor.

#### Board-Level Issues

The PMC interface requires no devices on the board level, assuming that the PCI interface is implemented in the APEX device.

As the APEX device only supports 3.3-V PCI I/O, 5.0-V PMCs are not supported. PMCs can use up to 7.5 W and are supported by the development board.

The PCI clock signal should be driven to both the PMC CLK pin and to one of the APEX device dedicated clock inputs. This signal must comply with the PCI electrical and timing requirements.

The PCI mezzanine card standard only defines operation at 33 MHz. However, the development board is designed to support 66 MHz signaling. Table 31 lists the PMC-PCI interface characteristics.

| Table 31. PMC-PCI Interface Characteristics              |                                            |       |        |       |  |  |

|----------------------------------------------------------|--------------------------------------------|-------|--------|-------|--|--|

| Interface Features I/O Pins Voltages Clocks Power Budget |                                            |       |        |       |  |  |

| PMC-PCI Interface                                        | PMC-PCI Interface 94 +/- 12 V 33 MHz 7.5 W |       |        |       |  |  |

|                                                          | 94                                         | 3.3 V | 66 MHz | 7.5 W |  |  |

## General-Purpose Mezzanine Interface

The general-purpose mezzanine interface provides an additional custom interface prototyping area. The interface includes 38 general-purpose user I/O lines, power (3.3 V, 5 V, 12 V, and -12 V), and clock pins. The clock interface is synchronous with the main processor and memory clock to ease the effort required to interface with the rest of the board.

The general purpose mezzanine interface also includes a JTAG chain so that devices can be programmed using the same interface as devices on the development board.

External feedback pins for the PLL circuitry are also connected to the general-purpose mezzanine interface. This allows an optional method for externally connecting these signals. They may also be internally connected to the APEX device.

Table 84 on page 75 and Table 85 on page 76 provide a list of the general-purpose mezzanine signal pin assignments.

A socket is available for a user defined clock, which is distributed to both the APEX device and the general-purpose mezzanine connector. In addition, a BNC connector for an external clock signal can be selected. Table 32 shows the PMC-GP interface characteristics.

| Table 32. PMC-GP Interface Characteristics |                                      |           |        |       |  |  |

|--------------------------------------------|--------------------------------------|-----------|--------|-------|--|--|

| Feature                                    | I/O Pins Voltages Clocks Power Budge |           |        |       |  |  |

| PMC-GP                                     | 38                                   | 12, –12 V | Socket | 7.5 W |  |  |

| interface                                  | 38                                   | 3.3 V     | Socket | 7.5 W |  |  |

# **Display & Switch Interfaces**

A two-row, 16-character liquid crystal display (LCD) is provided on the board. The LCD has an integrated controller and operates from a single 5.0-V supply. The LCD display is an Emerging Technologies ED162A0RU display that uses a Hitachi HD44780U controller. See Table 33.

| Table 33. IEEE-1284 Interface Device Reference |              |                                  |                                                                       |  |  |

|------------------------------------------------|--------------|----------------------------------|-----------------------------------------------------------------------|--|--|

| Reference<br>Designator                        | Part Number  | Manufacturer                     | Description                                                           |  |  |

| J5                                             | ED162A0RU    | Emerging Display<br>Technologies | 2 × 16 Character<br>display (connected<br>through a 1 × 16<br>header) |  |  |

| N/A                                            | HD44780U     | Hitachi                          | LCD controller<br>(installed on the<br>display)                       |  |  |

| U7                                             | SN74LV245BDW | Texas Instruments                | Bus transceiver                                                       |  |  |

The LCD is powered from a 5.0-V supply, where the output signal levels are 5.0-V TTL. A 3.3-V bus transceiver translates signal levels to match with the APEX device inputs. The direction of the bus transceiver is controlled by the read/write line of the display, so no additional control logic is required. The LCD interface requires a nominal 270 kHz clock, which is generated from a general-purpose APEX device output. Table 34 shows the LCD interface characteristics.

| Table 34. LCD Interface Characteristics |  |  |  |  |  |

|-----------------------------------------|--|--|--|--|--|

| Feature I/O Pins Voltages Power Budget  |  |  |  |  |  |

| LCD controller 11 5.0, -5.0 V 0.1 W     |  |  |  |  |  |

Table 87 on page 77 lists the LCD signal pin assignments.

## LED Interface

The development board has several LEDs that tie user-defined functions and application-specific functions directly to the APEX device. Table 88 on page 77 provides more information on APEX device pins connected to LEDS

Six LEDs are connected directly to the APEX device I/O pins. The LEDs illuminate when an I/O pin is driven low. These LEDs consist of:

- Four green LEDs (LED1, LED2, LED3, LED4)

- Two red LEDs (LED5, LED6)

LEDs are also used for specific application functions on the board, such as the configuration and ethernet interfaces. The green LEDs are also used as phase-locked loop (PLL) lock indicators. Table 35 lists the LEDs and their functions.

| Table 35. Application LED Usage |             |                                                                          |  |  |  |

|---------------------------------|-------------|--------------------------------------------------------------------------|--|--|--|

| LED Reference                   | Application | Use                                                                      |  |  |  |

| D2                              | Conf_Done   | Indicates that the APEX configuration is complete                        |  |  |  |

| D1                              | NStatus     | Indicates an error in the APEX configuration                             |  |  |  |

| D5                              | LEDL        | Ethernet: Link Up (normally on)                                          |  |  |  |

| D6                              | LEDTX       | Ethernet: TX (on during TX)                                              |  |  |  |

| D7                              | LEDRX       | Ethernet: RX (on During RX)                                              |  |  |  |

| D4                              | LEDCOL      | Ethernet: collision in half duplex mode (off in full duplex mode)        |  |  |  |

| D8                              | LEDBTX      | Ethernet: 100 BaseT connection (off for all other connection interfaces) |  |  |  |

| D9                              | LEDBT       | Ethernet: 10 BaseT connection (off for all other connections)            |  |  |  |

| D10                             | LEDFX       | Ethernet: full duplex on (off in half duplex)                            |  |  |  |

### VGA Monitor Interface

The VGA monitor interface is a restricted version of VGA, and is compliant with the monitor interface used with the Altera University Program Design Laboratory Package.

The VGA monitor interface includes three-color outputs that can be turned on or off. High output on any of the R, G, or B outputs results in a 0.7-V nominal signal at the VGA connector pin. Low output results in 0-V output at the VGA connector. The output is achieved with a resistor/diode network between an APEX device I/O pin and the connector. The horizontal and vertical sync signals are connected directly from the APEX device. Table 86 on page 76 provides more information on the VGA interface. Table 36 shows the VGA monitor interface characteristics

| Table 36. VGA Monitor Interface Characteristics |          |              |              |  |

|-------------------------------------------------|----------|--------------|--------------|--|

| Feature                                         | I/O Pins | Clocks (MHz) | Power Budget |  |

| VGA interface                                   | 5        | 25.175       | 0            |  |

## User-Defined Switches

Four momentary switches with integrated LEDs are connected to the APEX device. Pressing the switch inputs a low signal to the APEX device pin until the switch is released.

The (S1) switch is the device-wide clear input pin and is connected to DEV\_CLRn on the APEX device. Another switch (S2) is connected to a low-skew dedicated input and functions as a reset input for applications where DEV\_CLRn is not applicable. The remaining switches are connected to I/O pins and can be configured internally. Debouncing is provided for these signals and must be performed internally. Table 87 on page 77 provides more information on the switch interface.

## User-Defined LEDs

The development board provides six user-definable LEDs driven from the APEX device that consist of two red LEDs, two yellow LEDs and two green LEDs. Table 37 lists the interface characteristics for the LED interfaces.

| Table 37. LED Interface Characteristics |          |             |                  |  |

|-----------------------------------------|----------|-------------|------------------|--|

| Feature                                 | I/O Pins | Voltage (V) | Power Budget (W) |  |

| Two red LEDs                            | 2        | 5.0         | 0.05             |  |

| Two yellow LEDs                         | 2        | 5.0         | 0.05             |  |

| Two green LEDs                          | 2        | 5.0         | 0.05             |  |

# **Test & Debugging Features**

The development board includes three test features:

- The SignalTap embedded logic analyzer, which uses a JTAG interface to allow access to activity on internal nodes

- An EJTAG connector, which can be used for debugging processor cores

- Test connectors provided for debugging with a logic analyzer

## SignalTap Embedded Logic Analyzer

The development board supports in-circuit debugging with the SignalTap logic analyzer using the Quartus software and MasterBlaster communication cable.

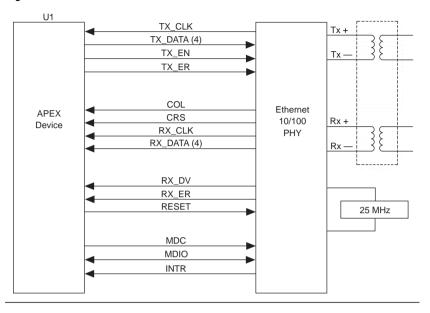

### EJTAG Interface

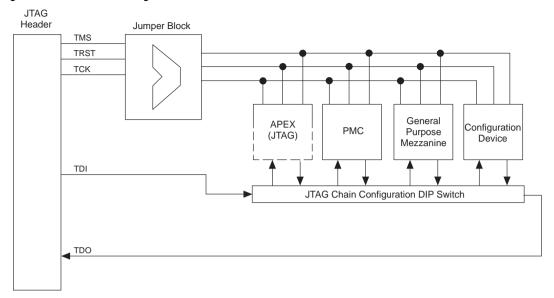

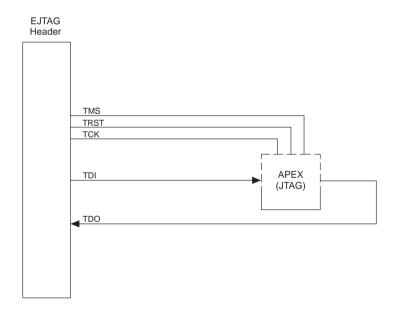

A 52-pin header is provided for use with an EJTAG interface for debugging a MIPS processor core in the APEX device. Although the EJTAG interface supports normal JTAG signals, it is not included as part of the programming chain. The EJTAG interface uses normal I/O pins. Before the APEX device is completely configured, these I/O pins are not available for general use because the external JTAG chain could be broken. Figure 6 shows the organization of the JTAG and EJTAG interfaces. The two interfaces are separate. The JTAG chain configuration jumpers are used to access all of the JTAG devices separately or as part of a long chain.

Figure 6. JTAG/EJTAG Configuration

Key external signals may be attached to connectors to support direct connection to external logic analyzers. External connectors are used during validation of the development board and can be removed from the final product. However, the SignalTap logic analyzer is designed to work effectively in conjunction with external logic analyzers, such as the SignalTap Plus system analyzer, supporting cross-triggering and other features. Table 80 on page 70 lists the APEX device pins used for the EJTAG interface.

Refer to the MIPS EJTAG Debug Solution Rev 2.0 for a detailed reference on using the EJTAG interface.

#### Test Connectors

Six test connectors are provided on the development board. These test connectors allow for external monitoring of the high-speed memory interfaces. Refer to Table 99 on page 84 through Table 104 on page 87 for pin definitions of all of the test connectors.

# Jumper Configuration

The jumpers on the development board serve several functions:

- Clock distribution

- Enabling the PLL interface

- JTAG configuration

- Optional USB power setting

- IEEE 1284 parallel interface configuration

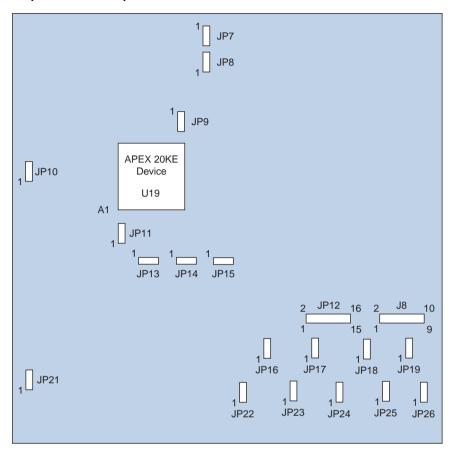

Figure 7 illustrates the development board jumper configuration.

Figure 7. Development Board Jumper Locations

### **Clock Distribution**

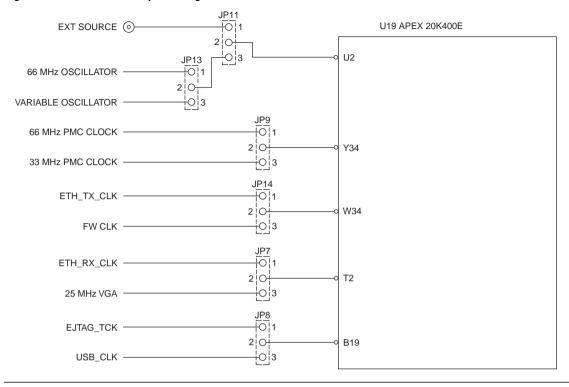

Five inputs on the APEX device are used for clocks. Four are global clock inputs, and one is a low-skew dedicated input. Jumpers JP9 to JP14 are used to select different clock inputs. Table 38 lists all clock sources on the development board. Table 39 lists the APEX device pins used as clock inputs and the possible sources of the clock inputs for each pin. Table 40 and Figure 8 illustrate how to configure the clock selection jumpers.

| Table 38. SOPC Clock Sources |                        |            |                                                                                    |

|------------------------------|------------------------|------------|------------------------------------------------------------------------------------|

| Source<br>Number             | Name                   | Source Pin | Description                                                                        |

| 1                            | Memory/processor clock | U28        | The 66 MHz main clock provided to all the synchronous memory and a processor core. |

| 2                            | PMC clock (33MHz)      | U27        | 33 MHz oscillator for a 33-MHz PCI core and PMC card.                              |

| 3                            | PMC clock (66 MHz)     | U6         | 66 MHz oscillator for a 66 MHz-PCI core and PMC card.                              |

| 4                            | Ethernet TX clock      | U29 pin 27 | TX clock output from Phy.                                                          |

| 5                            | Ethernet RX clock      | U29 pin 24 | RX clock output from Phy.                                                          |

| 6                            | External source        | J6         | External source for the memory/processor clock.                                    |

| 7                            | VGA clock              | U2         | 25.175 oscillator for VGA interface.                                               |

| 8                            | USB clock              | U8         | 48 MHz oscillator for USB interface.                                               |

| 9                            | FireWire clock         | U31 pin 2  | FireWire SYSCLCK output from transceiver.                                          |

| 10                           | EJTAG TCK              | J10 Pin 9  | TCK input from EJTAG header.                                                       |

| 11                           | Variable oscillator    | U30        | Socket provided for populating various clock frequencies.                          |

| Table 39. EP20K400E Clock Input Pins and Sources |                    |                           |  |

|--------------------------------------------------|--------------------|---------------------------|--|

| Pin                                              | Description        | Clock Inputs to Pin       |  |

| U2                                               | Global clock input | Clock source 1, 6, and 11 |  |

| Y34                                              | Global clock input | Clock source 2, and 3     |  |

| W34                                              | Global clock input | Clock source 4, and 9     |  |

| T2                                               | Global clock input | Clock source 5, and 7     |  |

| B19                                              | Low skew input     | Clock source 8, and 10    |  |

| Table 40. Clock Jumper Configuration |             |                                    |                     |  |

|--------------------------------------|-------------|------------------------------------|---------------------|--|

| Clock Description                    | Header      | Jumper Position and Input Selected |                     |  |

|                                      | Designation | 1-2                                | 2-3                 |  |

| PMC clock                            | JP9         | 66 MHz                             | 33 MHz              |  |

| Memory clock                         | JP11        | External source<br>J6              | Output of JP13      |  |

| VGA/ethernet RX clock                | JP7         | VGA 25.175 MHz                     | Ethernet RX         |  |

| EJTAG/USB clock                      | JP8         | EJTAG                              | USB 48 MHz          |  |

| Mezzanine clock                      | JP13        | 66 MHz                             | Variable oscillator |  |

| FireWire/ethernet TX clock           | JP14        | Ethernet TX                        | FireWire clock      |  |

Figure 8. Clock Source Jumper Configuration

Jumpers JP11 and JP13 are used to select one clock input. JP11 chooses between the 66 MHz or the socketed variable oscillator. JP13 chooses between the output from JP11 and the external clock input.

The master clock input is the 66-MHz oscillator. This clock is used for all synchronous memory interfaces as well as the general-purpose mezzanine interface and the APEX device.

During development, you may need to run the interface at a slower clock rate, using either the external clock input or the variable oscillator.

The external oscillator is a BNC cable input (J6) that can be used to input a signal from a laboratory signal generator. The variable oscillator is a four-pin socket that supports a variety of 5.0-V oscillators.

The development board operates best for synchronous memory interface frequencies up to 66 MHz. You may attempt higher frequencies without risk of damaging the board; however, results may be unpredictable.

### **JTAG Configuration**

All devices that can be programmed through the JTAG interface are connected to a  $2 \times 8$  0.1-inch configuration header, JP12. The devices connected to the chain are programmed in the following order:

- EP20K400E device

- EPC2 configuration devices

- PMC interface

- General-purpose mezzanine interface

| Table 41. JTAG Chain Configuration  |                                          |                                            |  |  |

|-------------------------------------|------------------------------------------|--------------------------------------------|--|--|

| Device                              | Bypass Jumper Setting<br>(Pins for JP12) | Chained Jumper Settings<br>(Pins for JP12) |  |  |

| APEX 20KE device                    | 1-3                                      | 1-2<br>3-4                                 |  |  |

| EPC2 configuration device           | 5-7                                      | 5-6<br>7-8                                 |  |  |

| PMC interface                       | 9-11                                     | 9-10<br>11-12                              |  |  |

| General-purpose mezzanine interface | 13-15                                    | 13-14<br>15-16                             |  |  |

If a device is not included in the programming chain, the device must be bypassed at JP12 to prevent the the JTAG chain from being broken. For example, if the APEX device is programmed alone, shunts would be installed. Table 42 shows the JP12 configuration for APEX and EPC2 devices.

| Table 42. JP12 Configuration for APEX & EPC2 Devices |             |  |  |

|------------------------------------------------------|-------------|--|--|

| APEX Device                                          | EPC2 Device |  |  |

| Pins 1-2                                             | Pins 1-3    |  |  |

| Pins 3-4                                             | Pins 5-6    |  |  |

| Pins 5-7                                             | Pins 7-8    |  |  |

| Pins 9-11                                            | Pins 9-11   |  |  |

| Pins 13-15                                           | Pins 13-15  |  |  |

The EPC2 device can be programmed with the MAX+PLUS II software version 9.5 or higher or the Quartus software version 2000.02 or higher using either the MasterBlaster or ByteBlasterMV communications cable. Figure 9 shows how to connect the MasterBlaster or ByteBlasterMV communication cable.

Figure 9. Connecting the MasterBlaster & ByteBlasterMV Cables

#### **IEEE 1284 Parallel Interface**

The IEEE 1284 parallel interface can be configured so that the development board can operate as a host or as a peripheral. To configure the interface to use the board as a host, jumpers JP19 to JP34 must be set to the 1-2 position. To configure the interface to use the development board as a peripheral, jumpers JP19 to JP34 must be set to the 2-3 position.

The same female connector is used when configuring the interface for host and peripheral mode. The interface does not meet the standard mechanical requirements when in peripheral mode; however, the interface meets the standard electrical requirements. A 25-pin gender adapter is required to allow a normal peripheral cable to be used with the development board.

# Interface Specifications

Tables 43 through 53 list the interface specifications for the development board.

| Interface                     | I/O Pins |

|-------------------------------|----------|

| Global reset input            | 1        |

| CCINT                         | 40       |

| /CCIO                         | 24       |

| /CCPLL                        | 5        |

| /CCCLK                        | 1        |

| GNDINT                        | 68       |

| GNDPLL                        | 6        |

| GNDCLK                        | 1        |

| Memory - SRAM #1              | 64       |

| Memory - SRAM #1              | 64       |

| lemory - EPROM, Flash & SDRAM | 79       |

| clocks                        | 5        |

| Configuration                 | 19       |

| S232C - DTE                   | 7        |