# **Quartus® II Software Design Series: Timing Analysis**

#### **Design Verification**

- Most PLD development time is spent verifying your design

- Verification includes

- Timing analysis

- Simulation (internal & system-level)

- Formal verification

- Power analysis

- Signal integrity analysis

- In-system testing

#### **Quartus II Software Support**

- Quartus<sup>®</sup> II software provides features to aid & accelerate the verification process

- TimeQuest Timing Analyzer (TA)

- Quartus II Simulator and 3<sup>rd</sup>-party support\*

- PowerPlay Power Analyzer\*

- Debugging tools (in-system testing)\*

<sup>\*</sup>These topics are covered in the "Quartus II Software Design Series: Verification" course

#### Other Quartus II Design Series courses

#### Quartus II Software Design Series: Foundation

- Project creation and management

- Design entry methods and tools

- Compilation and compilation results analysis

- Creating and editing settings and assignments

- I/O planning and management

- Introduction to timing analysis with the TimeQuest timing analyzer

#### Quartus II Software Design Series: Verification

- Basic design simulation with ModelSim-Altera

- Power analysis

- Debugging solutions

#### Quartus II Software Design Series: Optimization

- Incremental compilation

- Quartus II optimization features & techniques

#### **Objectives**

- Display a complete understanding of timing analysis

- Build SDC files for constraining PLD designs

- Verify timing on simple & complex designs using TimeQuest TA

#### Class Agenda

- TimeQuest basics

- Timing analysis basics

- Exercise 1

- TimeQuest reporting

- Clock constraints

- Exercise 2

- Synchronous I/O constraints

- Exercise 3

- Source Synchronous I/O constraints

- Exercise 4

- Constraining asynchronous signals

- Timing exceptions

- False paths

- Multicycle constraints

- Exercise 5

#### How does timing verification work?

- Every device path in design must be analyzed with respect to timing specifications/requirements

- Catch timing-related errors faster and easier than gate-level simulation & board testing

- Designer must enter timing requirements & exceptions

- Used to guide fitter during placement & routing

- Used to compare against actual results

# **Quartus® II Software Design Series: Timing Analysis**

**TimeQuest Basics**

# **Timing Analysis Agenda**

- TimeQuest basics

- Timing analysis basics

- Timing reports

- Timing constraints

- Example application

#### **TimeQuest Timing Analyzer**

- Timing engine in Quartus Il software

- Provides timing analysis solution for all levels of experience

- Features

- Synopsys Design Constraints (SDC) support

- Standardized constraint methodology

- Easy-to-use interface

- Constraint entry

- Standard reporting

- Scripting emphasis

- Presentation focuses on using GUI

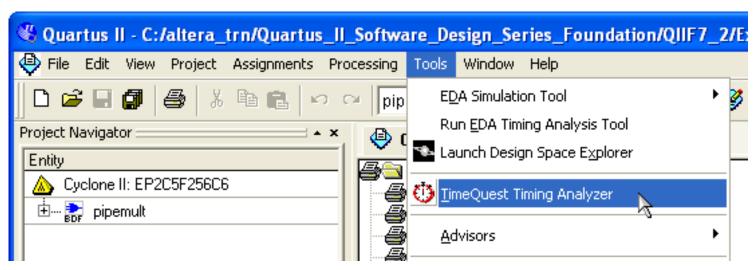

#### **Opening the TimeQuest Interface**

- Toolbar button (\*\*)

- **Tools** menu

- Tasks window

- Stand-alone mode

- quartus staw

- Command line

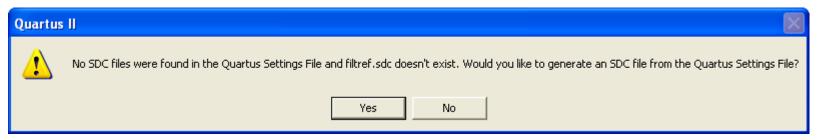

#### **Quartus Settings File (QSF)**

- SDC constraints are **not** stored in QSF

- For 90nm and older devices, TimeQuest TA uses script to convert QSF timing assignments to SDC

- TimeQuest Constraints menu

- Done automatically if no SDC file exists when first opening timing analyzer

- See Quartus II Handbook chapter, Switching to the TimeQuest Timing Analyzer for details

- Differences between Classic Timing Analyzer and TimeQuest TA

- Details on conversion utility

- Online training also available

- Switching to the TimeQuest Timing Analyzer

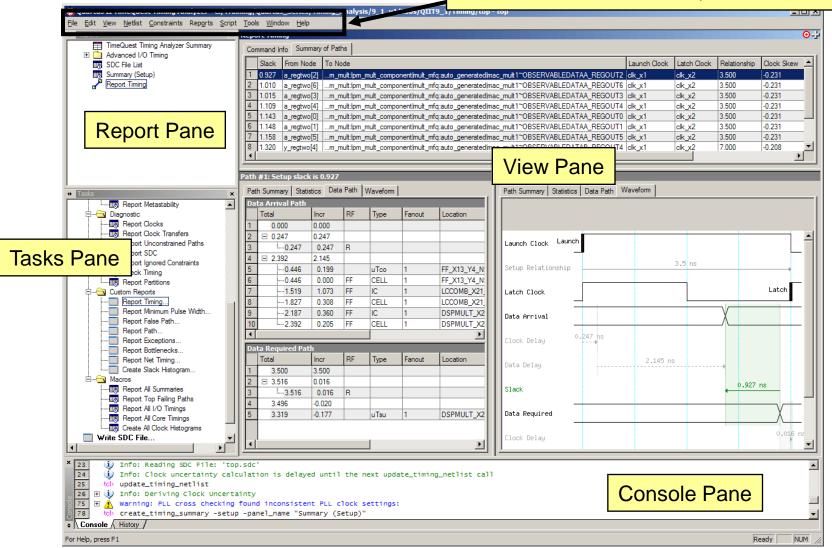

#### **TimeQuest GUI**

#### Menu access to all TimeQuest features

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat. & Tm. Off. and Altera marks in and outside the U.S.

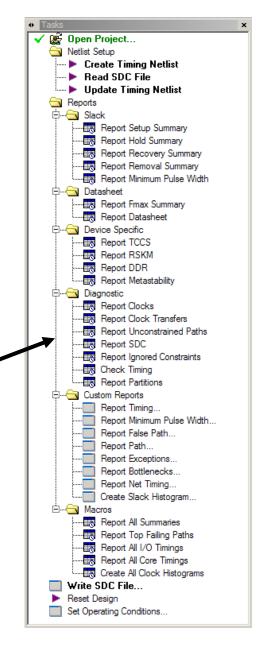

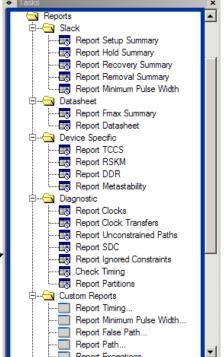

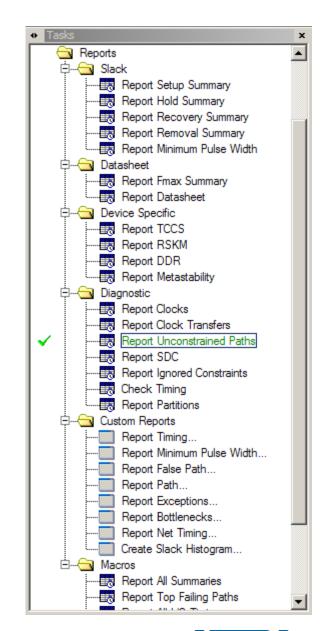

#### **Tasks Pane**

- Provides quick access to common operations

- Command execution

- Report generation

- Executes most commands with default settings

Double-click to execute any command

Use menus for nondefault settings

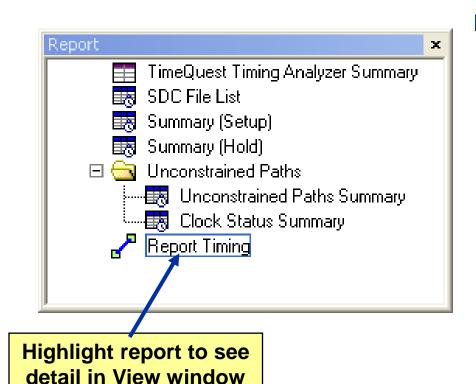

#### **Report Pane**

- Displays list of generated reports currently available for viewing

- Reports generated by Tasks pane

- Reports generated using report commands

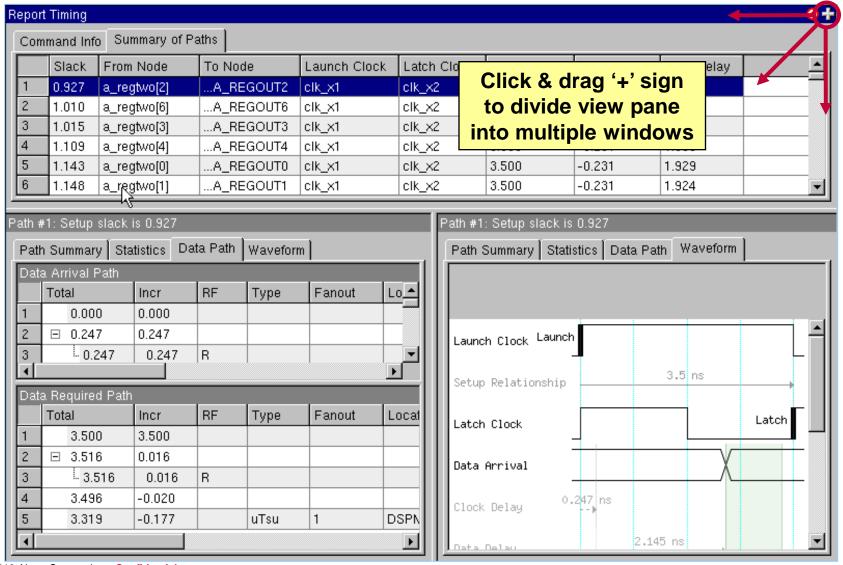

# **Viewing Multiple Reports**

© 2010 Altera Corporation—Confidential

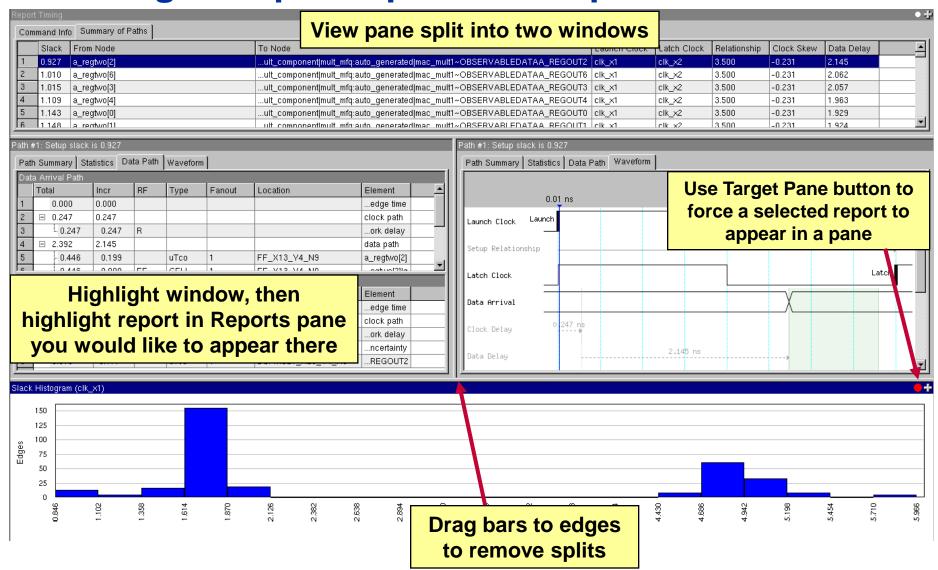

## Viewing Multiple Reports Example

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat. & Tm. Off. and Altera marks in and outside the U.S.

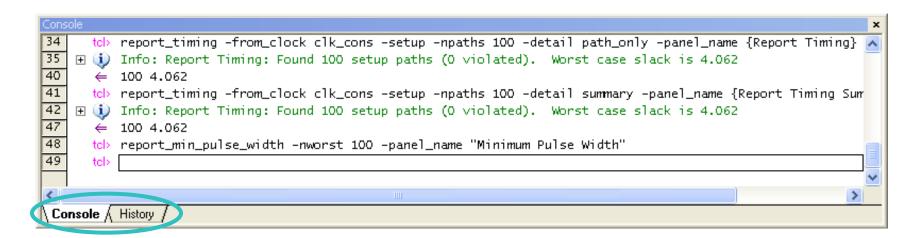

#### **Console pane**

- Allows direct entry and execution of SDC & Tcl commands

- Displays equivalent of command executed by GUI

- Displays TimeQuest output messages

- History tab records all executed SDC & Tcl commands

- Copy & paste to create scripts or SDC files

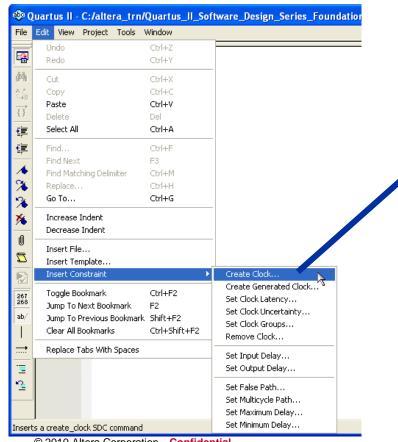

#### **SDC** File Editor = Quartus II Text Editor

- Use Quartus II editor to create and/or edit SDC

- SDC editing unique features (for .sdc files)

- Access to GUI dialog boxes for constraint entry (Edit ⇒ Insert Constraint)

- Syntax coloring

- Tooltip syntax help

- SDC templates

```

TimeQuest File menu ⇒ New/Open SDC File

Quartus II File menu ⇒ New ⇒ Other Files

🕸 Quartus II - C

File Edit View Project Tools Window

35

44

38

39

40

41

create Tclock -name {clk1} -period 6.000 -waveform { 0.000 3.000 } [get ports {clk1}] -add

42

create_clock [-add] [-name <clock_name>] -period <value> [-waveform <edge_list>] [<targets>]

-add: Adds clock to a node with an existing clock

43

# # * * * * -name <clock_name >: Clock name of the created clock

-period <value>: Speed of the clock in terms of clock period

-waveform <edge_list>: List of edge values

46

# * * * * * <targets>: List or collection of targets

47

3.250 [get ports {dataa[1]}]

set input delay -add delay -max -clock [get clocks {clk1}]

49

set input delay -add delay

in -clock [get clocks {clk1}]

1.750 [get ports {dataa[1]}]

50

set input delay -add delay

nax -clock [get clocks {clk1}]

3.250 [get ports {dataa[3]}]

set input delay -add delay

min -clock [get clocks {clk1}]

1.750 [get ports {dataa[3]}]

set input delay -add delay

max -clock [get clocks {clk1}]

2.500 [get ports {wraddress[0]}]

53

set input delay -add delay

min -clock [get clocks {clk1}]

1.000 [get ports {wraddress[0]}]

set input delay -add delay

max -clock [get clocks {clk1}]

2.500 [get ports {wraddress[1]}]

55

set input delay -add delay

min -clock [get clocks {clk1}]

1.000 [get ports {wraddress[1]}]

set input delay -add delay

max -clock [get clocks {clk1}]

2.500 [get ports {wraddress[2]}]

set input delay -add delay

min -clock [get clocks {clk1}]

1.000 [get ports {wraddress[2]}]

58

set input delay -add delay

-max -clock [get clocks {clk1}]

2.500 [get ports {wraddress[3]}]

59

set input delay -add delay

-min -clock [get clocks {clk1}]

1.000 [get ports {wraddress[3]}]

set input delay -add delay -max -clock [get clocks {clk1}]

2.500 [get ports {wren}]

61

set input delay -add delay

-min -clock [get clocks {clk1}]

1.000 [get ports {wren}]

62

set input delay -add delay

-max -clock [get clocks {clk1}]

2.500 [get ports {rdaddress[4]}]

set input delay -add delay

1.000 [get ports {rdaddress[4]}]

63

-min -clock [get clocks {clk1}]

set input delay -add delay

-max -clock [get clocks {clk1}]

2.500 [get ports {wraddress[4]}]

set input delay -add delay

-min -clock [get clocks {clk1}]

1.000 [get ports {wraddress[4]}]

set input delay -add delay -max -clock [get clocks {clk1}]

2.500 [get ports {rdaddress[0]}]

set input delay -add delay

1.000 [get ports {rdaddress[0]}]

-min -clock [get clocks {clk1}]

For Help, press F1

Ln 41, Col 9

```

Place cursor over command to see tooltip

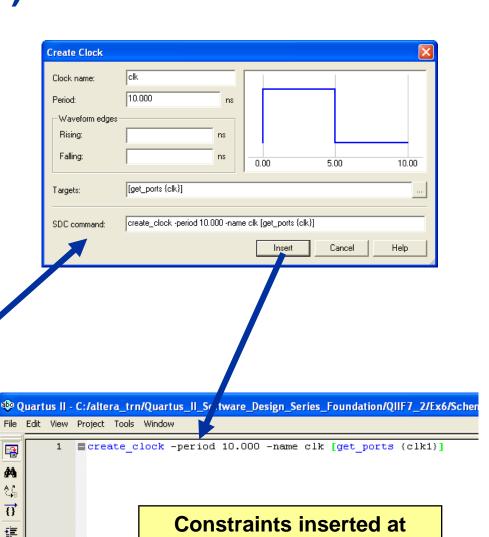

#### **SDC File Editor (cont.)**

Construct an SDC file using TimeQuest graphical constraint creation tools

cursor location

© 2010 Altera Corporation—Confidential

+=

#### **SDC Templates**

Quickly add customized constraint templates

© 2010 Altera Corporation—Confidential

## **Basic Steps to Using TimeQuest TA**

- Generate timing netlist

- Enter SDC constraints

- a. Create and/or read in SDC file (recommended method)

#### or

- b. Constrain design directly in console

- 3. Update timing netlist

- Generate timing reports

- Save timing constraints (optional)

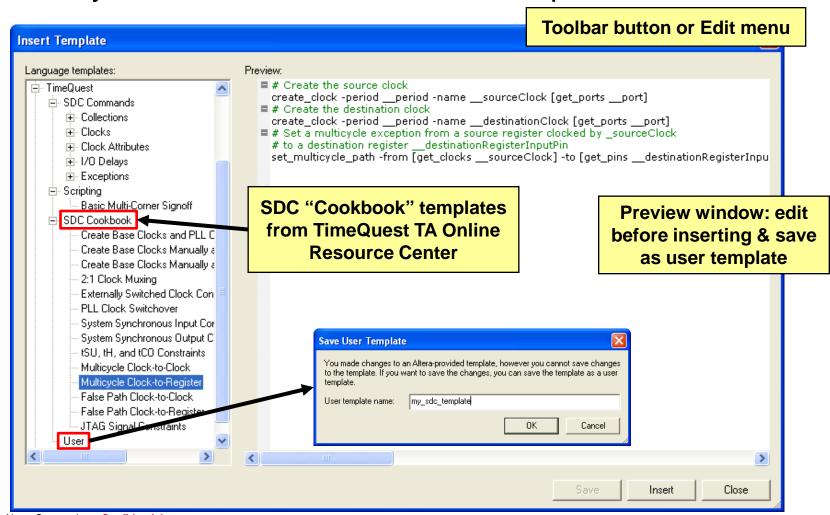

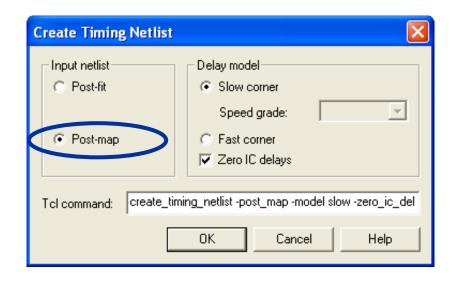

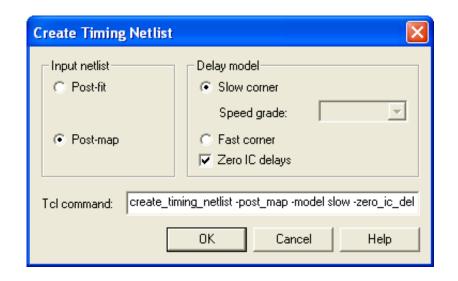

## 1) Generate Timing Netlist

- Create a timing netlist (i.e. database) based on compilation results

- Post-synthesis (mapping) or post-fit (if design already fully compiled)

- Worst-case (slow; maximum operating temperature), best-case (fast; minimum operating temperature) timing models

- Set custom operating conditions (65 nm technology devices; military; industrial, etc.)

- To execute:

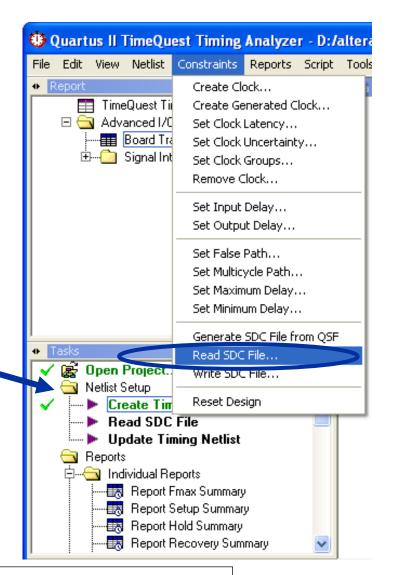

## 2a) Create or Read in SDC File

- Create SDC file using SDC file editor

- Don't enter constraints using Constraints menu

- Read in constraints & exceptions from existing SDC file and/or HDL

- -hdl: looks for ALTERA\_ATTRIBUTE embedded in HDL first before reading SDC files

- Execution

- Read SDC File (Tasks pane or Constraints menu)

- File precedence (if no filename specified)

- Files specifically added to Quartus II project

- <current\_revision>.sdc (if it exists in project directory)

## 2b) Constrain Directly in Console

- Apply new constraints directly to netlist with console SDC commands or from the Constraints menu

- Not automatically added to SDC file

- Not needed if all constraints in SDC file

- Use remove\_<command> to remove applied constraints

- Only remove\_clock is in GUI

Recommend using SDC file (step 2a) instead to ease management and storage of constraints

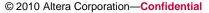

## **Using GUI to Enter Constraints Directly**

- Most common constraints can be accessed from the Constraints menu

- Same as Edit menu ⇒ Insert Constraints in SDC file editor

- Use if unfamiliar with SDC syntax

© 2010 Altera Corporation—Confidential

## **Constraining**

- User MUST enter constraints for all paths to <u>fully</u> analyze design

- Timing analyzer only performs slack analysis on constrained design paths

- Constraints guide the fitter to place & route design in order to meet timing requirements

- Recommendation: Constrain all paths (at least clocks & I/O)

- Not as difficult a task as it may sound

- Wildcards

- Single, generalized constraints cover many paths, even all paths in an entire clock domain

## 3) Update Timing Netlist

- Apply SDC constraints/exceptions to current timing netlist

- Generates warnings

- Undefined clocks

- Partially defined I/O delays

- Combinational loops

- Update timing netlist after adding any new constraint

- Execution

- Update Timing Netlist (Tasks pane or Netlist menu)

Tcl: update\_timing\_netlist

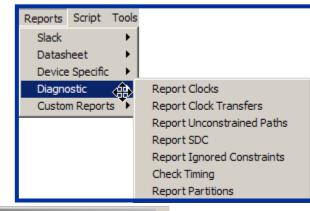

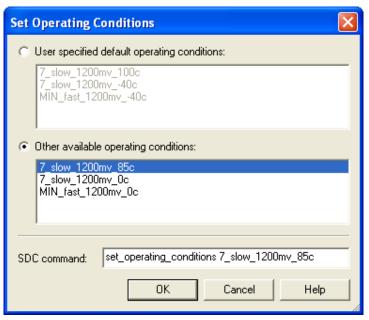

## 4) Generate Timing Reports

- Verify timing requirements and locate violations

- Check for fully constrained design or ignored timing constraints

- Two methods

- Tasks pane

- Shortcut: Automatically creates/updates netlist & reads default SDC file if needed

- Reports menu

- Must have valid netlist to access

Double-click to create individual report

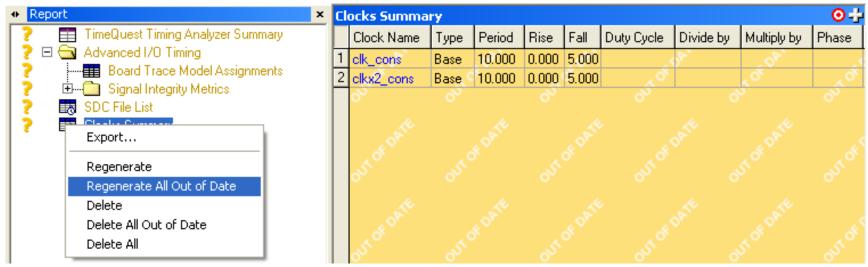

#### "Out of Date" Reports

- Adding new constraints interactively in console causes current reports to be "out of date"

- Update timing netlist & regenerate reports (Report pane right-click menu)

- No such warning when using SDC file

#### **Reset Design Command**

- Tasks pane or Constraints menu

- Flushes <u>all</u> timing constraints from current timing netlist

- Functional Tcl equivalent: delete\_timing\_netlistcommand followed by create\_timing\_netlist

#### Uses

- "Re-starting" timing analysis on same timing netlist applying different constraints or SDC file

- Starting analysis over if results seem to be unexpected

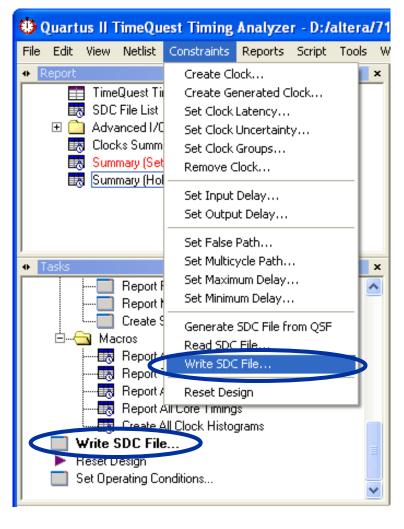

## 5) Save Timing Constraints (Optional)

#### write\_sdc command

- Saves all constraints & exceptions applied to current netlist into SDC file

- Use if constraints added during TimeQuest session in console instead of SDC file

#### Notes

- SDC files generated by TimeQuest TA only if requested

- Use -expand option (not in GUI) to convert Altera-specific SDC commands (discussed later) into standard SDC

- Run report\_sdc command (console, Tasks pane, or Report menu) to see what will get written to SDC file

# **Basic Steps to Using TimeQuest TA (Review)**

- Generate timing netlist

- Enter SDC constraints

- a. Create and/or read in SDC file (recommended method)

#### or

- b. Constrain design directly in console

- 3. Update timing netlist

- Generate timing reports

- Save timing constraints (optional)

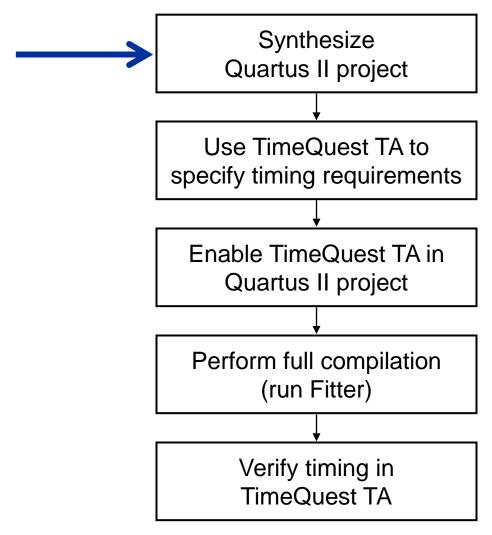

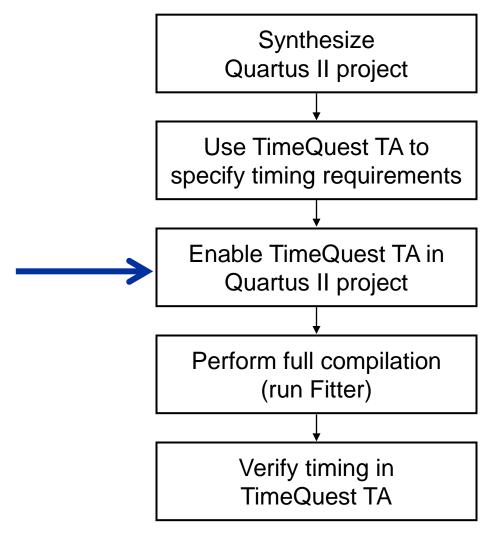

#### **Using TimeQuest TA in Quartus II Flow**

# **Timing Requirements: Create Post-Map Netlist**

- Follow TimeQuest flow

- Use -post\_map argument for synthesis (mapping) only netlist

- If design already fully compiled, choose-post\_fit (default)

- Tasks list command defaults to post-fit, so must use

Netlist menu in GUI

- Zero IC delays auto-enabled with Post-map

- Assumes no interconnect delays to determine if it will be possible to meet timing

#### **Using TimeQuest TA in Quartus II Flow**

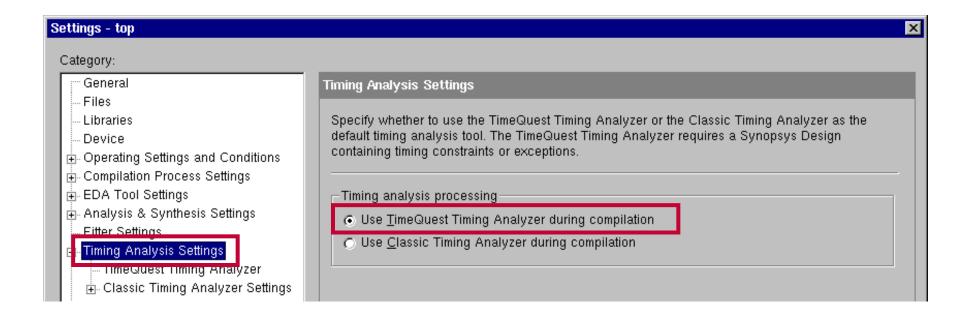

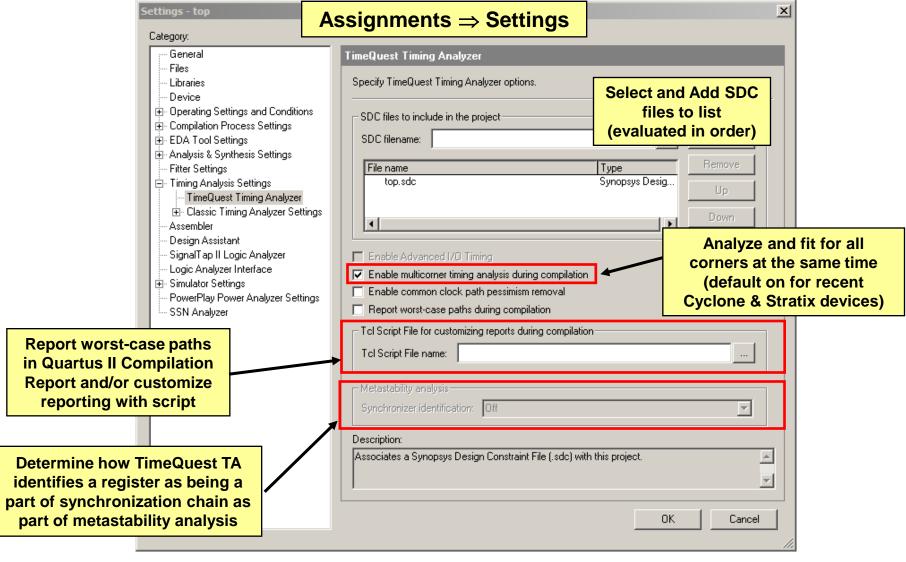

## **Enable TimeQuest TA in Quartus II Software**

- Tells the Quartus II software to use SDC constraints during fitting

- File order precedence

- Any SDC files manually added to Quartus II project (in order)

- current\_revision>.SDC located in project directory

## **Enabling TimeQuest in Quartus II Software**

#### Notes:

- Arria<sup>®</sup> GX and newer devices only support Timequest TA.

- TimeQuest TA is enabled by default for new Stratix® III and Cyclone® III designs.

## **Quartus II TimeQuest Settings**

© 2010 Altera Corporation—Confidential

Note: Advanced I/O Timing & Common Clock Path Pessimism

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, MOSSELSSENTIA LOT Reg. U.S. Pat. & Tm. Off. and Altera marks in and outside the U.S.

## **Using TimeQuest TA in Quartus II Flow**

## **Verifying Timing Requirements**

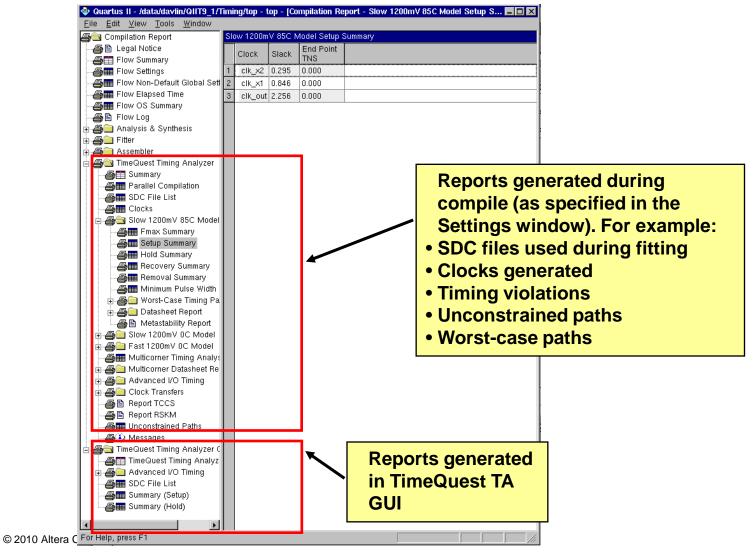

- View TimeQuest summary information directly in Quartus

II Compilation Report

- Open TimeQuest TA for more thorough analysis

- Follow TimeQuest flow, selecting Post-fit netlist

- Optional: Enable Zero IC Delays to see if there is any chance of meeting timing without having to enable optimization options

- Run TimeQuest easy-to-use reporting capabilities (Tasks pane)

- Many different reporting options available

- Place Tcl reporting commands into script file

- Easy repetition

- Verify whether Fitter was able to meet timing requirements

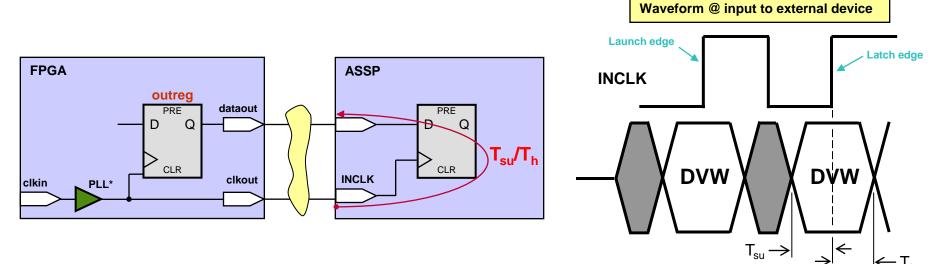

## **TimeQuest Reports in Compilation Report**

# **Quartus® II Software Design Series: Timing Analysis**

Timing Analysis Basics

# **Timing Analysis Basics**

- Launch vs. latch edges

- Setup & hold times

- Data & clock arrival time

- Data required time

- Setup & hold slack analysis

- I/O analysis

- Recovery & removal

- Timing models

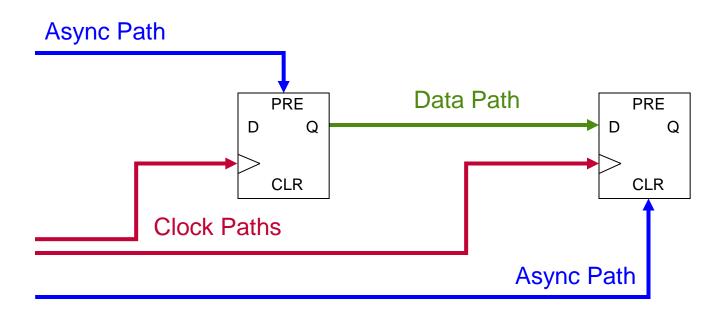

## Path & Analysis Types

#### Three types of Paths:

- Clock Paths

- Data Path

- 3. Asynchronous Paths\*

#### Two types of Analysis:

- 1. Synchronous clock & data paths

- Asynchronous\* clock & async paths

<sup>\*</sup>Asynchronous refers to signals feeding the asynchronous control ports of the registers

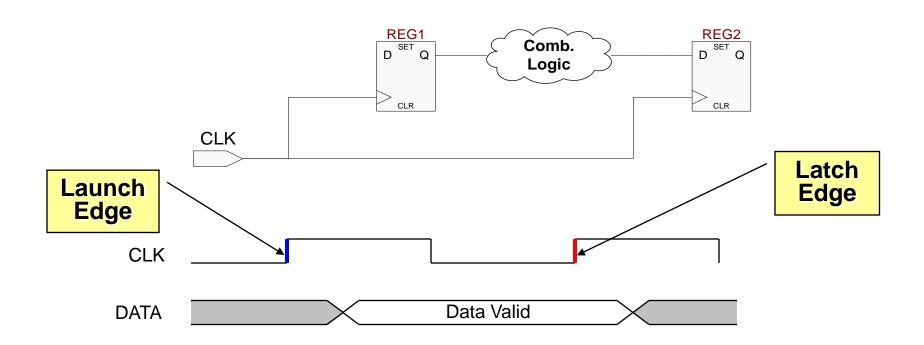

## Launch & Latch Edges

Launch Edge: the edge which "launches" the data from source register

the edge which "latches" the data at destination register (with respect to the launch edge, selected by timing analyzer; typically 1 cycle) Latch Edge:

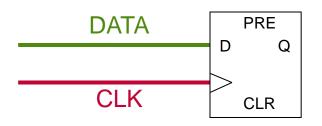

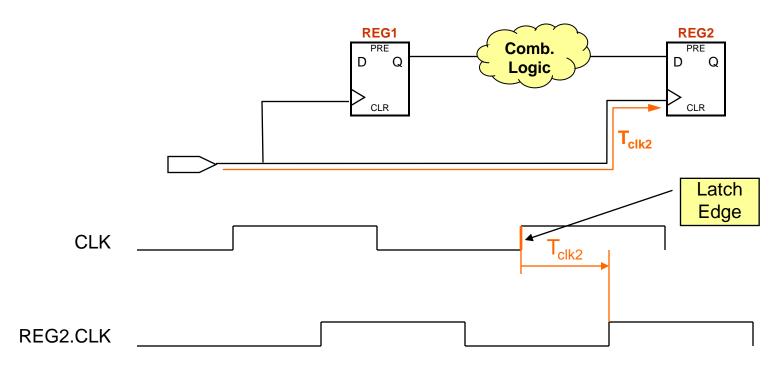

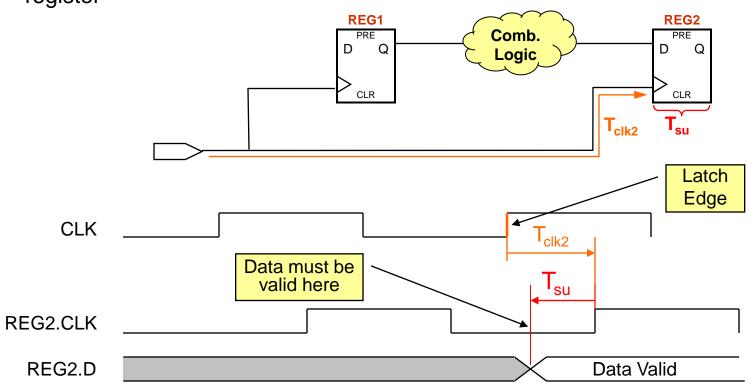

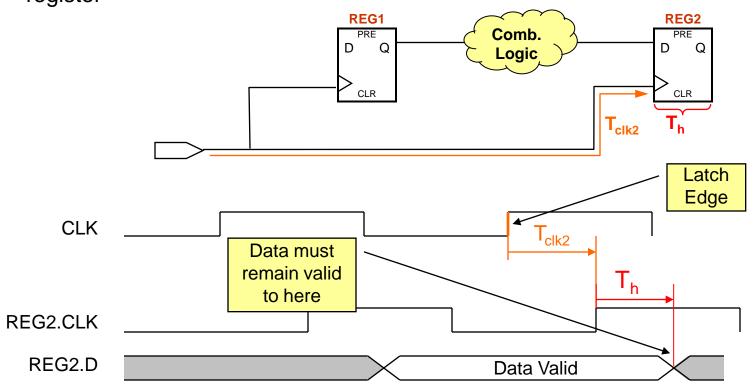

## **Setup & Hold**

Setup: The minimum time data signal must be stable

BEFORE clock edge

Hold: The minimum time data signal must be stable

AFTER clock edge

Together, the setup time and hold time form a Data Required Window, the time around a clock edge in which data must be stable.

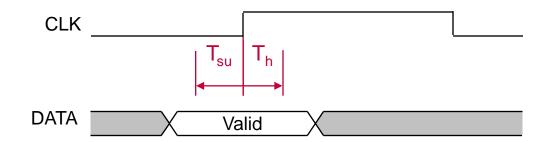

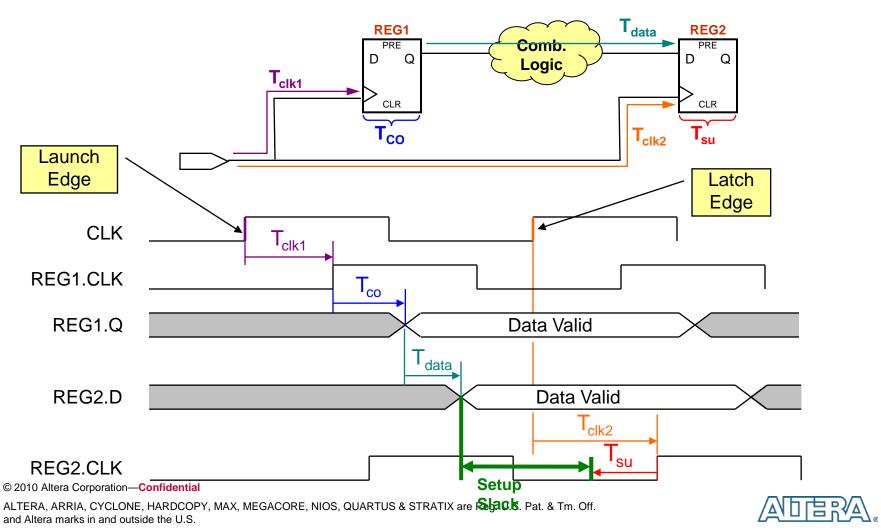

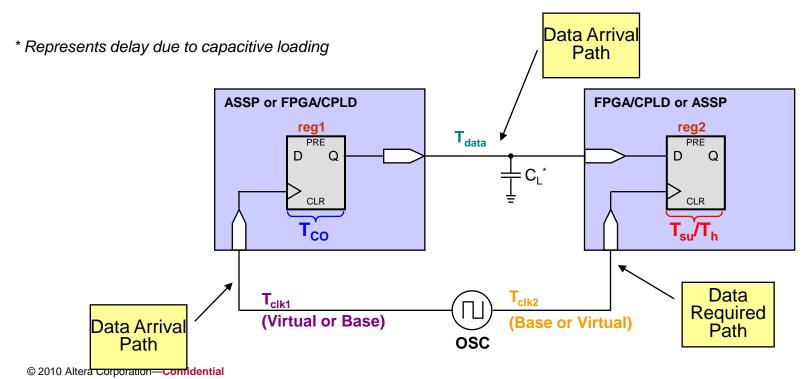

## **Data Arrival Time**

The time for data to arrive at destination register's D input

Data Arrival Time = launch edge +  $T_{clk1}$  +  $T_{co}$  +  $T_{data}$

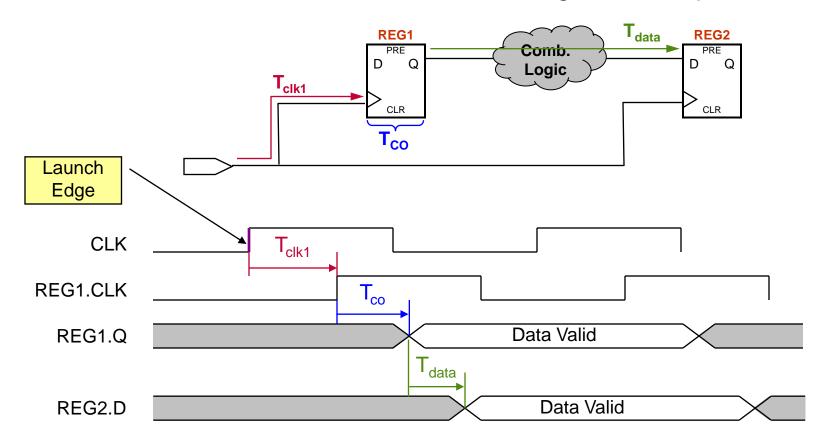

## **Clock Arrival Time**

The time for clock to arrive at destination register's clock input

Clock Arrival Time = latch edge + T<sub>clk2</sub>

## **Data Required Time - Setup**

The minimum time required for the data to get latched into the destination register

Data Required Time = Clock Arrival Time - T<sub>su</sub> - Setup Uncertainty

# **Data Required Time - Hold**

The minimum time required for the data to get latched into the destination register

Data Required Time = Clock Arrival Time + T<sub>h</sub> + Hold Uncertainty

# **Setup Slack**

The margin by which the setup timing requirement is met. It ensures launched data arrives in time to meet the latching requirement.

# Setup Slack (cont'd)

Setup Slack = Data Required Time (Setup)

- Data Arrival Time

#### Positive slack

Timing requirement met

### Negative slack

Timing requirement not met

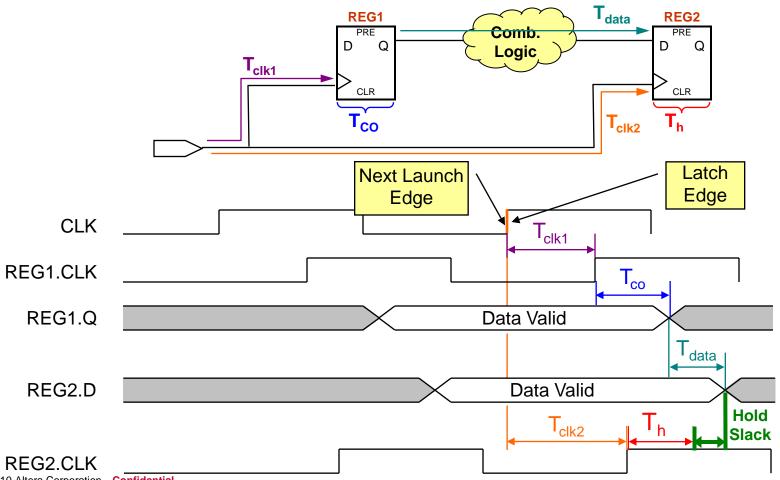

## **Hold Slack**

The margin by which the hold timing requirement is met. It ensures latch data is not corrupted by data from another launch edge. It also prevents "double-clocking".

© 2010 Altera Corporation—Confidential

## Hold Slack (cont'd)

## Hold Slack = Data Arrival Time

Data Required Time (Hold)

#### Positive slack

Timing requirement met

### Negative slack

Timing requirement not met

# I/O Analysis (Common Clock Source)

- Analyzing I/O performance in a synchronous design uses the same slack equations

- Must include external device & PCB timing parameters

- Recommend use virtual clock for specifying input/output delays

- Otherwise, can be difficult to accurately constrain I/Os

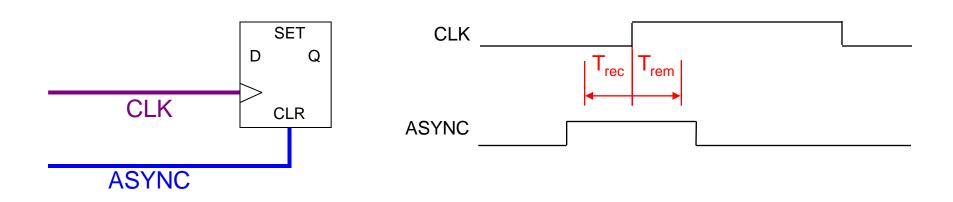

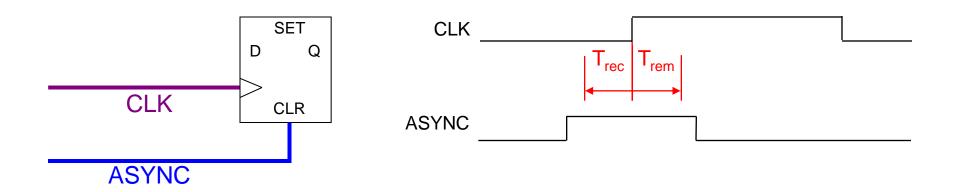

## **Recovery & Removal**

Recovery: The minimum time an asynchronous signal can be

de-asserted BEFORE clock edge

Removal: The minimum time an asynchronous signal can be

de-asserted AFTER clock edge

## **Asynchronous = Synchronous?**

- Asynchronous control signal source is assumed synchronous

- Slack equations still apply

- data arrival path = asynchronous control path

- $T_{su} \approx T_{rec}$ ;  $T_h \approx T_{rem}$

- External device & board timing parameters may be needed (Ex. 1)

Example 1

Example 2

© 2010 Altera Corporation—Confidential

# Why Are These Calculations Important?

- Calculations are important when timing violations occur

- Need to be able to understand cause of violation

## Example causes

- Data path too long

- Requirement too short (incorrect analysis)

- Large clock skew signifying a gated clock, etc.

# TimeQuest timing analyzer uses them

- Equations to calculate slack

- Terminology (launch and latch edges, Data Arrival Path, Data Required Path, etc.) in timing reports

## **Timing Models in Detail**

- Quartus II software models device timing at two PVT conditions by default

- Slow Corner Model

- Indicates slowest possible performance for any single path

- Timing for slowest device at maximum operating temperature and VCC<sub>MIN</sub>

- Fast Corner Model

- Indicates fastest possible performance for any single path

- Timing for fastest device at minimum operating temperature and VCC<sub>MAX</sub>

- Why two corner timing models?

- Ensure setup timing is met in slow model

- Ensure hold timing is met in fast model

- Essential for source synchronous interfaces

- Third model (slow, min. temp.) available only for 65 nm and smaller technology devices (temperature inversion phenomenon)

## **Generating Fast/Slow Netlist**

- Specify one of the default timing models to be used when creating your netlist

- Default is the slow timing netlist

- To specify fast timing netlist

- Use -fast\_model option with create\_timing\_netlist command

- Choose Fast corner in GUI when executing Create Timing Netlist from Netlist menu

- CANNOT select fast corner from Tasks Pane

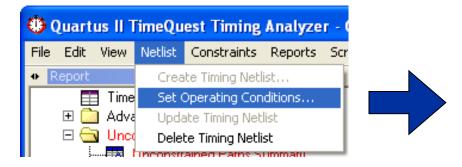

## **Specifying Operating Conditions**

- Perform timing analysis for different delay models without recreating the existing timing netlist

- Takes precedence over already generated netlist

- Required for selecting slow, min. temp. model and other models (industrial, military, etc.) depending on device

Use get\_available\_operating\_conditions to see available

conditions for target device

# Please go to Exercise 1

# **Quartus® II Software Design Series: Timing Analysis**

Timing Reports

## **Timing Reports**

- Timing results available in both the Quartus II Compilation Report and TimeQuest GUI

- TimeQuest TA includes more extensive reporting capabilities

- Create reports while creating constraints (postmap netlist) before fitting to see if design can meet timing requirements

- Create reports after fitting (post-fit netlist) to verify that placed & routed design meets timing requirements

## **Summary Reports**

- Simplest, most common type of timing report

- Each row reports on a clock domain in the design

- Worst case (positive or negative slack) listed first

- If negative, total negative slack (TNS) on all edges in clock domain

- Command: create\_timing\_summary

- setup, -hold, -recovery, -removal: create report for selected analysis type

## **Detailed Slack/Path Analysis**

- Create more specific/detailed reports

- Ex. Details on a specific clock domain

- Ex. View timing paths between particular I/O & registers

- Create using Tcl commands or GUI

- Use GUI to see report immediately

- Use Tcl file for repeatability

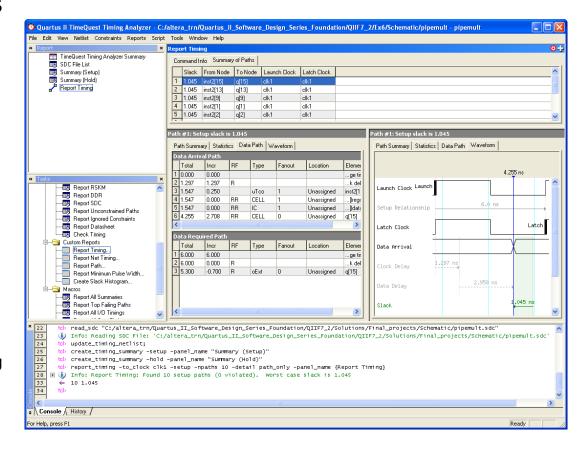

## **Advanced Reporting: Report Timing**

```

report timing

-from <source nodes>

-from clock <source clock names>

-rise from clock <source clock names>

-fall from clock <source clock names>

-through <thru node>

-to <destination nodes>

-to clock <destination clock names>

-rise to clock <destination clock names>

-fall to clock <destination clock names>

-setup | -hold | -recovery | -removal

-detail <summary/path_only/path_and_clock/full_path>

-file <file name>

-append

-panel name < report name >

-stdout

-less than slack <slack limit>

-npaths <# of paths to display>

-nworst <max # of paths per endpoint>

-false path

-pairs only

-show routing

```

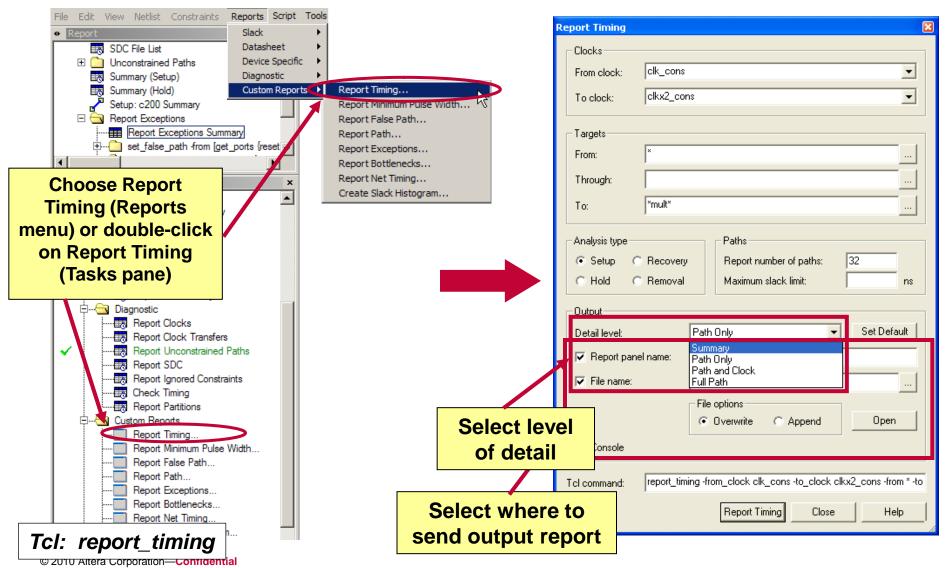

## report\_timing Arguments

- -setup|hold|recovery|removal are mutually exclusive

- Default is -setup

- -detail <option> how to report clock path detail

- path\_only: lumps clock network delay together (default option)

- summary: lists individual path (condense path report)

- path\_and\_clock: shows clock network delay in detail

- full\_path: shows clock network in more detail, particularly generated clock

- -npaths: number of paths to report; defaults to 10

## **Report Timing (GUI)**

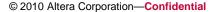

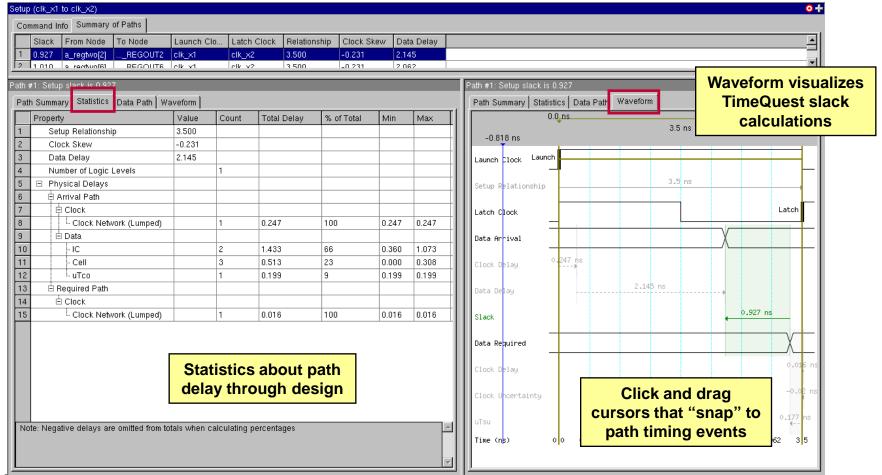

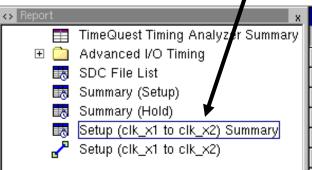

## **Summary Slack/Path Report**

```

report_timing -from_clock clk_x1 -to_clock clk_x2 \

-setup -npaths 10 -detail summary \

-panel_name "Setup (clk_x1 to clk_x2) Summary"

```

| Set | Setup (clk_x1 to clk_x2) Summary |             |                   |              |             |              |            |            |  |

|-----|----------------------------------|-------------|-------------------|--------------|-------------|--------------|------------|------------|--|

|     | Slack                            | From Node   | To Node           | Launch Clock | Latch Clock | Relationship | Clock Skew | Data Delay |  |

| 1   | 0.927                            | a_regtwo[2] | ABLEDATAA_REGOUT2 | clk_x1       | clk_x2      | 3.500        | -0.231     | 2.145      |  |

| 2   | 1.010                            | a_regtwo[6] | ABLEDATAA_REGOUT6 | clk_x1       | clk_x2      | 3.500        | -0.231     | 2.062      |  |

| 3   | 1.015                            | a_regtwo[3] | ABLEDATAA_REGOUT3 | clk_x1       | clk_x2      | 3.500        | -0.231     | 2.057      |  |

| 4   | 1.109                            | a_regtwo[4] | ABLEDATAA_REGOUT4 | clk_x1       | clk_x2      | 3.500        | -0.231     | 1.963      |  |

| 5   | 1.143                            | a_regtwo[0] | ABLEDATAA_REGOUT0 | clk_x1       | clk_x2      | 3.500        | -0.231     | 1.929      |  |

| 6   | 1.148                            | a_regtwo[1] | ABLEDATAA_REGOUT1 | clk_x1       | clk_x2      | 3.500        | -0.231     | 1.924      |  |

| 7   | 1.158                            | a_regtwo[5] | ABLEDATAA_REGOUT5 | clk_x1       | clk_x2      | 3.500        | -0.231     | 1.914      |  |

| 8   | 1.318                            | y_regtwo[4] | ABLEDATAB_REGOUT4 | clk_x1       | clk_x2      | 7.000        | -0.208     | 5.277      |  |

| 9   | 1.347                            | y_regtwo[6] | ABLEDATAB_REGOUT6 | clk_x1       | clk_x2      | 7.000        | -0.208     | 5.248      |  |

| 10  | 1.382                            | y_regtwo[5] | ABLEDATAB_REGOUT5 | clk_x1       | clk_x2      | 7.000        | -0.207     | 5.214      |  |

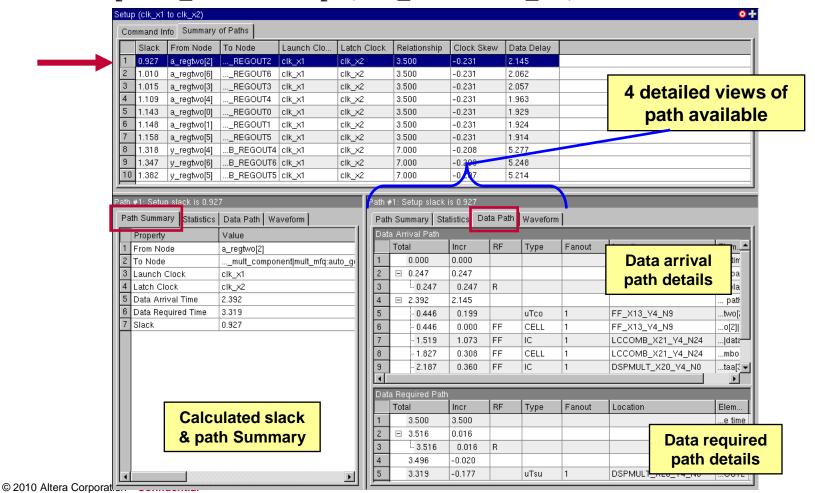

## **Detailed Slack/Path Report**

```

report_timing -from_clock clk_x1 -to_clock clk_x2 \

-setup -npaths 10 -detail path_only \

-panel_name "Setup (clk_x1 to clk_x2)"

```

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat. & Tm. Off.

and Altera marks in and outside the U.S.

#### **Detailed Slack/Path Report (cont.)**

```

report_timing -from_clock c100 -to_clock c200 \

-setup -npaths 10 -detail path_only \

-panel_name "Setup (c100 to c200)"

```

© 2010 Altera Corporation—Confidential

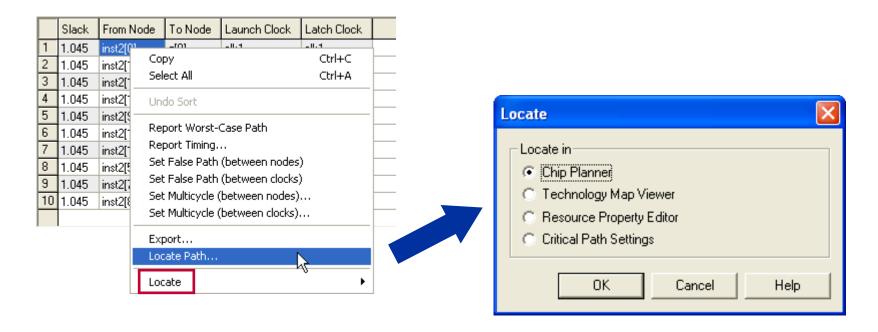

#### **Further Path Analysis**

- Right-click path(s) to cross-probe to other

Quartus II tools or design files

- locate command in Console

# **Quartus® II Software Design Series: Timing Analysis**

Timing Constraints

# Importance of Constraining

- Timing analysis tells how a circuit WILL behave

- Providing timing constraints tells tools how you WANT the design to behave

- Constraints paint picture of how design should operate

- Based on design specs & specs from other devices on PCB

- Provide goals for fitter to target during compilation

- Provide values to which to compare timing results

- TimeQuest TA performs limited analysis without timing constraints

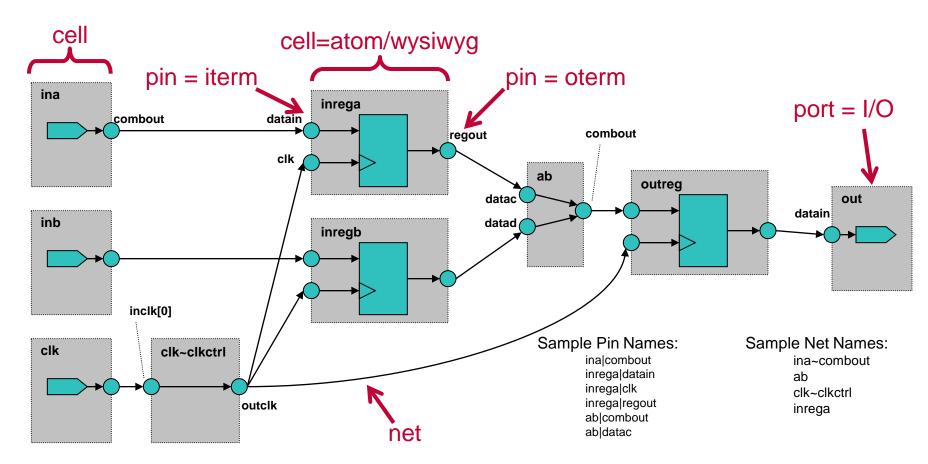

# **SDC Netlist Terminology**

| Term | Definition                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------|

| Cell | Device building blocks (e.g. look-up tables, registers, embedded multipliers, memory blocks, I/O elements, PLLs, etc.) |

| Pin  | Input or outputs of cells                                                                                              |

| Net  | Connections between pins                                                                                               |

| Port | Top-level inputs and outputs (e.g. device pins)                                                                        |

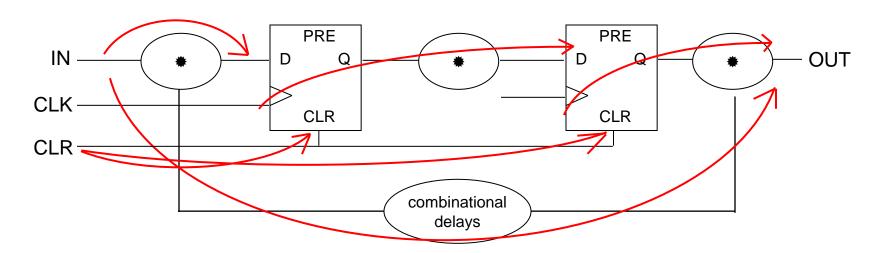

# **SDC Netlist Example**

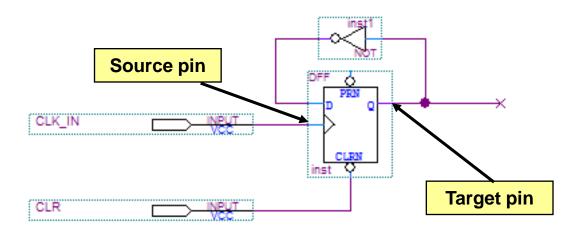

Paths defined in constraints by targeted endpoints (pins or ports)

© 2010 Altera Corporation—Confidential

#### **Collections**

- Searches and returns from the design netlist with a list of names meeting criteria

- Used in SDC commands

- Some collections searched automatically during a command's usage and may not need to be specified

#### Examples

- get\_ports

- get\_pins

- get\_clocks

- all\_clocks

- all\_registers

- all\_inputs

- all\_outputs

See "TimeQuest Timing Analyzer" chapter of the Quartus II Software Handbook (Volume 3) for a complete list & description of each

# **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

#### What are clocks in SDC?

- Defined, repeating signal characteristics applied to a point anywhere in the design

- Internal: applied to a specific node being used as a clock in design (port or pin)

- "Virtual": No real source in, or direct interaction with design

- Example: Clocks on external devices that feed or are fed by the FPGA design, required for I/O analysis

- Name clocks after node to which they are applied or something more meaningful

- Similar to clock settings in older Quartus II timing engine (Classic timing analyzer)

#### Clocks in SDC (cont.)

#### Two types

- Clock

- Absolute or base clock

- Generated clock

- Timing derived from another clock in design

- Must have defined relation with source clock

- Apply to output of logic function that modifies clock input

- PLLs, clock dividers, output clocks, ripple clocks, etc.

# All clocks are related by default

Cross-domain transfers analyzed

#### **Clock Constraints**

- Create clock

- Create generated clock

- PLL clocks

- Automatic clock detection & creation

- Default constraints

- Clock latency

- Clock uncertainty

- Common clock path pessimism removal

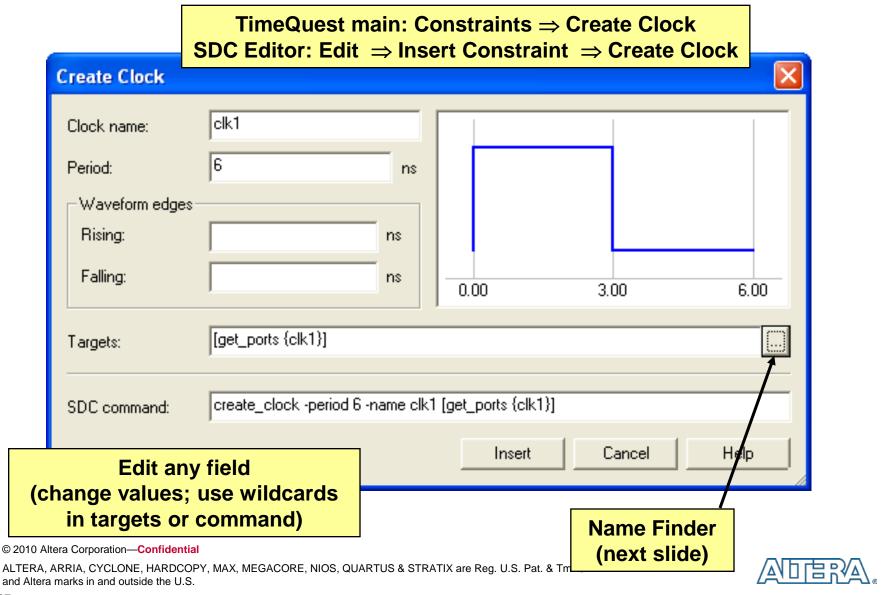

# **Creating a Clock**

- Command: create\_clock

- Options

```

[-name <clock_name>]

-period <time>

[-waveform {<rise_time> <fall_time>}]

[<targets>]

[-add]

```

[] = optional

Note: In general, the more options added to a constraint command, the more specific the constraint is. When options are not specified, the constraint is more generalized and pertains to more of the target.

© 2010 Altera Corporation—Confidential

#### create\_clock Notes

- –name: Assigns name to the clock to be used in other commands & reports when referring to clock

- Optional; defaults to target name if not specified

- -waveform: Indicates clock offset or non-50% duty cycle clocks

- 50% duty cycle is assumed unless otherwise indicated

- -add: Adds clock to node with existing clock

- Without -add, warning given former clock constraint is over written

- <targets>: Target ports or pins for clock setting

- Virtual clock created if no target specified

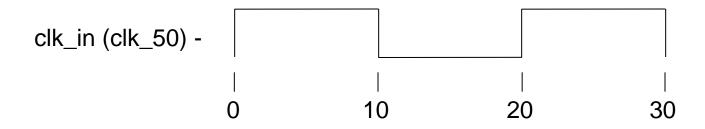

#### create\_clock Examples

create\_clock -period 20.0 -name clk\_50 [get\_ports clk\_in]

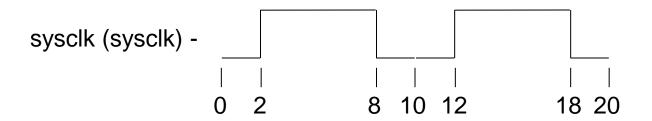

create\_clock -period 10.0 -waveform {2.0 8.0} [get\_ports sysclk]

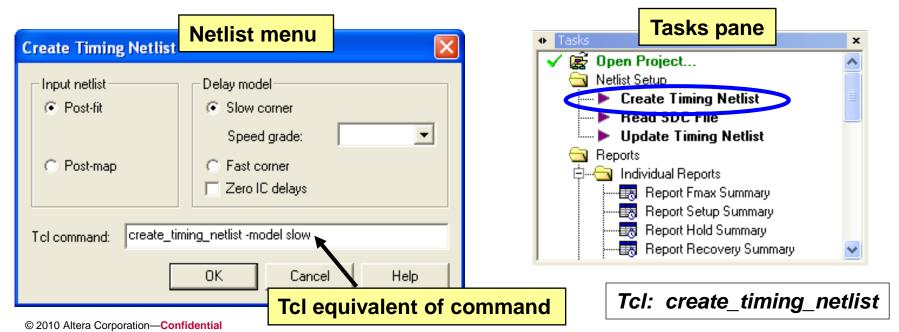

# **Create Clock using GUI**

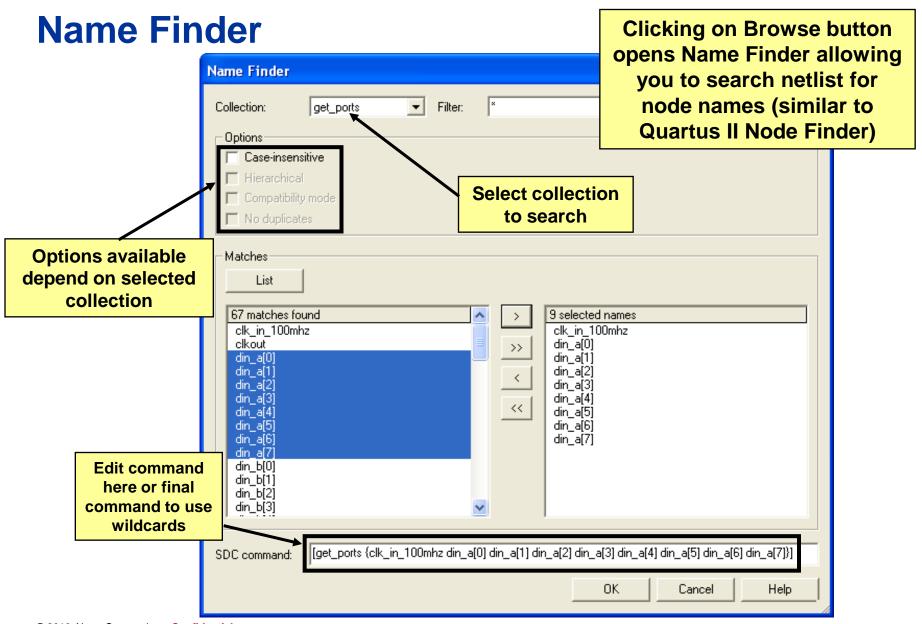

# Name Finder Search Options (FYI)

#### All options off

- Hierarchy levels in Filter match results except for \*

- \* finds all names in all levels of hierarchy in selected collection

- Ex: \* | data\* finds names starting with data at second level only

- Case-insensitive (all collections)

- Names match Filter ignoring capitalization

- Hierarchical (get\_pins; get\_cells collections only)

- Filter must be just cell name or in form of <cell> | <pin>

- Ex: foo | \* finds all pins on cell named foo

- Ex: \* | data\* finds all pins starting with data at any level of hierarchy

- Compatibility mode (get\_pins; get\_cells collections only)

- Always searches entire hierarchy

- Ex: \* | data\* finds all pins starting with data at any level of hierarchy

- Ex: \* | \* | data\* performs the same search; extra \* | not required

#### **Creating a Generated Clock**

- Command: create\_generated\_clock

- Options

```

[-name <clock_name>]

-source <master_pin>

[-master_clock <clock_name>]

[-divide_by <factor>]

[-multiply_by <factor>]

[-duty_cycle <percent>]

[-invert]

[-phase <degrees>]

[-edges <edge_list>]

[-edge_shift <shift_list>]

[<targets>]

[-add]

```

#### create\_generated\_clock Notes

- source: Species the node in design from which generated clock is derived

- Ex. Placing source before vs. after an inverter would yield different results

- -master\_clock: Used if multiple clocks exist at source due to -add option

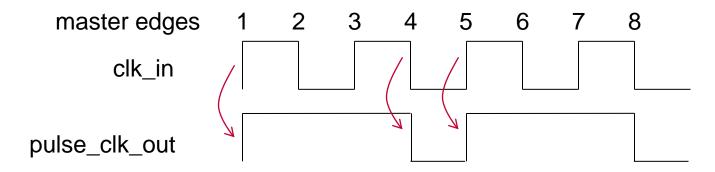

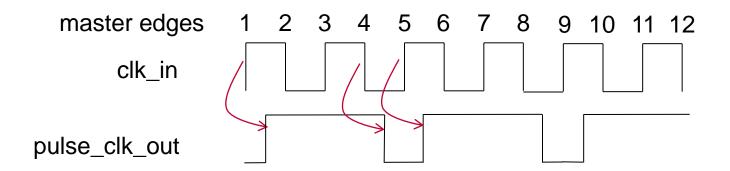

- -edges: Relates rising/falling edges of generated clock to rising/falling edges of source based on numbered edges

- -edge\_shift: Relates edges based on amount of time shifted (requires -edges)

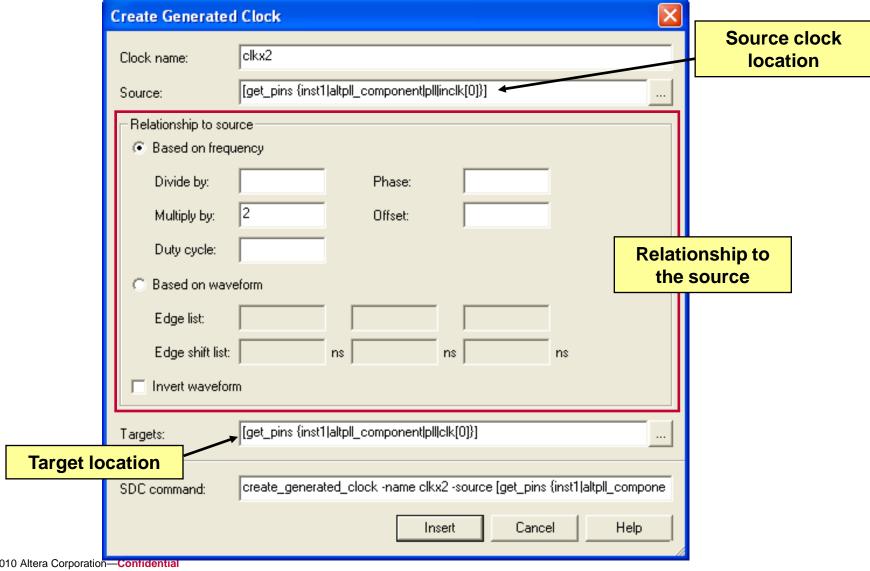

# **Create Generated Clock using GUI**

© 2010 Altera Corporation—Confidential

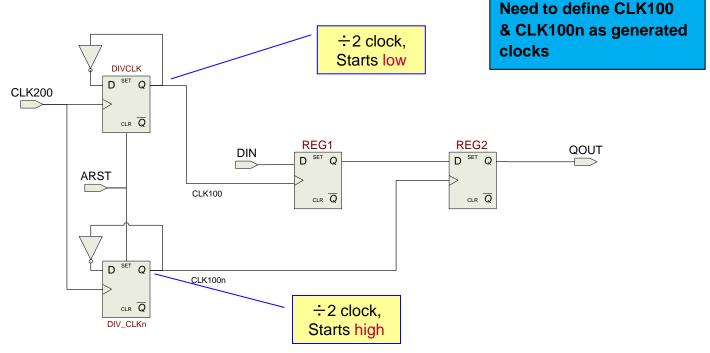

#### **Generated Clock Example 1**

```

create_clock -period 10 [get_ports clk_in]

create_generated_clock -name clk_div \

-source [get_pins inst|clk] \

-divide_by 2 \

[get_pins inst|regout]

```

#### **Generated Clock Example 2**

# **Generated Clock Example 3**

#### **Inverted Clock Example**

```

create_clock -period 5 [get_ports clk200]

create_generated_clock -name clk100 -source [get_pins divclk|clk] \

-divide_by 2 [get_pins divclk|regout]

create_generated_clock -name clk100n -source [get_pins div_clkn|clk] \

-divide_by 2 -invert [get_pins div_clkn|regout]

```

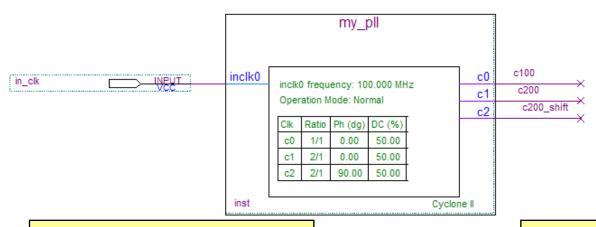

# PLL Clocks (Altera SDC Extension)

- Command: derive\_pll\_clocks

- [-use\_tan\_name]: names clock after design net name from Classic timing analyzer settings instead of the default PLL output SDC pin name

- [-create\_base\_clocks]: generates create\_clock constraint(s) for PLL input clocks

- Create generated clocks on all PLL outputs

- Based on input clock & PLL settings

- Requires defining PLL input as clock unless -create\_base\_clocks is used

- Automatically updates generated clocks on PLL outputs as changes made to PLL design

- write\_sdc -expand expands constraint into standard create\_clock and create\_generated\_clock commands

- Not in GUI; must be entered in SDC manually

#### derive\_pll\_clocks Example

#### **Using generated clock commands**

```

create_clock -period 10.0 [get_ports in_clk]

create_generated_clock -name c100 \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-divide_by 1 \

[get_pins {inst|altpll_component|pll|clk[0]}]

create_generated_clock -name c200 \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-multiply_by 2 \

[get_pins {inst|altpll_component|pll|clk[1]}]

create_generated_clock -name c200_shift \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-multiply_by 2 \

-phase 90 \

[get_pins {inst|altpll_component|pll|clk[2]}]

```

#### Using derive pll command

```

create_clock -period 10.0 \

[get_ports in_clk]

derive_pll_clocks

# or simply:

derive_pll_clocks \

-create_base_clocks

# Note the clock names for

# the generated clocks

# will be the names of

# the PLL output pins

```

#### **Automatic Clock Detection & Creation**

- Command: derive\_clocks

- [-period]: same use as with create\_clock

- [-waveform]: same use as with create\_clock

- No target required

- Automatically create clocks on clock pins in design that don't already have clocks defined

- Does not work with PLL outputs (use derive\_pll\_clocks)

- SDC extension expanded with write\_sdc -expand

- Not in GUI

- Not recommended for final timing sign-off

#### **Default Clock Constraints**

- Remember, all clocks must be constrained to analyze design with timing analysis

- If no clock constraints exist, default constraints created through two commands

```

derive_clocks -period 1.0

derive_pll_clocks

```

Default constraints not applied if at least one clock constraint exists

- Not in GUI

- Not recommended for final timing sign-off

#### **Non-Ideal Clock Constraints**

- So far, all clocks have been ideal

- Nice square waves

- No accounting for delays outside of FPGA

- Add extra constraints to define realistic, non-ideal clocks

- Three special constraints

- set\_clock\_latency

- set\_clock\_uncertainty

- derive\_clock\_uncertainty

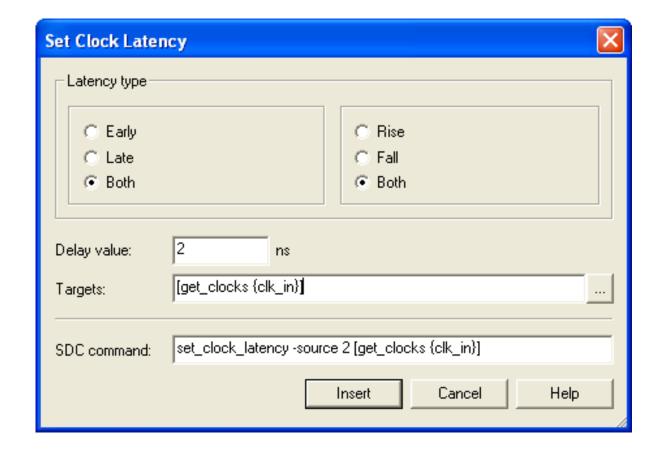

# **Clock Latency**

- Two types of latency

- Source: From clock source to input port (board latency)

- Network: From input port to destination register clock pin

- Network latency handled and understood by timing analysis automatically

- Need to model source latency

- TimeQuest TA knows nothing about delays external to device

- Provide a more realistic picture of external clock behavior

- Example

- External feedback clock: need to specify delay from clock output I/O to clock input I/O

- Clocks created with create\_clock have default source latency of 0

# **Clock Latency (cont.)**

- Command: set\_clock\_latency

- Specify source latency on external path(s) to device

#### Options

```

- -source

```

```

- [-clock <clock_list>]

```

```

- [-early | -late]

```

```

- [-fall | -rise]

```

- <delay>

- <targets>

#### set\_clock\_latency Notes

- -source: required argument for constraint (no options)

- -fall | -rise: latency applied on only falling or rising edge of clock

- -early | -late: latency on shortest/longest external path

- Used by timing analyzer as part of definition of data/clock arrival paths for setup/hold analyses

#### **Clock Latency (GUI)**

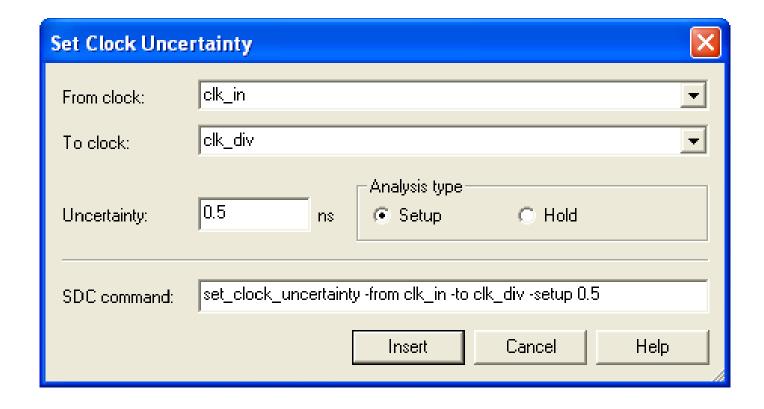

# **Clock Uncertainty**

- Command: set\_clock\_uncertainty

- Use to model jitter, guard band, or skew

- Allows generation of clocks that are non-ideal

#### Options

```

- [-setup | -hold]

- [-fall_from <fall_from_clock>]

- [-fall_to <fall_to_clock>]

- [-from <from_clock>]

- [-rise_from <rise_from_clock>]

- [-rise_to <rise_to_clock>]

- [-to <to_clock>]

- <value>

```

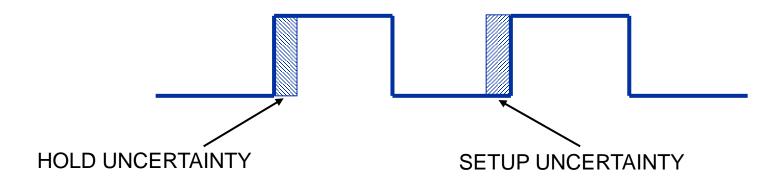

# **Clock Uncertainty**

- Setup uncertainty decreases setup required time

- Hold uncertainty increases hold required time

Ex. To add a 0.5-ns guardband around clock, use 250 ps of setup uncertainty and 250 ps of hold uncertainty.

#### set\_clock\_uncertainty Notes

- -from, -to: uncertainty added to transfers within single clock domain or between different domains

- -fall\_from, -fall\_to, -rise\_from, -rise\_to: apply uncertainty only on rising/falling edges of source/destination clock domain

- Not available in the GUI; add options manually

## **Clock Uncertainty (GUI)**

## **Automatically Derive Uncertainty**

- Command: derive\_clock\_uncertainty

- Automatically derive clock uncertainties in supported devices

- Cyclone III, Stratix II, HardCopy® II, Stratix III, and new devices

- Uncertainties created manually with set\_clock\_uncertainty have higher precedence

- Options

- [-overwrite]: overwrites any existing uncertainty constraints

- [-add]: adds derived uncertainties to existing constraints

- SDC extension expanded with write\_sdc -expand

- Not in GUI

- Use is recommended with supported devices

## **Types of Derived Uncertainties**

- Intra-clock transfers

- Transfers within a single clock domain within FPGA

- Inter-clock transfers

- Transfers between different clock domains within FPGA

- I/O interface clock transfers

- Transfers between an I/O port and internal design registers

- Requires creation of virtual clock (same as base clock)

- Reference clock for set\_input\_delay and set\_output\_delay constraints (described later)

- Timing analyzer derives intra- and inter-clock transfers for I/O if virtual clock not defined

112

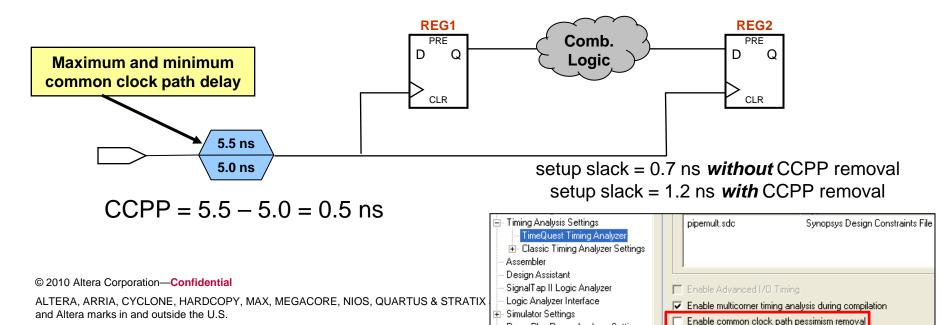

#### Common Clock Path Pessimism Removal

- Remove clock delay pessimism to account for min/max delays on common clock paths (Cyclone III, Stratix III and newer devices)

- Ex: Max delay for data arrival time; min delay for data required time

- Also used to improve minimum required clock pulse widths

- Enable for Fitter and for timing analysis

- TimeQuest Timing Analyzer settings in Quartus II software

- enable\_ccpp\_removal in TimeQuest script or console

- May result in longer compilation time

PowerPlay Power Analyzer Settings

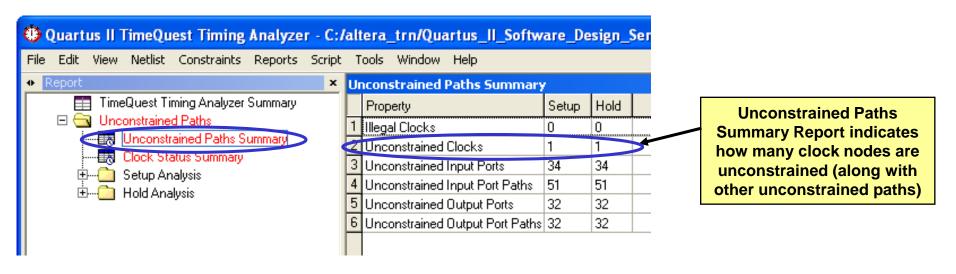

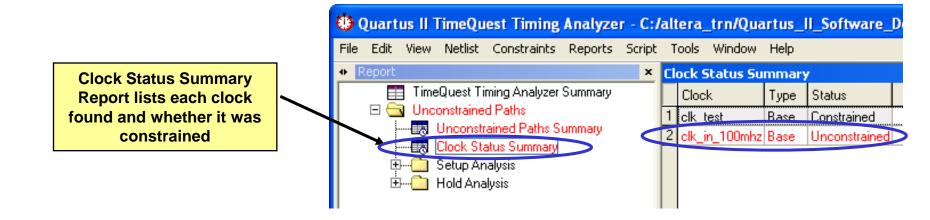

## **Checking Clock Constraints**

Nodes used as clocks but not defined with SDC clock constraint considered unconstrained

#### Solution

- Use Unconstrained Paths Report to find unconstrained clocks

- Quartus II Compilation Report timing summary

- Run report\_ucp command

- Choose Report Unconstrained Paths (Tasks Pane or Reports menu)

- Use Clock Report to verify clocks are constrained correctly

## **Unconstrained Path Report**

## Report Clocks (report\_clocks)

List details about the properties of constrained clocks

Clock properties

| Cl | Clocks Summary   |           |        |            |        |       |            |           |             |       |        |           |            |          |        |                                |                                |

|----|------------------|-----------|--------|------------|--------|-------|------------|-----------|-------------|-------|--------|-----------|------------|----------|--------|--------------------------------|--------------------------------|

|    | Clock Name       | Туре      | Period | Frequency  | Rise   | Fall  | Duty Cycle | Divide by | Multiply by | Phase | Offset | Edge List | Edge Shift | Inverted | Master | Source                         | Targets                        |

| 1  | clk_in           | Base      | 7.000  | 142.86 MHz | 0.000  | 3.500 |            |           |             |       |        |           |            |          |        |                                | {clk_in}                       |

| 2  | clk_in_vir       | Virtual   | 7.000  | 142.86 MHz | 0.000  | 3.500 |            |           |             |       |        |           |            |          |        |                                | {}                             |

| 3  | clk_o            | Generated | 7.000  | 142.86 MHz | -0.899 | 2.601 |            | 1         | 1           | -46.3 |        |           |            | false    | clk_in | t auto_generated pl 1 inclk[0] | t auto_generated pll1 clk[2] } |

| 4  |                  | Generated | 7.000  | 142.86 MHz | 6.101  | 9.601 |            | 1         | 1           |       |        |           |            | false    | clk_o  | nt auto_generated pll1 clk[2]  | { clkout }                     |

| 5  | clk_x1           | Generated | 7.000  | 142.86 MHz | 0.000  | 3.500 |            | 1         | 1           |       |        |           |            | false    | clk_in | t auto_generated pl 1 inclk[0] | t auto_generated pll1 clk[0] } |

| 6  | clk_x1<br>clk_x2 | Generated | 3.500  | 285.71 MHz | 0.000  | 1.750 |            | 1         | 2           |       |        |           |            | false    | clk_in | t auto_generated pll1 inclk[0] | t auto_generated pll1 clk[1]}  |

Clock names (-name argument or default name)

# Please go to Exercise 2

# **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

#### **I/O Constraints**

- Combinational I/O interface

- Synchronous I/O interface

- Source synchronous interface

#### **Combinational Interface**

- All paths from IN to OUT need to be constrained

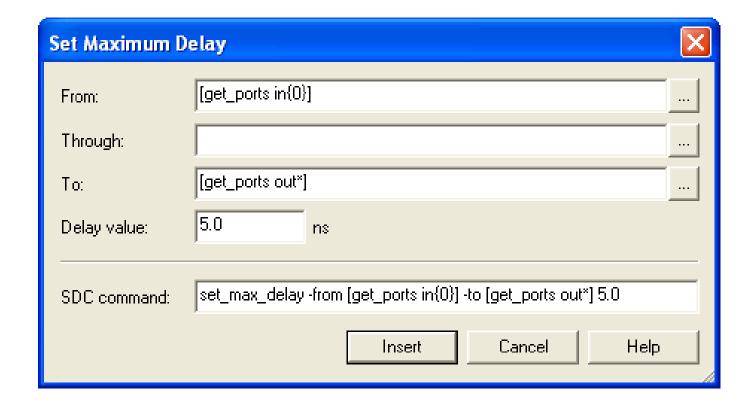

- Use set\_max\_delay & set\_min\_delay commands

- Specify an absolute maximum & minimum delay between points

## Options

[-from < names>]

[-to < names>]

[-through]

<delay>

### set\_max\_delay & set\_min\_delay Notes

- -from & -to: Use to indicate source & destination nodes for constraints

- -through: Use to indicate the constraint should only be applied to path(s) going through a particular node name

### set\_max\_delay & set\_min\_delay (GUI)

## **Combinational Interface Example**

```

set_max_delay -from [get_ports in1] -to [get_ports out*] 5.0

set_max_delay -from [get_ports in2] -to [get_ports out*] 7.5

set_max_delay -from [get_ports in3] -to [get_ports out*] 9.0

set_min_delay -from [get_ports in1] -to [get_ports out*] 1.0

set_min_delay -from [get_ports in2] -to [get_ports out*] 2.0

set_min_delay -from [get_ports in3] -to [get_ports out*] 3.0

```

# I/O Timing – FPGA-Centric vs. System-Centric

- To specify I/O timing, we must decide whether we want to look at the I/O timing FPGA-centric or system-centric

- FPGA-centric means we determine what chip-level T<sub>SU</sub>, T<sub>H</sub>, T<sub>CO</sub> specs we need to meet

- Useful when FPGA may end up in a variety of environments or interacts with defined bus interface (e.g. PCI)

- System-centric means we take into account specs of specific surrounding chips, board delays, chip-to-chip skews

- Can specify some interfaces FPGA-centric and others system-centric

- Concentrate on system-centric in the class.

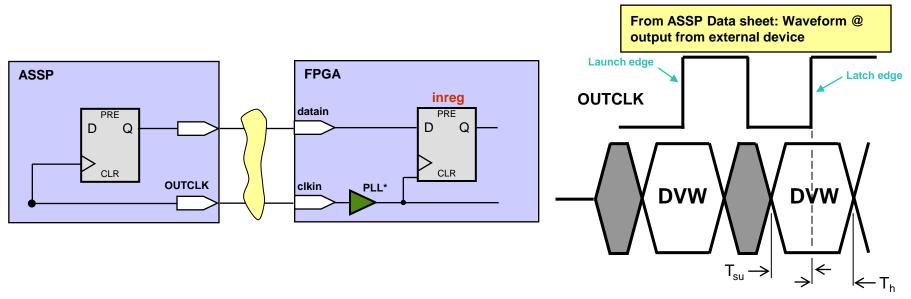

# I/O Timing – Virtual Clocks

- Recommended to use virtual clocks for specifying input / output delays

- Separate clock to represent external clock timing allows derive\_clock\_uncertainty to calculate correctly

- Easier to identify input / output paths in timing reports by virtual clocks at launch or latch edge

- In some cases (e.g. DDR), difficult to accurately constrain I/O without using virtual clocks

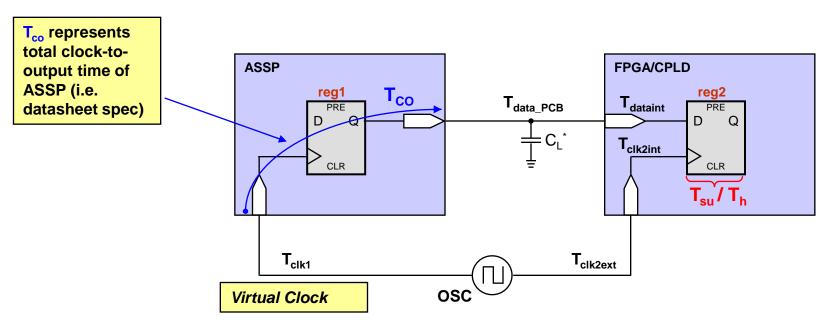

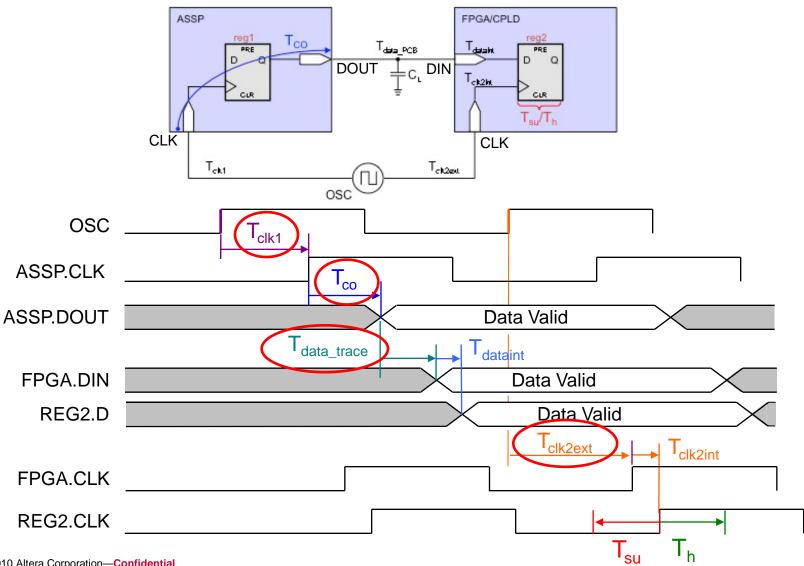

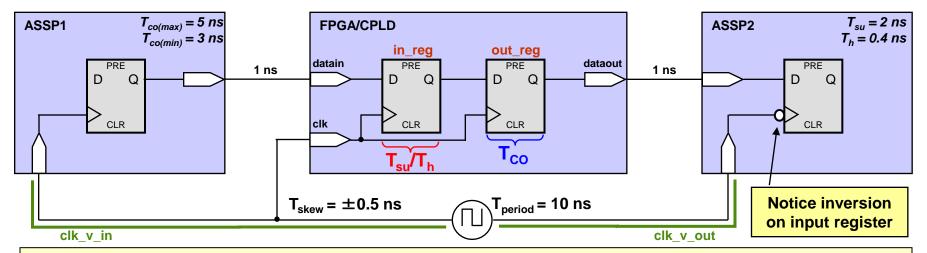

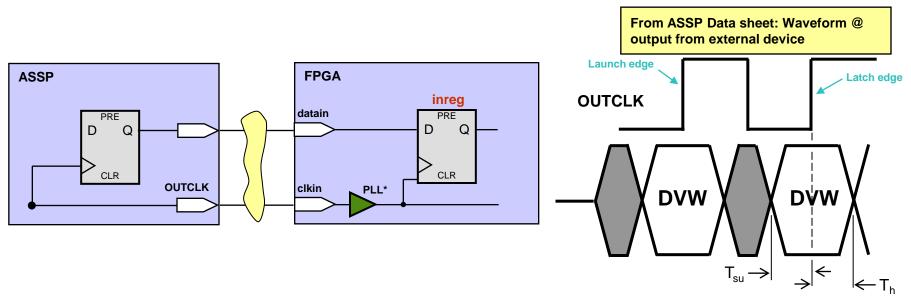

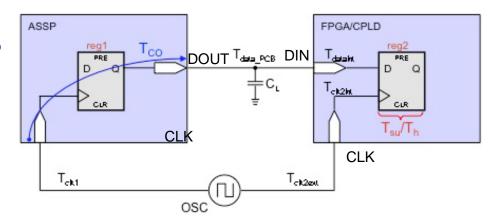

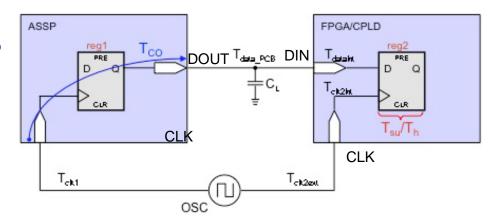

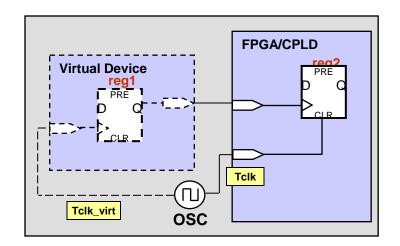

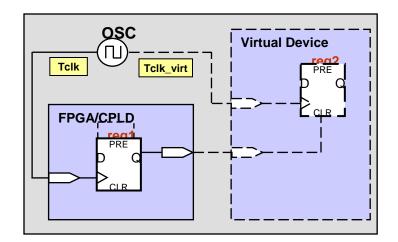

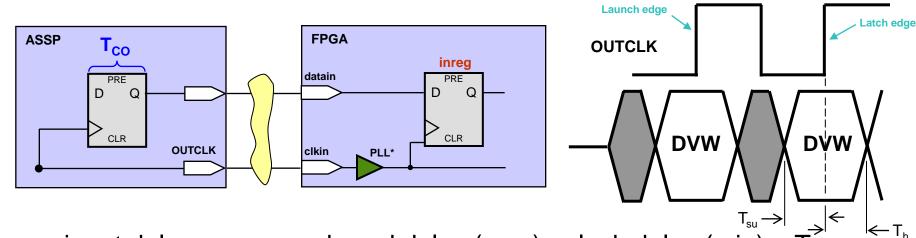

# **Synchronous Inputs**

Need to specify timing relationship from ASSP to FPGA/CPLD to guarantee setup/hold in FPGA/CPLD

<sup>\*</sup> Represents delay due to capacitive loading

## **Synchronous Inputs**

© 2010 Altera Corporation—Confidential

## **Constraining Synchronous Inputs**

- Use set\_input\_delay (-max option) command to constrain input setup time (maximum time to arrive and still meet T<sub>su</sub>)

- Calculated input delay value represents all delays external to device

#### System-centric:

input delay max = Data trace (max) – Board clock skew (min) +

$$T_{co(max)}$$

=  $(T_{data\_PCB(max)} + T_{CL}) - (T_{clk2ext(min)} - T_{clk1(max)}) + T_{co(max)}$

#### FPGA-centric:

input delay max =

$$(T_{launch} - T_{latch}) - T_{SU}$$

- Use set\_input\_delay (-min option) command to constrain input hold time (minimum time to stay active and still meet T<sub>h</sub>)

- Calculated input delay value represents all delays external to device

#### System-centric:

input delay min = Data trace (min) - Board clock skew (max) +

$$T_{co(min)}$$

=  $(T_{data\_PCB(min)} + T_{CL}) - (T_{clk2ext(max)} - T_{clk1(min)}) + T_{co(min)}$

#### FPGA-centric:

input delay min  $= T_h$

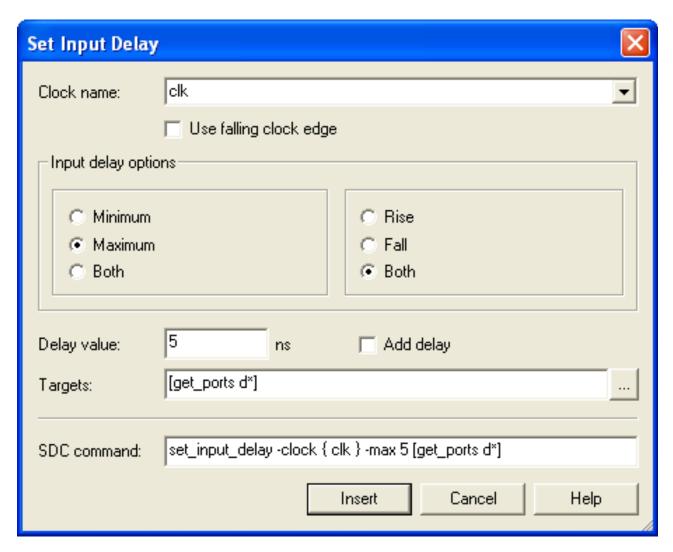

### set\_input\_delay Command

Constrains input pins by specifying external device timing parameters

## Options

```

-clock <clock_name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-source_latency_included]

<delay value>

<targets>

```

### set\_input\_delay Notes

- -clock: Specifies the clock driving the source (external) register

- Use the virtual clock

- Used to determine launch edge vs. latch edge relationship

- -clock\_fall: Use to specify input signal was launched by a falling edge clock transition

- -rise | -fall: Use to indicate whether input delay value is for a rising or falling edge transaction

- To fully constrain, must specify both -max & -min

- Each will default to the value of the other setting if only one assigned (same with rise/fall)

- Warning message if one or the other not specified

### set\_input\_delay Notes

- -add\_delay: Use to specify multiple constraints on single input

- Only one <u>set</u> of max/min & rise/fall constraints allowed on an input pin

- -source\_latency\_included: input delay value specified includes clock source latency normally added automatically

- Tells TimeQuest to ignore any clock latency constraints applied to source clock

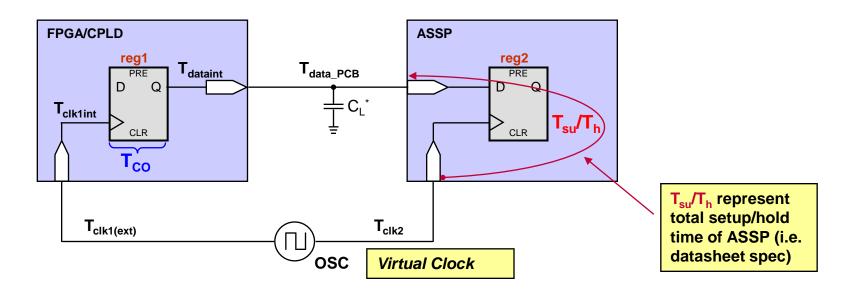

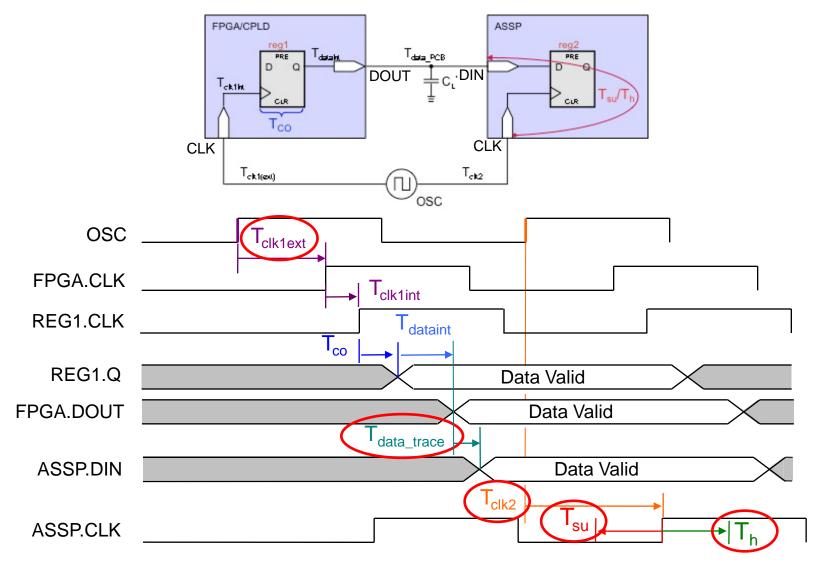

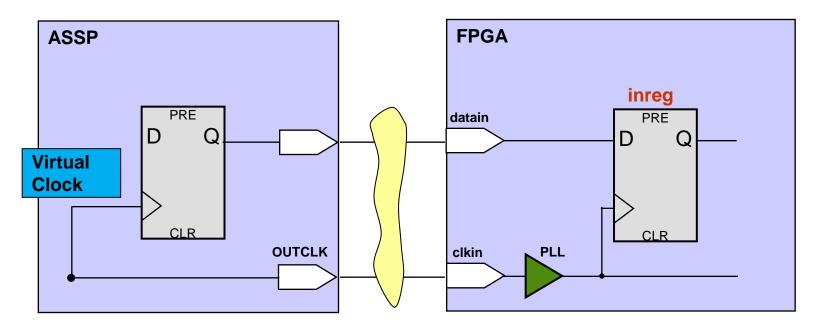

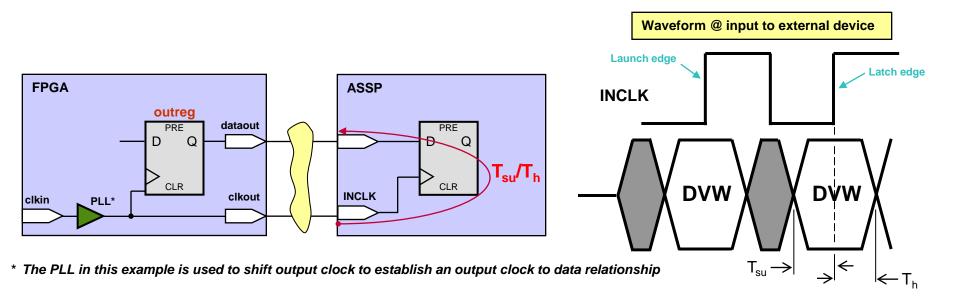

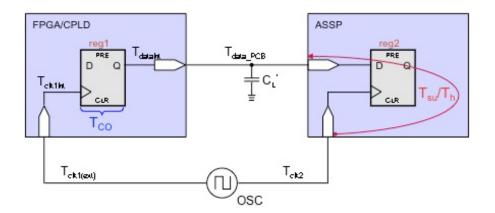

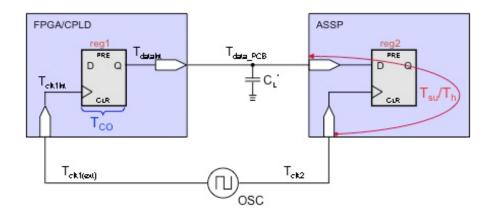

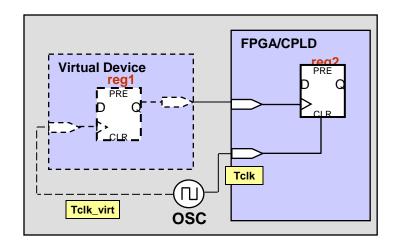

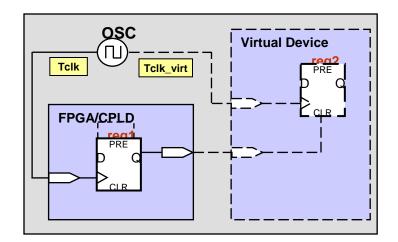

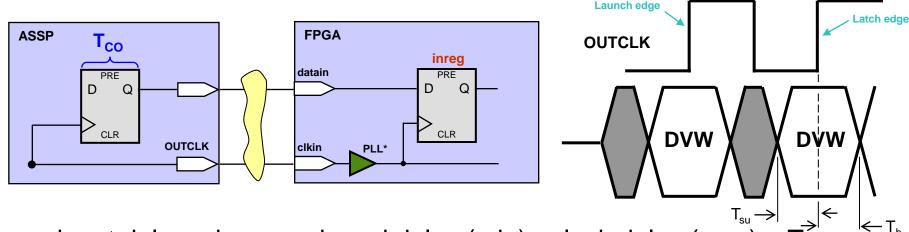

## **Synchronous Outputs**

Need to specify timing relationship from FPGA/CPLD to ASSP to guarantee clock-tooutput times in FPGA/CPLD

<sup>\*</sup> Represents delay due to capacitive loading

## **Synchronous Outputs**

## **Constraining Synchronous Outputs**

- Use set\_output\_delay (-max option) command to constrain maximum clock-to-output (maximum time to arrive and still meet ASSP's T<sub>su</sub>)

- Calculated output delay value represents all delays external to device

#### **System-Centric**:

output delay max = Data trace (max) - Board clock skew (min) + T<sub>su</sub>

$$= (T_{data\_PCB(max)} + T_{CL}) - (T_{clk2(min)} - T_{clk1ext(max)}) + T_{su}$$

**FPGA-Centric**:

output delay max =  $(T_{launch} - T_{latch}) - T_{CO(max)}$

- Use set\_output\_delay (-min option) command to constrain minimum clock-to-output (minimum time to stay active and still meet ASSP's T<sub>h</sub>)

- Calculated output delay value represents all delays external to device

#### **System-Centric:**

output delay min = Data trace (min) - Board clock skew (max)  $- T_h$

$$= (T_{\text{data\_PCB(min)}} + T_{\text{CL}}) - (T_{\text{clk2(max)}} - T_{\text{clk1ext(min)}}) - T_{\text{h}}$$

FPGA-Centric:

output delay min =  $-T_{CO(min)}$

#### set\_output\_delay Command

Constrains output pins by specifying external device timing parameters

### Options

```

-clock <clock_name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

<delay value>

<targets>

```

### set\_output\_delay Notes

-clock\_fall: output signal was latched by a falling edge clock transition

All others same as set\_input\_delay command

## Input/Output Delays (GUI)

## Synchronous I/O Example

<u>Note</u>: expr in these constraints is used to simply calculate the value of the equation broken down into the 3 parts defined by the input/output delay

© 2010 Altera Corporation—Confidential

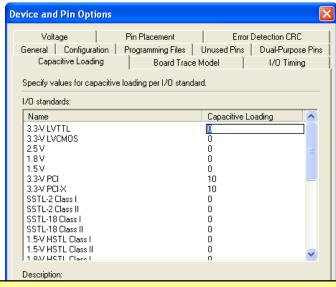

## **Output Pin Load**

Capacitive Loading tab of Device and Pin Options button in Device Settings

- Specifies output pin loading in picofarads (pf)

- Changes default loading value of I/O standard

- Changes t<sub>co</sub> of output pins

- Allows designer to accurately model board conditions

- Specify for entire I/O standard in Device Settings

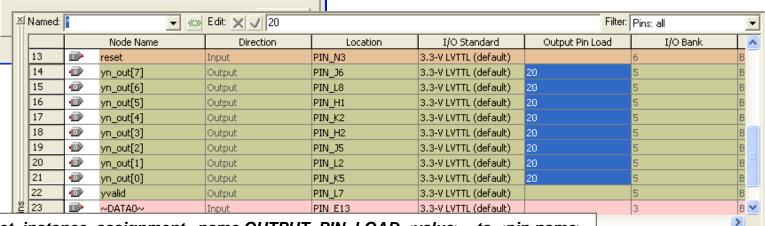

- Apply to individual output or bidirectional pins in Assignment Editor or Pin Planner All Pins list

- Applies to 90-nm or older devices only

Tcl: set\_instance\_assignment -name OUTPUT\_PIN\_LOAD <value> -to <pin name>

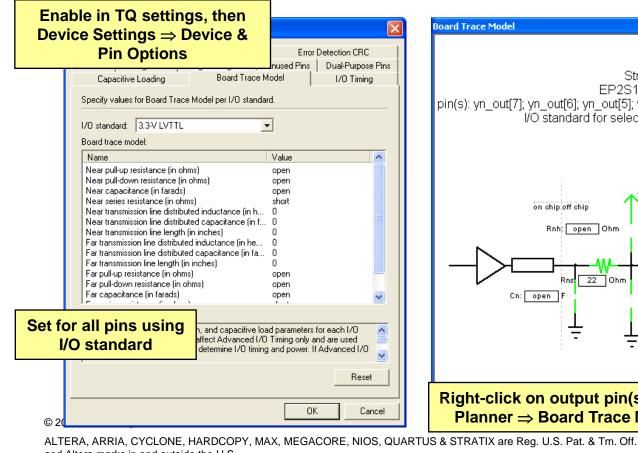

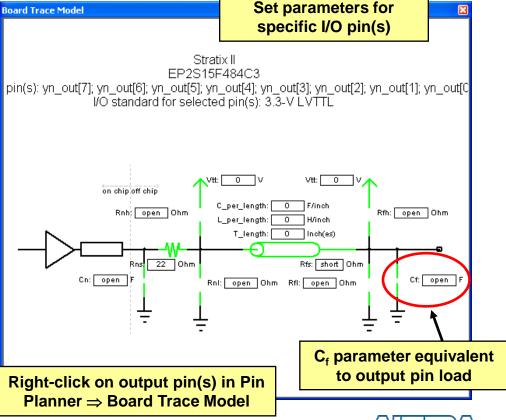

## **Advanced I/O Timing**

- Enhances analysis (over capacitive loading) by allowing user to enter boardlevel parameters (Cyclone III, Stratix II, III, & IV devices only)

- Use in lieu of or in addition to HSPICE & IBIS modeling

- View signal integrity metrics in Compilation Report (TimeQuest folder)

and Altera marks in and outside the U.S.

# **Synchronous I/O Timing Summary**

|                    | System-centric                                                                                                                                                                     | FPGA-centric             |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Input delay (max)  | Board delay (max) - Board clock Skew (min) + $T_{CO(max)}$<br>Board delay (max) = $T_{data\_PCB(max)}$ + $T_{CL}$<br>Board clock skew (min) = $T_{clk2ext(min)}$ - $T_{clk1(max)}$ | T-T <sub>SU</sub>        |

| Input delay (min)  | Board Delay (min) - Board clock skew (max) + $T_{CO(min)}$<br>Board delay (min) = $T_{data\_PCB(min)}$ + $T_{CL}$<br>Board clock skew (max) = $T_{clk2ext(max)}$ - $T_{clk1(min)}$ | T <sub>h</sub>           |

| Output delay (max) | Board Delay (max) - Board clock skew (min) + $T_{SU}$<br>Board delay (max) = $T_{data\_PCB(max)}$ + $T_{CL}$<br>Board clock skew (min) = $T_{clk2(min)}$ - $T_{clk1ext(max)}$      | T - T <sub>CO(max)</sub> |

| Output delay (min) | Board Delay (min) - Board clock skew (max) - $T_h$<br>Board delay (min) = $T_{data\_PCB(min)}$ + $T_{CL}$<br>Board clock skew (max) = $T_{clk2(max)}$ - $T_{clk1ext(min)}$         | -T <sub>CO(min)</sub>    |

Note: The  $T_{SU}$ ,  $T_h$ ,  $T_{CO(max)}$  and  $T_{CO(min)}$ , for FPGA-centric, are chip-level timing requirements.  $T = (T_{latch} - T_{launch})$

# Please go to Exercise 3

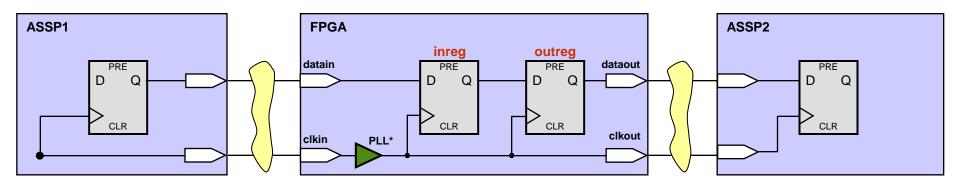

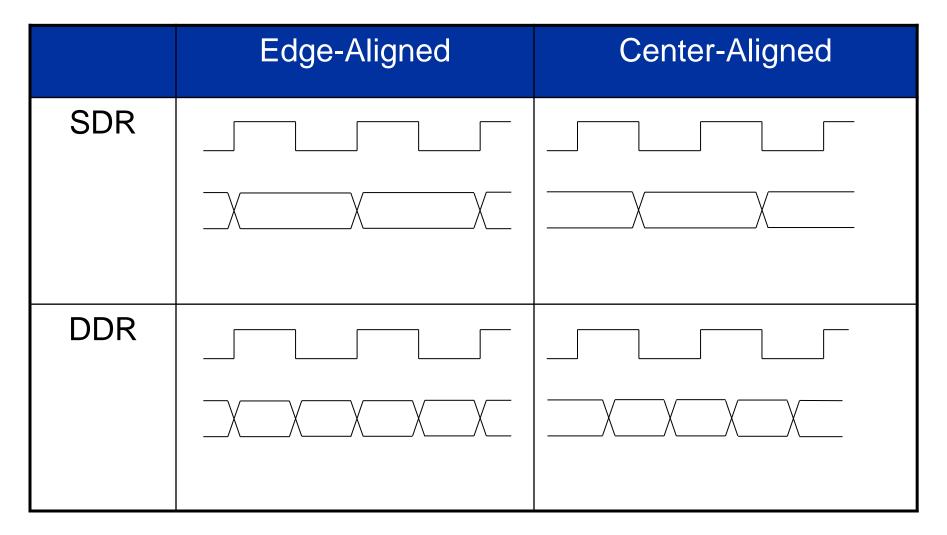

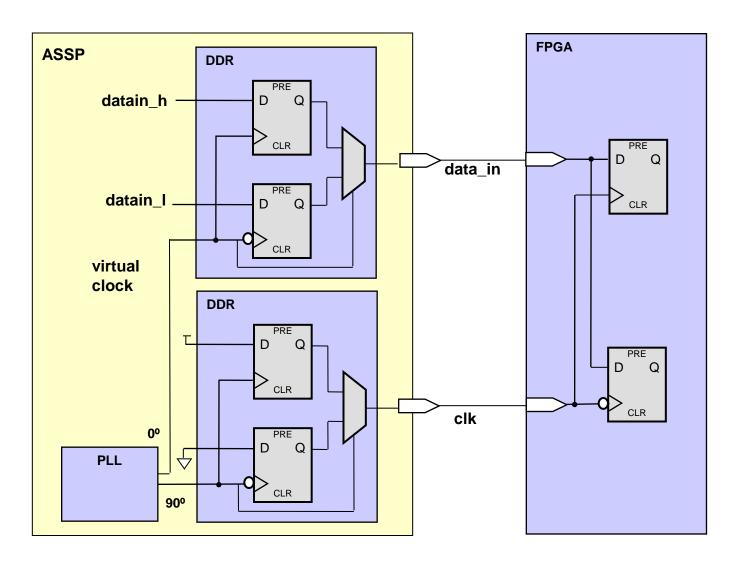

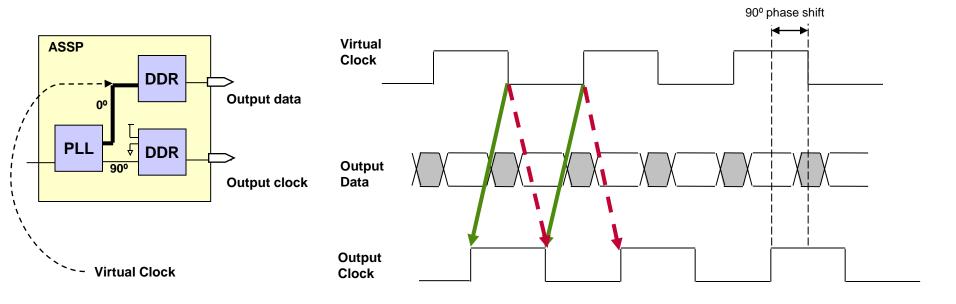

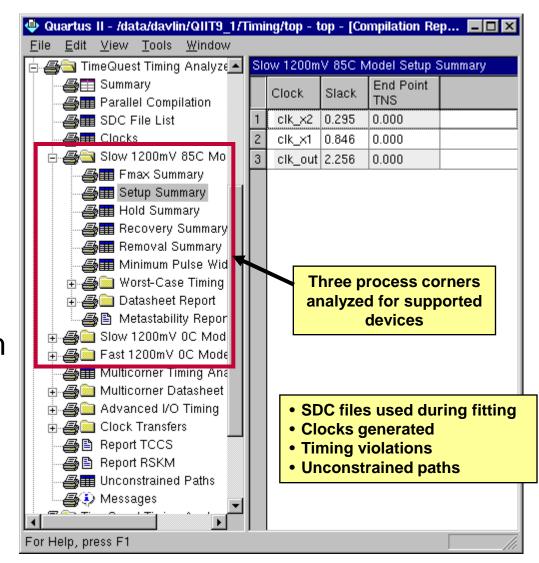

## **Source-Synchronous Interfaces**

- Both data & clock transmitted by host device with designated phase relationship (e.g. edge or centeraligned)

- No clock tree skew included in calculation

- Target device uses transmitted clock to sample incoming data

- Skew between data and clock is the limitation factor of transmission speed

- Enables higher interface speeds (compared to using system clock)

- \* The optional PLL in this example, represented by a single symbol, is actually generating multiple outputs clocks

## **Source Synchronous Clocking Schemes**

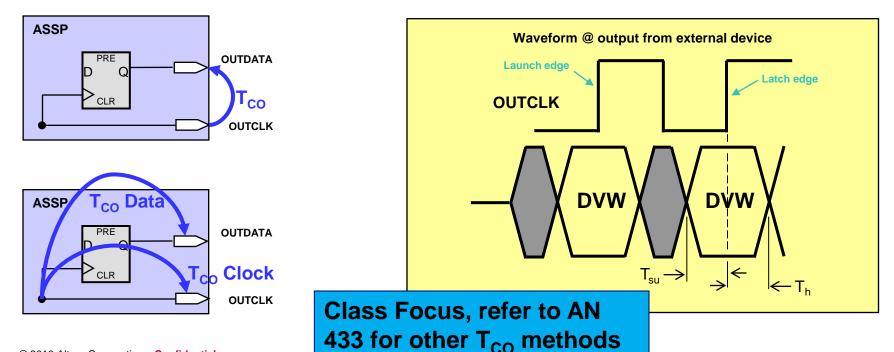

## SDR Source-Synchronous Input (Data Sheet)

- The FPGA input constraints vary depending on what's given by the data sheet of the ASSP:

- T<sub>CO</sub> relative to the output clock

- T<sub>CO</sub> relative to the input clock

- Specify setup and hold parameters for the data output

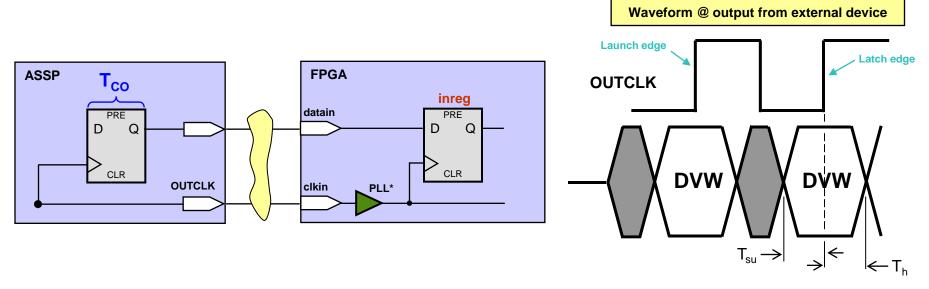

## SDR Source-Synchronous Input (Center-Aligned)

- Total setup/hold relationship of FPGA to clock (clkin) already defined by output waveform of external device

- T<sub>su</sub> is start of DVW

- T<sub>h</sub> is end of DVW

- Must derive set\_input\_delay values from T<sub>su</sub> & T<sub>h</sub>

<sup>\*</sup> The PLL in this example is used to maintain the input clock to data relationship © 2010 Altera Corporation—Confidential

## SDR Source-Synchronous Input (Center-Aligned)

#### System-centric approach:

input delay max = data trace (max) - clock trace (min) + (latch edge - launch edge)\* - T<sub>SU</sub>

#### FPGA-centric approach:

input delay max = (latch edge - launch edge)\* - T<sub>su</sub>

\*Typically 1 clock period for SDR

© 2010 Altera Corporation—Confidential

## SDR Source-Synchronous Input (Center-Aligned)

#### System-centric approach:

input delay min = data trace (min) - clock trace (max) + T<sub>h</sub>

#### FPGA-centric approach:

input delay min  $= T_h$

## **Using SDC with Source-Sync Input**

- Create clock on clock input port

- Use set\_input\_delay command with reference to virtual clock

- Same as with synchronous input

## SDR Source-Synchronous Output (Center-Aligned)

#### System-Centric:

output delay max = data trace (max) – clock trace (min) +  $T_{su}$  output delay min = data trace (min) – clock trace (max) – Th

#### **FPGA-Centric:**

output delay max = Tsu output delay min = Th

Notice output delay minimum is negative

© 2010 Altera Corporation—Confidential

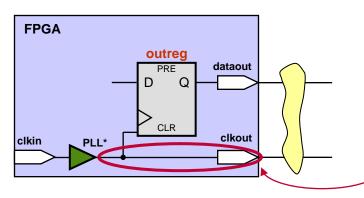

#### **Using SDC with Source-Synch Output**

This path must be analyzed when calculating data required time

- Must tell timing analyzer to analyze path from clock source to output clock port during analysis

- Use set\_output\_delay command on dataout with reference to new generated clock on output port

- Create generated clock on output clock port (source is PLL output pin)

- Use -clock argument in output delay assignment to associate output clock to output data bus

- Path from PLL output pin to output port still considered unconstrained (clock path viewed as a data path by timing analyzer)

- Constrain path from PLL pin to output port with false path (described later),

set\_min/max\_delay, or set\_output\_delay

#### **Constraining Source-Sync Output Example**

```

create clock -period 5 -name clkin \

[get ports clkin]

create generated clock -name pllclk -divide by 1 \

-source [get ports clkin]

[get_pins inst|altpll_component|pll|clk[0]]

# Place clock on external clock output

create generated clock -name clkout \

-source [get_pins inst|altpll_component|pll|clk[0]] \

-divide by 1 [get ports clkout]

# Constrain dataout with an external tsu of 0.5 ns

# and th of 0.5 ns using clkout as clock

set_output_delay -clock [get_clocks clkout] \

-max 0.500 [get ports dataout]

set_output_delay -clock [get_clocks clkout] \

-min -0.500 [get ports dataout]

```

## Source Synchronous I/O Timing Summary

|                       | System-centric                                                                      | FPGA-centric                                 |

|-----------------------|-------------------------------------------------------------------------------------|----------------------------------------------|

| Input delay (-max)    | Data trace (max) – clock trace (min) + (latch edge – launch edge) - T <sub>SU</sub> | (latch edge – launch edge) – T <sub>SU</sub> |

| Input delay (-min)    | Data trace (min) – clock trace (max) + T <sub>h</sub>                               | T <sub>h</sub>                               |

| Input delay –clock    | Target virtual input clock                                                          |                                              |

| Output delay (-max)   | Data trace (max) – clock trace (min) + T <sub>SU</sub>                              | T <sub>SU</sub>                              |

| Output delay (-min)   | Data trace (max) – clock trace (min) - T <sub>h</sub>                               | -T <sub>h</sub>                              |

| Output delay (-clock) | Target generated clock on FPGA output port                                          |                                              |

#### Notes:

- The above only applies to center-aligned only. Also there are many other ways to constrain source synchronous I/Os. For more information, please refer to <u>AN 433:</u> <u>Constraining and Analyzing Source-Synchronous Interfaces</u>

- May also require some other timing exception constraints (to be discussed later).

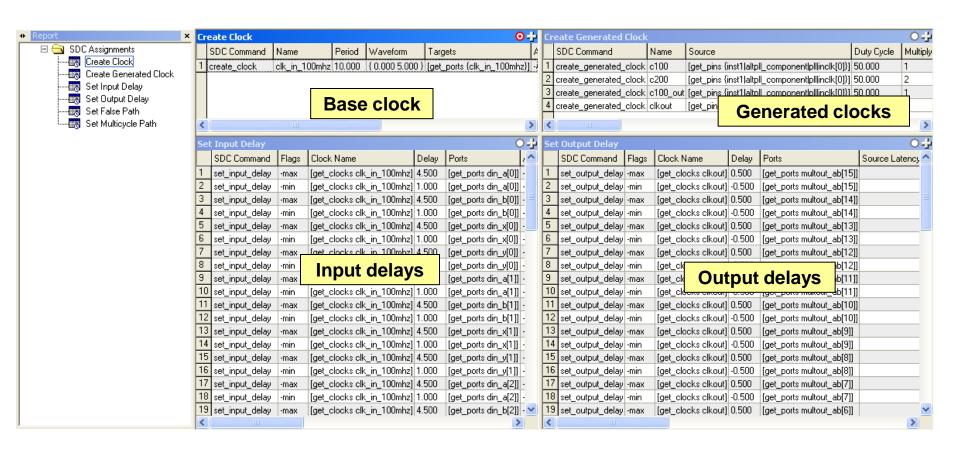

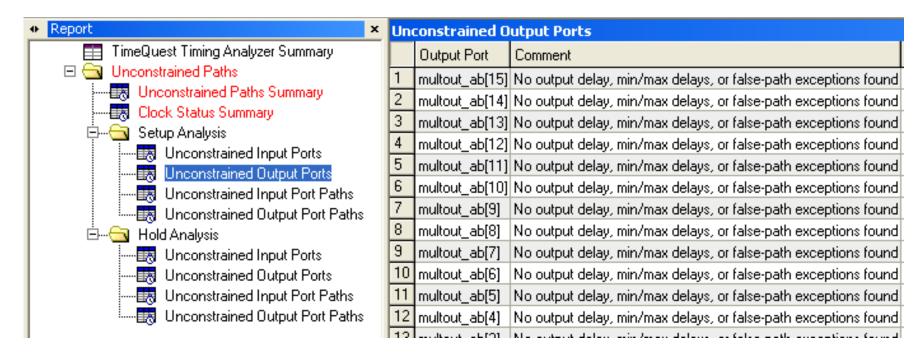

## **Checking I/O Constraints**

- Helpful TimeQuest reports to run to verify constraints

- Report SDC

- Report Unconstrained

- Report Ignored Constraints

#### Report SDC (report\_sdc)

List SDC constraints applied to netlist

#### Report Unconstrained Paths (report\_ucp)

- Same report as before used for unconstrained clocks (Clock Status Summary report)

- Setup and Hold Analysis folders list unconstrained I/O ports and paths

#### **Verifying Clocks & I/O Timing**

- Use Setup & Hold Summary reports to check worst slack for each clock

- Obtaining summary reports

- Use create\_timing\_summary Tcl command

- TimeQuest folder of Compilation Report

- Run Report Setup Summary & Report Hold Summary reports from Tasks pane or Reports menu

- For detailed slack/path analysis

- Run Report Timing from Tasks pane or Constraints menu

- Use report\_timing command

# Please go to Exercise 4

## **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

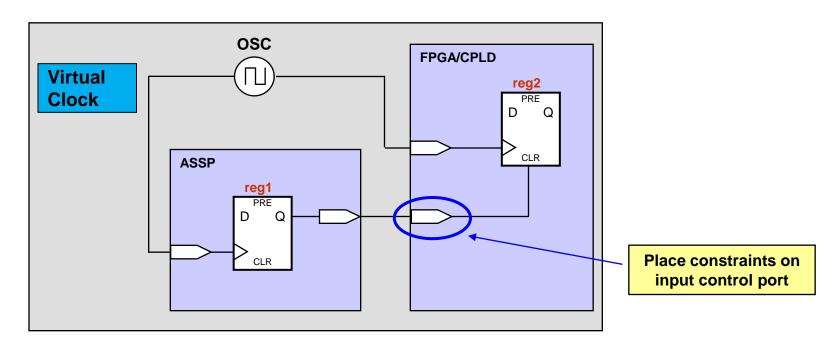

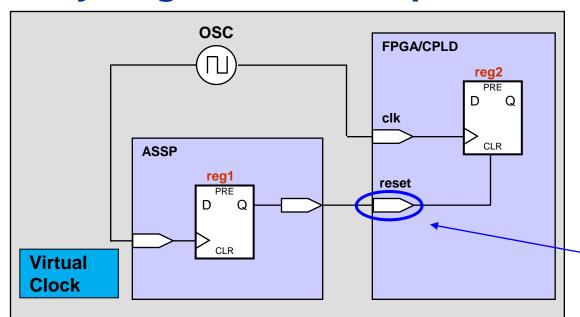

#### **Asynchronous Paths**

- Definition: signals that drive asynchronous inputs on internal registers (e.g. clear, preset)

- Used for design initialization & as outputs of control structures

- Must be constrained

#### **TimeQuest TA & Asynchronous Ports**

- Asynchronous inputs assumed registered either internally or externally

- Timing analyzer performs recovery (setup) & removal (hold) analysis on asynchronous inputs

- Required times & arrival times are calculated just like for synchronous data

#### Recovery & Removal (Review)

Recovery: The minimum time an asynchronous signal can be

de-asserted BEFORE clock edge

Removal: The minimum time an asynchronous signal can be

de-asserted AFTER clock edge

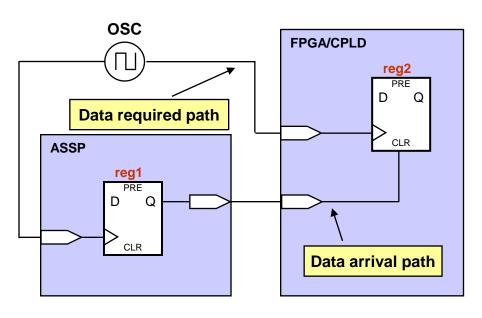

#### **Types of Asynchronous Paths**

- Externally registered

- Internally registered

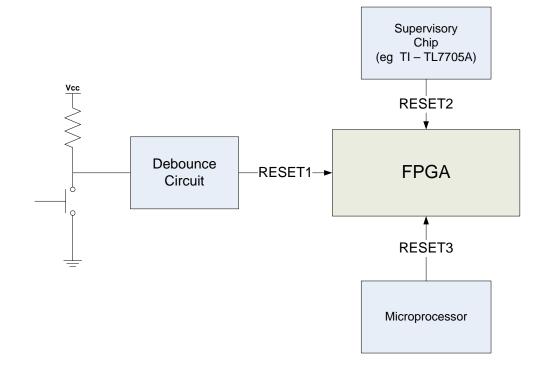

#### **Externally Registered**

- Control signal generated by a registered output of another device

- Typical sources are:

- Push button reset thru debounce circuit

- Supervisory chip

- Micro-processor GPIO

#### **Externally Registered (cont.)**

Apply set\_input\_delay -max & set\_input\_delay -min to input port to constrain

#### **Externally Registered Example**

Place constraints on input control port

© 2010 Altera Corporation—Confidential

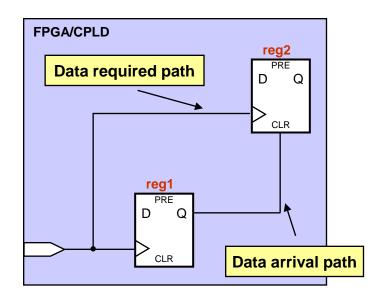

#### **Internally Registered**

- Control signal generated as output of internal register

- Paths are covered by clock constraints

#### **Checking Asynchronous Control Constraints**

Use same reports as for clocks & I/O

#### Externally registered

If unconstrained, paths show up as unconstrained input ports & paths

#### Internally registered

If unconstrained, clock driving register appears as unconstrained

#### **Reporting Asynchronous Control Paths**

Use same methods as clocks & I/O

#### Summary reports

- Use -recovery | -removal options with create\_timing\_summary

- Run Report Recovery/Removal Summary (Tasks pane or Reports menu)

#### Detailed slack/path reports

- Use -recovery | -removal options with report\_timing

- Choose Recovery or Removal as Analysis Type when running Report Timing (Tasks pane or Reports menu)

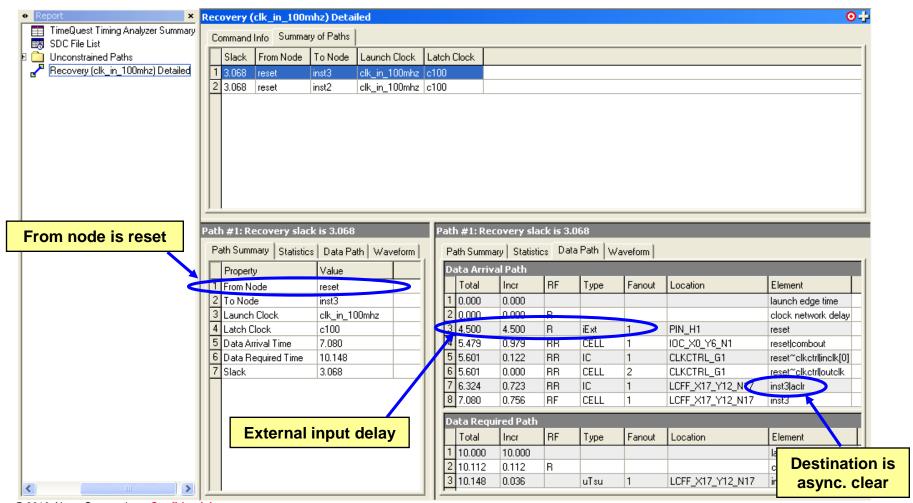

#### **Example Recovery Report (Ext. Registered)**

report\_timing -from\_clock clk\_in\_100mhz -recovery -npaths 10 \

-detail path\_only -panel\_name {Recovery (clk\_in\_100mhz) Detailed}

© 2010 Altera Corporation—Confidential

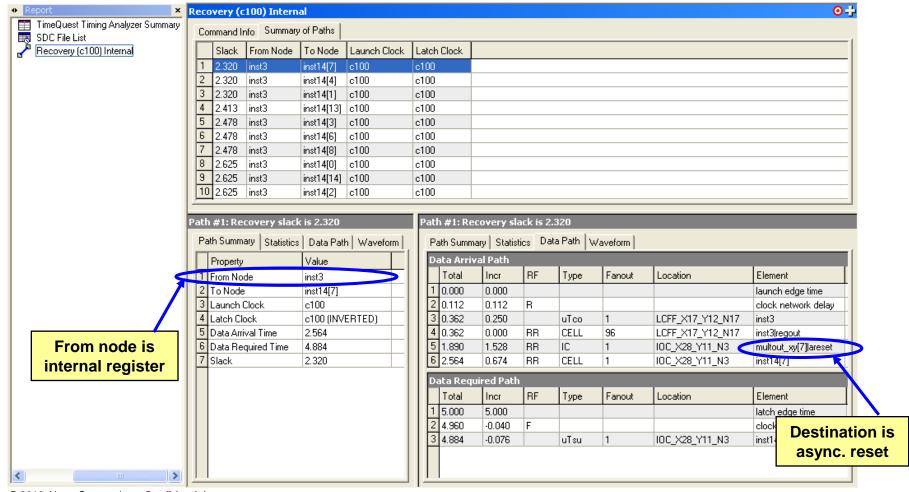

#### **Example Recovery Report (Int. Registered)**

report\_timing -from\_clock c100 -recovery -npaths 10 \

-detail path\_only -panel\_name {Recovery (c100) Internal}

© 2010 Altera Corporation—Confidential

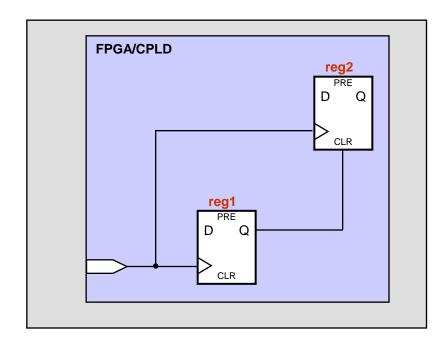

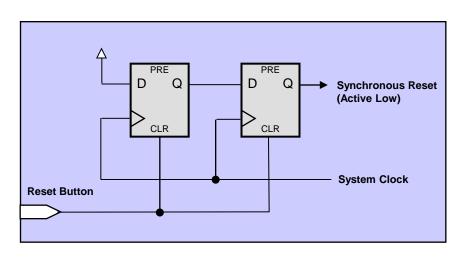

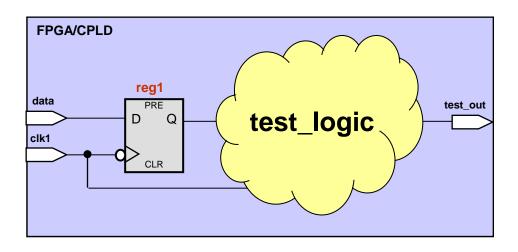

#### What about truly asynchronous control inputs?

- BAD IDEA to use it directly!!!!

- Solution: Synchronize inputs with internal clock

- Input may then become false path (discussed in next section)

- But if you must...

- Use set\_max\_delay &

set\_min\_delay to

constrain paths

OR

- Use set\_input\_delay of 0 on input

- Asynchronous signal valid as soon as it arrives on input port

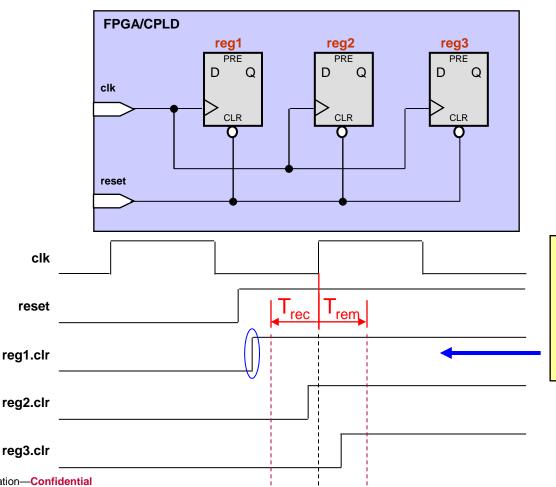

#### **Need More Proof?**

For example, these state machine registers should all be de-asserted together, but...

Due to routing delay (skew) of the clear signal, only reg1 comes out of reset correctly, the rest may de-assert on the next clock cycle. This could mean starting in the wrong state (or even an illegal state).

© 2010 Altera Corporation—Confidential

## **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

#### **Timing Exceptions: False Paths**

- Logic-based

- Paths not relevant during normal circuit operation

- e.g. Test logic, static or quasi-static registers

- Timing-based

- Paths intentionally not analyzed by designer

- e.g. Bridging asynchronous clock domains using synchronizer circuits

- Must be marked by constraint to tell TimeQuest to ignore them

#### **Two Methods to Create False Paths**

- set\_false\_path command

- Use when particular nodes are involved

- Examples

- All paths from an input pin to a set of registers

- All paths from a register to another clock domain

- set\_clock\_groups command

- Use when just clock domains are involved

#### set\_false\_path Command

- Indicates paths that should be ignored during fitting and timing analysis

- Options

```

[-fall_from <clocks>]

[-rise_from <clocks>]

[-from <names>]

[-through <names>]

[-to <names>]

[-fall_to <clocks>]

[-rise_to <clocks>]

[-setup]

[-hold]

<targets>

```

#### set\_false\_path Notes

- -from & -to: Use to specify source & target nodes

- Target nodes can be clocks, registers, ports, pins or cells

- For registers, -from should be source register clock pin

- Specify a clock name to constrain all paths going into or out of its domain

- Constrains both rising and falling edge clock transitions

- More efficient than specifying individual nodes

- -rise\_from & -fall\_from: Use to indicate clocks for the source node & whether constraint is for a rising or falling edge clock transition; not in GUI

- -rise\_to & -fall\_to: Use to indicate clocks for destination node & direction of transition; not in GUI

- -setup & -hold: Use to apply false paths to only setup/recovery or hold/removal analysis; not in GUI

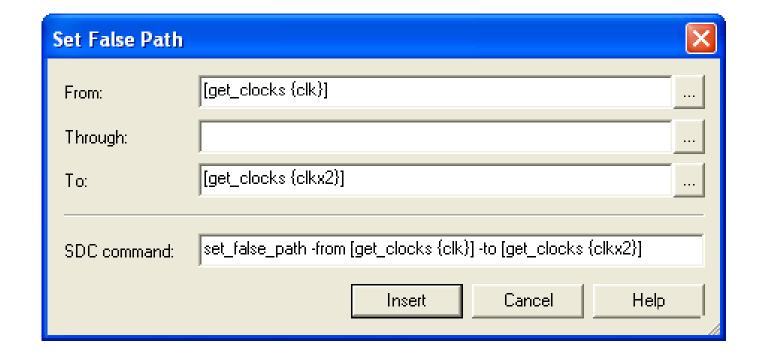

#### **Set False Path (GUI)**

#### **False Path Example 1**

Simple synchronizer circuit between two asynchronous clock domains

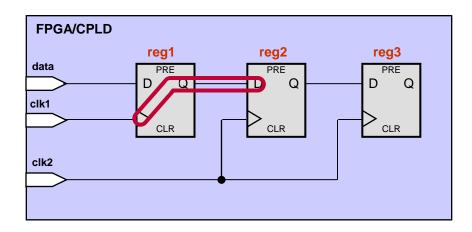

#### False Path Example 2

Cutting analysis of inserted test logic

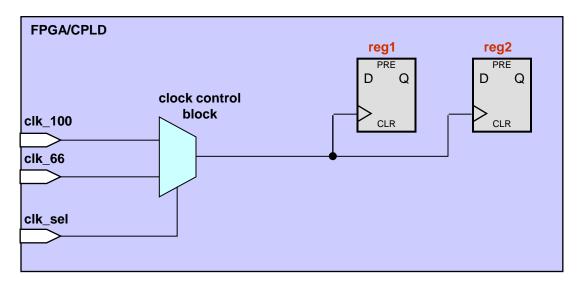

## set\_clock\_groups Command

- Tells Fitter and timing analyzer to ignore ALL paths between specified clock domains

- Great for clock muxes

- Equivalent to setting false paths (-from & -to) on all paths between domains

## Options

```

[-asynchronous | -exclusive]

-group <clock name>

-group <clock_name>

[-group <clock name>]...

```

## set\_clock\_groups Notes

-group: each group of clock names is mutually exclusive to other clock groups

### Additional argument\*:

- asynchronous: no phase relationship, but clocks active at the same time

- exclusive: clocks not active at the same time

- Example: clock muxes

#### \*Notes:

- Need at least one of the two arguments (-asynchronous or -exclusive)

- TimeQuest Timing Analyzer treats both options as if they were the same

- With one -group argument, TimeQuest Timing Analyzer cut analysis of ALL paths to that group of clocks.

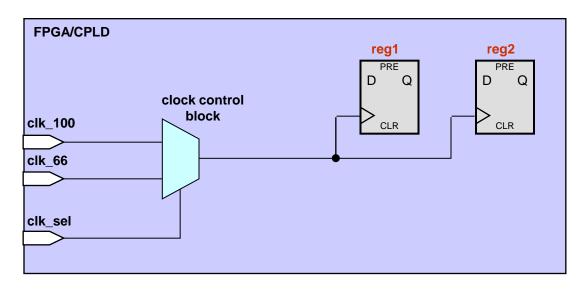

## **Clock Mux Example 1**

```

create_clock -period 10.0 [get_ports clk_100]

create_clock -period 15.0 [get_ports clk_66]

set_clock_groups -exclusive -group {clk_100} -group {clk_66}

# Since clocks are muxed, timing analyzer should not analyze # cross-domain paths as only one clock will be driving the # registers at any one time.

```

## **Clock Mux Example 1 (Alternative)**

```

create_clock -period 10.0 [get_ports clk_100]

create_clock -period 15.0 [get_ports clk_66]

set_false_paths -from [get_clocks clk_100] -to [get_clocks clk_66]

set_false_paths -from [get_clocks clk_66] -to [get_clocks clk_100]

# For an equivalent constraint using false paths, you must

# consider paths going both directions

```

© 2010 Altera Corporation—Confidential

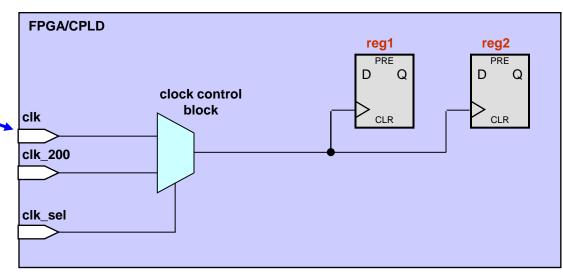

## **Clock Mux Example 2**

Applying two clock settings to same input port

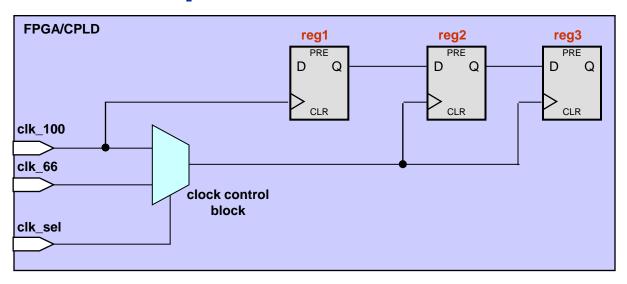

## **Clock Mux Example 3**

© 2010 Altera Corporation—Confidential

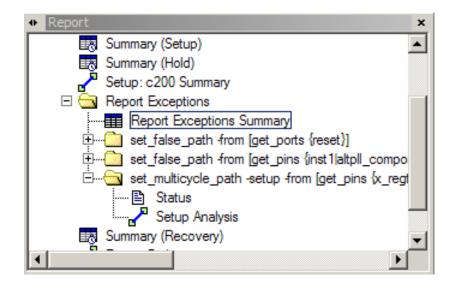

## **Verifying False Paths & Groups**

## False paths

- Create timing exceptions report

- report\_exceptions

- Tasks pane or Reports menu: Report Exceptions

## Clock groups

- Check clock transfers to ensure no paths are returned

- report\_clock\_transfers

- Tasks pane or Reports menu: Report Clock Transfers

## **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

## **Timing Exceptions: Multicycle Paths**

- Paths requiring more than one cycle for data to propagate

- Causes timing analyzer to select another latch or launch edge

- Designer specifies number of cycles to move edge

- Logic must be designed to work this way

- Constraint informs timing analysis how logic is supposed to function

## Other Instances to Use Multicycle Paths

- Design does not require single cycle to transfer data (non-critical paths)

- Otherwise needlessly over-constrain paths

- Clocks are integer multiples of each other with or without offset

- Demonstrated in Exercise 5

- Clock enables ensuring register(s) not sampling data every clock edge

## **Multicycle Types**

| Туре                   | Clock       | Timing Check | Shorthand |  |

|------------------------|-------------|--------------|-----------|--|

| End Multicycle Setup   | Destination | Setup        | EMS       |  |

| End Multicycle Hold    | Destination | Hold         | EMH       |  |

| Start Multicycle Setup | Source      | Setup        | SMS       |  |

| Start Multicycle Hold  | Source      | Hold         | SMH       |  |

#### Destination

- Constraint based on destination clock edges

- Moves latch edge backward (later in time) to relax required setup/hold time

- Used in most multicycle situations

#### Source

- Constraint based on source clock edges

- Moves launch edge forward (earlier in time) to relax required setup/hold time

- Useful when source clock is at higher frequency than destination

#### Setup

- Increases the number of cycles for setup analysis

- Default is 1

#### Hold

- Increases the number of cycles for hold analysis

- Default is 0

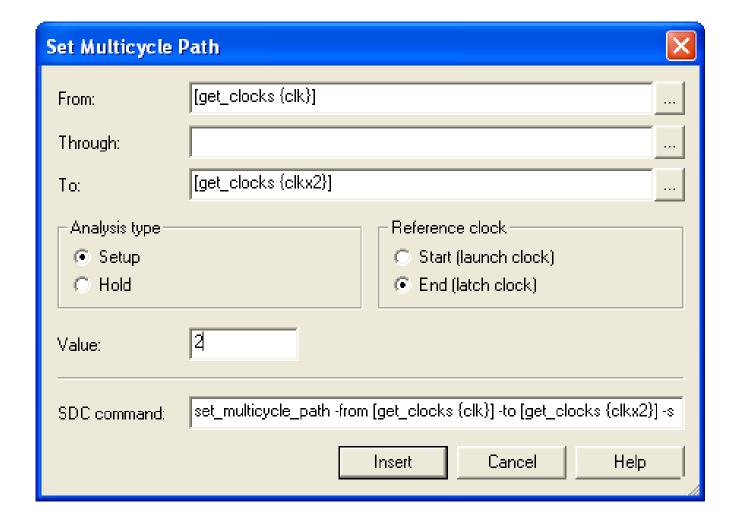

## set\_multicycle\_path Command

Indicates by how many cycles the required time (setup or hold) should be extended from defaults

#### Options

```

[-start | -end]

[-setup | -hold]

[-fall_from <clocks>]

[-rise_from <clocks>]

[-from <names>]

[-through <names>]

[-to <names>]

[-fall_to <clocks>]

[-rise_to <clocks>]

<targets>

```

## set\_multicycle\_path Notes

- -start: Use to select a source multicycle

- -end: Use to select a destination multicycle (default)

- -setup | -hold: Specifies if the multicycle value is applied to the setup or hold calculation

- <value>: Cycle multiplier Number of edges by which to extend analysis

- All other options behave similar to set\_false\_path options

## **Set Multicycle Path (GUI)**

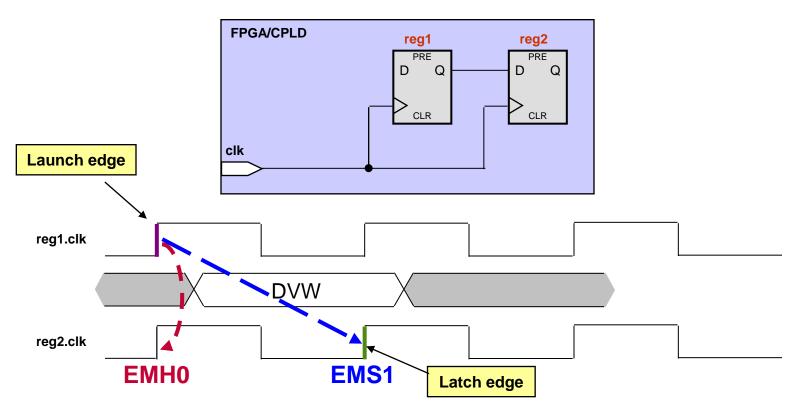

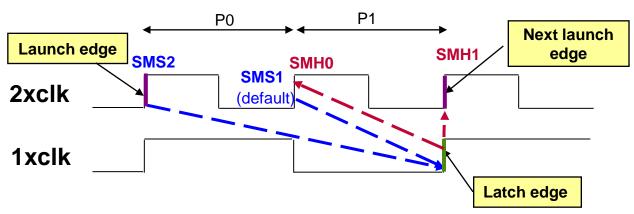

## **Understanding Multicycle (1)**

#### Standard single-cycle register transfer

- Multicycle Setup = 1 (Default)

- - Multicycle Hold = 0 (Default)\*

\*Default hold edge is one edge before/after setup edge

© 2010 Altera Corporation—Confidential

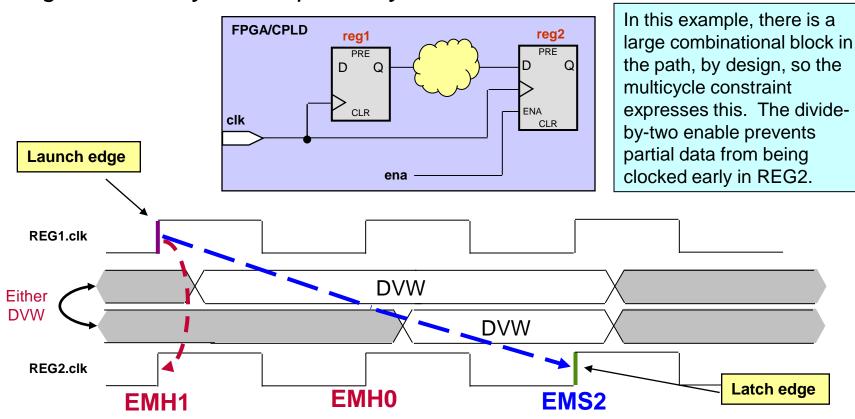

## **Understanding Multicycle (2)**

Change to a two cycle setup; two cycle hold transfer

set\_multicycle\_path -from [get\_pins reg1|clk] -to [get\_pins reg2|datain] -setup 2 set\_multicycle\_path -from [get\_pins reg1|clk] -to [get\_pins reg2|datain] -hold 1

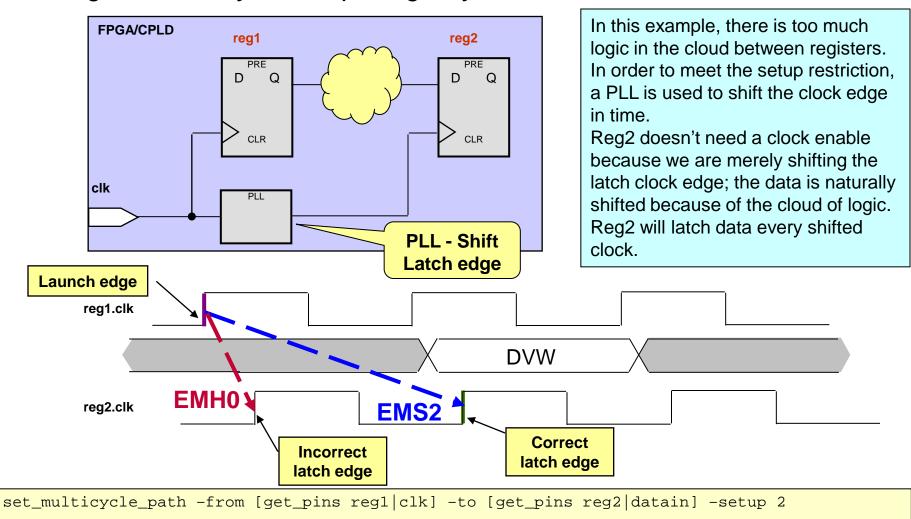

## **Understanding Multicycle (3)**

Change to a two cycle setup; single cycle hold transfer

© 2010 Altera Corporation—Confidential

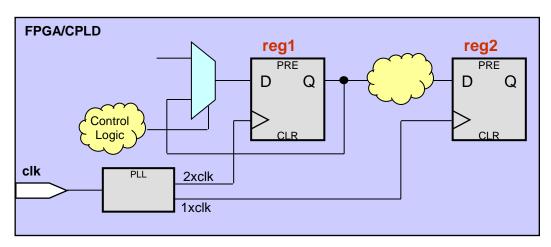

## **Understanding Multicycle (4)**

#### Move the launch edge

In this example, a register clocked by a 2x clock feeds a register clocked with a 1x clock. The launch register only changes value in phase P0 only and never in P1.

Rather than moving the latch edge, we are going to move the launch edge instead, with the -start argument.

```

set_multicycle_path -from [get_pins reg1|clk] -to [get_pins reg2|datain] -start -setup 2 set_multicycle_path -from [get_pins reg1|clk] -to [get_pins reg2|datain] -start -hold 1

```

© 2010 Altera Corporation—Confidential

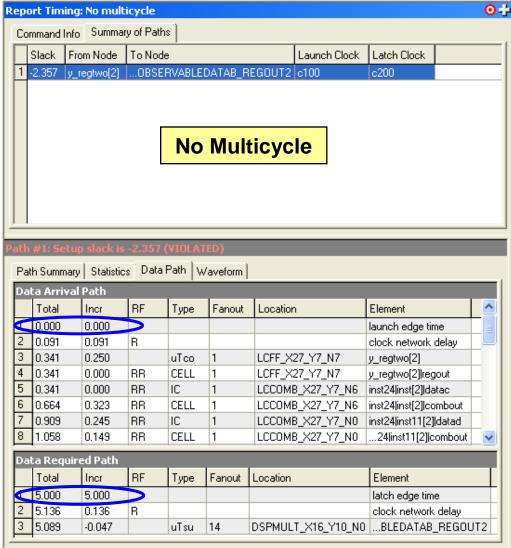

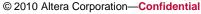

## **Reporting Multicycles**

## **Reporting Multicycles**

## **Report Exceptions**

- Provide information specifically about timing exceptions (false paths and multicycle paths)

- report\_exceptions

- From Tasks pane or Report menu

| R | Report Exceptions Summary |                                                           |             |            |                |               |  |  |

|---|---------------------------|-----------------------------------------------------------|-------------|------------|----------------|---------------|--|--|

|   | Status                    | Exception                                                 | Setup Slack | Hold Slack | Recovery Slack | Removal Slack |  |  |

| 1 | Complete                  | set_false_path -from [get_ports {reset}]                  | Invalid     | n/a        | n/a            | n/a           |  |  |

| 2 | Complete                  | t1 altpll_component pll clk[2]}] -to [get_ports {clkout}] | Invalid     | n/a        | n/a            | n/a           |  |  |

| 3 | Complete                  | tup -from [get_pins {x_regtwo* clk y_regtwo* clk}] 2      | 2.961       | n/a        | n/a            | n/a           |  |  |

## **SDC Timing Constraints**

- Clocks

- I/O

- Asynchronous paths

- False paths

- Multicycle paths

- Delay and skew specifications

# **Absolute Delays**

- Applies a timing value to a particular path

- Overrides the current setup/hold information for the path derived from clock and I/O constraints

- Apply set\_max\_delay & set\_min\_delay constraints to paths

# **Absolute Delay Example**

- Specify an input port-to-register or register-to-output port constraint without using input & output delays

- Use -rise\_from/-fall\_from & -rise\_to/-fall\_to (not in GUI) to restrict timing value to only registers responding to a rising or falling edge transition

### Ex. DDR input

```

# Apply a 2ns max delay for an input port only to nodes clocked by

# the rising edge of clock CLK

set_max_delay -from [get_ports in*] -rise_to [get_clocks CLK] 2.000

```

# **Specify skew**

- set\_max\_skew

- from, -include, -to: specify paths or pins of a cell

- <skew>: required maximum skew

- Specify maximum path-based skew requirements for registers and ports in the design.

- By default, the command excludes set\_input\_delay and set\_output\_delay values

- When used, results are reported with report\_max\_skew

# **Quartus® II Software Design Series: Timing Analysis**

Example Application – DDR Input

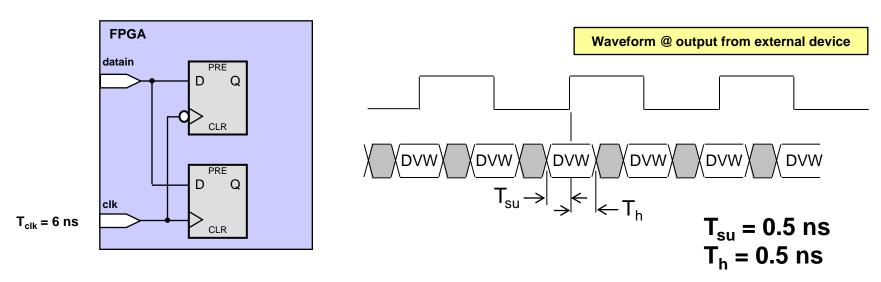

## **DDR Input Example**

## **DDR Input Example (cont.)**

- What's different about this circuit than prior examples?

- Rising & falling edge input registers from same input port

- Registers have ½ clock period for required time

## DDR Input Example (cont.)

- Correct Hold relationship

- - Correct Setup relationship

- Need false path exceptions to prevent timing analysis on opposite-edge transfers

## **DDR Input Example (cont.)**

```

# Define variables

set clk period 6

set Tsu 0.5

set Th 0.5

# Create clocks and virtual clocks

create clock -period $clk period [get ports clk]

create_clock -period $clk_period -name clk_v

# Rising edge clock constraint

set_input_delay -clock clk_virt -max [expr $clk_period / 2 - $Tsu] [get_ports {datain}]

set input delay -clock clk virt -min $Th [get ports {datain}]

# Falling clock edge constraint

set_input_delay -clock clk_virt -max [expr $clk_period / 2 - $Tsu] [get_ports {datain}] \

-clock fall -add delay

set_input_delay -clock clk_virt -min $Th [get_ports {datain}] \

-clock fall -add delay

# Set false paths

set_false_path -setup -rise_from {clk_virt} -fall_to {clk}

set false path -setup -fall from {clk virt} -rise to {clk}

set_false_path -hold -rise_from {clk_virt} -rise_to {clk}

set_false_path -hold -fall_from {clk_virt} -fall_to {clk}

```

## **DDR Reporting**

- Use report\_timing Command

- Must check all rising & falling edge transitions

- Two data valid windows to check

- One from a rising edge source clock

- One from a falling edge source clock

- Use rise\_from, rise\_to, fall\_from, fall\_to

# Please go to Exercise 5