# **FP-MCU AG1F1 Device Datasheet**

Version 0.52 February 2008

Agate Logic, Inc.

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Agate Logic, Inc. reserves the right to discontinue or make changes, without prior notice, to any products herein to improve reliability, function, or design. Agate Logic, Inc. advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

Copyright © 2005-2008 Agate Logic, Inc. All rights reserved. No part of this document may be copied, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the written permission of Agate Logic, Inc. All trademarks are the property of their respective companies.

# Contents

#### **About This Datasheet**

| Typographic Conventions      | V   |

|------------------------------|-----|

| Additional Resources         | V   |

| Technical Support Assistance | .VI |

#### Section 1. Introduction

| Overview | 1 |

|----------|---|

| Features | 1 |

#### Section 2. Architecture

| Architecture Overview             |

|-----------------------------------|

| Top Level Architecture Overview   |

| FP Programmable (FP) Core         |

| Features                          |

| FP Logic Cell5                    |

| Clock Bundle Control Logic9       |

| Routing Architecture11            |

| Embedded Memory11                 |

| Memory Modes12                    |

| Conflict Avoidance                |

| Parity Bit Support16              |

| Memory Configuration Sizes16      |

| Byte Enables17                    |

| PLL                               |

| Clock Multiplication and Division |

| PLL Control Signals               |

| Agate 8051                        |

| Introduction                      |

| Features                          |

| Model and Signals                 |

| Memory Organization               |

| Internal Data Memory21            |

| External Data Memory22            |

| Program Memory23                  |

| Data RAM Extension                |

| Register Space                    |

| Register Space Assignment24       |

| Register Reset Value              |

| Register Description              |

| Accumulator Register (ACC)        |

| B Register                           |    |

|--------------------------------------|----|

| Program Status Word Register (PSW)   | 26 |

| Stack Pointer Register (SP)          | 27 |

| Data Pointer Registers (DPL and DPH) | 27 |

| Ports 0 to 3 Registers               | 27 |

| Interrupt Registers                  | 27 |

| Timers/Counters Registers            | 28 |

| Serial Interface Registers           |    |

| Watchdog Timer Registers             |    |

| Performance Improvement              |    |

|                                      |    |

#### Section 3. Configuration

| 39 |

|----|

|    |

| 40 |

| 40 |

| 40 |

|    |

#### Section 4. DC Characteristics

| SPIO DC Specifications       | 41 |

|------------------------------|----|

| LVCMOS33 D.C. Specifications | 41 |

| LVCMOS25 D.C. Specifications | 41 |

| LVCMOS18 D.C. Specifications | 42 |

| LVCMOS15 D.C. Specifications | 42 |

| Different IO Driven Strength | 42 |

| GPIO DC Specifications       | 43 |

| LVCMOS33 D.C. Specifications | 43 |

#### Section 5. Pinout Information

| Overview                                        | 44 |

|-------------------------------------------------|----|

| Pin Types                                       | 44 |

| LQFP144: 144-lead Low Profile Quad Flat Package |    |

|                                                 |    |

#### **Revision History**

| <b>Revision History</b> | 4 |

|-------------------------|---|

|-------------------------|---|

# About This Datasheet

This datasheet provides comprehensive information about the Agate Logic FP-MCU AG1F1 devices.

# **Typographic Conventions**

| Visual Cue                  | Meaning                                                                                                   |

|-----------------------------|-----------------------------------------------------------------------------------------------------------|

| Bold                        | Headings, figure and table indexes, figure titles,<br>and table items. Example: Figure 2.3.1 8051<br>Mode |

| Italic Bold                 | Table titles. Example: Table 1.1 FP-MCUAG1F1 Features                                                     |

| Helvetica                   | Text and figures in tables. Example: Core Voltage                                                         |

| Arial                       | Note reminders. Example: Notes for above tables                                                           |

| Palatino Linotype in italic | Reference to sections within this document.Example: Clock Bundle Control Logic                            |

| •                           | A list of items whose sequence is not important                                                           |

| (1), (2)                    | Numbers in a note instruction                                                                             |

| $\checkmark$                | A procedure that consists of one step only.                                                               |

The following typographic conventions are used in this document.

# **Additional Resources**

To find additional documentation about Agate Logic products, please see the Agate Logic website at:

#### www.agatelogic.com.cn

To find the up-to-date information about Agate Logic products, please see the Agate Logic website at:

www.agatelogic.com.cn

# **Technical Support Assistance**

Tel: +86 10 82150100

E-mail: <u>support@agatelogic.com.cn</u>

Website: <u>www.agatelogic.com.cn</u>

# Introduction

#### Section 1

Datasheet

This document provides designers with the datasheet specifications for a special member of the Agate Logic Configurable Logic Device Product family: AG1F1, the first product generation of FP-MCU series. These sections contain feature definitions of the internal architecture, configuration, DC operating conditions, pinout information, etc.

#### **Overview**

AG1F1 is a configurable system-on-chip device and optimized for embedded systems applications. With a unique combination of over 1K logic cells (LUT/Register), 36K bits dual-port embedded memory (DPRAM), one configurable PLL, plus a high-performance 8051 MCU and 32K+8K bytes internal RAM, the MCU 8051 is integrated with the FP core logic, not just a bonus additional IP. The AG1F1 devices are designed to offer exceptional functionality, performance and value.

For flexible application, the AG1F1 devices deliver a perfect union of a high-performance 8051 microcontroller and the FP logic cell, which gives designers multiple channels for information getting. For steady and fast performance, a non-volatile SPI flash combined with the AG1F1 devices stores the 8051's user code and FP's configuration data, and the user's code can be copied to and executed from the internal SRAM.

#### **Features**

AG1F1 devices offer the following features:

- Configurable System-on-Chip (CSoC) platform

- More than 1K Field Programmable LUT/Register Logic Cells

- High-performance, industry-standard 8051-compatible microcontroller

- Stand-alone operation from a single external memory (code + configuration)

- 36K bits of configurable dual-port RAM in 9K bits blocks

- 32K + 8K bytes single-port RAM, dedicated for 8051

- Various Configuration (bootstrapping) modes, to support different application requirements

- 1 PLL (Phase-Locked) with clock multiplication and division

- Up to 16 low skew global clocks and reset trees

#### • Software Programmable IOs (SPIOs) and General Purpose IOs (GPIOs)

Table 1.1 summarizes the features of the AG1F1 devices.

| Table 1.1 FP-MCU AG1F1 Features |                            |                           |  |  |  |        |  |  |

|---------------------------------|----------------------------|---------------------------|--|--|--|--------|--|--|

| Parameter                       | AG1F1                      |                           |  |  |  |        |  |  |

| Core Voltage                    |                            | 1.2 V                     |  |  |  |        |  |  |

| GPIOs Voltage                   |                            | 3.3 V                     |  |  |  |        |  |  |

| SPIOs Voltage                   | 3.3 V, 2.5 V, 1.8 V, 1.5 V |                           |  |  |  |        |  |  |

| Process Technology              | 130-nm                     |                           |  |  |  | 130-nm |  |  |

| LC (Logic Cells)                | 1,024                      |                           |  |  |  |        |  |  |

| User I/O Pins                   | 100                        |                           |  |  |  |        |  |  |

| RAM8K Blocks                    | 4                          |                           |  |  |  |        |  |  |

| PLL                             | 1                          |                           |  |  |  |        |  |  |

|                                 | GPIOs LVCMOS 3.3V          |                           |  |  |  |        |  |  |

| IO Standards Support            | SPIOs                      | LVCMOS/LVTTL              |  |  |  |        |  |  |

|                                 | SPIUS                      | 3.3V/2.5V/1.8V/1.5V, LVDS |  |  |  |        |  |  |

# Architecture

#### Section 2

Datasheet

Integrating 1K Field Programmable LUT/Register Logic Cells, an embedded high-performance 8051-based microcontroller and a large block of RAM, the FP-MCU AG1F1 is optimized for low-cost, more flexible industrial control applications. This section provides comprehensive information about the architecture of Agate AG1F1 device.

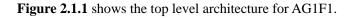

# **Top Level Architecture Overview**

Note:

(1) SPIO means software programmable IO. GPIO means general purpose IO.

The AG1F1 device architecture contains the following fundamental elements.

The 1K logic cells which is also called FP (Field Programmable) core cells provides "derivative on demand" system customization. Same as the general FPGA, these logic cells can perform various potential functions, including combinatorial and sequential logic.

The IO blocks provide the interface between external functions and the internal system bus or configurable system logic. The SPIOs offer advanced IO configuration options such as selectable output current driven strength, single-end IO standard and differential IO standard. The general purpose IO can be programmed to input, output, or inout at LVCMOS3.3V level.

Four blocks of 9Kb DPRAM can be configured to multiplicate data width types from 1 bit to 36 bits. The DPRAM blocks support a parity bit for each byte which can implement parity checking for error detection.

There is also a configurable PLL provided for clock multiplication and division.

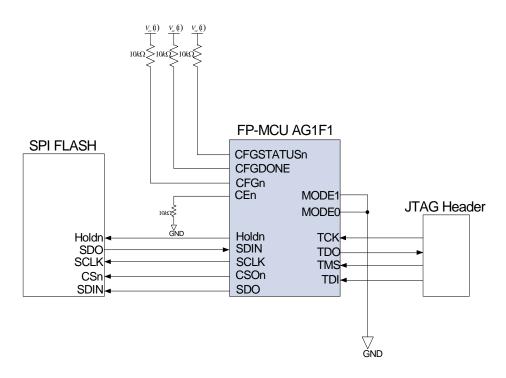

The FP's configuration data and 8051's user code can be stored in a unique SPI Flash. In this mode, the user's code is copied to and executed from the internal SRAM. Using serial interface Flash frees numbers of device IOs. Configuration programs can also be downloaded directly through the JTAG port and written to external Flash via JTAG interface.

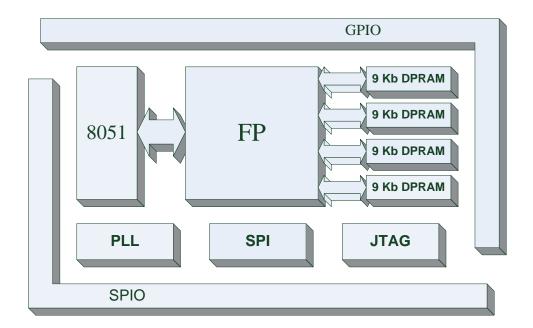

The embedded high-performance 8051-based microcontroller is instruction-compatible with industry-standard 8051-based devices. There is a protected watchdog timer integrated in 8051 MCU. The 8051 MCU is connected with FP directly as shown in **Figure 2.1.2**. All 8051 signals can go through FP to use IO resource. The special interface for FP extension can be used to extend external data RAM or to access DPRAM resource. A large block of fast, byte-wide SRAM provides internal storage for temporary data storage or for code storage.

Figure 2.1.2 provides the connection information of 8051 and FP.

Figure 2.1.2 Connections of 8051 and FP

# Field Programmable

Chapter 2.2

Datasheet

(FP) Core

#### **Features**

As the first product of Agate Logic, FP-MCU AG1F1 devices contain an array of field programmable (FP) logic blocks. Features of the FP are described as follows:

- 1024 logic cells

- 16 global signals available for register clock and reset signals

- 2048 D-type flip-flops available, each cell has two flip-flops

- Every two adjacent logic cells can be combined to function as one 8-input AND, or 8-input OR, or 8-input XOR

- Dedicated arithmetic circuitry

# **FP Logic Cell**

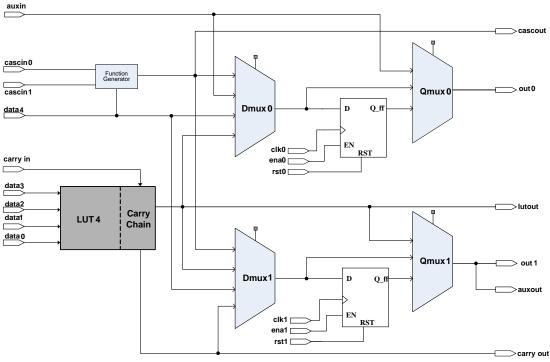

The architecture of the logic cell is shown in **Figure 2.2.1**. The logic cell contains a 4-input Look-Up table (LUT) and 2 logic paths: path0 and path1. Each path leads to a logic cell output that drives the routing fabric. The path1 output is also considered as an auxiliary output and can drive other components in AG1F1 devices, such as SPIO, PLL, and 8051 IP, etc. Path0 has a configurable option to receive the auxiliary input (which can be driven by the output of SPIO, PLL, and 8051, etc) and send it directly to the routing fabric. Each path can be configured independently as a registered path, either registered by a D-type flip-flop. Or, each path can be configured to bypass the registers if the logic cell represents a level of logic in a multi-level logic cone.

Figure 2.2.1 FP Logic Cell

The D-type flip-flop (DFF) in path0 use a clock, a reset, and a clock enable coming from that logic cell's clock bundle control unit, the DFF in path1 use a clock, a reset, and a clock enable that are independent of the global signals driving the path0 register elements. Clocks entering the logic cells trigger the DFF's on the rising-edge when the logic level is VDD. Resets entering the logic cells are asynchronous and active-high. Clock enables entering the logic cells are active-high. For more information on clock, reset and clock enable signal, see the *Clock Bundle Control Logic* section.

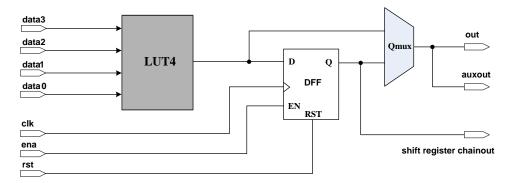

#### Normal Mode

The logic cell in normal mode contains a 4-input LUT and one DFF. User design can be synthesized friendly based on the basic cell. **Figure 2.2.2** shows the logic cell in normal mode.

Figure 2.2.2 Normal Mode

The 4-input LUT is used as a whole to realize a LUT4 function: the output of LUT4 can lead to routing fabric directly, or pass through DFF to routing fabric then drive the auxout. Output of the register can be the input of shift register in next level.

#### **Arithmetic Mode**

The arithmetic mode is idea for implementing adders and subtractors. The operands are 2 of the 4 inputs to the LUT4 function.

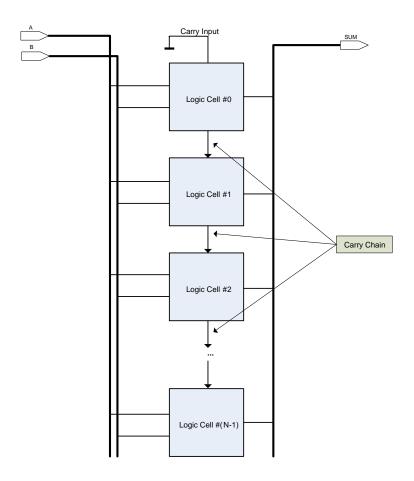

#### **Carry Chains**

An arbitrary number of contiguous logic cells can be configured to realize an adder or subtracter function with carry. **Figure 2.2.3** shows a series of logic cells configured as an adder.

Figure 2.2.3 FP Adder

Here, an N-length adder is configured where, at each logic cell, 2 of the 4 inputs to the LUT are allocated for the adder operands.

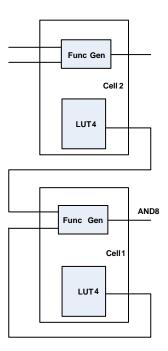

#### **Function Generator**

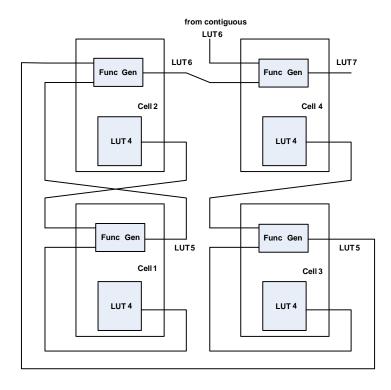

The Function Generator allows the logic cell to efficiently implement some logic functions of five or more inputs. Each individual Function Generator module can be configured to be AND, OR, XOR, or MUX. The two inputs for the AND, OR, and XOR gates are the LUT outputs as are the data inputs to the MUX. The "data4" input of the logic cell is used as the select input of the mux with the 0 select value choosing the "even" input and the 1 selecting the "odd" input. **Figure 2.2.4** describes an example of Dual logic cell functions: 8-input AND.

**Figure 2.2.4 Dual Logic Cell Function**

Figure 2.2.5 shows how to combine to LUT5, LUT6, and LUT7.

Figure 2.2.5 Combined LUTS

| Table 2.2.1   | lists 1 | the   | multiple | logic | cells | functions | supported | and | the | number | of |

|---------------|---------|-------|----------|-------|-------|-----------|-----------|-----|-----|--------|----|

| contiguous lo | ogic ce | lls r | equired. |       |       |           |           |     |     |        |    |

| Table 2.2.1 Multiple Logic Cell Functions |                       |  |  |  |  |

|-------------------------------------------|-----------------------|--|--|--|--|

| Function                                  | Number of Logic Cells |  |  |  |  |

| LUT5                                      | 2                     |  |  |  |  |

| LUT6                                      | 4                     |  |  |  |  |

| AND8                                      | 2                     |  |  |  |  |

| OR8                                       | 2                     |  |  |  |  |

| XOR8                                      | 2                     |  |  |  |  |

There are 4 special logic functions that require 2 adjacent logic cells. The logic cell at the even position (if cells are numbered starting with 0 at one end of the routing tree) produces the function result and takes the AND, OR, XOR, or MUX of the LUT results from the 2 logic cells involved.

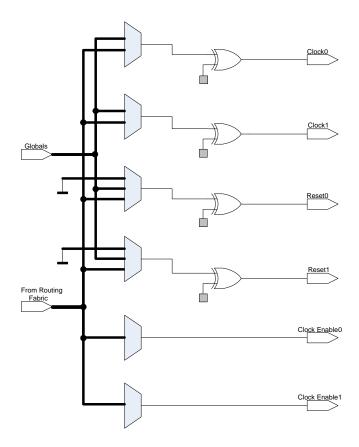

#### **Clock Bundle Control Logic**

A clock control unit exists for every 16 logic cells. This unit contains configurable muxes to select the source of the logic cell register clocks, resets, and enables for the 16 logic cells associated with it. **Figure 2.2.6** shows the logic composition of the clock control unit.

Figure 2.2.6 FP Clock Control

The squares in gray indicate configuration memory bits that control the selection of active logic level of the clocks and resets. The path0 clock, reset, and enables fan-out to 16 logic cells clustered near the clock control, driving the path0 registers in each of those cells. Likewise, the path1 clock, reset, and enables fan-out to those same logic cells but drive the path1 registers.

Each clock mux can be configured to select 1 out of 16 global signals and 4 routing fabric wires to use as logic cell register clocks. The same global signals can also be configured at each reset mux to use as logic cell register asynchronous resets. In addition, the reset muxes can select 1 out of 32 of the 36 available routing lines for resets generated by configured logic elsewhere in the core. The 16 upper-most selects at each reset mux are grounded. The clock enable muxes can select 1 out of 32 of the same 36 routing lines. The assignment of routing lines at each reset or clock enable mux varies.

Following each clock mux is an XOR gate that, under configuration, can reverse the polarity of the clock. By default, clocks are rising-edge triggering for DFF's. If the configuration bit at the XOR gate is set, the clock at that point becomes falling-edge triggering or active low. Similarly, each reset mux is followed by an XOR under configuration control for determining the active logic level of the selected reset. By default, resets are active-high. If the configuration bit is set, the reset at that point

becomes active-low. Clock enables are always active-high signals.

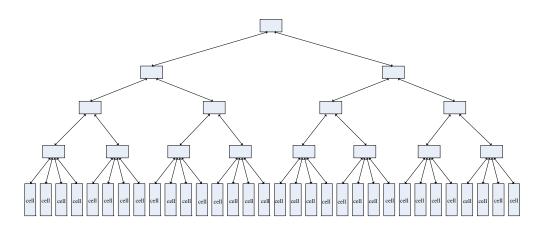

#### **Routing Architecture**

The FP core consists of an array of configurable logic cells and configurable routing muxes that interconnect the logic cells in a hierarchical architecture. The routing architecture resembles a tree where the logic cells are at the leaf nodes of the tree and the routing muxes are at all other nodes. Muxes propagating signals from the logic cells up the tree towards the apex are referred to as output (direction relative to logic cells) or up muxes. Muxes propagating signals towards the logic cells and away from the apex are referred to as input or down muxes.

Figure 2.2.7 illustrates the tree structure of the routing architecture.

Figure 2.2.7 FP Routing Tree

The illustration provides a rough view of the routing architecture and how signals are propagated from logic cell to logic cell. Depending on the distance of the receiving cell from the sending cell, signals are driven from the sender onto the routing fabric, typically through some number of up muxes until turning at a node to a down mux (turns shown as arcs in the diagram), then traversing through the same number of down muxes until the receiver is reached. The specific details are much more elaborate than what **Figure 2.2.7** can show, but the diagram does show the basic idea of how logic is interconnected in the FP core.

#### **Embedded Memory**

The AG1F1 embedded memory consists of columns of RAM8K memory blocks. Each RAM8K block can implement various types of memory with or without parity, including true dual-port and single-port RAM.

The RAM8K blocks support the following features:

- 9,216 RAM bits

- True dual-port memory

- Single-port memory

- Mixed clock mode

- Byte enable

- Parity bits

- Support the following DPRAM width configurations:  $8k \times 1$ ,  $9k \times 1$ ,  $4k \times 2$ ,  $2k \times 4$ ,  $1k \times 8$ ,  $1k \times 9$ ,  $512 \times 16$ ,  $512 \times 18$ ,  $256 \times 32$ ,  $256 \times 36$

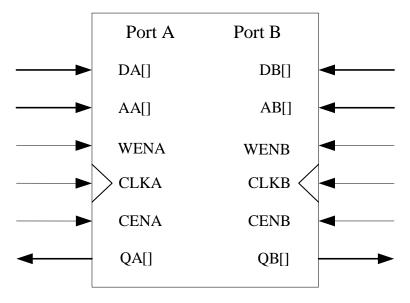

#### **Memory Modes**

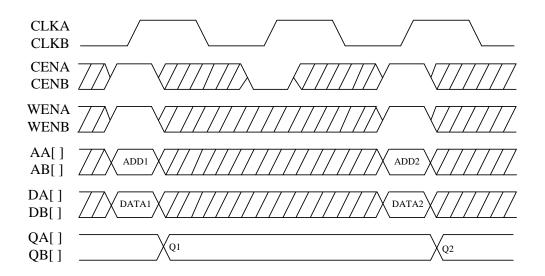

The RAM8K memory blocks include input registers that synchronize writes. Each RAM8K block offers a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. **Figure 2.2.8** shows true dual-port memory.

Figure 2.2.8 True Dual-port Memory Mode

The following tables summarize the ports and the function of true dual-port memory mode.

Table 2.2.2 shows a logic table of true dual-port memory mode function.

| Table 2.2.2 Lo | Table 2.2.2 Logic Table of True Dual-port Memory Mode Function |     |               |                                                                     |  |  |  |  |  |

|----------------|----------------------------------------------------------------|-----|---------------|---------------------------------------------------------------------|--|--|--|--|--|

|                | Inputs                                                         |     | Outputs       |                                                                     |  |  |  |  |  |

| CENA (B)       | WENA (B)                                                       | CLK | Status QA (B) |                                                                     |  |  |  |  |  |

| 0              | x                                                              | Х   | HOLD          | Data stored in the memory is retained.                              |  |  |  |  |  |

| 1              | 0                                                              | Ť   | READ          | Data is read from the memory location specified by the address bus. |  |  |  |  |  |

| 1              | 1                                                              | ↑   | WRITE         | DA (B)                                                              |  |  |  |  |  |

Table 2.2.3 shows the pin descriptions of true dual-port memory mode.

| Table 2.2.3 Pin De | Table 2.2.3 Pin Descriptions of True Dual-port Memory Mode |                                                                           |  |  |  |

|--------------------|------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| Name               | Туре                                                       | Description                                                               |  |  |  |

| AA (B)             | Input                                                      | Port A (B) Address.                                                       |  |  |  |

| DA (B)             | Input                                                      | Port A (B) Data Input.                                                    |  |  |  |

| QA (B)             | Output                                                     | Port A (B) Data Output.                                                   |  |  |  |

| WENA (B)           | Input                                                      | Port A (B) Write Enable. Data is written into the dual-port SRAM upon the |  |  |  |

|                    |                                                            | rising edge of the clock when both WENA (B) and CENA (B) are high.        |  |  |  |

| CENA (B)           | Input                                                      | Port A (B) Enable. When CENA (B) is high and WENA (B) is low, data read   |  |  |  |

|                    |                                                            | from the dual-port SRAM address AA (B) is available upon the next rising  |  |  |  |

|                    |                                                            | edge of CLKA (B). If CENA (B) is low, QA (B) retains its value.           |  |  |  |

| CLKA (B)           | Input                                                      | Port A (B) Clock.                                                         |  |  |  |

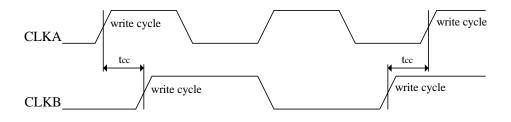

Read and write operation waveforms of true dual-port memory mode are shown in **Figure 2.2.9**.

#### Figure 2.2.9 True Dual-Port Memory Read-Write Waveform

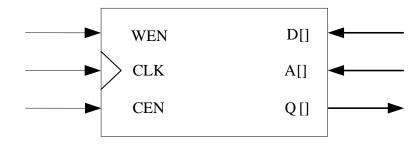

In addition to true dual-port memory mode, the RAM8K memory blocks support single-port memory modes. **Figure 2.2.10** shows single-port memory mode of AG1F1

RAM8K memory blocks.

Figure 2.2.10 Single-port Memory Mode

Figure 2.2.11 gives the waveforms of read and write operations in this mode.

Figure 2.2.11 Single-Port Memory Read-Write Waveform

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times$  1 mode at port A and read out in  $\times$  16 mode from port B.

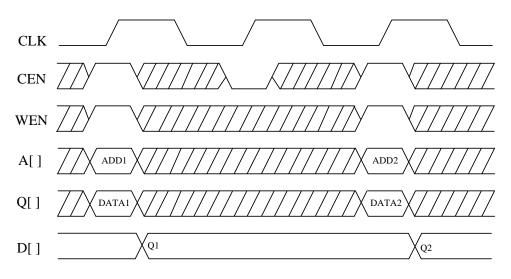

#### **Conflict Avoidance**

For dual-port memory modes, both ports can access any memory address at any time. When both ports access the same address, the read and write behaviour should observe certain clock timing restrictions. These restrictions are adaptable to both synchronous and asynchronous clock.

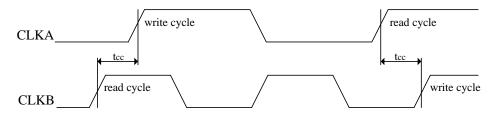

Figure 2.2.12, Figure 2.2.13, and Figure 2.2.14 illustrate the clock timings that may cause conflict in read and write operations with dual-port memory modes.

Figure 2.2.12 Dual-port memory Write-Read Clock Timing

Figure 2.2.13 Dual-port memory Read-Write Clock Timing

#### Figure 2.2.14 Dual-port memory Write-Write Clock Timing

#### Note for Figure 2.2.12 to Figure 2.2.14:

(1) tcc means clock collision. The Min value of it is 0.748 ns based on the conditions of temperature =  $25 \,^{\circ}$ C, power supply =  $1.2 \,$ V.

**Table 2.2.4** shows read and write behaviour during clock conflicts, when both ports access the same address.

| Table 2.2.4 Dual-port Memory Read and W           | /rite Behaviour whei         | n accessing the same address |

|---------------------------------------------------|------------------------------|------------------------------|

| Action                                            | Condition                    | Behaviour                    |

| Write from one port then read from the other port | t <sub>cc</sub> is satisfied | Write OK                     |

|                                                   | (see Figure 2.2.12)          | D-to-Q write through OK      |

|                                                   |                              | Read (new data) OK           |

|                                                   | $t_{cc}$ is not satisfied    | Write fails                  |

|                                                   | (see Figure 2.2.12)          | D-to-Q write through OK      |

|                                                   |                              | Read fails                   |

| Read from one port then write from the other port | t <sub>cc</sub> is satisfied | Write OK                     |

|                                                   | (see Figure 2.2.13)          | D-to-Q write through OK      |

|                                                   |                              | Read (old data) OK           |

|                                                   | $t_{cc}$ is not satisfied    | Write fails                  |

| Table 2.2.4 Dual-port Memory Read and Write Behaviour when accessing the same address |                           |                                         |  |  |  |

|---------------------------------------------------------------------------------------|---------------------------|-----------------------------------------|--|--|--|

| Action                                                                                | Condition                 | Behaviour                               |  |  |  |

|                                                                                       | (see Figure 2.2.13)       | D-to-Q write through OK                 |  |  |  |

|                                                                                       |                           | Read fails                              |  |  |  |

| Write from one port then write from the other port                                    | $t_{cc}$ is satisfied     | Both writes OK (second write overwrites |  |  |  |

|                                                                                       | (see Figure 2.2.14)       | first write)                            |  |  |  |

|                                                                                       |                           | D-to-Q write through OK                 |  |  |  |

|                                                                                       | $t_{cc}$ is not satisfied | Both writes fail                        |  |  |  |

|                                                                                       | (see Figure 2.2.14)       | D-to-Q write through OK                 |  |  |  |

| Read from one port then read from the other port                                      | No restriction            | Both reads OK                           |  |  |  |

### **Parity Bit Support**

The RAM8K blocks support a parity bit for each byte. The parity bit, along with internal FP Logic cell, can implement parity checking for error detection to ensure data integrity. You can also use parity-size data words to store user-specified control bits. Byte enables are also available for data input masking during write operations.

### **Memory Configuration Sizes**

The memory address depths and output widths can be configured as  $8,192 \times 1, 9,216 \times 1, 4,096 \times 2, 2,048 \times 4, 1,024 \times 8$  (or  $1,024 \times 9$  bits),  $512 \times 16$  (or  $512 \times 18$  bits), and  $256 \times 32$  (or  $256 \times 36$  bits).

Table 2.2.5 summarizes the possible RAM8K block configurations.

|          |              | Port B       |              |              |              |              |              |              |              |              |  |

|----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

| Port A   | 8K ×         | 4K ×         | 2K ×         | 1K ×         | 512 ×        | 256 ×        | 9 k          | 1K           | 512 ×        | 256 ×        |  |

|          | 1            | 2            | 4            | 8            | 16           | 32           | × 1          | × 9          | 18           | 36           |  |

| 8K × 1   | $\checkmark$ |              |              |              |              |              |              |              |              |              |  |

| 4K × 2   |              | $\checkmark$ |              |              |              |              |              |              |              |              |  |

| 2K × 4   |              |              | $\checkmark$ |              |              |              |              |              |              |              |  |

| 1K × 8   |              |              |              | $\checkmark$ |              |              |              |              |              |              |  |

| 512 × 16 |              |              |              |              | $\checkmark$ |              |              |              |              |              |  |

| 256 × 32 |              |              |              |              |              | $\checkmark$ |              |              |              |              |  |

| 9K × 1   |              |              |              |              |              |              | $\checkmark$ |              |              |              |  |

| 1K × 9   |              |              |              |              |              |              |              | $\checkmark$ |              |              |  |

| 512 × 18 |              |              |              |              |              |              |              |              | $\checkmark$ |              |  |

| 256 × 36 |              |              |              |              |              | T            |              |              |              | $\checkmark$ |  |

## **Byte Enables**

RAM8K blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value.

Table 2.2.6 summarizes the byte selection.

| Table 2.2.6 Byte Enable for RAM8K Blocks |       |        |  |  |  |  |

|------------------------------------------|-------|--------|--|--|--|--|

| byteena[30] datain x18 datain x36        |       |        |  |  |  |  |

| [0] = 1                                  | [80]  | [80]   |  |  |  |  |

| [1] = 1                                  | [179] | [179]  |  |  |  |  |

| [2] = 1                                  | -     | [2618] |  |  |  |  |

| [3] = 1                                  | -     | [3527] |  |  |  |  |

# PLL

FP-MCU AG1F1 PLL provides general-purpose clocks with clock multiplication and division. AG1F1 device contains one PLL.

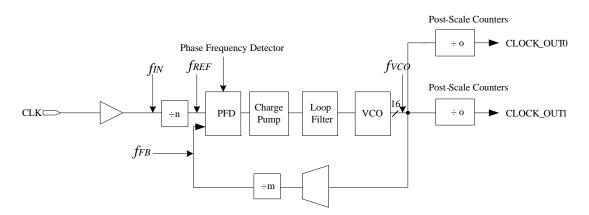

**Table 2.2.7** shows the PLL features in AG1F1. Figure 2.2.15 shows FP-MCU AG1F1PLL.

| Table 2.2.7 PLL Features        |                    |  |  |  |  |

|---------------------------------|--------------------|--|--|--|--|

| Parameter                       | Value              |  |  |  |  |

| Input reference frequency range | 2MHz - 50MHz       |  |  |  |  |

| Output frequency range          | 2.34 MHz - 450 MHz |  |  |  |  |

| VCO output frequency range      | 150MHz - 450MHz    |  |  |  |  |

| Reference divider values        | 1 - 64             |  |  |  |  |

| Feedback divider values         | 1 - 4096           |  |  |  |  |

| Output divider values           | 1 - 64             |  |  |  |  |

| Output phase separation         | 6.25% VCO cycle    |  |  |  |  |

Following is the FP-MCU AG1F1 PLL diagram.

Figure 2.2.15 AG1F1 PLL

#### **Clock Multiplication and Division**

FP-MCU AG1F1 PLL provides clock synthesis for PLL two output ports, both using m/ (n x o) scaling factors. The input clock is divided by a reference divider, *n*, and is then multiplied by the *m* feedback factor. The control loop drives the VCO to match  $f_{IN} \times (m/n)$ . Then the port0 and port1 have a post-scale counter to divide down the high-frequency VCO. The frequency of port1, port0 is divided by a post-scale divider, o.

PLL has one reference divider, n, that can range in value from 1 to 64. PLL also has one multiply divider, m, which can range in value from 1 to 4096. The pose-scale divider has a value range from 1 to 64.

#### **PLL Control Signals**

There are three control signals: RESET, PWRDN, and BYPASS. You can use these signals to control PLL resynchronization and the ability to gate PLL output clocks for low-power applications.

When the RESET signal is high, the PLL counter will reset, clearing the PLL output and placing the PLL out of lock. And it will be in resting mode when PWRDN is driven high. PLL signal will be bypassed if BYPASS goes high. At this time, the output signal equals the input signal.

Datasheet

## Introduction

The Agate 8051 processor core is binary compatible to the well known 8051 processor from Intel. It offers faster program execution compared to the original 8051 devices since the processor's architecture have been optimized. In Agate 8051, instructions need only one to four clock cycles.

# **Features**

- Fully synchronous circuit design, single clock

- Instruction set compatible to the industry standard 8051 microcontroller with new optimized architecture. Only one to four clock cycles per one OP code

- 128 bytes scratchpad RAM

- 8K bytes internal Data RAM

- 32K bytes internal Program RAM

- Separate address spaces for code and data

- 4, 8-bit wide, output ports (byte or bit addressable)

- 4, 8-bit wide, input ports (byte or bit addressable)

- Two 16-bit Timer/Counters

- Five Interrupt Sources

- Programmable Serial Channel

- Average performance is about (0.5~1) MIPS/MHz, which is about 8.4 times against original 8051

- Maximum working frequency is about 50 MHz

- Programmable Watchdog Timer

- ISD51 supported

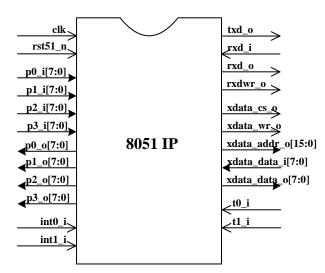

# **Model and Signals**

Figure 2.3.1 8051 Model

All signals are connected with FP directly. Any application can be implemented with FP logic expediently. See description of signals definition in **Table 2.3.1**.

| le 2.3.1 Sig | nals Definitio | on (Part i)                   |                                   |  |  |

|--------------|----------------|-------------------------------|-----------------------------------|--|--|

| Port         | Width          | Direction                     | Description                       |  |  |

| clk          | 1              | input                         | Clock                             |  |  |

| rst51_n      | 1              | input                         | input Reset signal, low active    |  |  |

| p0_i         | 8              | input                         | input Parallel port 0 input       |  |  |

| p1_i         | 8              | input                         | input Parallel port 1 input       |  |  |

| p2_i         | 8              | input                         | input Parallel port 2 input       |  |  |

| p3_i         | 8              | input Parallel port 3 input   |                                   |  |  |

| p0_o         | 8              | output Parallel port 0 output |                                   |  |  |

| p1_o         | 8              | output                        | output Parallel port 1 output     |  |  |

| p2_o         | 8              | output                        | Parallel port 2 output            |  |  |

| p3_o         | 8              | output                        | Parallel port 3 output            |  |  |

| int0_i       | 1              | input                         | External interrupt 0 input        |  |  |

| int1_i       | 1              | input                         | External interrupt 1 input        |  |  |

| txd_o        | 1              | output                        | Serial port output (transmit)     |  |  |

| rxd_i        | 1              | input                         | input Serial port input (receive) |  |  |

| Port         | Width | Direction                                | Description                             |  |  |

|--------------|-------|------------------------------------------|-----------------------------------------|--|--|

| 1 011        | main  | Direction                                | •                                       |  |  |

| rxd_o        | 1     | output                                   | Serial port output (transmit in mode 0) |  |  |

| rxdwr_o      | 1     | output Serial port output enable (for RX |                                         |  |  |

| xdata_cs_o   | 1     | output                                   | Data memory extension chip selection    |  |  |

| xdata_wr_o   | 1     | output                                   | Data memory extension write strob       |  |  |

| xdata_addr_o | 16    | output                                   | Data memory extension address           |  |  |

| xdata_data_i | 8     | input                                    | Data memory extension read data         |  |  |

| xdata_data_o | 8     | output                                   | Data memory extension write data        |  |  |

| t0_i         | 1     | input                                    | Timer 0 external clock input            |  |  |

| t1_i 1 input |       |                                          | Timer 1 external clock input            |  |  |

Note:

(1) Inputs and outputs of port 0~3 are separated.

#### **Memory Organization**

The Agate 8051 uses a Harvard Architecture with separate address spaces for program and data memory. Memory in the Agate 8051 is organized into three distinct areas:

- 256 bytes Internal Data memory space (SFRs and 128 bytes scratchpad RAM)

- Up to 64K bytes External Data memory space (8K bytes SRAM on-chip)

- 32K bytes Program memory space (All on-chip)

#### **Internal Data Memory**

The Agate 8051 contains 128 bytes of general SRAM data memory and 128 bytes of Special Function Register (SFR) space. The total internal data memory space is 256 bytes as shown in **Figure 2.3.2**.

- The upper 128 bytes contain the Special Function Registers. This area is accessible only by direct addressing. See Register Space and Register Description sections for detail description.

- The lower 128 bytes contain work registers and bit-addressable memory. The lower 48 bytes of this area of memory space are further divided as follows:

- ✓ The lower 32 bytes (00h-1Fh) form four banks of eight registers (R0-R7). The RS0 and RS1 bits in the Program Status Word register (PSW) select which bank is currently in use.

✓ The next 16 bytes (20h-2Fh) form a block of bit-addressable memory space, covering the bit address range 00h-7Fh.

| FFh        |                   |    |    |        |      |    |    |    |  |  |

|------------|-------------------|----|----|--------|------|----|----|----|--|--|

| 80h        | SFR (Direct Only) |    |    |        |      |    |    |    |  |  |

| 7Fh        | ,                 |    |    |        |      |    |    |    |  |  |

|            |                   |    |    | Direct | RAM  |    |    |    |  |  |

| 30h        |                   |    |    |        |      |    |    |    |  |  |

| 2Fh        | 7F                | 7E | 7D | 7C     | 7B   | 7A | 79 | 78 |  |  |

| 2Eh        | 77                | 76 | 75 | 74     | 73   | 72 | 71 | 70 |  |  |

| 2Dh        | 6F                | 6E | 6D | 6C     | 6B   | 6A | 69 | 68 |  |  |

| 2Ch        | 67                | 66 | 65 | 64     | 63   | 62 | 61 | 60 |  |  |

| 2Bh        | 5F                | 5E | 5D | 5C     | 5B   | 5A | 59 | 58 |  |  |

| 2Ah        | 57                | 56 | 55 | 54     | 53   | 52 | 51 | 50 |  |  |

| 29h        | 4F                | 4E | 4D | 4C     | 4B   | 4A | 49 | 48 |  |  |

| 28h        | 47                | 46 | 45 | 44     | 43   | 42 | 41 | 40 |  |  |

| 27h        | 3F                | 3E | 3D | 3C     | 3B   | 3A | 39 | 38 |  |  |

| 26h        | 37                | 36 | 35 | 34     | 33   | 32 | 31 | 30 |  |  |

| 25h        | 2F                | 2E | 2D | 2C     | 2B   | 2A | 29 | 28 |  |  |

| 24h        | 27                | 26 | 25 | 24     | 23   | 22 | 21 | 20 |  |  |

| 23h        | 1F                | 1E | 1D | 1C     | 1B   | 1A | 19 | 18 |  |  |

| 22h        | 17                | 16 | 15 | 14     | 13   | 12 | 11 | 10 |  |  |

| 21h        | 0F                | 0E | 0D | 0C     | 0B   | 0A | 09 | 08 |  |  |

| 20h        | 07                | 06 | 05 | 04     | 03   | 02 | 01 | 00 |  |  |

| 1Fh        |                   |    |    |        |      |    |    |    |  |  |

| 4.01-      |                   |    |    | Ban    | ik 3 |    |    |    |  |  |

| 18h<br>17h |                   |    |    |        |      |    |    |    |  |  |

| 1711       |                   |    |    | Ban    | k 2  |    |    |    |  |  |

| 10h        |                   |    |    | Dan    | _    |    |    |    |  |  |

| 0Fh        |                   |    |    |        |      |    |    |    |  |  |

| 0.01       |                   |    |    | Ban    | ik 1 |    |    |    |  |  |

| 08h<br>07h |                   |    |    |        |      |    |    |    |  |  |

| 0/11       |                   |    |    | Ban    | k 0  |    |    |    |  |  |

| 00h        |                   |    |    |        | •    |    |    |    |  |  |

Figure 2.3.2 256 bytes Internal Data Memory Space

# **External Data Memory**

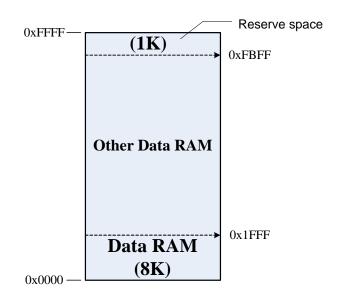

The Agate 8051 supports a regular linear address space for up to 64K bytes data memory space. The external Data memory space can be accessed directly, through the 16 bit Data Pointer Register (DPTR).

#### Figure 2.3.3 64K Bytes External Data Memory Space

The External Data memory space is divided as **Figure 2.3.3**. The lower 8K Data RAM is on-chip SRAM. For extension, other Data RAM must be assigned through FP connection.

| Table 2.3.2 External Data Memory Address Space Assignment |                                                                                                                      |  |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Address Space Description                                 |                                                                                                                      |  |  |  |  |

| 0x0000 ~ 0x1FFF                                           | Internal 8K Data RAM space                                                                                           |  |  |  |  |

| 0x2000 ~ 0xFBFF                                           | Other Extension Data RAM space. User can add available RAM size through FP connected other Internal or External RAM. |  |  |  |  |

| 0xFC00 ~ 0xFFFF                                           | Reserved                                                                                                             |  |  |  |  |

Note:

(1) Watchdog register address is included in 0xFC00 ~ 0xFFFF address space.

#### **Program Memory**

Now the Agate 8051 supports a regular linear address space for 32K bytes program memory space. And all the 32K bytes program memory is implemented by on-chip SRAM. The program memory space can be accessed directly.

### **Data RAM Extension**

As shown in **Figure 2.3.3**, when the Data RAM address is upper than 8K space, the read/write operation will occur on data memory extension port (the ones with prefix

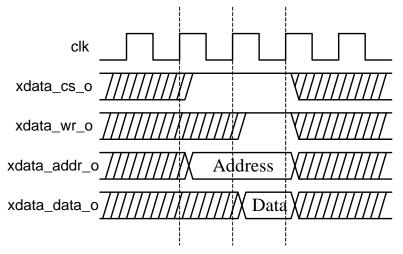

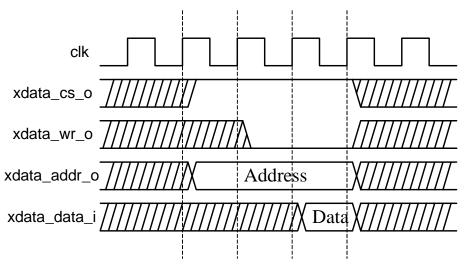

xdata in **Table 2.3.1**). Use OP code 'MOVX @DPTR, A' or 'MOVX @RI, A' for write operation, and use 'MOVX A, @DPTR' or 'MOVX A, @RI' for read operation. The write and read operation waveforms are shown as below.

Figure 2.3.4 Extension Port Write Operation Waveform

Figure 2.3.5 Extension Port Read Operation Waveform

## **Register Space**

#### **Register Space Assignment**

The Agate 8051 uses Special Function Registers (SFRs) to control and monitor peripherals and their modes. The SFRs reside in the locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This allows a program to modify a particular bit without changing the others. The bit-addressable SFRs are those with addresses that end in 0 or 8. The list of the SFRs is shown in **Table 2.3.3**

| Table 2.3 | .3 Special | Function R | egister (SF | R) Assign | ment |     |      |

|-----------|------------|------------|-------------|-----------|------|-----|------|

| F8h       |            |            |             |           |      |     |      |

| F0h       | В          |            |             |           |      |     |      |

| E8h       |            |            |             |           |      |     |      |

| E0h       | ACC        |            |             |           |      |     |      |

| D8h       |            |            |             |           |      |     |      |

| D0h       | PSW        |            |             |           |      |     |      |

| C8h       |            |            |             |           |      |     |      |

| C0h       |            |            |             |           |      |     |      |

| B8h       | IP         |            |             |           |      |     |      |

| B0h       | P3         |            |             |           |      |     |      |

| A8h       | IE         |            |             |           |      |     |      |

| A0h       | P2         |            |             |           |      |     |      |

| 98h       | SCON       | SBUF       |             |           |      |     |      |

| 90h       | P1         |            |             |           |      |     |      |

| 88h       | TCON       | TMOD       | TL0         | TL1       | TH0  | TH1 |      |

| 80h       | PO         | SP         | DPL         | DPH       |      |     | PCON |

with eight locations per row. Empty locations indicate that these are no SFR registers at these locations.

The Agate 8051 system offers a programmable Watchdog Timer (WDT) for fail-safe protection against software deadlock and automatic recovery. WDT registers are not in SFR space. **Table 2.3.4** shows the corresponding address assignment.

| Table 2.3.4 WDT Register Assignment |         |

|-------------------------------------|---------|

| FC10h                               | WDTC    |

| FC11h                               | WDT_INT |

# **Register Reset Value**

| Table 2.3.5 Contents of the Registers after Reset |             |               |             |

|---------------------------------------------------|-------------|---------------|-------------|

| Register Name                                     | Reset Value | Register Name | Reset Value |

| ACC                                               | 0000_0000   | PO            | 1111_1111   |

| В                                                 | 0000_0000   | P1            | 1111_1111   |

| PSW                                               | 0000_0000   | P2            | 1111_1111   |

| SP                                                | 0000_0111   | P3            | 1111_1111   |

| IP                                                | 0000_0000   | DPH           | 0000_0000   |

| IE                                                | 0000_0000   | DPL           | 0000_0000   |

| TMOD                                              | 0000_0000   | PCON          | 0000_0000   |

| TCON                                              | 0000_0000   | WDTC          | 0000_0000   |

| SBUF                                              | 0000_0000   | WDT_INT       | 0000_0000   |

| SCON                                              | 0000_0000   | -             | _           |

# **Register Description**

#### Accumulator Register (ACC)

Most instructions use the Accumulator to hold the operand. The mnemonics for accumulator-specific instructions, however, refer to the accumulator simply as A.

#### **B** Register

To improve the performance of Agate 8051, DIV and MUL commands are not implemented. So the B register will be only used as a scratch-pad register to hold temporary data.

#### Program Status Word Register (PSW)

The PSW register contains program status information as detailed in **Table 2.3.6**. Note the contents of (RS1, RS0) enable the working register banks as shown in **Table 2.3.7**.

| Table2.3. 6 Program Status Word Register (PSW) |        |                                                                              |

|------------------------------------------------|--------|------------------------------------------------------------------------------|

| Bit                                            | Symbol | Function                                                                     |

| PSW.7                                          | CY     | Carry flag                                                                   |

| PSW.6                                          | AC     | Auxiliary Carry flag                                                         |

| PSW.5                                          | F1     | Flag 0 available to the user for general purpose                             |

| PSW.4                                          | RS1    | Register bank select control bit 1 (See Table 2.3.7)                         |

| PSW.3                                          | RS0    | Register bank select control bit 0 (See Table 2.3.7)                         |

| PSW.2                                          | OV     | Overflow flag                                                                |

| PSW.1                                          | F0     | User definable flag                                                          |

| PSW.0 P                                        | Р      | Parity flag. Set / Cleared by hardware each instruction cycle to indicate an |

|                                                |        | odd / even number of '1' bits in the accumulator                             |

| Table | Table2.3.7 Bank Selection |               |         |

|-------|---------------------------|---------------|---------|

| RS1   | RS0                       | Register Bank | Address |

| 0     | 0                         | Bank 0        | 00H-07H |

| 0     | 1                         | Bank 1        | 08H-0FH |

| 1     | 0                         | Bank 2        | 10H-17H |

| 1     | 1                         | Bank 3        | 18H-1FH |

#### **Stack Pointer Register (SP)**

The Stack Pointer is a 1-byte register. It is initialized to 07H after reset, and this causes the stack to begin at location 08H. It is incremented before data is stored during PUSH and CALL executions.

#### **Data Pointer Registers (DPL and DPH)**

The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

#### Ports 0 to 3 Registers

P0, P1, P2 and P3 are the SFR latches of Ports 0, 1, 2, 3. The contents of the SFR can be access through corresponding SFR access interface.

#### **Interrupt Registers**

The Agate 8051 provides five interrupt sources.

The External Interrupts INTO and INT1 can be either level-activated or transition-activated, depending on corresponding register setting. The flags that actually generate these interrupts are bits IEO and IE1. These flags will be cleared by hardware when the service routine is vectored to only if the interrupt was transition-activated. If the interrupt is level-activated, the external requesting source will control the request flag, rather than the on-chip hardware.

The Timer 0 and Timer 1 Interrupts are indicated as bits TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers. The flag will be cleared by the on-chip hardware when the service routine is vectored to.

The Serial Port Interrupt is generated by the logic OR of RI and TI. These flags can only be cleared by software.

Special Function Register IP, IE contains the control and status bits for the interrupt system. The detail description about them is shown as below.

| Table 2.3.8 Interrupt Enable register (IE) |        |                                                                                  |

|--------------------------------------------|--------|----------------------------------------------------------------------------------|

| Bit                                        | Symbol | Function                                                                         |

|                                            |        | Enable or disable all interrupts.                                                |

| IE.7                                       | EA     | If EA = 0, no interrupt will be acknowledge. If EA = 1, each interrupt source is |

|                                            |        | individually enabled or disabled by setting or clearing its enable bit.          |

| IE.6                                       | -      | Not implemented, reserved for future use                                         |

| IE.5                                       | -      | Not implemented, reserved for future use                                         |

| IE.4                                       | ES     | Enable or disable the Serial port interrupt                                      |

| IE.3                                       | ET1    | Enable or disable the Timer 1 overflow interrupt                                 |

| IE.2                                       | EX1    | Enable or disable External Interrupt 1                                           |

| IE.1                                       | ET0    | Enable or disable the Timer 0 overflow interrupt                                 |

| IE.0                                       | EX0    | Enable or disable External Interrupt 0                                           |

| Table 2.3.9 Interrupt Priority register (IP) |        |                                                   |

|----------------------------------------------|--------|---------------------------------------------------|

| Bit                                          | Symbol | Function                                          |

| IP.7                                         | -      | Not implemented, reserved for future use          |

| IP.6                                         | -      | Not implemented, reserved for future use          |

| IP.5                                         | -      | Not implemented, reserved for future use          |

| IP.4                                         | PS     | Defines the Serial Port interrupt priority level. |

| IP.3                                         | PT1    | Defines the Timer 1 interrupt priority level.     |

| IP.2                                         | PX1    | Defines the External Interrupt 1 priority level.  |

| IP.1                                         | PT0    | Defines the Timer 0 interrupt priority level.     |

| IP.0                                         | PX0    | Defines the External Interrupt 0 priority level.  |

If two requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced, this polling sequence is a second priority structure defined as follows in **Table 2.3.10**.

| Table 2.3.10 Interrupt Priority Level |          |                |

|---------------------------------------|----------|----------------|

| Number                                | Source   | Priority Level |

| 1                                     | IE0      | Highest        |

| 2                                     | TF0      | Ì              |

| 3                                     | IE1      |                |

| 4                                     | TF1      |                |

| 5                                     | RI or TI | Lowest         |

### **Timers/Counters Registers**

The Agate 8051 has two 16-bit timer/counter registers: Timer 0 and Timer 1. Both can be configured for counter or timer operations.

In timer mode, the register is incremented every 12 clock cycles.

In counter mode, a sample operation happens in every 12 clock cycles. The register is incremented when the falling edge is observed at the corresponding input pin T0 or T1. Since it takes 24 clock cycles to recognize a 1-to-0 event, the maximum input count rate is 1/24 of the external clock frequency. There are no restrictions on the duty cycle, however to ensure proper recognition of 0 or 1 state, an input should be stable for at least 12 clock cycles.

Four operating modes can be selected for Timer 0 and Timer 1. Two Special Function Registers (TMOD and TCON) are used to select the appropriate mode.

Special Function Register TH0, TL0, TH1, TL1, TCON, TMOD contains the control and status bits for the timer/counters. The detailed description about them is shown as below.

| Table 2.3.11 Timer 0 High Byte register (TH0) |                      |

|-----------------------------------------------|----------------------|

| Bit                                           | Function             |

| TH0[7:0]                                      | High Byte of Timer 0 |

| Table 2.3.12. Timer 0 Low Byte register (TL0) |                     |

|-----------------------------------------------|---------------------|

| Bit                                           | Function            |

| TL0[7:0]                                      | Low Byte of Timer 0 |

| Table 2.3.13 Timer 1 High Byte register (TH1) |                      |

|-----------------------------------------------|----------------------|

| Bit                                           | Function             |

| TH1[7:0]                                      | High Byte of Timer 1 |

| Table 2.3.14 Timer 1 Low Byte register (TL1) |                     |

|----------------------------------------------|---------------------|

| Bit                                          | Function            |

| TL1[7:0]                                     | Low Byte of Timer 1 |

| Table 2.3.15 Timer/Counter Control register (TCON) (Part i) |                                                                                  |                                                                                  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Bit                                                         | Symbol                                                                           | Function                                                                         |

| TCON.7 TF1                                                  | TE1                                                                              | Timer/Counter 1 overflow flag. Set by hardware when Timer/Counter 1 overflows.   |

|                                                             | Cleared by hardware as processor vectors to the interrupt service routine        |                                                                                  |

| TCON.6 TR1                                                  | Timer/Counter 1 Run control bit. Set/Cleared by software to turn Timer/Counter 1 |                                                                                  |

|                                                             | ON/OFF.                                                                          |                                                                                  |

| TCON.5                                                      | TFO                                                                              | Timer/Counter 0 overflow flag. Set by hardware when Timer/Counter 0 overflows.   |

| TCON.5 TF0                                                  | Cleared by hardware as processor vectors to the interrupt service routine        |                                                                                  |

| TCON.4 TRO                                                  | TDO                                                                              | Timer/Counter 0 Run control bit. Set/Cleared by software to turn Timer/Counter 0 |

|                                                             | IKU                                                                              | ON/OFF.                                                                          |

| Table 2.3.15 Timer/Counter Control register (TCON)       (Part ii) |        |                                                                                    |  |  |  |

|--------------------------------------------------------------------|--------|------------------------------------------------------------------------------------|--|--|--|

| Bit                                                                | Symbol | Function                                                                           |  |  |  |

| TCON.3                                                             | IE1    | External Interrupt 1 edge flag. Set by hardware when an edge/level is detected on  |  |  |  |

|                                                                    |        | INT1_i. Cleared by hardware when the service routine is vectored only if the       |  |  |  |

|                                                                    |        | interrupt was edge triggered. Otherwise, it will follow the pin.                   |  |  |  |

| TCON.2                                                             | IT1    | Interrupt 1 type control bit. Set/cleared by software to specify falling edge/high |  |  |  |

|                                                                    |        | level triggered External Interrupt.                                                |  |  |  |

| TCON.1                                                             | IE0    | External Interrupt 0 edge flag. Set by hardware when an edge/level is detected on  |  |  |  |

|                                                                    |        | INT1_i. Cleared by hardware when the service routine is vectored only if the       |  |  |  |

|                                                                    |        | interrupt was edge triggered. Otherwise, it will follow the pin.                   |  |  |  |

| TCON.0                                                             | ІТО    | Interrupt 0 type control bit. Set/cleared by software to specify falling edge/high |  |  |  |

|                                                                    |        | level triggered External Interrupt.                                                |  |  |  |

| Table 2.3.16 Timer/Counter Mode Control register (TMOD) |        |                                                                                |  |  |  |

|---------------------------------------------------------|--------|--------------------------------------------------------------------------------|--|--|--|

| Bit                                                     | Symbol | Function                                                                       |  |  |  |

|                                                         |        | When TR1 (in TCON) is set and GATE = 1, Timer/Counter1 will run only when      |  |  |  |

| TMOD.7                                                  | GATE   | INT1 pin is high (hardware control).                                           |  |  |  |

|                                                         |        | When GATE = 0, Timer/Counter1 will run only when TR1 = 1 (software control).   |  |  |  |

| TMOD.6                                                  | С/Т    | Timer or Counter selector for Timer 1. Clear for Timer operation (input from   |  |  |  |

|                                                         |        | internal system clock). Set for Counter operation (input from t1_i input pin). |  |  |  |

| TMOD.5                                                  | M1     | Timer/Counter 1 mode select bit 1.                                             |  |  |  |

| TMOD.4                                                  | MO     | Timer/Counter 1 mode select bit 0.                                             |  |  |  |

|                                                         | GATE   | When TR0 (in TCON) is set and GATE = 1, Timer/Counter0 will run only when      |  |  |  |

| TMOD.3                                                  |        | INT0 pin is high (hardware control).                                           |  |  |  |

|                                                         |        | When GATE = 0, Timer/Counter0 will run only when TR0 = 1 (software control).   |  |  |  |

| TMOD.2                                                  | C/T    | Timer or Counter selector for Timer 0. Clear for Timer operation (input from   |  |  |  |

|                                                         |        | internal system clock). Set for Counter operation (input from t0_i input pin). |  |  |  |

| TMOD.1                                                  | M1     | Timer/Counter 0 mode select bit 1.                                             |  |  |  |

| TMOD.0                                                  | M0     | Timer/Counter 0 mode select bit 0.                                             |  |  |  |

There are four timer/counter modes supported for the two timers. The mode is determined by the state of bits M1 and M0 in the TMOD register. The set method is shown in **Table 2.3.17**.

| Table 2.3.17 Mode Set Method |    |                    |  |  |  |

|------------------------------|----|--------------------|--|--|--|

| M1                           | MO | Timer/Counter Mode |  |  |  |

| 0                            | 0  | Mode 0             |  |  |  |

| 0                            | 1  | Mode 1             |  |  |  |

| 1                            | 0  | Mode 2             |  |  |  |

| 1                            | 1  | Mode 3             |  |  |  |

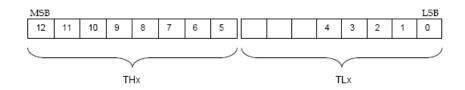

• Timer/Counter Mode 0

When in Mode 0, the Timer/Counter is set to 13 bits. If the Timer/Counter is enabled, it will count from its set value (set by software) up to 1FFFh, at which point TFx is set to 1 to indicate overflow. Hardware then resets this value to 0 after TimerX Interrupt Service routine is processed.

When overflow occurs, the Timer/Counter will roll over to 0000h and continue to count up to 1FFFh, at which point TFx is set to 1 once again. This cycle continues until the Timer/Counter is disabled.

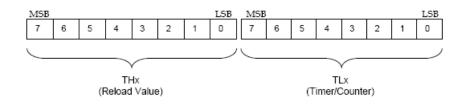

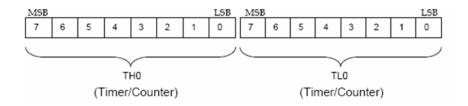

Figure 2.3.6 Timer/Counter in Mode 0

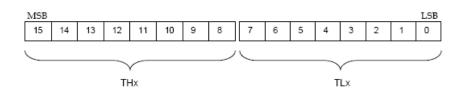

• Timer/Counter Mode 1

When in Mode 1, the Timer/Counter is set to 16 bits. The operation of the Timer/Counter in this mode is comparable to that in Mode 0. However, for this mode all 8 bits of the TLx register are used and therefore, the maximum value before overflow is FFFFh.

Figure 2.3.7 Timer/Counter in Mode 1

• Timer/Counter Mode 2

When in Mode 2, the Timer/Counter is set to 8 bits. This mode enables the Timer/Counter to be reloaded with its set value immediately after overflow. The two timing registers THx and TLx are used differently.

In this mode, THx hold the reload value, which is copied to TLx after overflow is detected, whereas TLx is the 8-bit dedicated Timer/Counter.

• Timer/Counter Mode 3

When Timer/Counter 0 works on Mode 3, the TH0 and TL0 registers operate independently of each other as follows:

TL0 operates as an 8-bit Timer/Counter, controlled by Timer/Counter 0 mode control bits TMOD.3 and TMOD.2.

TH0 operates as a dedicated 8-bit Timer, controlled by Timer/Counter 1 mode control bits TMOD.7 and TMOD.6, with no external gate control.

In this condition, Timer/Counter 1 can be defined as Mode 0, Mode 1 or Mode 2. But the interrupt TF1 cannot be used by Timer/Counter 1.

Figure 2.3.9 Timer/Counter in Mode 3

#### **Serial Interface Registers**

The serial interface provides both synchronous (In mode 0) and asynchronous (In mode 1, 2, 3) modes. Asynchronous transmission and reception can occur simultaneously, even at different baud rates.

It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost). The serial port receive and transmit registers are both accessed at Special Function Register SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses the receive register.

#### Four Modes of Serial Port Operation

• Mode 0

When in mode 0, Serial data enter and exit through rxd\_i and rxd\_o. The txd\_o exports the shift clock. Eight bits are transmitted with LSB first. The baud rate is fixed at 1/12 of the 8051 work clock frequency.

• Mode 1

When in mode 1, Serial data enter and exit through rxd\_i and txd\_o. No external shift clock is used. 10 bits are transmitted: a start bit 0, 8 data bits (LSB first), and a stop bit 1. On reception, the start bit synchronizes the transmission, 8 data bits are made available by reading SBUF, and the stop bit sets the flag RB8 in the Special Function Register SCON.

• Mode 2

This mode is similar to Mode 1, with two differences. The baud rate is fixed at 1/32 or 1/64 of oscillator frequency, and 11 bits are transmitted or received: a start bit 0, 8 data bits (LSB first), a programmable 9th bit, and a stop bit 1. The 9th bit can be used to control the parity of the serial interface: at transmission, bit TB8 in SCON is output as the 9th bit, and at reception, the 9th bit affects RB8 in the Special Function Register SCON.

• Mode 3

The only difference between Mode 2 and Mode 3 is that the baud rate is variable in Mode 3.

#### **Multiprocessor Communication**

The feature of receiving 9 bits in Modes 2 and 3 can be used for multiprocessor communication. In this case, the slave processors have bit SM2 in SCON set to 1. When the master processor outputs a slave's address, it sets the 9th bit to 1, causing a serial port to receive interrupt in all the slaves. The slave processors compare the received byte with their network address. If there is a match, the addressed slave will clear SM2 and receive the rest of the message, while other slaves will leave the SM2 bit unaffected and ignore the message. After addressing the slave, the host will output the rest of the message with the 9th bit set to 0, so no serial port receiving interrupt will be generated in unselected slaves.

#### Registers

Special Function Register SBUF, PCON, SCON contains the control and status bits for the serial port.

The Serial Data Buffer (SBUF) is actually two separate registers, a transmit buffer register and a receive buffer register. When data is moved to SBUF, it goes to the transmit buffer where it is held for serial transmission. When data is moved from SBUF, it comes from the receive buffer.

The detail description about PCON and SCON is shown as below tables.

| Table 2.3.18 | Table 2.3.18 Power Control Register (PCON) |                                                                          |  |  |  |  |  |

|--------------|--------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|

| Bit          | Symbol                                     | Function                                                                 |  |  |  |  |  |

|              |                                            | Double baud rate bit. If Timer 1 is used to generate the baud rate and   |  |  |  |  |  |

| PCON.7       | SMOD                                       | SMOD = 1, the baud rate is doubled when the Serial Port is used in modes |  |  |  |  |  |

|              |                                            | 1,2 or 3                                                                 |  |  |  |  |  |

| PCON.6       | -                                          | Not implemented, reserved for future use                                 |  |  |  |  |  |

| PCON.5       | -                                          | Not implemented, reserved for future use                                 |  |  |  |  |  |

| PCON.4       | -                                          | Not implemented, reserved for future use                                 |  |  |  |  |  |

| PCON.3       | -                                          | Not implemented, reserved for future use                                 |  |  |  |  |  |