# **Angelo Family Datasheet**

Version 1.0 February 2009

Agate Logic, Inc.

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Agate Logic, Inc. reserves the right to discontinue or make changes, without prior notice, to any products herein to improve reliability, function, or design. Agate Logic, Inc. advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

Copyright © 2005-2009 Agate Logic, Inc. All rights reserved. No part of this document may be copied, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the written permission of Agate Logic, Inc. All trademarks are the property of their respective companies.

# Contents

| Abou | ut This Datasheet                                        |    |

|------|----------------------------------------------------------|----|

| Туро | ographic Conventions                                     | V  |

| Addi | itional Resources                                        | V  |

| Tech | nical Support Assistance                                 | VI |

| 1.1  | Overview                                                 | 1  |

| 1.2  | Features                                                 | 1  |

| 1.3  | Supported Packages                                       | 2  |

| 2.1  | Architecture Overview                                    | 3  |

| 2.2  | Logic Cell & Carry Chain                                 | 4  |

| 2.3  | Routing Resources                                        | 6  |

|      | 2.3.1 Hierarchical logic box and hierarchical switch box | 6  |

| 2.4  | Block RAM                                                | 8  |

|      | 2.4.1 Features                                           |    |

|      | 2.4.3 Conflict Avoidance                                 |    |

|      | 2.4.4 Parity Bit Support                                 | 14 |

|      | 2.4.5 Memory Configuration Sizes                         |    |

|      | 2.4.6 Byte Enables                                       |    |

| 2.5  | Global Clock Network and PLL                             | 16 |

|      | 2.5.1 Global Clock Network                               | 16 |

|      | 2.5.2 Global Clock for I/O                               |    |

|      | 2.5.3 Global Clock for Internal EMB9K                    |    |

|      | 2.5.4 PLLs                                               |    |

|      | 2.5.5 Clock Multiplication and Division                  | 21 |

| 2.6  | I/O Capabilities                                         |    |

|      | 2.6.1 Features                                           |    |

|      | 2.6.2 Programmable Drive Strength                        |    |

|      | 2.6.3 Slew Rate Control                                  |    |

|      | 2.6.4 Bus Hold                                           |    |

| 2.7  | Power-On Reset Circuitry                                 | 24 |

| 3.1  | Configuration Overview                                   |    |

| 3.2    | Configuration Pins and Behavior                                     |    |

|--------|---------------------------------------------------------------------|----|

| 3.3    | JTAG and SPI Configuration Descriptions                             | 27 |

|        | 3.3.1 JTAG Configuration                                            |    |

|        | 3.3.2 SPI Configuration                                             |    |

|        | Active Serial (AS) SPI Configuration                                |    |

|        | Passive Serial (PS) SPI Configuration                               |    |

| 4.1 DC | C Specifications                                                    |    |

|        | 4.1.1 LVCMOS33 D.C. Specifications                                  |    |

|        | 4.1.2 LVTTL33 D.C. Specifications                                   |    |

|        | 4.1.3 Different I/O Driven Strength                                 |    |

| 5.1    | Overview                                                            |    |

| 5.2    | Pin Types                                                           |    |

| 5.3    | 100-Pin Thin Quad Flat Package (TQFP100) with internal flash        |    |

| 5.4    | 144-Pin Low-profile Quad Flat Package (LQFP144) with internal flash |    |

| 5.5    | 208-Pin Plastic Quad Flat Package (PQFP208) with internal flash     |    |

| 5.6    | 208-Pin Plastic Quad Flat Package (PQFP208) without internal flash  |    |

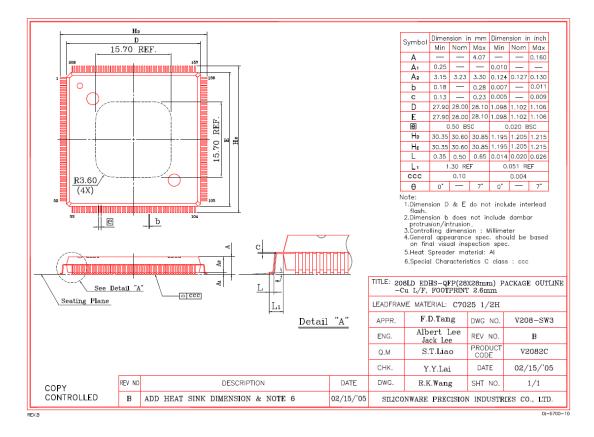

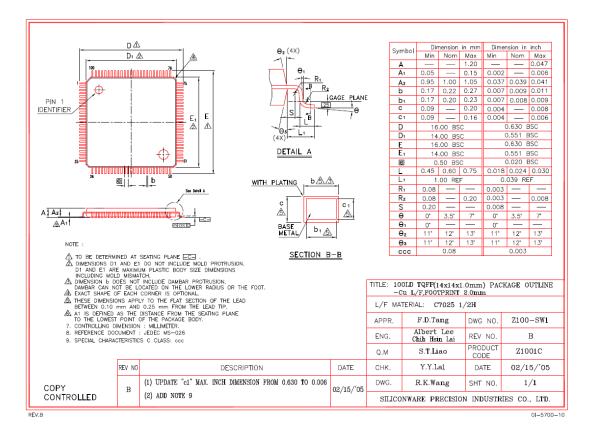

| Mecha  | anical                                                              | 42 |

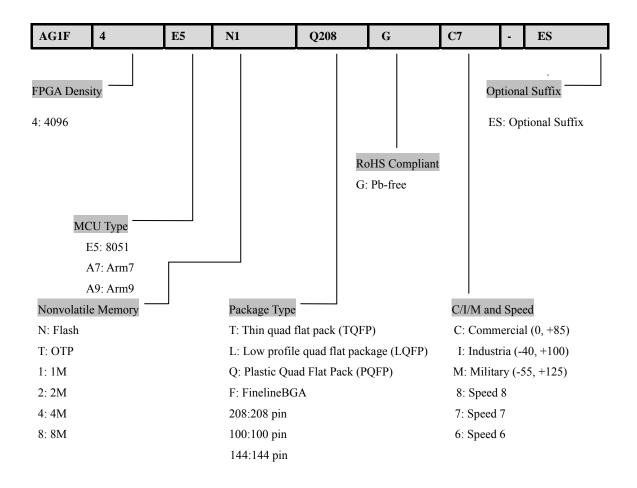

|        | ing Information                                                     |    |

# About This Datasheet

This datasheet provides comprehensive information about the Agate Logic Angelo devices.

# **Typographic Conventions**

The following typographic conventions are used in this document.

| Visual Cue                  | Meaning                                                                                                                |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Bold                        | Headings, figure and table indexes, figure titles,<br>and table items. Example: Figure 2.1.1 Top<br>Level Architecture |

| Italic Bold                 | Table titles.Example:Table 1.1AngeloFeatures                                                                           |

| Helvetica                   | Text and figures in tables. Example: Core Voltage                                                                      |

| Arial                       | Note reminders. Example: Notes for above tables                                                                        |

| Palatino Linotype in italic | Reference to sections within this document.Example: Clock Bundle Control Logic                                         |

| •                           | A list of items whose sequence is not important                                                                        |

| (1), (2)                    | Numbers in a note instruction                                                                                          |

| $\checkmark$                | A procedure that consists of one step only.                                                                            |

### **Additional Resources**

To find additional documentation about Agate Logic products, please see the Agate Logic website at:

#### www.agatelogic.com.cn

To find the up-to-date information about Agate Logic products, please see the Agate Logic website at:

www.agatelogic.com.cn

# **Technical Support Assistance**

E-mail: <u>support@agatelogic.com</u>

Website: <u>www.agatelogic.com.cn</u>

# **FETTE** Introduction

#### Section 1

Datasheet

This document provides designers with the datasheet specifications for one member of the Agate Logic Configurable Logic Device family: Angelo. These sections contain feature definitions of the ordering information, function descriptions, configuration, DC & switching characteristics, pinout information, etc.

#### 1.1 Overview

Agate Logic Angelo is constructed on a brand-new architecture, based on a leading-edge 0.13 micron process technology. With the unique combination of the soft IP cores for 4096 Field Programmable logic cells (LCs), 8 embedded memory blocks with 9K bits (EMB9Ks), and 2 phase-locked loops (PLLs), Agate Logic Angelo provides you better solutions.

The architecture of Agate Logic Angelo is optimized, giving 16 global clocks and 2 PLL for clock management, JTAG port, SPI Port and Bootstrap & Reset Unit for convenient configuration and reset, EMB9K to address on-chip memory demand, and TQFP100/ LQFP144/ PQFP208 packages to provide the customers with great flexibility and convenience.

#### **1.2 Features**

Angelo devices offer the following features:

- Field-programmable through internal DPRAM-based FPGA fabric

- Capacity to accommodate the unique designs

- ✓ Up to 4096 Field Programmable LCs

- ✓ Each LC includes one 4-input LUT and register

- ✓ Up to 72K bits of configurable and pipeline-able true dual-port RAM

- ✓ Up to two PLLs per device Frequency Synthesis, Deskew, Phase-shift

- ✓ Up to 16 low skew global clocks and reset trees

- Flexible I/O options

- ✓ Software Programmable I/Os: 3.3V LVCMOS/LVTTL, with programmable drive strength of 2 mA/4 mA/8 mA/12 mA/16 mA

- Internal Nonvolatile Memory for security: protect customer's design

- Support customer for multiple intellectual property (IP) cores

- Temperature: commerce and industry grades

- ESD 4000V HBM

- Power on reset

- Routing architecture delivers predictable timing and high utilization

- Manufactured in leading-edge 0.13 micron process for maximum performance and density

- Package options

- ✓ 100 pin TQFP with internal flash, 16 x 16 mm package size 56 user I/Os

- ✓ 144 pin LQFP with internal flash, 22 x 22 mm package size 96 user I/Os

- ✓ 208 pin PQFP with internal flash, 30.6 x 30.6 mm package size 156 user I/Os

- ✓ 208 pin PQFP without internal flash, 30.6 x 30.6 mm package size 153 user I/Os

Table 1.1 summarizes the features of the Angelo devices.

| Table 1.1 Angelo Features |                   |  |  |  |  |

|---------------------------|-------------------|--|--|--|--|

| Feature                   | Value             |  |  |  |  |

| Core Voltage              | 1.2 V             |  |  |  |  |

| I/O Voltage               | 3.3 V             |  |  |  |  |

| Process Technology        | 130-nm            |  |  |  |  |

| LC                        | 4,096             |  |  |  |  |

| User I/O Pin              | Up to 156         |  |  |  |  |

| ЕМВ9К                     | 8                 |  |  |  |  |

| PLL                       | 2                 |  |  |  |  |

| I/O Standards Support     | LVCMOS/LVTTL 3.3V |  |  |  |  |

#### **1.3 Supported Packages**

Angelo devices provide four kinds of packages including TQFP100 with internal flash, LQFP144 with internal flash, PQFP208 with internal flash, and PQFP208 without internal flash. See the detailed pinout information in *Pinout Information* section

#### Section 2

Datasheet

Integrating 4096 Field Programmable LUT/Register Logic Cells, a large block of RAM and so on, the Agate Logic Angelo is optimized for low-cost, more flexible industrial control applications. This section provides comprehensive information about the functionalities of Agate Angelo devices.

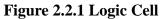

#### 2.1 Architecture Overview

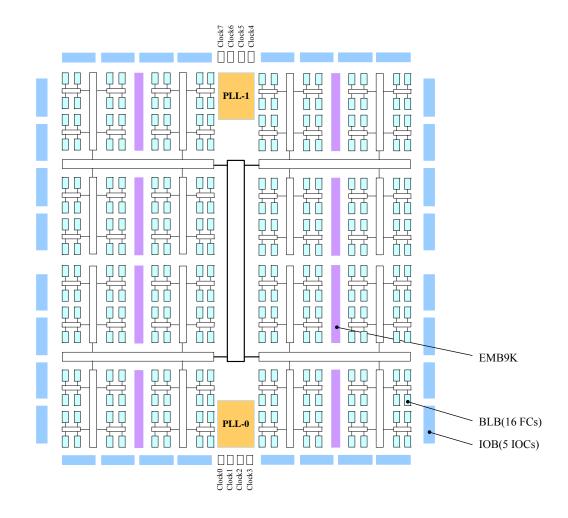

**Figure 2.1 Top Level Architecture** shows the top level architecture for Angelo. The Angelo device is constructed from four basic units, including Basic Logic Block (BLB), I/O Block (IOB), EMB9K and PLL.

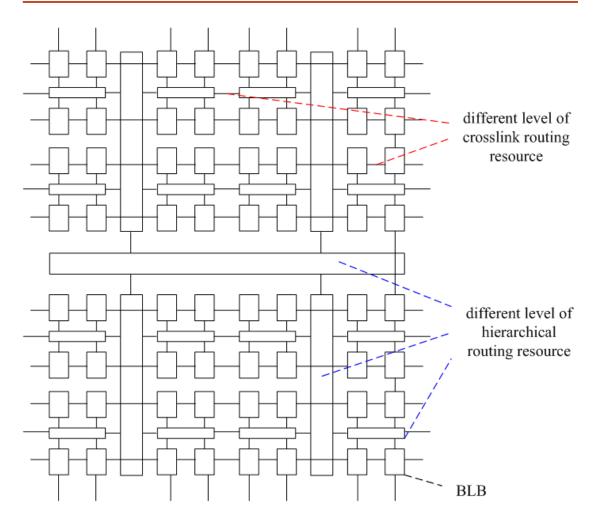

The BLB contains 16 logic cells. There are 256 BLBs in Angelo device, which are connected together using a hybrid routing architecture of Quad-Tree hierarchical architecture and Crosslink planar architecture. Under the Quad-Tree arch, 4 BLB is grouped into level-2 block. In a same way, 4 of this level-2 block is grouped into level-3 block. Since there are 4096 logic cells or 256 BLBs, so there are 4 levels in Angelo device.

The IOB contains 5 I/O cells. Each side there are 8 IOBs, so there can be up to 160 (8x4x5=160) User I/Os totally. For different package, we bound out part of these 160 user I/Os. The IOB is connected to logic array using the Crosslink planar architecture.

The EMB9K contains 9K-bit SRAM. There are 8 EMB9Ks in Angelo devices and there are distributed equally into the logic array. Each EMB9K can be configured into different depth and width ranged from 9Kx1 to 256x36. The EMB9K is connected to logic array using the Crosslink planar architecture.

The PLL block can be used for clock multiplication, division and phase shift. There are 2 PLLs in Angelo devices. There are 4 dedicated clock pads attached to each PLL as the clock source. Each PLL block generate 8 global clocks and there can be up to 16 global clocks in Angelo devices.

| able 2.1 Angelo Performance |                                         |             |       |  |  |  |

|-----------------------------|-----------------------------------------|-------------|-------|--|--|--|

| Applications                | Resources Used                          | Performance |       |  |  |  |

|                             | LCs                                     | Frequency   | Units |  |  |  |

| MUX16-1                     | 10                                      | 303         | MHz   |  |  |  |

| MUX32-1                     | 21                                      | 135.4       | MHz   |  |  |  |

| adder16                     | 16         317           32         194 |             | MHz   |  |  |  |

| adder32                     |                                         |             | MHz   |  |  |  |

| adder64                     | 64                                      | 123.6       | MHz   |  |  |  |

| counter8                    | 8                                       | 350         | MHz   |  |  |  |

| counter16                   | 16                                      | 350         | MHz   |  |  |  |

| counter32                   | 32                                      | 280         | MHz   |  |  |  |

Note:

(1) The data above are samples.

(2) Because of the PLL limitation, the max frequency of counter8 and counter16 is 350MHz.

#### 2.2 Logic Cell & Carry Chain

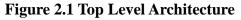

Logic cell is the smallest unit in the Field Programmable (FP) block, providing beneficial features as:

- A 4-input LUT that can implement any function of four variables

- The CarryGen function can be used for adder/subtracter

- The Nor chain and WLUT chain can extend the function of LUT

- A programmable register

- Support register feedback to LUT

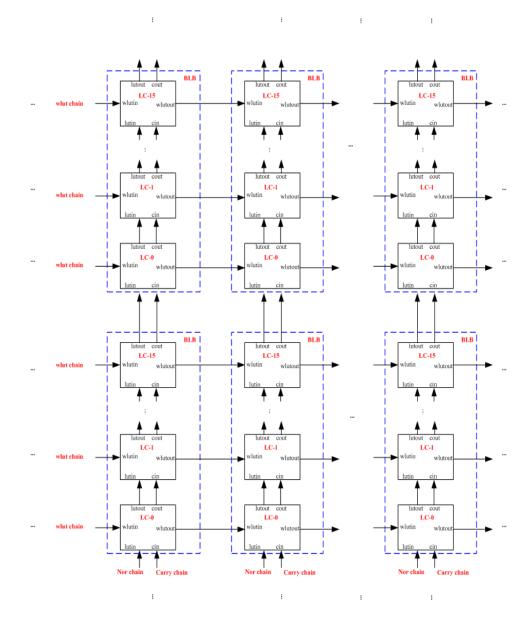

The carry chains are cascaded together through the carry chain input (CI) and carry chain output (CO) signals. The Nor chain are cascaded together through lutin and lutout; The WLUT chain are cascaded together through wlutin and wlutout. **Figure 2.2.2** shows the cascading of LCs.

Figure 2.2.2 Carry Chain, Nor chain and WLUT chain

#### 2.3 Routing Resources

#### 2.3.1 Hierarchical logic box and hierarchical switch box

Routing resource is composed of a Quad-Tree style routing MUX architecture and crosslink routing architecture. The hierarchical Quad-Tree routing resource provide sufficient routing path for all BLB, wherein BLB is the smallest node of the tree and contains 16 LCs. The Crosslink routing resource provide fast routing path between BLBs.

Figure 2.3.1 Diagram of Routing Resource

#### BLB

BLB is composed of 16 LCs and the BLB\_ctrl block. BLB\_ctrl provides the clk, cen, rstn and sload signal for all the 16 cells.

| BLB_ctrl | LC-15         LC-14         LC-13         LC-12         LC-11         LC-10         LC-9         LC-8         LC-7         LC-6         LC-5         LC-4         LC-2         LC-1         LC-1 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 2.3.2 BLB Structure

#### 2.4 Block RAM

The Angelo consists of the type of EMB9K to address on-chip memory needs. The EMB9K is a dual-port SRAM that can implement various types of memory with or without parity, including true dual-port, simple dual-port and single-port RAM. The memory blocks can be used to provide memory functions such as RAM and FIFO. There are 8 blocks of EMB9K Angelo devices.

#### 2.4.1 Features

The EMB blocks support the following features:

- 9,216 RAM bits

- True dual-port mode

- Simple dual-port mode

- Single-port mode

- FIFO Buffers

- Mixed clock mode

- Byte enable

- Parity bit

- Support the following width configurations:  $9k \times 1$ ,  $8K \times 1$ ,  $4k \times 2$ ,  $2k \times 4$ ,  $1k \times 8$ ,  $1k \times 9$ ,  $512 \times 16$ ,  $512 \times 18$ ,  $256 \times 32$ ,  $256 \times 36$

#### 2.4.2 Memory Modes

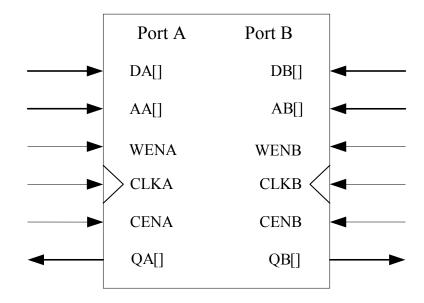

The EMB9K includes input registers that synchronize writes. EMB9K offers a true dual-port mode to support any combination of two-port operations: two read ports, two write ports, or one read and one write at two different clock frequencies. **Figure 2.4.1** shows true dual-port memory mode.

Figure 2.4.1 True Dual-port Memory Mode

The following tables summarize the ports and the function of true dual-port memory mode.

Table 2.4.1 shows the pin descriptions of true dual-port memory mode.

| Table 2.4.1 Pin Descriptions of True Dual-port Memory Mode |                       |                                                                           |  |  |  |

|------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------|--|--|--|

| Name                                                       | Name Type Description |                                                                           |  |  |  |

| AA (B)                                                     | Input                 | Port A (B) Address.                                                       |  |  |  |

| DA (B)                                                     | Input                 | Port A (B) Data Input.                                                    |  |  |  |

| QA (B)                                                     | Output                | Port A (B) Data Output.                                                   |  |  |  |

| WENA (B)                                                   | Input                 | Port A (B) Write Enable. Data is written into the dual-port SRAM upon the |  |  |  |

|                                                            |                       | rising edge of the clock when both WENA (B) and CENA (B) are high.        |  |  |  |

| CENA (B)                                                   | Input                 | Port A (B) Enable. When CENA (B) is high and WENA (B) is low, data        |  |  |  |

|                                                            |                       | from the dual-port SRAM address AA (B) is available upon the next rising  |  |  |  |

|                                                            |                       | edge of CLKA (B). If CENA (B) is low, QA (B) retains its value.           |  |  |  |

| CLKA (B)                                                   | Input                 | Port A (B) Clock.                                                         |  |  |  |

**Table 2.4.2** shows a logic table of true dual-port mode function.

| Table 2.4.2 Logic Table of True Dual-port Memory Mode Function |          |     |        |                                                                     |  |  |  |

|----------------------------------------------------------------|----------|-----|--------|---------------------------------------------------------------------|--|--|--|

|                                                                | Inputs   |     |        | Outputs                                                             |  |  |  |

| CENA (B)                                                       | WENA (B) | CLK | Status | QA (B)                                                              |  |  |  |

| 0                                                              | X X      |     | HOLD   | Data stored in the memory is retained.                              |  |  |  |

| 1                                                              | 0        | Ť   | READ   | Data is read from the memory location specified by the address bus. |  |  |  |

| 1                                                              | 1        | ↑   | WRITE  | DA (B)                                                              |  |  |  |

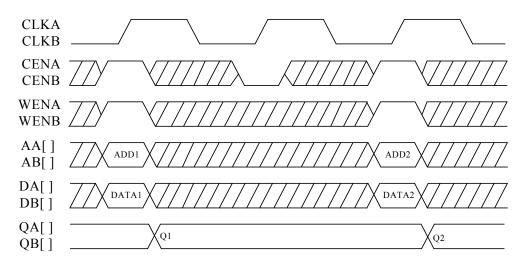

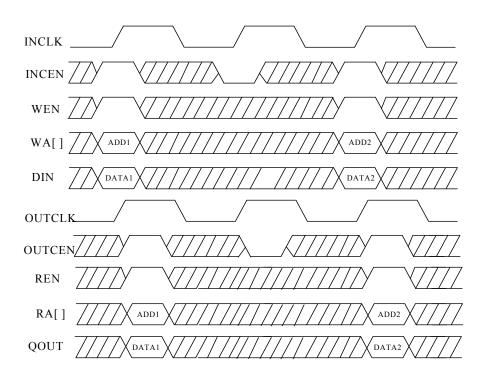

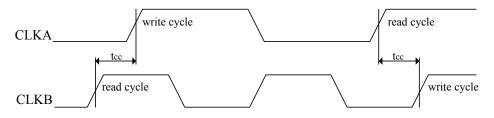

Read and write operation waveforms of true dual-port memory mode are shown in **Figure 2.4.2**.

Figure 2.4.2 True Dual-Port Memory Read-Write Waveform

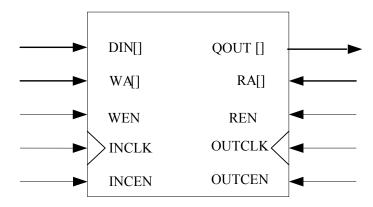

Besides, the EMB9K memory also supports simple dual-port memory mode.

#### Figure 2.4.3 Simple dual-port memory mode

| Table 2.4.3 Pin Descriptions of Simple Dual-port Memory Mode |             |                      |  |  |  |

|--------------------------------------------------------------|-------------|----------------------|--|--|--|

| Name                                                         | Description |                      |  |  |  |

| DIN                                                          | Input       | Data Input.          |  |  |  |

| WA                                                           | Input       | Write Address.       |  |  |  |

| WEN                                                          | Input       | Write Enable.        |  |  |  |

| INCLK                                                        | Input       | Input Clock.         |  |  |  |

| INCEN                                                        | Input       | Input Clock Enable.  |  |  |  |

| QOUT                                                         | Input       | Port A (B) Clock.    |  |  |  |

| RA                                                           | Output      | Read Address.        |  |  |  |

| REN                                                          | Input       | Read Enable.         |  |  |  |

| OUTCLK                                                       | Input       | Output Clock.        |  |  |  |

| OUTCEN                                                       | Input       | Output Clock Enable. |  |  |  |

Read and write operation waveforms of simple dual-port memory mode are shown in **Figure 2.4.4**.

Figure 2.4.4 Simple Dual-Port Memory Read-Write Waveform

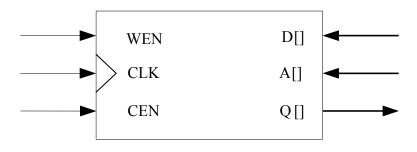

In addition to true dual-port memory mode, the EMB9K memory blocks support single-port memory mode. **Figure 2.4.5** shows this mode of Angelo EMB9K memory blocks.

Figure 2.4.5 Single-port Memory Mode

Figure 2.4.6 gives the waveforms of read and write operations in this mode.

Figure 2.4.6 Single-Port Memory Read-Write Waveform

The memory blocks also enable mixed-width data ports for reading and writing to the EMB9K ports in dual-port EMB9K configuration. For example, the memory block can be written in  $\times$  1 mode at port A and read out in  $\times$  16 mode from port B.

#### 2.4.3 Conflict Avoidance

For dual-port memory modes, both ports can access any memory address at any time. When both ports access the same address, the read and write behaviour should observe certain clock timing restrictions. These restrictions are adaptable to both synchronous and asynchronous clock.

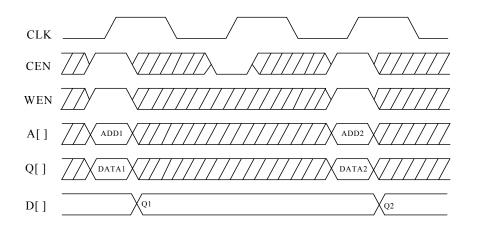

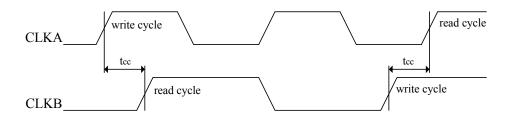

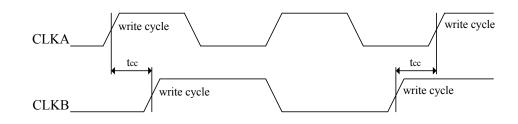

Figures 2.4.7, Figure 2.4.8, and Figure 2.4.9 illustrate the clock timings that may cause conflict in read and write operations with dual-port memory modes.

Figure 2.4.7 Dual-port memory Write-Read Clock Timing

Figure 2.4.8 Dual-port memory Read-Write Clock Timing

#### Figure 2.4.9 Dual-port memory Write-Write Clock Timing

#### Note for Figure 2.4.6 to Figure 2.4.9:

(1) tcc means clock collision. The Min value of it is 0.748ns based on the conditions of temperature =  $25 \,^{\circ}$ C, power supply =  $1.2 \,$ V.

**Table 2.4.4** shows read and write behaviour during clock conflicts, when both ports access the same address.

| Table 2.4.4 Dual-port Memory Read and Write Behaviour when accessing the same address |                           |                                         |  |  |  |  |

|---------------------------------------------------------------------------------------|---------------------------|-----------------------------------------|--|--|--|--|

| Action                                                                                | Condition                 | Behaviour                               |  |  |  |  |

| Write from one port then read from the other port                                     | $t_{cc}$ is satisfied     | Write OK                                |  |  |  |  |

|                                                                                       | (see Figure 2.4.5)        | D-to-Q write through OK                 |  |  |  |  |

|                                                                                       |                           | Read (new data) OK                      |  |  |  |  |

|                                                                                       | $t_{cc}$ is not satisfied | Write fails                             |  |  |  |  |

|                                                                                       | (see Figure 2.4.5)        | D-to-Q write through OK                 |  |  |  |  |

|                                                                                       |                           | Read fails                              |  |  |  |  |

| Read from one port then write from the other port                                     | $t_{cc}$ is satisfied     | Write OK                                |  |  |  |  |

|                                                                                       | (see Figure 2.4.6)        | D-to-Q write through OK                 |  |  |  |  |

|                                                                                       |                           | Read (old data) OK                      |  |  |  |  |

|                                                                                       | $t_{cc}$ is not satisfied | Write fails                             |  |  |  |  |

|                                                                                       | (see Figure 2.4.6)        | D-to-Q write through OK                 |  |  |  |  |

|                                                                                       |                           | Read fails                              |  |  |  |  |

| Write from one port then write from the other port                                    | $t_{cc}$ is satisfied     | Both writes OK (second write overwrites |  |  |  |  |

|                                                                                       | (see Figure 2.4.7)        | first write)                            |  |  |  |  |

|                                                                                       |                           | D-to-Q write through OK                 |  |  |  |  |

|                                                                                       | $t_{cc}$ is not satisfied | Both writes fail                        |  |  |  |  |

|                                                                                       | (see Figure 2.4.7)        | D-to-Q write through OK                 |  |  |  |  |

| Read from one port then read from the other port                                      | No restriction            | Both reads OK                           |  |  |  |  |

#### 2.4.4 Parity Bit Support

The EMB9K blocks support a parity bit for each byte. The parity bit, along with internal LC, can implement parity checking for error detection to ensure data integrity. You can also use parity-sized data words to store user-specified control bits. Byte enables are also available for data input masking when writing operations.

# 2.4.5 Memory Configuration Sizes

The memory address depths and output widths can be configured as **Table 2.4.5**, **Table 2.4.6**, and **Table 2.4.7**. Mixed-width configurations are also possible, allowing different read and write widths.

| Table 2.4.5 EMB9K Block Configurations (Single Port) |        |      |      |        |        |       |      |        |            |

|------------------------------------------------------|--------|------|------|--------|--------|-------|------|--------|------------|

|                                                      | Port A |      |      |        |        |       |      |        |            |

| 8K×1                                                 | 4K×2   | 2K×4 | 1K×8 | 512×16 | 256×32 | 9 k×1 | 1K×9 | 512×18 | 256<br>×36 |

| Port A   |              | Port B       |              |              |              |              |              |              |              |              |

|----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|          | 8K×1         | 4K×2         | 2K×4         | 1K×8         | 512×16       | 256×32       | 9 k×1        | 1K×9         | 512×18       | 256×36       |

| 8K × 1   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 4K × 2   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 2K × 4   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 1K × 8   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 512 × 16 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 256 × 32 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| 9K × 1   |              |              |              |              |              |              | $\checkmark$ |              |              |              |

| 1K × 9   |              |              |              |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 512 × 18 |              |              |              |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 256 × 36 | Ī            |              |              |              |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Table 2.4.7 EMB9K Block Configurations (True Dual-Port) |              |              |              |              |              |              |              |              |  |

|---------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--|

| Port A                                                  | Port B       |              |              |              |              |              |              |              |  |

| FULLA                                                   | 8K × 1       | 4K × 2       | 2K × 4       | 1K × 8       | 512 × 16     | 9 k × 1      | 1K × 9       | 512 × 18     |  |

| 8K × 1                                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |  |

| 4K × 2                                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |  |

| 2K × 4                                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |  |

| 1K × 8                                                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |  |

| 512 × 16                                                | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |  |

| 9K × 1                                                  |              |              |              |              |              | $\checkmark$ |              |              |  |

| 1K × 9                                                  |              |              |              |              |              |              | $\checkmark$ | $\checkmark$ |  |

| 512 × 18                                                |              |              |              |              |              |              | $\checkmark$ | $\checkmark$ |  |

#### 2.4.6 Byte Enables

EMB9K blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value.

Table 2.4.8 summarizes byte selection.

| Table 2.4.8 Byte Enable for EMB9K Blocks |          |          |          |          |  |  |  |

|------------------------------------------|----------|----------|----------|----------|--|--|--|

| wena[30]                                 | din[150] | din[170] | din[310] | din[350] |  |  |  |

| [0] = 0                                  | [70]     | [80]     | [70]     | [80]     |  |  |  |

| [1] = 0                                  | [158]    | [179]    | [158]    | [179]    |  |  |  |

| [2] = 0                                  | -        | -        | [2316]   | [2618]   |  |  |  |

| [3] = 0                                  | -        | -        | [3124]   | [3527]   |  |  |  |

#### 2.5 Global Clock Network and PLL

Angelo devices offer up to 16 global clocks and 2 PLLs to provide precision for time management.

#### 2.5.1 Global Clock Network

There are 16 global clocks, which can be driven by dedicated clock pins, PLL outputs, and LCs. Angelo devices provide up to 8 dedicated clock pins.

Global clock network provides clock for FP, Internal DPRAMs, and IOCs. Global clock can be of clock control signal for FP, such as clock signal and reset signal of FP register. At the same time, global clock, asynchronous reset signal, and clock enable signal also can be driven by FP internal logic.

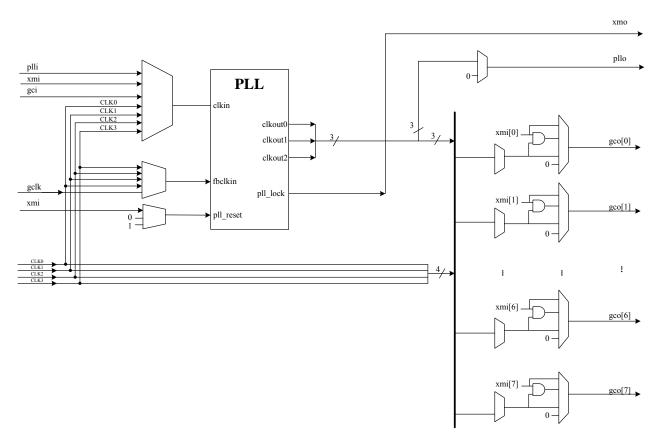

#### Figure 2.5.1 Global Clock Controller

**Table 2.5.1** gives the detailed information of PLL signal connection relationship for Angelo.

| Table 2.5.1 Signal connection of PLL |                                                                                              |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| Signal                               | Source / Destination                                                                         |  |  |  |

| plli                                 | From the other PLL to cascade the PLLs together                                              |  |  |  |

| xmi                                  | From FP core                                                                                 |  |  |  |

| gci                                  | From the other PLL to provide source signals for clkin                                       |  |  |  |

| CLK[3:0]                             | From dedicated clock pins                                                                    |  |  |  |

| gclk[15:0]                           | From Global Clock Network, eight bits from gco[7:0], and the other eight bits from gco[15:8] |  |  |  |

| pllo                                 | To the other PLL to cascade the PLLs together                                                |  |  |  |

| xmo                                  | To FP core                                                                                   |  |  |  |

| gco[7:0]                             | To Global Clock Network                                                                      |  |  |  |

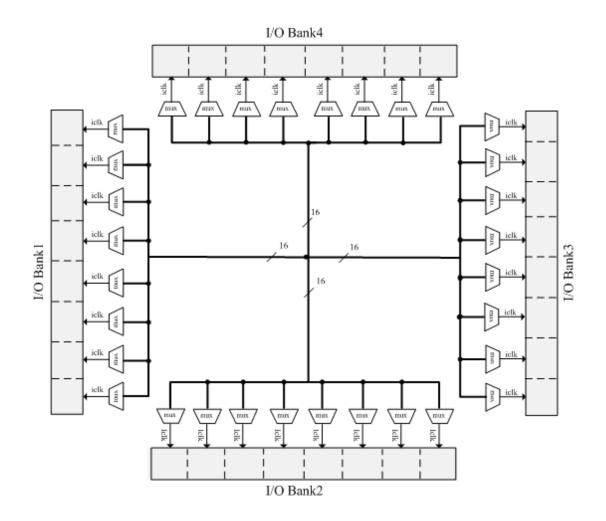

#### 2.5.2 Global Clock for I/O

Angelo provides four I/O Banks: BANK1 to BANK4. Each bank includes 8 IOBs, each IOB contains 5 IOCs, and all the clocks are from global clock network shown as **Figure 2.5.2**:

Figure 2.5.2 Clock for I/O

## 2.5.3 Global Clock for Internal EMB9K

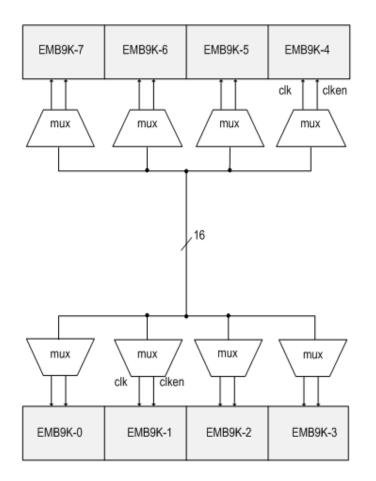

There are 8 internal EMB9Ks in Angelo devices. Each EMB9K has a different clock domain. Diagram of clock for internal memory is shown as **Figure 2.5.3**.

#### Figure 2.5.3 Clock for EMB9K

#### 2.5.4 PLLs

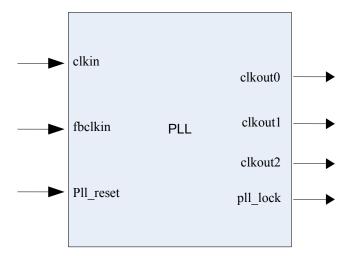

Angelo PLLs provide general-purpose clocks with clock multiplication and division. Angelo device contains two PLLs.

The PLLs in Angelo devices provide the following features:

- Support of Clock Bypass Mode;

- Support of Power-down mode, realizing minimum power consumption;

- Clock multiplication and division: include reference division counter (N), multiplication counter (M) and post-scale counters(C0,C1, C2);

- Optional phase shift function: 1/10, 1/20, 1/40, 1/80, 1/160, 1/320 shift output;

- Internal and board level deskew function for system synchronization;

- Up to three different post-scale counters for each PLL;

- Lock detection output;

Table 2.5.2 shows the PLL features in Angelo.

| Table 2.5.2 PLL Specification |                            |                   |  |  |  |

|-------------------------------|----------------------------|-------------------|--|--|--|

| Parameter                     |                            | Value             |  |  |  |

| Input reference frequency     | range                      | 5MHz - 350MHz     |  |  |  |

| VCO output frequency rar      | ige                        | 320MHz - 800MHz   |  |  |  |

| PFD input frequency rang      | e                          | 5MHz - 350MHz     |  |  |  |

|                               | Without phase shift option | 10 MHz - 350 MHz  |  |  |  |

|                               | Of 10 output phase step    | 320 MHz - 350 MHz |  |  |  |

|                               | Of 20 output phase step    | 160 MHz - 350 MHz |  |  |  |

| Output frequency range        | Of 40 output phase steps   | 80 MHz - 200 MHz  |  |  |  |

|                               | Of 80 output phase steps   | 40 MHz - 100 MHz  |  |  |  |

|                               | Of 160 output phase steps  | 20 MHz - 50 MHz   |  |  |  |

|                               | Of 320 output phase steps  | 10 MHz - 25 MHz   |  |  |  |

| Output Duty Cycle             | •                          | 50% ± 16.7%       |  |  |  |

| Range of counter N            |                            | 2- 32             |  |  |  |

| Range of counter M            |                            | 1- 512            |  |  |  |

| Range of counter C            |                            | 1- 32             |  |  |  |

|                               | Deskew with phase shift    | 10                |  |  |  |

| Device Consumption            | mode, 3 outputs at 350 MHz | 12 mA             |  |  |  |

| Power Consumption             | Normal mode                | 7.5 mA            |  |  |  |

|                               | Powerdown mode             | 1 mA              |  |  |  |

| Operation voltage range       |                            | 1.2 V ± 10%       |  |  |  |

Figure 2.5.4 shows the signal connection of Angelo PLL.

Figure 2.5.4 PLL Interface

**Table 2.5.3** shows the detail information of PLL interface. For the device with 8 clock pins, CLK0/1/2/3 drive PLL0; while CLK4/5/6/7 drive PLL1.For the device with 4 clock pins, CLK0/1 drive PLL0; while CLK2/3 drive PLL1.

| Table 2.5. | 3 Port Defi | nition of P | LL                                                                                    |

|------------|-------------|-------------|---------------------------------------------------------------------------------------|

| Name       | Туре        | Width       | Description                                                                           |

| clkin      | Input       | 1           | Reference clock input.                                                                |

| fbclkin    | Input       | 1           | Feedback clock input, used in deskew mode.                                            |

| pll_reset  | Input       | 1           | PLL reset signal. High active. When reset, all outputs are low.                       |

| clkout0    | Output      | 1           | Main clock output.                                                                    |

| clkout1    | Output      | 1           | First shifted phase clock output. Can run at different frequency in synthesize mode.  |

| clkout2    | Output      | 1           | Second shifted phase clock output. Can run at different frequency in synthesize mode. |

| pll_lock   | Output      | 1           | Lock status output. High active.                                                      |

## 2.5.5 Clock Multiplication and Division

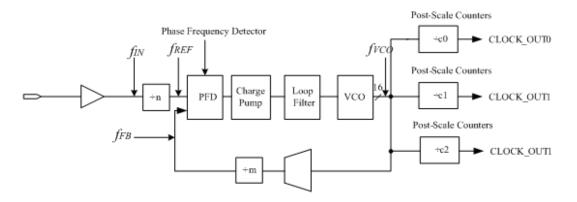

Figure 2.5.5 is the schematic diagram of Angelo PLL.

Figure 2.5.5 Angelo PLL

$$\begin{split} f_{REF} &= f_{IN} / n; \\ f_{VCO} &= f_{REF} * m = f_{IN} * (m / n) \\ f_{FB} &= f_{VCO} / m; \\ f_{CLOCK\_OUT0} &= f_{VCO} / c0 = f_{IN} * (m / (n * c0)) \\ f_{CLOCK\_OUT1} &= f_{VCO} / c1 = f_{IN} * (m / (n * c1)) \\ f_{CLOCK\_OUT2} &= f_{VCO} / c2 = f_{IN} * (m / (n * c2)) \end{split}$$

Angelo PLL provides clock synthesis for three PLL output ports, all using m/ (n x o) scaling factors. The input clock is divided by a reference divider, n, and is then multiplied by the *m* feedback factor. The control loop drives the VCO to match fin ×

(m/n). Then the port0 and port1 have a post-scale counter to divide down the high-frequency VCO. The frequency of port0, port1 and port2 is divided by a post-scale divider, c.

PLL has one reference divider, n, that can range in value from 2 to 32. PLL also has one multiply divider, m, which can range in value from 1 to 512. The pose-scale divider has a value range from 1 to 32.

#### 2.6 I/O Capabilities

#### 2.6.1 Features

Angelo IOCs support many features including:

- LVCMOS/LVTTL input and output

- Joint Test Action Group (JTAG) Boundary-Scan Test (BST) support

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable pull-down resistor

- Asynchronous input/output

- Synchronous input/output aligned with positive/negative clock edge

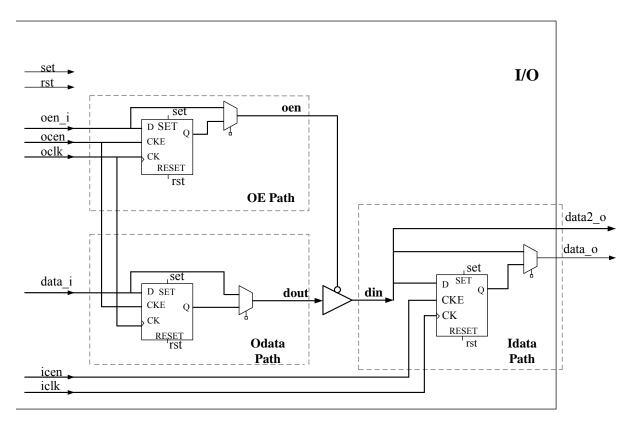

Angelo device IOCs contains a bidirectional I/O buffer and three registers for complete internal bidirectional single or dual data rate transfer.

Figure 2.6 Angelo I/O Structure

#### 2.6.2 Programmable Drive Strength

The output buffer for each Angelo device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standards have several levels of drive strength that you can control. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

Table 2.6 shows the possible settings for the I/O standards with drive strength control.

| Table 2.6 Drive Strength and Maximum Output Clock Toggle Rate on Angelo Devices |                  |                                        |  |  |  |  |

|---------------------------------------------------------------------------------|------------------|----------------------------------------|--|--|--|--|

| I/O Standard                                                                    | Driving strength | Maximum Output Clock Toggle Rate (MHz) |  |  |  |  |

|                                                                                 | 2mA              | 160                                    |  |  |  |  |

|                                                                                 | 4mA              | 180                                    |  |  |  |  |

| LVTTL/LVCMOS (3.3 V)                                                            | 8mA              | 260                                    |  |  |  |  |

|                                                                                 | 12mA             | 280                                    |  |  |  |  |

|                                                                                 | 16mA             | 300                                    |  |  |  |  |

#### 2.6.3 Slew Rate Control

Each I/O output buffer has a control bit to control the switching edge rate. This control

bit can be individually programmed to either 0 (default) or 1. A 0 value means fast slew rate and a 1 value means slow slew rate.

Each I/O has a control bit. This output slew-rate control can be individually configured. This configuration affects the rising edge and descending edge of output signal. Both rising edge and descending edge of slew rate can be controlled by adjusting driving-strength.

Each user I/O has an individually configured pull-up resistor. This resistor will drag the I/O output to VDDIO. The value of this resistor is between 60-90k ohms. Each user I/O also has an individually configured pull-down resistor. This resistor will drag the I/O output to 0. The value of this resistor is between 60-90k ohms.

#### 2.6.4 Bus Hold

Each Angelo device user I/O pin provides an optional bus-hold feature. The bus-hold circuitry can hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not necessary to hold a signal level when the bus is tri-stated.

The bus-hold circuitry also pulls un-driven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than VCCIO to prevent overdriving signals.

If the bus-hold feature is enabled, the device cannot use the programmable pull-up option. Bus hold circuitry is not available on dedicated clock pins.

The bus-hold circuitry is only active after configuration. After you enter the user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

#### 2.7 Power-On Reset Circuitry

Angelo devices have internal Power-On Reset (POR) circuits to monitor VCCINT and VCCIO voltage levels during power-up. The POR circuit keeps the device in reset state until VCCINT and VCCIO reach the trigger point. The POR circuit of Angelo device does not monitor the VCCINT and VCCIO voltage levels after the device enters into user mode. In the user mode, POR circuit can accept external reset signal and drag the chip into reset stage until this signal was released.

Section 3

Datasheet

## 3.1 Configuration Overview

The LCs of the Angelo devices use SRAM cells to store configuration data. Since SRAM is volatile, configuration data must be downloaded to device each time the device powers up. You can download configuration data to Angelo devices using the SPI or JTAG interfaces.

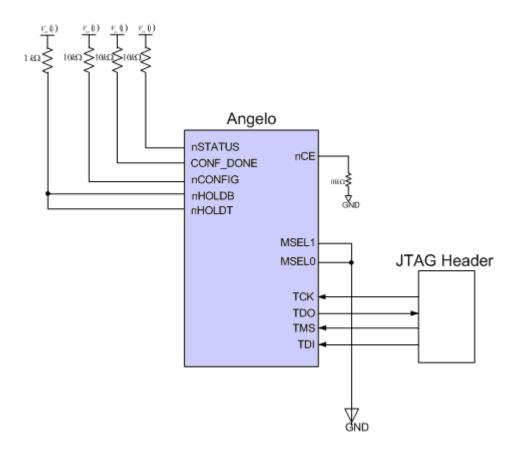

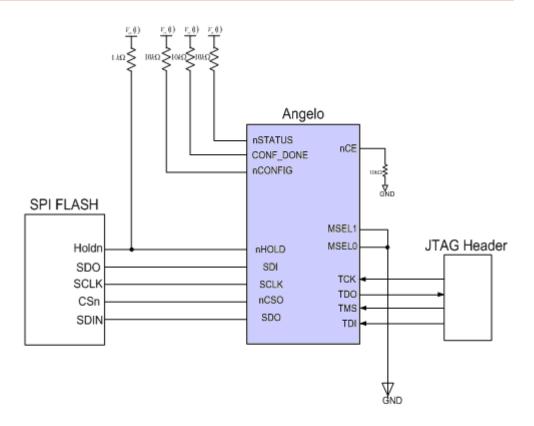

**Figure 3.1.1** and **Figure 3.1.2** show the pin connection information of SPI configuration scheme and JTAG-based configuration for Angelo devices.

Figure 3.1.1 Configuration for devices with internal flash

#### Figure 3.1.2 Configuration for devices without internal flash

Note:

(1) For more information about descriptions of the configuration related pins on Angelo device, please refer to **Table 3.2** - Configuration Pin Information Summary in the *Configuration Pins and Behavior* section.

(2) Vcc=3.3V

## 3.2 Configuration Pins and Behavior

This part describes the function information of configuration pins. See Table 3.2.

| Table 3.2 Configuration and JTAG Pins |                           |                                                               |  |  |  |  |

|---------------------------------------|---------------------------|---------------------------------------------------------------|--|--|--|--|

| nCONFIG                               | input                     | Chip global reset input. Active low                           |  |  |  |  |

| nSTATUS                               | Bidirectional(open drain) | This is a dedicated configuration status pin , not user I/O   |  |  |  |  |

| CONF_DONE                             | Bidirectional(open drain) | This is a dedicated configuration status pin , not user I/O   |  |  |  |  |

|                                       |                           | Dedicated mode select control pins for the configuration mode |  |  |  |  |

|                                       |                           | for the device : 00 :Active Serial (Auto Configuration) , 01  |  |  |  |  |

|                                       |                           | Passive Serial , 11 TEST MODE , if JTAG is selected then      |  |  |  |  |

| MSEL0/1                               | Input                     | bits are ignored .                                            |  |  |  |  |

| nCE                                   | Input                     | Configuration Enable. active low                              |  |  |  |  |

|        |                                   | Output that drive low when device configuration is completed.  |

|--------|-----------------------------------|----------------------------------------------------------------|

|        |                                   | During multi device configuration, this pin feeds a            |

|        |                                   | subsequence device's CEn pin. During single device             |

|        |                                   | configuration and for the last device in multi-device          |

| nCEO   | I/O, output                       | configuration, this pin can be used                            |

| TMS    | Input                             | JTAG input pin.                                                |

| TDI    | Input                             | JTAG input pin.                                                |

| ТСК    | Input                             | JTAG input pin.                                                |

| TDO    | Output                            | JTAG output pin.                                               |

|        |                                   | In passive serial configuration mode, SCLK is a clock input    |

|        |                                   | used to clock configuration data from external device source   |

|        |                                   | into Angelo device. In active serial configuration mode, SCLK  |

|        |                                   | is a clock output from Angelo device which is a master in this |

| SCLK   | input(PS mode) , output (AS mode) | mode.                                                          |

| SDI    | input                             | Dedicated configuration data input pin.                        |

|        |                                   | Active serial data output from the Angelo device. In passive   |

| SDO    | I/O, Output                       | serial configuration, this pin becomes user I/O pin.           |

|        |                                   | Chip select output to enable/disable a serial configuration    |

|        |                                   | device. This output is used during active serial configuration |

|        |                                   | mode. In passive serial configuration mode this pin become     |

| nCSO   | I/O, Output                       | user I/O.                                                      |

|        |                                   | Signal of SPI interface. To pause any communication with the   |

| nHOLD  | bidirectional(open drain)         | device without deselecting it. Active low.                     |

|        |                                   | Signal of SPI interface. To pause any communication with the   |

| nHOLDB | bidirectional(open drain)         | device without deselecting it. Active low.                     |

|        |                                   | Signal of SPI interface. To pause any communication with the   |

| nHOLDT | bidirectional(open drain)         | device without deselecting it. Active low.                     |

|        |                                   |                                                                |

Note:

(1) The SCLK, SDIN, HOLDn pins only exist in the packages with external flash: 144-pin TQFP with external flash and 208-pin PQFP with external flash.

(2) PS mode is only applied to PQFP 208 without internal flash

(3) nHOLDB and nHOLDT should connect together with a 1k pull-up resistor for the devices with internal flash.

# 3.3 JTAG and SPI Configuration Descriptions

There are two different configurations: JTAG configuration and SPI configuration as the following table.

| Table 3. | Table 3.3 Angelo configuration mode |          |                                                        |  |  |  |  |

|----------|-------------------------------------|----------|--------------------------------------------------------|--|--|--|--|

| MSEL1    | MSEL0                               | Mode     | Description                                            |  |  |  |  |

| 0        | 0                                   | AS       | Configuration data was read from flash by internal SPI |  |  |  |  |

|          |                                     |          | controller                                             |  |  |  |  |

| 0        | 1                                   | PS       | Angelo acts as slave. External SPI controller feed     |  |  |  |  |

|          |                                     |          | configuration data into Angelo via SPI interface.      |  |  |  |  |

| 1        | 0                                   | JTAG     | JTAG configuration takes high privilege over AS mode   |  |  |  |  |

| 1        | 1                                   | Reserved | For testing purpose, not open to customer.             |  |  |  |  |

Notes:

1) JTAG configuration is available in AS and JTAG modes; in AS mode, JTAG configuration takes precedence over SPI configuration.

2) Do not leave these pins floating; connect them to VCCIO or ground.

#### 3.3.1 JTAG Configuration

During JTAG configuration, data is downloaded to the device on the board through download cable. Configuring devices through a cable is similar to programming devices in-system.

Angelo devices are designed in such ways that JTAG instructions have precede CEn over any device operating modes. So JTAG configuration can take place without waiting for other configuration to complete (e.g. configuration with serial or enhanced configuration devices). If you attempt JTAG configuration in Angelo devices during non-JTAG configuration, non-JTAG configuration is terminated and JTAG configuration is initiated.

#### **3.3.2 SPI Configuration**

#### Active Serial (AS) SPI Configuration

In the AS configuration scheme, Angelo MSEL1 pin should be set to 0 and MSEL0 should be set to 0. Angelo devices are configured using the industry-standard SPI serial devices. These configuration devices are low cost ones with a non-volatile memory that features a simple few pin interface and a small form factor. These features make serial configuration devices an ideal solution for configuring the low-cost Angelo devices.

Serial configuration devices provide a serial interface to access configuration data. During device configuration, Angelo devices read configuration data via the serial interface, and configure their SRAM cells. This scheme is referred to as an AS configuration scheme because the device controls the configuration interface.

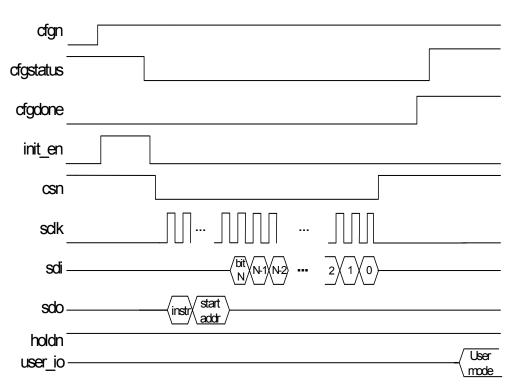

Figure 3.3 Angelo AS Waveform

Above is the AS configuration process. After pow-on-reset, initialization process will start in parallel and will last for 25752 cycles. Init\_en will keep high during initialization process. Cfgstatus will go low to prepare for the configuration process when initialization done. When initialization completed, device will send out csn and sclk for reading configuration data in flash. It will also send the read instruction and the read start address by sdo in serial. Instruction is 8 bit long and start address is twenty-four bit long. Then configuration data will then be read out in serial. Holdn will keep logic high level during AS configuration process. Cfgdone will be pulled up by an external resistor about six cycles after csn goes to high level. Then cfgstatus will also be pulled up at the next negedge of sysclk when cfgdone is one. User mode will go high one clock cycle after the posedge of cfgdone.

#### Passive Serial (PS) SPI Configuration

In the PS scheme, an external host (configuration device, internal processor, or host PC) controls configuration. Configuration data is input to the target Angelo devices via the SDIN pin at each rising edge of SCLK.

You should select the PS configuration scheme for your application by setting Angelo MSEL1 as 0 and MSEL0 as 1.

# DC & Switching Characteristics

Section 4

Datasheet

# 4.1 DC Specifications

This section mainly describes the DC specifications of Agate Logic Angelo devices.

#### 4.1.1 LVCMOS33 D.C. Specifications

| Table 4.1.1 LVCMOS33 D.C. Characteristics |        |                   |           |     |           |       |  |  |

|-------------------------------------------|--------|-------------------|-----------|-----|-----------|-------|--|--|

| Parameter                                 | Symbol | Condition         | Min       | Тур | Max       | Units |  |  |

| Supply Voltage                            | VCCIO  | -                 | 2.97      | 3.3 | 3.63      | V     |  |  |

| Input Voltage Low                         | VIL    | -                 | -0.3      | -   | 0.8       | V     |  |  |

| Input Voltage High                        | VIH    | -                 | 2.0       | -   | VCCIO+0.3 | V     |  |  |

|                                           | VOL    | lol = 0.1mA       | -         | -   | 0.2       | V     |  |  |

| Output Voltage Low                        |        | lol = 2 to 16mA   | -         | -   | 0.4       | V     |  |  |

| Output Voltage High                       | VOH    | loh = -0.1mA      | VCCIO-0.2 | -   | -         | V     |  |  |

|                                           |        | loh = -2 to -16mA | 2.4       | -   | -         | V     |  |  |

# 4.1.2 LVTTL33 D.C. Specifications

| Table 4.1.2 LVTTL33 D.C. Characteristics |        |                   |      |     |           |       |  |  |

|------------------------------------------|--------|-------------------|------|-----|-----------|-------|--|--|

| Parameter                                | Symbol | Condition         | Min  | Тур | Max       | Units |  |  |

| Supply Voltage                           | VCCIO  | -                 | 2.97 | 3.3 | 3.63      | V     |  |  |

| Input Voltage Low                        | VIL    | -                 | -0.3 | -   | 0.8       | V     |  |  |

| Input Voltage High                       | VIH    | -                 | 2.0  | -   | VCCIO+0.3 | V     |  |  |

| Output Voltage Low                       | VOL    | lol = 2 to 16mA   | -    | -   | 0.4       | V     |  |  |

| Output Voltage High                      | VOH    | loh = -2 to -16mA | 2.4  | -   | -         | V     |  |  |

Notes for the tables above:

- (1) Descriptions of the symbols used in these tables are as follows:

- VCCIO Supply voltage for single-ended inputs and for output drivers

- lol Output current condition under which VOL is tested

- loh Output current condition under which VOH is tested

- VIL Input voltage that indicates a low logic level

- VIH Input voltage that indicates a high logic level

- VOL Output voltage that indicates a low logic level

- VOH Output voltage that indicates a high logic level

(2) Absolute maximum ratings are stress ratings. Continuously operating at or beyond these ratings listed above may cause unrecoverable damage to the device.

## 4.1.3 Different I/O Driven Strength

| Table 4.1.3 I/O Driven Strength |                     |    |   |   |   |  |  |

|---------------------------------|---------------------|----|---|---|---|--|--|

| I/O Standard (V)                | Driven Strength(mA) |    |   |   |   |  |  |

| 3.3 LVTTL/LVCMOS                | 16                  | 12 | 8 | 4 | 2 |  |  |

Note:

(1) The values in this table are based on the conditions of testing temperature =  $25 \,^{\circ}$ C, VCCINT = 1.2V, VCCIO = 3.3V.

# **Pinout Descriptions**

#### Section 5

Datasheet

#### 5.1 Overview

The Angelo devices are available in three package styles: TQFP100 with internal flash, LQFP144 with internal flash, PQFP 208 with internal flash, and PQFP208 without internal flash. This section mainly describes the various pins on Angelo and how they connect within the supported component packages.

### 5.2 Pin Types

Most pins of Angelo devices are general-purpose, user-defined I/O pins. There are, however, up to 3 different functional types of pins on Angelo packages, which are Power Supply and Voltage Reference Pins, Clock and PLL Pins and Configuration and JTAG Pins, as outlined in **Table 5.2**.

| Table 5.2 Type | Table 5.2 Types of Pins on Angelo |                                                                   |  |  |  |

|----------------|-----------------------------------|-------------------------------------------------------------------|--|--|--|

| Pin Name       | Pin Type                          | Pin Description                                                   |  |  |  |

|                | Power Supply                      | and Voltage Reference Pins                                        |  |  |  |

| VCCIO          | Power                             | Digital VDD for I/O 3.3V                                          |  |  |  |

| VCCCORE        | Power                             | Digital VDD for CORE 1.2V                                         |  |  |  |

| GND            | Ground                            | Digital Ground.                                                   |  |  |  |

|                |                                   | Analog power for PLLs. It should connect to 1.5V even if PLL is   |  |  |  |

| VCCA_PLL1/2    | Power                             | not used                                                          |  |  |  |

|                |                                   | Analog ground for PLLs. It can connect to Ground plan on the      |  |  |  |

| GNDA_PLL1/2    | Ground                            | board                                                             |  |  |  |

|                | Configu                           | uration and JTAG Pins                                             |  |  |  |

| nCONFIG        | input                             | Chip reset pin. Active low                                        |  |  |  |

| nSTATUS        | Bidirectional(open drain)         | This is a dedicated configuration status pin.                     |  |  |  |

| CONF_DONE      | Bidirectional(open drain)         | This is a dedicated configuration status pin.                     |  |  |  |

|                |                                   | Dedicated mode select control pins for the configuration mode for |  |  |  |

|                |                                   | the device: 00: Active Serial (Auto Configuration), 01 Passive    |  |  |  |

| MSEL0/1        | Input                             | Serial, 11 TEST MODE, if JTAG is selected then bits is ignored.   |  |  |  |

| nCE            | Input                             | Configuration Enable. active low                                  |  |  |  |

|            |                             | Output that drives low when device configuration is completed.        |

|------------|-----------------------------|-----------------------------------------------------------------------|

|            |                             | During multi-device configuration, this pin feeds a subsequence       |

|            |                             | device's nCE pin. During single device configuration and for the      |

| nCEO       | I/O, output                 | last device in multi-device configuration, this pin can be used       |

| TMS        | Input                       | JTAG input pin.                                                       |

| TDI        | Input                       | JTAG input pin.                                                       |

| тск        | Input                       | JTAG input pin.                                                       |

| TDO        | Output                      | JTAG output pin.                                                      |

|            |                             | In passive serial configuration mode, SCLK is a clock input used      |

|            |                             | to clock configuration data from external device source into          |

|            | input(PS mode) , output (AS | Angelo device. In active serial configuration mode, SCLK is a         |

| SCLK       | mode)                       | clock output from Angelo device which is a master in this mode.       |

| SDI        | input                       | Dedicated configuration data input pin.                               |

|            |                             | Active serial data output from the Angelo device. In passive serial   |

| SDO        | I/O, Output                 | configuration, this pin becomes user I/O pin.                         |

|            |                             | Chip select output to enable/disable a serial configuration device.   |

|            |                             | This output is used during active serial configuration mode. In       |

| nCSO       | I/O, Output                 | passive serial configuration mode this pin become user I/O.           |

|            |                             | Signal of SPI interface. To pause any communication with the          |

| nHOLD      | bidirectional(open drain)   | device without deselecting it. Active low.                            |

|            |                             | Signal of SPI interface. To pause any communication with the          |

| nHOLDB     | bidirectional(open drain)   | device without deselecting it. Active low.                            |

|            |                             | Signal of SPI interface. To pause any communication with the          |

| nHOLDT     | bidirectional(open drain)   | device without deselecting it. Active low.                            |

|            | Cle                         | ock and PLL Pins                                                      |

|            |                             | Dedicated global clock input, If it is not used as clock input, this  |

| CLK0/1/2/3 | Input                       | pin can be general input port.                                        |

|            |                             | Dedicated global clock input, If it is not used as clock input , this |

|            |                             |                                                                       |

Notes:

(1) The pinout information of Configuration and JTAG Pins is presented in the Configuration *Pins and Behavior* section.

(2) PS mode is only applied to PQFP 208 without internal flash

(3) nHOLDB and nHOLDT should connect together with a 1k pull-up resistor for the devices with internal flash.

# 5.3 100-Pin Thin Quad Flat Package (TQFP100) with internal

#### flash

Angelo is available in the 100-pin plastic quad flat package with internal flash. **Table 5.3** lists all the package pins. They are arranged in pin numbers.

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name    |

|---------------|----------|---------------|-------------|---------------|-------------|

| 1             | I/O1     | 35            | I/O13       | 69            | GND         |

| 2             | I/O2     | 36            | VCCINT      | 70            | VCCINT      |

| 3             | I/O3     | 37            | GND         | 71            | VCCIO5      |

| 4             | I/O4     | 38            | I/O14       | 72            | I/O37       |

| 5             | I/O5     | 39            | VCCA_PLL0   | 73            | I/O38       |

| 6             | I/O6     | 40            | GNDA_PLL0   | 74            | I/O39       |

| 7             | VCCINT   | 41            | I/O15(CLK0) | 75            | GND         |

| 8             | GND      | 42            | I/O16(CLK1) | 76            | GND         |

| 9             | GND      | 43            | I/O17(CLK2) | 77            | I/O40       |

| 10            | VCCI00   | 44            | I/O18(CLK3) | 78            | I/O41       |

| 11            | nHOLDB   | 45            | I/O19       | 79            | I/O42       |

| 12            | TMS      | 46            | I/O20       | 80            | VCCIO6      |

| 13            | тск      | 47            | GND         | 81            | I/O43       |

| 14            | TDI      | 48            | VCCIO3      | 82            | I/O44       |

| 15            | TDO      | 49            | I/O21       | 83            | I/O45       |

| 16            | I/O7     | 50            | I/O22(nCEO) | 84            | VCCA_PLL1   |

| 17            | I/O8     | 51            | I/O23       | 85            | GNDA_PLL1   |

| 18            | I/O9     | 52            | I/O24       | 86            | I/O46(CLK4) |

| 19            | VCCINT   | 53            | GND         | 87            | I/O47(CLK5) |

| 20            | GND      | 54            | VCCINT      | 88            | I/O48(CLK6) |

| 21            | I/O10    | 55            | I/O25       | 89            | I/O49(CLK7) |

| 22            | I/O11    | 56            | I/O26       | 90            | I/O50       |

| 23            | GND      | 57            | I/O27       | 91            | VCCINT      |

| 24            | nHOLDT   | 58            | I/O28       | 92            | GND         |

| 25            | VCCIO1   | 59            | I/O29       | 93            | GND         |

| 26            | VCCIO2   | 60            | I/O30       | 94            | VCCI07      |

| 27            | GND      | 61            | VCCIO4      | 95            | I/O51       |

| 28            | nCONFIG  | 62            | GND         | 96            | I/O52       |

| 29            | nCE      | 63            | I/O31       | 97            | I/O53       |

| 30            | MSEL0    | 64            | I/O32       | 98            | I/O54       |

| 31            | MSEL1    | 65            | I/O33       | 99            | I/O55       |

| 32 | CONF_DONE | 66 | I/O34 | 100 | I/O56 |

|----|-----------|----|-------|-----|-------|

| 33 | nSTATUS   | 67 | I/O35 |     |       |

| 34 | I/O12     | 68 | I/O36 |     |       |

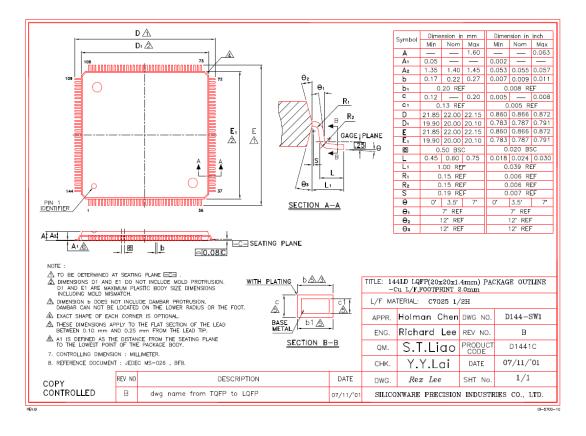

# 5.4 144-Pin Low-profile Quad Flat Package (LQFP144) with

# internal flash

Angelo is available in the 144-pin low-profile quad flat package with internal flash. **Table 5.4** lists all the package pins. They are arranged in pin numbers.

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name    | Pin<br>Number | Pin Name |

|---------------|----------|---------------|-------------|---------------|----------|

| 1             | I/O1     | 49            | IO27        | 97            | IO63     |

| 2             | I/O2     | 50            | GND         | 98            | GND      |

| 3             | I/O3     | 51            | VCCIO3      | 99            | VCCINT   |

| 4             | I/O4     | 52            | IO28        | 100           | VCCIO6   |

| 5             | I/O5     | 53            | IO29        | 101           | IO64     |

| 6             | I/O6     | 54            | VCCINT      | 102           | IO65     |

| 7             | I/07     | 55            | GND         | 103           | I/O66    |

| 8             | I/O8     | 56            | I/O30       | 104           | I/O67    |

| 9             | I/O9     | 57            | VCCA_PLL0   | 105           | I/O68    |

| 10            | VCCINT   | 58            | GNDA_PLL0   | 106           | I/O69    |

| 11            | GND      | 59            | I/O31(CLK0) | 107           | I/O70    |

| 12            | I/O10    | 60            | I/O32(CLK1) | 108           | GND      |

| 13            | I/O11    | 61            | I/O33       | 109           | GND      |

| 14            | GND      | 62            | I/O34       | 110           | I/071    |

| 15            | VCCIO0   | 63            | I/O35       | 111           | I/072    |

| 16            | nHOLDB   | 64            | I/O36       | 112           | I/O73    |

| 17            | I/O12    | 65            | GND         | 113           | I/O74    |

| 18            | I/O13    | 66            | VCCIO4      | 114           | I/O75    |

| 19            | I/O14    | 67            | I/O37       | 115           | VCCI07   |

| 20            | TMS      | 68            | I/O38       | 116           | I/O76    |

| 21            | тск      | 69            | I/O39       | 117           | I/077    |

|    | 1         |    |             | I   |             |

|----|-----------|----|-------------|-----|-------------|

| 22 | TDI       | 70 | I/O40(nCEO) | 118 | I/O78       |

| 23 | TDO       | 71 | I/O41       | 119 | I/O79       |

| 24 | I/O15     | 72 | I/O42       | 120 | I/O80       |

| 25 | I/O16     | 73 | I/O43       | 121 | VCCA_PLL1   |

| 26 | I/O17     | 74 | I/O44       | 122 | GNDA_PLL1   |

| 27 | I/O18     | 75 | I/O45       | 123 | I/O81(CLK2) |

| 28 | VCCINT    | 76 | I/O46       | 124 | I/O82(CLK3) |

| 29 | GND       | 77 | GND         | 125 | I/O83       |

| 30 | I/O19     | 78 | VCCINT      | 126 | I/O84       |

| 31 | I/O20     | 79 | I/O47       | 127 | I/O85       |

| 32 | I/O21     | 80 | I/O48       | 128 | I/O86       |

| 33 | I/O22     | 81 | I/O49       | 129 | VCCINT      |

| 34 | GND       | 82 | I/O50       | 130 | GND         |

| 35 | nHOLDT    | 83 | I/O51       | 131 | GND         |

| 36 | VCCIO1    | 84 | I/O52       | 132 | VCCIO8      |

| 37 | VCCIO2    | 85 | I/O53       | 133 | I/O87       |

| 38 | GND       | 86 | I/O54       | 134 | I/O88       |

| 39 | nCONFIG   | 87 | I/O55       | 135 | I/O89       |

| 40 | nCE       | 88 | VCCIO5      | 136 | I/O90       |

| 41 | MSEL0     | 89 | GND         | 137 | I/O91       |

| 42 | MSEL1     | 90 | I/O56       | 138 | I/O92       |

| 43 | I/O23     | 91 | I/O57       | 139 | GND         |

| 44 | I/O24     | 92 | I/O58       | 140 | VCCIO9      |

| 45 | I/O25     | 93 | I/O59       | 141 | I/O93       |

| 46 | CONF_DONE | 94 | I/O60       | 142 | I/O94       |

| 47 | nSTATUS   | 95 | I/O61       | 143 | I/O95       |

| 48 | I/O26     | 96 | I/O62       | 144 | I/O96       |

# 5.5 208-Pin Plastic Quad Flat Package (PQFP208) with internal flash

Angelo is available in the 208-pin plastic quad flat package with internal flash. **Table 5.5** lists all the package pins. They are arranged in pin number.

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name    | Pin Number | Pin Name |

|---------------|----------|---------------|-------------|------------|----------|

| 1             | I/O1     | 71            | GND         | 141        | I/O103   |

| 2             | I/O2     | 72            | VCCIO4      | 142        | GND      |

| 3             | I/O3     | 73            | I/O47       | 143        | VCCINT   |

| 4             | I/O4     | 74            | I/O48       | 144        | I/O104   |

| 5             | I/O5     | 75            | I/O49       | 145        | I/O105   |

| 6             | I/O6     | 76            | I/O50       | 146        | VCCI08   |

| 7             | I/07     | 77            | I/O51       | 147        | I/O106   |

| 8             | VCCI00   | 78            | I/O52       | 148        | I/O107   |

| 9             | GND      | 79            | VCCINT      | 149        | I/O108   |