# PIO-24.PCI ™ USER MANUAL

#### Part # 8008

**Sealevel Systems, Inc** 155 Technology Place P.O. Box 830

Liberty, SC 29657 USA

Phone: (864) 843-4343 FAX: (864) 843-3067 www.sealevel.com

# **Contents**

| INTRODUCTION                                                   | 1       |

|----------------------------------------------------------------|---------|

| Overview                                                       | 1       |

| What's Included                                                |         |

| INSTALLATION                                                   |         |

|                                                                |         |

| CARD SETUP                                                     |         |

| SOFTWARE INSTALLATION                                          |         |

| Linux Users                                                    |         |

| System Installation                                            |         |

| TECHNICAL DESCRIPTION                                          | 3       |

| WINDOWS SOFTWARE                                               | 3       |

| LINUX SOFTWARE                                                 | 3       |

| 3 <sup>rd</sup> Party Software Support                         |         |

| 50 PIN RIBBON CABLE PIN OUT                                    |         |

| ELECTRICAL CHARACTERISTICS                                     | 6       |

| Pull Ups                                                       |         |

| PROGRAMMING                                                    |         |

|                                                                |         |

| Application Programmers Interface (API)                        |         |

| Reading the Inputs:                                            | ٥       |

| Reading the Outputs:                                           | ٥       |

| Presetting an Output Port:                                     |         |

| Writing the Outputs:                                           |         |

| Interrupts:                                                    |         |

| Port Confirmation                                              |         |

| Port Configuration:RELATIVE ADDRESSING VS. ABSOLUTE ADDRESSING |         |

| Addressing ContinuedAddressing Continued                       |         |

| · · · · · · · · · · · · · · · · · · ·                          |         |

| DIRECT HARDWARE CONTROL                                        |         |

| Reading the Inputs:                                            |         |

| Reading the Outputs:Presetting an Output Port:                 | 13      |

| Writing the Outputs:                                           |         |

| Bit Set/Reset                                                  |         |

| Port Configuration:                                            |         |

| Interrupts                                                     |         |

| Register Description (for direct hardware cont                 | rol) 14 |

| Control Words                                                  |         |

| I/O Configuration                                              |         |

| Bit Set or Reset Port C                                        |         |

| Interrupt control                                              |         |

| Interrupt mode select table                                    |         |

| Interrupt Read                                                 |         |

| SDECIFICATIONS                                                 |         |

| ENVIRONMENTAL SPECIFICATIONS                                 | 18         |

|--------------------------------------------------------------|------------|

| POWER CONSUMPTION                                            | 18         |

| MEAN TIME BETWEEN FAILURES (MTBF)                            | 18         |

| PHYSICAL DIMENSIONS                                          |            |

| APPENDIX A - TROUBLESHOOTING                                 | 19         |

| APPENDIX B - HOW TO GET ASSISTANCE                           | 20         |

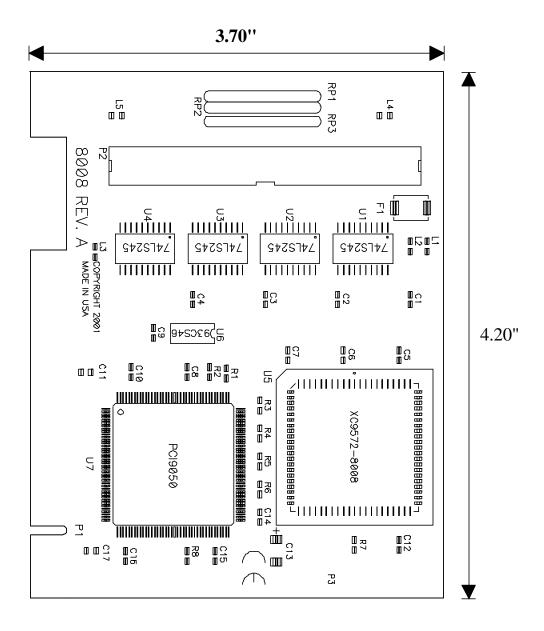

| APPENDIX C - SILK-SCREEN                                     | <b>2</b> 1 |

| APPENDIX D - COMPLIANCE NOTICES                              | 22         |

| FEDERAL COMMUNICATIONS COMMISSION STATEMENT                  |            |

| EMC DIRECTIVE STATEMENT                                      |            |

| WARRANTY                                                     | 23         |

| FIGURES                                                      |            |

| Figure 1-50 Pin Ribbon Cable Pin Out                         | 5          |

| Figure 2-Electrical Characteristics                          | 6          |

| Figure 3-Pull Up Resistors                                   | 7          |

| Figure 4-Control Words                                       |            |

| Figure 5-Absolute byte Address, (any configuration)          | 11         |

| Figure 6-Relative Byte Address                               | 11         |

| Figure 7-Relative Byte Address Continued                     | 11         |

| Figure 8-Relative Byte Address                               |            |

| Figure 9-Register Description                                |            |

| Figure 10-I/O Configuration                                  | 15         |

| Figure 11-Control Word, Port Setup                           |            |

| Figure 12-Bit Set or Reset                                   |            |

| Figure 13-Interrupt Control Tables                           | 17         |

| © 20011 Sealevel Systems, Incorporated. All rights reserved. |            |

#### Introduction

#### Overview

The Sealevel Systems **PIO-24.PCI** provides one 8255 mode 0 compatible port providing two eight-bit ports and two four-bit ports. When configured as outputs each bit of the two four-bit ports may be set or reset individually.

#### What's Included

The **PIO-24.PCI** is shipped with the following items. If any of these items is missing or damaged, contact the supplier.

- PIO-24.PCI Adapter

- Sealevel Software CD

- Industry Standard Relay Rack Cables are Available: Part number CA135 for Edge Connection Part number CA167 for IDC Connection

#### **Installation**

#### **Card Setup**

The **PIO-24.PCI** is a fully compliant PCI 'Plug and Play' adapter. All card resources (i.e. I/O address, IRQ selection) are auto-assigned by either your system BIOS or your 'Plug and Play' operating system.

#### **Software Installation**

For proper operation install software first. To install the software place the CD in your CD-ROM tray and the auto-run program will start. If auto-run is not available browse the CD and choose "index.htm". Choose **Install Software** at the beginning of the CD. Select the **Digital I/O** software drivers and install **SeaIO** prior to installing hardware.

#### **Linux Users**

Refer to the installation instructions at the beginning of the CD for details on installing the Sealevel Systems digital I/O cards in Linux.

#### **System Installation**

The PIO-24.PCI can be installed in any of the PCI expansion slots.

- 1. Turn off PC power. Disconnect the power cord.

- 2. Remove the PC case cover.

- 3. Locate an available PCI slot and remove the blank metal slot cover.

- 4. Remove the clamping portion of the bracket from the card.

- 5. Gently insert the **PIO-24.PCI** into the slot. Make sure that the adapter is seated properly.

- 6. Feed the 50-pin ribbon cable through the cutout bracket and connect it to the card.

- 7. Replace the bracket retaining screw.

- 8. Install the clamping portion of the bracket

- 9. Replace the computer cover.

- 10. Connect the power cord. Installation is complete.

#### **Technical Description**

The **PIO-24.PCI** provides 24 channels of digital I/O configurable as inputs or outputs, which can be utilized for PC based control and automation of equipment including: sensors, switches, satellite antenna control systems, video and audio studio automation, security control systems, and other industrial automation systems.

#### **Windows Software**

The **PIO-24.PCI** ships with Sealevel Systems' Seal/O suite of Windows 98/NT/ME/2000 drivers. Seal/O provides the user with a consistent and straightforward API, allowing the developer to concentrate on the details of the application as opposed to low level driver development. Popular development environments, including Visual C++, Visual Basic, and Delphi, are supported for application development. Seal/O includes a utility for configuring the driver parameters under Windows, further simplifying installation. Sample applications are included to facilitate rapid application development.

#### **Linux Software**

The **PIO-24.PCI** ships with software for Linux, including a kernel-mode driver, API, and the SeaIOTst diagnostic tool. The kernel-mode driver is provided as a module, so future driver upgrades may be performed with minimal (usually zero) downtime. The Linux API is identical to its Windows counterpart, facilitating quick and easy ports of existing SeaI/O-aware applications to the Linux operating system. All source code for the Linux software suite is provided under the GNU Public License (GPL v2.0), to assist in "roll-your-own"-type applications.

# 3<sup>rd</sup> Party Software Support

Third party software support for many HMI/MMI and other process control software is included on the product installation CD. For the most up to date information on third party software support, please visit http://www.sealevel.com/3rdpartysw.htm.

### 50 pin ribbon cable pin out

Figure 1-50 Pin Ribbon Cable Pin Out

| Description | Pin #            |

|-------------|------------------|

| P           | ort A            |

| A0          | 47               |

| A1          | 45               |

| A2          | 43               |

| A3          | 41               |

| A4          | 39               |

| A5          | 37               |

| A6          | 35               |

| A7          | 33               |

| P           | ort B            |

| B0          | 31               |

| B1          | 29               |

| B2          | 27               |

| B3          | 25               |

| B4          | 23               |

| B5          | 21               |

| B6          | 19               |

| B7          | 17               |

| P           | ort C            |

| C0          | 15               |

| C1          | 13               |

| C1<br>C2    | 11               |

| C3          | 9                |

| C4          | 7                |

| C5          | 9<br>7<br>5<br>3 |

| C6          | 3                |

| C7          | 1                |

|             |                  |

| GND         | All Even pins    |

| +5V         | 49               |

#### **Electrical Characteristics**

The table below provides the electrical characteristics of each Input/Output. Each port is buffered with a 74LS245 octal bi-directional transceiver. Each input is capable of sinking up to 24 mA, while each output can source up to 15 mA.

| Recommended Operating Conditions |     |        |  |  |

|----------------------------------|-----|--------|--|--|

| Min                              |     |        |  |  |

| Input                            | 0 V | 5.25 V |  |  |

| Source                           |     | 15 mA  |  |  |

| Sink                             |     | 24 mA  |  |  |

| Electrical Characteristics |                         |  |  |  |

|----------------------------|-------------------------|--|--|--|

| High Level Input Voltage   | Min 2 V                 |  |  |  |

| Low Level Input Voltage    | Max 0.8 V               |  |  |  |

|                            |                         |  |  |  |

| High Level Output Voltage  | Min 2 V at 15 mA        |  |  |  |

|                            | Typically 3.4 V at 3 mA |  |  |  |

| Low Level Output Voltage   | Max 0.55 V at 24 mA     |  |  |  |

Figure 2-Electrical Characteristics

### **Pull Ups**

Nine or ten pin bussed resistor packs are installed to provide pull-ups to the input ports. These are installed on all ports. The pull-up resistor packs are rated at 10K ohms. Figure 3 below provides the bussed resistor and corresponding port. The resistors insure that no line is floating which is not connected. This provides consistent biasing on all un-terminated lines.

| Bussed   | Corresponding |

|----------|---------------|

| Resistor | Port          |

| RP1      | Port A        |

| RP2      | Port B        |

| RP3      | Port C        |

Figure 3-Pull Up Resistors

#### **Programming**

#### **Application Programmers Interface (API)**

Most modern operating systems do not allow direct hardware access. The SeaIO driver and API have been included to provide control over the hardware in Windows and Linux environments. The purpose of this section of the manual is to help the customer with the mapping of the API to the actual inputs for the **PIO-24.PCI** specifically. Complete documentation of the API can be found in its accompanying help file.

#### **Reading the Inputs:**

The API presents the inputs as active low. If an input is driven high (2V to 5.25 V) it will read as a logical zero (0), if driven low (0V to 0.8V) it will read as a logical one (1). If an input is not driven it will read as a zero (0) due to the 10K ohm pull up resistors on each port.

#### **Reading the Outputs:**

The API returns the complement of value that is currently being used to drive the outputs. The outputs cannot be read with relative addressing, absolute addressing must be used. Refer to **Relative Addressing vs. Absolute Addressing** for more information.

#### **Presetting an Output Port:**

Each port has an output register associated with it. This register may be written and retains its value whether the port is configured as an input or an output. To preset the value of an output port the program should write to the port when it is configured as an input then configure it as an output. Inputs cannot be written to with relative addressing, absolute addressing must be used. See **Relative Addressing vs. Absolute Addressing** below.

#### **Writing the Outputs:**

The outputs are active high. Writing a one (1) corresponds to 5V while writing a zero (0) corresponds to 0V, at the output.

#### **Interrupts:**

Interrupt sampling can be set up in the API. **Port A bit zero is the interrupt source(pin 47)**. Refer to the API section in the SeaI/O help file for more detailed information.

#### Port C

Port C has the ability to be configured as two four bit ports. If both lower and upper nibbles are configured the same then no special considerations need to be made. But if they are configured differently, one nibble as input, and one as output then the user will have to keep this in mind.

#### Port C absolute addressing (when port C is split)

When reading, the input nibble will be returned on the corresponding upper or lower nibble while the outputs will be returned on their corresponding upper or lower nibble. When writing, the corresponding nibble will be written to the output nibble, while the input nibble will have its output register written to. The output register can be written to without affecting the inputs. These will be eight bit operations and it will up to the programmer to keep track of the two four bit nibbles.

#### Port C relative addressing (when port C is split)

The input and output nibbles will each be treated as individual four bit ports.

#### **Port Configuration:**

Each eight-bit port can be configured as inputs or outputs. The API provides a set adapter state call to access the control words. For this device, one control word is used.

**Note:** The control panel also allows you to configure the device. Your program can over ride the control panel configuration when executed, but the control panel configuration will be the default on power up. The default settings are based on the settings in the control panel application when last changed and saved after re-booting.

# Control Words I/O Configuration

| CWnD0 | Port C1 lower nibble (bits 0-3) | 1 = input              | 0 = output | 1 on power up |  |

|-------|---------------------------------|------------------------|------------|---------------|--|

| CWnD1 | Port B1                         | 1 = input $0 = output$ |            | 1 on power up |  |

| CWnD2 | 0                               | or 1 (no effec         | et)        |               |  |

| CWnD3 | Port C1 upper nibble (bits 4-7) | 1 = input              | 0 = output | 1 on power up |  |

| CWnD4 | Port A1                         | 1 = input $0 = output$ |            | 1 on power up |  |

| CWnD5 | 0 or 1 (no effect)              |                        |            |               |  |

| CWnD6 | 0 or 1 (no effect)              |                        |            |               |  |

| CWnD7 | Always a 1                      |                        |            |               |  |

Figure 4-Control Words

#### Relative Addressing vs. Absolute Addressing

The SeaIO API makes a distinction between "absolute" and "relative" addressing modes. In absolute addressing mode, the Port argument to the API function acts as a simple byte offset from the base I/O address of the device. For instance, Port #0 refers to the I/O address base + 0; Port #1 refers to the I/O address base + 1.

Relative addressing mode, on the other hand, refers to input and output ports in a logical fashion. With a Port argument of 0 and an API function meant to output data, the first  $(0^{th})$  output port on the device will be utilized. Likewise, with a Port argument of 0 and an API function designed to input data, the first  $(0^{th})$  input port of the device will be utilized.

In all addressing modes, port numbers are zero-indexed; that is, the first port is port #0, the second port is #1, the third #2, and so on.

Tables 5-8 give the: API Port/bit reference numbers for Absolute and Relative Addressing

R = Read

W = Write

R/W = Read or Write

| Port | API Port # Absolute<br>Address (function) |

|------|-------------------------------------------|

| A    | 0 ( R/W )                                 |

| В    | 1 ( R/W )                                 |

| С    | 2 ( R/W )                                 |

Figure 5-Absolute byte Address, (any configuration)

| Port | API Port # Relative Address<br>(function) | Port Type   |

|------|-------------------------------------------|-------------|

| A    | 0(R)                                      | Input Port  |

| В    | 0 ( W )                                   | Output Port |

| С    | 1 ( W )                                   | Output Port |

Figure 6-Relative Byte Address

Relative byte Address Given: Inputs A,

Outputs B, C

| Port    | API Port # Relative Address<br>(function) | Port Type   |

|---------|-------------------------------------------|-------------|

| A       | 0(R)                                      | Input Port  |

| В       | 0 ( W )                                   | Output Port |

| C Lower | 1 ( W )                                   | Output Port |

| C Upper | 1 ( R )                                   | Input Port  |

Figure 7-Relative Byte Address Continued

Relative byte Address Given: Inputs A, C Upper Outputs B, C Lower

# **Addressing Continued**

Figure~8-Relative~Byte~Address

Relative Address Given: Inputs A, C Upper Outputs B, C Lower

| API Bit # Absolute<br>Address (function) | API Bit # Relative<br>Address (function) | Port Bit    |

|------------------------------------------|------------------------------------------|-------------|

| radicis (taliction)                      | ridaress (runction)                      |             |

| 0 ( R/w )                                | 0(R)                                     | A0 - Input  |

| 1 ( R/w )                                | 1(R)                                     | A1 - Input  |

| 2 ( R/w )                                | 2(R)                                     | A2 - Input  |

| 3 ( R/w )                                | 3(R)                                     | A3 - Input  |

| 4 ( R/w )                                | 4 ( R )                                  | A4 - Input  |

| 5 ( R/w )                                | 5(R)                                     | A5 - Input  |

| 6 ( R/w )                                | 6(R)                                     | A6 - Input  |

| 7 ( R/w )                                | 7 (R)                                    | A7 - Input  |

| 8 ( R/w )                                | 0 ( W )                                  | B0 - Output |

| 9 ( R/w )                                | 1 ( W )                                  | B1 - Output |

| 10 ( R/w )                               | 2 (W)                                    | B2 - Output |

| 11 ( R/w )                               | 3 (W)                                    | B3 - Output |

| 12 ( R/w )                               | 4 ( W )                                  | B4 - Output |

| 13 ( R/w )                               | 5 (W)                                    | B5 - Output |

| 14 ( R/w )                               | 6 ( W )                                  | B6 - Output |

| 15 ( R/w )                               | 7 (W)                                    | B7 - Output |

| 16 ( R/W )                               | 8 ( W )                                  | C0 - Output |

| 17 ( R/W )                               | 9 (W)                                    | C1 - Output |

| 18 ( R/W )                               | 10( W )                                  | C2 - Output |

| 19 ( R/W )                               | 11( W )                                  | C3 - Output |

| 20 ( R/W )                               | 8(R)                                     | C4 - Input  |

| 21 ( R/W )                               | 9(R)                                     | C5 - Input  |

| 22 ( R/W )                               | 10(R)                                    | C6 - Input  |

| 23 ( R/W )                               | 11( R)                                   | C7 - Input  |

#### **Direct Hardware Control**

In systems where the users program has direct access to the hardware (DOS) the tables below gives the mapping and functions that the **PIO-24.PCI** provide. The address of each eight-bit port is calculated as shown in the table on the following page, the cards base address plus an offset.

#### **Reading the Inputs:**

The inputs are active high. If an input is driven high (2V to 5.25 V) it will read as a logical one (1), if driven low (0V to 0.8V) it will read as a logical zero (0). If an input is not driven it will read as a one due to the 10K ohm pull up resistors on each port.

#### **Reading the Outputs:**

The value that is currently being used to drive the outputs will be returned.

#### **Presetting an Output Port:**

Each port has an output register associated with it. This register may be written and retains its value whether the port is configured as an input or an output. To preset the value of an output port the program should write to the port when it is configured as an input then configure it as an output.

#### **Writing the Outputs:**

The outputs are active high. Writing a one (1) corresponds to 5V while writing a zero (0) corresponds to 0V, at the output.

#### Bit Set/Reset

Port C supports bit set/reset as shown in the tables below.

#### **Port Configuration:**

Each port can be configured as an input or an output by writing to its direction control bit, refer to the tables below.

#### **Interrupts**

Interrupts can be set up as shown in the tables below. Port A1 bit zero is the interrupt source, (pin 47).

#### Port C

Port C is written and read to as a single eight bit port, but it has the ability to be configured as two four bit ports. If both lower and upper nibbles are configure the same then no special considerations need to be made. But if they are configured differently, one nibble as input, and one as output then the user will have to keep this in mind. When reading, the input will be returned on the corresponding upper or lower nibble while the current outputs will be returned on their corresponding upper or lower nibble. When writing, the corresponding nibble will be written to the output nibble, while the input nibble will have its output register written to. The output register can be written to without affecting the inputs.

### Register Description (for direct hardware control)

| Address | Port ID           | Mode | <b>D7</b> | <b>D6</b> | <b>D5</b> | D4   | D3   | D2    | D1     | D0     |

|---------|-------------------|------|-----------|-----------|-----------|------|------|-------|--------|--------|

| Base+0  | Port A            | R/W  | PAD7      | PAD6      | PAD5      | PAD4 | PAD3 | PAD2  | PAD1   | PAD0   |

| Base+1  | Port B            | R/W  | PBD7      | PBD6      | PBD5      | PBD4 | PBD3 | PBD2  | PBD1   | PBD0   |

| Base+2  | Port C            | R/W  | PCD7      | PCD6      | PCD5      | PCD4 | PCD3 | PCD2  | PCD1   | PCD0   |

| Base+3  | Control Word Port | W    | CWD7      | 0         | 0         | CWD4 | CWD3 | 0     | CWD1   | CWD0   |

| Base+4  | Int. Config. Port | R/W  | 0         | 0         | 0         | 0    | 0    | IRQEN | IRQC11 | IRQC10 |

| Base+5  | Int. Status Port  | R    | 0         | 0         | 0         | 0    | 0    | 0     | 0      | IRQST  |

Figure 9-Register Description

### **Control Words**

### I/O Configuration

| CWnD0 | Port C1 lower nibble (bits 0-3) | 1 = input      | 0 = output | 1 on power up |  |

|-------|---------------------------------|----------------|------------|---------------|--|

| CWnD1 | Port B1                         | 1 = input      | 0 = output | 1 on power up |  |

| CWnD2 | 0 or 1 (no effect)              |                |            |               |  |

| CWnD3 | Port C1 upper nibble (bits 4-7) | 1 = input      | 0 = output | 1 on power up |  |

| CWnD4 | Port A1                         | 1 = input      | 0 = output | 1 on power up |  |

| CWnD5 | 0                               | or 1 (no effec | et)        |               |  |

| CWnD6 | 0 or 1 (no effect)              |                |            |               |  |

| CWnD7 |                                 | Always a 1     |            |               |  |

Figure 10-I/O Configuration

|   | ( | Contr | ol W | ord (2 | X = 0 | ) |   | Hex Value |     |     | Port Setup |         |

|---|---|-------|------|--------|-------|---|---|-----------|-----|-----|------------|---------|

| 7 | 6 | 5     | 4    | 3      | 2     | 1 | 0 |           | A   | В   | C Upper    | C Lower |

| 1 | X | X     | 0    | 0      | X     | 0 | 0 | 80        | Out | Out | Out        | Out     |

| 1 | X | X     | 0    | 0      | X     | 0 | 1 | 81        | Out | Out | Out        | In      |

| 1 | X | X     | 0    | 0      | X     | 1 | 0 | 82        | Out | In  | Out        | Out     |

| 1 | X | X     | 0    | 0      | X     | 1 | 1 | 83        | Out | In  | Out        | In      |

| 1 | X | X     | 0    | 1      | X     | 0 | 0 | 88        | Out | Out | In         | Out     |

| 1 | X | X     | 0    | 1      | X     | 0 | 1 | 89        | Out | Out | In         | In      |

| 1 | X | X     | 0    | 1      | X     | 1 | 0 | 8A        | Out | In  | In         | Out     |

| 1 | X | X     | 0    | 1      | X     | 1 | 1 | 8B        | Out | In  | In         | In      |

| 1 | X | X     | 1    | 0      | X     | 0 | 0 | 90        | In  | Out | Out        | Out     |

| 1 | X | X     | 1    | 0      | X     | 0 | 1 | 91        | In  | Out | Out        | In      |

| 1 | X | X     | 1    | 0      | X     | 1 | 0 | 92        | In  | In  | Out        | Out     |

| 1 | X | X     | 1    | 0      | X     | 1 | 1 | 93        | In  | In  | Out        | In      |

| 1 | X | X     | 1    | 1      | X     | 0 | 0 | 98        | In  | Out | In         | Out     |

| 1 | X | X     | 1    | 1      | X     | 0 | 1 | 99        | In  | Out | In         | In      |

| 1 | X | X     | 1    | 1      | X     | 1 | 0 | 9A        | In  | In  | In         | Out     |

| 1 | X | X     | 1    | 1      | X     | 1 | 1 | 9B        | In  | In  | In         | In      |

Figure 11-Control Word, Port Setup

### Bit Set or Reset Port C

| CWD0 | 1 = set to + 5V    | 0 = Reset to GND      |  |

|------|--------------------|-----------------------|--|

| CWD4 | 0 or 1 (n          | o effect)             |  |

| CWD5 | 0 or 1 (no effect) |                       |  |

| CWD6 | 0 or 1 (n          | o effect)             |  |

| CWD7 | Always a zero when | n using Bit set/reset |  |

| Bit Select |       |       |        |  |  |  |

|------------|-------|-------|--------|--|--|--|

| CWnD3      | CWnD2 | CWnD1 | C1 Bit |  |  |  |

| 0          | 0     | 0     | = 0    |  |  |  |

| 0          | 0     | 1     | = 1    |  |  |  |

| 0          | 1     | 0     | = 2    |  |  |  |

| 0          | 1     | 1     | = 3    |  |  |  |

| 1          | 0     | 0     | = 4    |  |  |  |

| 1          | 0     | 1     | = 5    |  |  |  |

| 1          | 1     | 0     | = 6    |  |  |  |

| 1          | 1     | 1     | = 7    |  |  |  |

| Control Word $(X = 0)$ |       |   |   |   |   |     | Hex Value | Port C |     |

|------------------------|-------|---|---|---|---|-----|-----------|--------|-----|

| 7                      | 6     | 5 | 4 | 3 | 2 | 1   | 0         |        | Bit |

|                        | Reset |   |   |   |   |     |           |        |     |

| 0                      | X     | X | X | 0 | 0 | 0   | 0         | 00     | 0   |

| 0                      | X     | X | X | 0 | 0 | 1   | 0         | 02     | 1   |

| 0                      | X     | X | X | 0 | 1 | 0   | 0         | 04     | 2   |

| 0                      | X     | X | X | 0 | 1 | 1   | 0         | 06     | 3   |

| 0                      | X     | X | X | 1 | 0 | 0   | 0         | 08     | 4   |

| 0                      | X     | X | X | 1 | 0 | 1   | 0         | 0A     | 5   |

| 0                      | X     | X | X | 1 | 1 | 0   | 0         | 0C     | 6   |

| 0                      | X     | X | X | 1 | 1 | 1   | 0         | 0E     | 7   |

|                        |       |   |   |   | ( | Set |           |        |     |

| 0                      | X     | X | X | 0 | 0 | 0   | 1         | 01     | 0   |

| 0                      | X     | X | X | 0 | 0 | 1   | 1         | 03     | 1   |

| 0                      | X     | X | X | 0 | 1 | 0   | 1         | 05     | 2   |

| 0                      | X     | X | X | 0 | 1 | 1   | 1         | 07     | 3   |

| 0                      | X     | X | X | 1 | 0 | 0   | 1         | 09     | 4   |

| 0                      | X     | X | X | 1 | 0 | 1   | 1         | 0B     | 5   |

| 0                      | X     | X | X | 1 | 1 | 0   | 1         | 0D     | 6   |

| 0                      | X     | X | X | 1 | 1 | 1   | 1         | 0F     | 7   |

Figure 12-Bit Set or Reset

### **Interrupt control**

| IRQENX | interrupt enable | 1 = enabled      | 0 = disabled  (0  on power up ) |

|--------|------------------|------------------|---------------------------------|

| IRQCX0 | Interru          | pt mode select s | ee table                        |

| IRQCX1 | Interru          | pt mode select s | ee table                        |

### Interrupt mode select table

| IRQCX1 | IRQCX0 | INT Type     |

|--------|--------|--------------|

| 0      | 0      | Low level    |

| 0      | 1      | High level   |

| 1      | 0      | Falling edge |

| 1      | 1      | Rising edge  |

### **Interrupt Read**

Reading this port clears a pending interrupt

| IRQST1 | (D0) Interrupt status | 1 = interrupt pending, $0 = $ none |

|--------|-----------------------|------------------------------------|

| IROST2 | (D4) Interrupt status | 1 = interrupt pending, 0 = none    |

Figure 13-Interrupt Control Tables

# **Specifications**

### **Environmental Specifications**

| Specification         | Operating       | Storage         |

|-----------------------|-----------------|-----------------|

| Temperature           | 0° to 50° C     | -20° to 70° C   |

| Range                 | (32° to 122° F) | (-4° to 158° F) |

| <b>Humidity Range</b> | 10 to 90% R.H.  | 10 to 90% R.H.  |

|                       | Non-Condensing  | Non-Condensing  |

### **Power Consumption**

| Supply line | +5 VDC |

|-------------|--------|

| Rating      | 480mA  |

### **Mean Time Between Failures (MTBF)**

Greater than 150,000 hours. (Calculated)

### **Physical Dimensions**

| Board Length                       | 4.72 inches  | (11.988 cm.) |

|------------------------------------|--------------|--------------|

| Board Height including Goldfingers | 3.70 inches  | (9.398cm.)   |

| Board Height excluding Goldfingers | 3.375 inches | (8.572 cm.)  |

### Appendix A - Troubleshooting

Following these simple steps can eliminate most common problems.

Install software <u>first</u>. After installing the software then proceed to adding the hardware. This places the required installation files in the correct locations.

- 1. Read this manual thoroughly before attempting to install the adapter in your system.

- 2. Use Device Manager under Windows to verify proper installation.

- 3. Use the SeaIO control panel applet for card identification and configuration.

- 4. If these steps do not solve your problem, please call Sealevel Systems' Technical Support, (864) 843-4343. Our technical support is free and available from 8:00AM-5PM Eastern Time Monday through Friday.

### Appendix B - How To Get Assistance

Please refer to Troubleshooting Guide prior to calling Technical Support.

- 1. Begin by reading through the Trouble Shooting Guide in Appendix A. If assistance is still needed please see below.

- 2. When calling for technical assistance, please have your user manual and current adapter settings. If possible, please have the adapter installed in a computer ready to run diagnostics.

- 3. Sealevel Systems provides an FAQ section on its web site. Please refer to this to answer many common questions. This section can be found at <a href="http://www.sealevel.com/faq.htm">http://www.sealevel.com/faq.htm</a>.

- 4. Sealevel Systems maintains a Home page on the Internet. Our home page address is <a href="www.sealevel.com">www.sealevel.com</a>. The latest software updates, and newest manuals are available via our FTP site that can be accessed from our home page.

- 5. Technical support is available Monday to Friday from 8:00 a.m. to 5:00 p.m. eastern time. Technical support can be reached at (864) 843-4343.

RETURN AUTHORIZATION MUST BE OBTAINED FROM SEALEVEL SYSTEMS BEFORE RETURNED MERCHANDISE WILL BE ACCEPTED. AUTHORIZATION CAN BE OBTAINED BY CALLING SEALEVEL SYSTEMS AND REQUESTING A RETURN MERCHANDISE AUTHORIZATION (RMA) NUMBER.

# Appendix C - Silk-Screen

### **Appendix D - Compliance Notices**

#### **Federal Communications Commission Statement**

FCC - This equipment has been tested and found to comply with the limits for Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference. In such case the user will be required to correct the interference at his own expense.

#### **EMC Directive Statement**

Products bearing the CE Label fulfill the requirements of the EMC directive (89/336/EEC) and of the low-voltage directive (73/23/EEC) issued by the European Commission.

To obey these directives, the following European standards must be met:

- EN55022 Class A "Limits and methods of measurement of radio interference characteristics of information technology equipment"

- EN55024 -'Information technology equipment Immunity characteristics Limits and methods of measurement'

- EN60950 (IEC950) "Safety of information technology equipment, including electrical business equipment"

#### Warning

This is a Class A Product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

Always use cabling provided with this product if possible. If no cable is provided or if an alternate cable is required, use high quality shielded cabling to maintain compliance with FCC/EMC directives.

### Warranty

WARRANTY Sealevel Systems, Inc. provides a limited lifetime warranty. Should this product fail to be in good working order at any time, Sealevel Systems will, at it's option, replace or repair it at no additional charge except as set forth in the following terms. This warranty does not apply to products damaged by misuse, modifications, accident or disaster.

Sealevel Systems assumes no liability for any damages, lost profits, lost savings or any other incidental or consequential damage resulting from the use, misuse of, or inability to use this product. Sealevel Systems will not be liable for any claim made by any other related party.

RETURN AUTHORIZATION MUST BE OBTAINED FROM SEALEVEL SYSTEMS BEFORE RETURNED MERCHANDISE WILL BE ACCEPTED. AUTHORIZATION CAN BE OBTAINED BY CALLING SEALEVEL SYSTEMS AND REQUESTING A RETURN MERCHANDISE AUTHORIZATION (RMA) NUMBER.

Sealevel Systems, Incorporated 155 Technology Place P.O. Box 830 Liberty, SC 29657 USA (864) 843-4343 FAX: (864) 843-3067 www.sealevel.com

email: support@sealevel.com

Technical Support is available from 8 a.m. to 5 p.m. Eastern time.

Monday - Friday

#### **Trademarks**

Sealevel Systems, Incorporated acknowledges that all trademarks referenced in this manual are the service mark, trademark, or registered trademark of the respective company.

PIO-24.PCI is a trademark of Sealevel Systems, Incorporated.