# Alliance Series 3.1i Quick Start Guide

Introduction

Implementation Tools Tutorial

Alliance FPGA Express Interface Notes

**Configuring Xprinter**

**Glossary of Terms**

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCl, RealPCl, 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235;

5.737.631: 5.742.178: 5.742.531: 5.744.974: 5.744.979: 5.744.995: 5.748.942: 5.748.979: 5.752.006: 5.752.035: 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5.828,231; 5.828,236; 5.828,608; 5.831,448; 5.831,460; 5.831,845; 5.831,907; 5.835,402; 5.838,167; 5.838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

### **About This Manual**

This manual provides an overview of the Alliance Series 3.1i Software, including a basic tutorial. This manual is geared towards the user who has already installed their software and online documentation, and set up their user environment variables.

Other publications you can consult for related information include the *Design Manager/Flow Engine Guide* and the *Alliance Release Notes* and *Installation Guide*.

**Note** This Xilinx software release is certified as Year 2000 compliant.

### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," provides general information on the Xilinx software.

- Chapter 2, "Implementation Tools Tutorial," provides a basic tutorial to illustrate the Xilinx design flow.

- Appendix A, "Alliance FPGA Express Interface Notes," describes installing and using FPGA Express for the Alliance 3.1i software.

- Appendix B, "Configuring Xprinter," provides information on how to print from Xilinx graphical interface programs on the workstation.

- "Glossary of Terms," provides definitions of basic terminology used in the Quick Start Guide.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                          |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools Search this database using the search function at http://support.xilinx.com/support/searchtd.htm                                                                                             |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                    |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                               |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                 |

### Conventions

This manual uses the following conventions. An example illustrates each convention.

### **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: - 100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt del net=

```

Courier bold also indicates commands that you select from a menu.

```

File \rightarrow Open

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

```

edif2ngd design_name

```

References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on|off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

```

allow block block name loc1 loc2locn;

```

#### Online Document

The following conventions are used for online documents.

Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.  Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Contents**

| Manual                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manual Contents i Additional Resources i |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ns                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Typographicali<br>Online Document i      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Introduction                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Supported Netlists                       | 1-2<br>1-3<br>1-5<br>1-6<br>1-8<br>1-9<br>1-9<br>1-11<br>1-12<br>1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Architecture Support                     | 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          | Manual Contents i Additional Resources i i Additional Resources i i ins  Typographical i Online Document i Introduction  Supported Netlists Operating System Compatibility i Xilinx Design Flow FPGA Design Flow CPLD Design Flow CPLD Design Flow CPLD Design Flow Software Manuals and Online Help Online Software Manuals i Software Manuals on the Web Online Help for Software Manuals Printing Software Manuals Printing PDF Files Printing From the Online Document Viewer EDA and Third Party Interface Support Software Installation and Licensing Support and Services Technical Support Customer Service |

| Chapter 2  | Implementation Tools Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|            | Installing the Tutorial Files Step 1: Creating an Implementation Project Design Manager Status Bar Design Manager Toolbox Step 2: Specifying Options Step 3: Translating the Design Step 4: Using the Constraints Editor How to Stop the Design Processing Flow Step 5: Mapping the Design Step 6: Using Timing Analysis to Evaluate Block Delays After Mapping Estimating Timing Goals With 50/50 Rule Report Paths In Timing Constraints Option Step 7: Placing and Routing the Design Step 8: Evaluating Post Layout Timing Step 9: Creating Timing Simulation Data Step 10: Creating Configuration Data Step 11: Using the PROM File Formatter | 2-3<br>2-9<br>2-9<br>2-12<br>2-14<br>2-17<br>2-18<br>2-20<br>2-21<br>2-22<br>2-22<br>2-25<br>2-27 |

| Appendix A | Alliance FPGA Express Interface Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                   |

|            | Additional Documentation  Alliance FPGA Express/Xilinx Design Flow  Installing FPGA Express  Entering a Design  Simulating a Design  Timing Constraints  Porting Code from FPGA Compiler to FPGA Express  Using LogiBLOX with FPGA Express                                                                                                                                                                                                                                                                                                                                                                                                         | A-2<br>A-4<br>A-4<br>A-5<br>A-5<br>A-5                                                            |

| Appendix B | Configuring Xprinter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                   |

|            | Required Wind/U Files Configuring .WindU Printer Information and PPD Files Unix Print Command Configuring Wind/U for Printing Defining a Port To Define a New Port To Modify an Existing Port Matching a Printer Type to a Defined Port To Match a Printer Device to a Port                                                                                                                                                                                                                                                                                                                                                                        | B-2<br>B-2<br>B-3<br>B-3<br>B-5<br>B-5<br>B-5                                                     |

| To Remove an Installed Printer | B-8  |

|--------------------------------|------|

| Specifying a Default Printer   |      |

| To Specify a Default Printer   |      |

| Setting Printer Options        |      |

| Sending Output to a File       |      |

| Solving Printing Problems      | B-12 |

# **Chapter 1**

### Introduction

This chapter contains general information on the Alliance 3.1i Software, including supported devices, design flow, documentation, installation, and licensing.

**Note** Complete software installation information is located in the *Alliance 3.1i Release Notes and Installation Guide.*

For complete information on the new features in this software release, refer to the "What's New" file included on your Alliance Implementation Tools CD-ROM. You can access this file through  $\mathtt{Start} \to \mathtt{Programs} \to \mathtt{Xilinx}$  Alliance.

For detailed information on configuring your third-party interface tools (such as Mentor Graphics, Synopsys, and Viewlogic) to work with the Alliance software flow, refer to the appropriate online interface guide at http://support.xilinx.com/support/sw\_manuals/3\_li/index.htm. For technical tips on the third-party interface tools, see http://support.xilinx.com/support/techsup/journals/index.htm.

This chapter contains the following sections.

- "Supported Netlists"

- "Operating System Compatibility"

- "Xilinx Design Flow"

- "Xilinx Development System Tools and Features"

- "Software Manuals and Online Help"

- "EDA and Third Party Interface Support"

- "Software Installation and Licensing"

- "Support and Services"

- "Architecture Support"

### **Supported Netlists**

You must use the Xilinx Unified Libraries to create your designs. Refer to the *Libraries Guide* for a list of components. The following table lists the netlist formats supported by the Xilinx software.

| Netlist Format | Variations            |

|----------------|-----------------------|

| EDIF           | SEDIF, EDN, EDF, EDIF |

| XNF            | SXNF, XFF, XTF, XNF   |

# **Operating System Compatibility**

The software in this release supports several operating systems, as shown in the following table.

Table 1-1 Operating System Compatibility

| Platform Type        | Version Number   |

|----------------------|------------------|

| Solaris <sup>®</sup> | Solaris 2.6/2.7  |

| HP Series 9000       | HP-UX 10.20/11.0 |

| Windows NT®          | NT 4.0           |

| Windows®             | Windows 98/2000  |

# Xilinx Design Flow

This section provides flow diagrams that illustrate the processing steps and flow of files in and out of the Design Manager for FPGAs and CPLDs.

**Note** For complete information on using the Design Manager, see the *Design Manager/Flow Engine Guide*.

### **FPGA Design Flow**

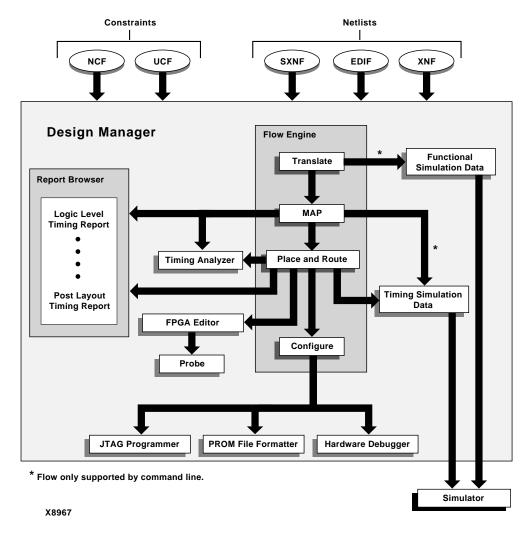

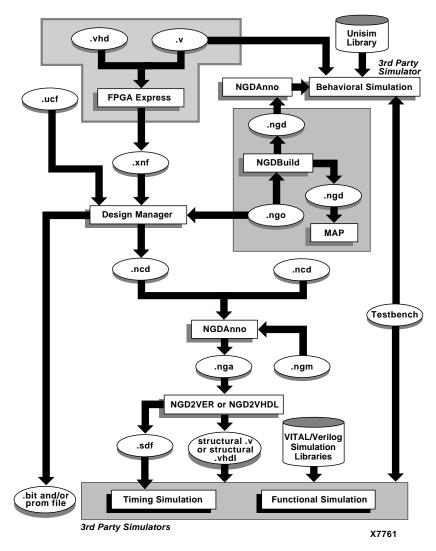

The following figure shows the processing steps and flow of files in and out of the Design Manager for FPGAs.

Figure 1-1 FPGA Design Flow

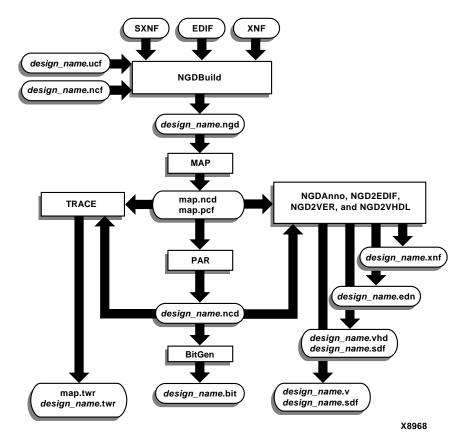

The following figure is a more detailed look at the various programs invoked during the FPGA design implementation process.

Figure 1-2 FPGA Detailed Design Flow

### **CPLD Design Flow**

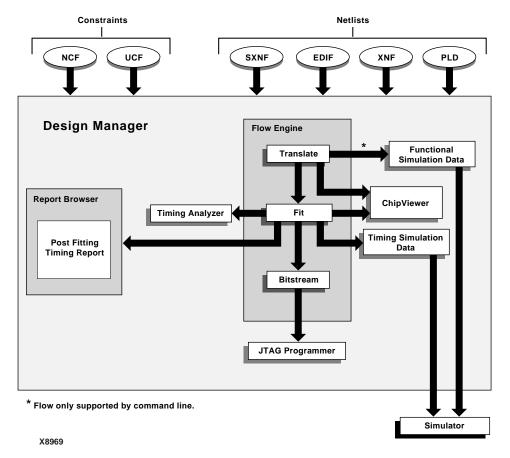

The following figure shows the processing steps and flow of files in and out of the Design Manager for CPLDs.

Figure 1-3 CPLD Design Flow

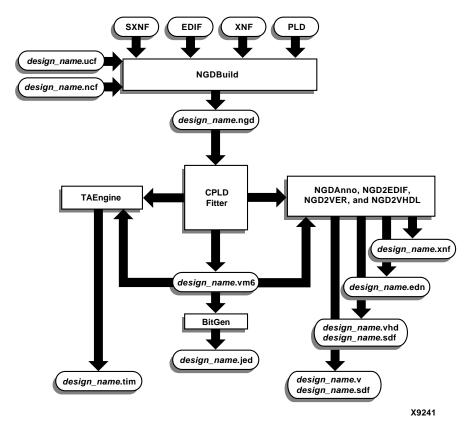

The following figure is a more detailed look at the various programs invoked during the CPLD design implementation process.

Figure 1-4 CPLD Detailed Design Flow

# Xilinx Development System Tools and Features

This section lists the tools and the main features of the Xilinx software. The tutorial in this manual provides a brief overview of how to use these software tools.

For detailed information on using the following tools, refer to the appropriate online software manual.

**Table 1-2 Xilinx Software Tools**

| Feature             | Description                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Design Manager      | Top level software module in the Xilinx Development<br>System. The Design Manager provides access to all the<br>tools you need to read a file from a design entry tool and<br>implement it in a device.                                                                                                                                        |  |

| Flow Engine         | Displays and executes all the steps needed to implement a Xilinx design, including translating design netlists; mapping logic to CLBs; placing and routing designs; creating a configuration file for downloading to a device; creating static timing reports; and creating timing simulation netlists in VHDL (Vital), Verilog, EDIF, or XNF. |  |

| LogiBLOX            | Graphical tool used to create high-level modules, such as counters, shift registers, and multiplexers.                                                                                                                                                                                                                                         |  |

| CORE Generator      | The CORE Generator tool generates and delivers parameterizable cores optimized for Xilinx devices.                                                                                                                                                                                                                                             |  |

| Floorplanner        | Graphical tool used to control the placement of your design into a target FPGA using a "drag and drop" paradigm with the mouse pointer.                                                                                                                                                                                                        |  |

| Constraints Editor  | Graphical tool used after running NGDBuild to add timing constraints and I/O pin locations.                                                                                                                                                                                                                                                    |  |

| FPGA Editor         | Graphical tool used to display and configure your designs before or after placing and routing.                                                                                                                                                                                                                                                 |  |

| Hardware Debugger   | Used to download your design to a device, verify the downloaded configuration, and display the internal states of the programmed device.                                                                                                                                                                                                       |  |

| PROM File Formatter | Creates files for serial or byte-wide configuration PROMs. Three formats are available: MCS, EXO, and TEK. The HEX format is also supported for microprocessor-based configuration.                                                                                                                                                            |  |

Table 1-3 Xilinx Software Features

| Feature                                      | Description                                                                                                                                                                                                                                                                           |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timing Specification Performance             | Xilinx software supports timing-driven placement and routing.                                                                                                                                                                                                                         |

| Multi-Pass PAR                               | The place and route (PAR) software allows multiple place and route iterations on a single machine, a $UNIX^{TM}$ network, or on multiple machines running in parallel. This feature provides optimum performance and efficiency, utilizing CPU time to achieve faster design results. |

| Re-Entrant Routing                           | Re-entrant routing skips placement and routes your design.<br>Routing begins with the existing placement and routing left in place.                                                                                                                                                   |

| Guide for Incre-<br>mental Design<br>Changes | You can select a previously mapped, routed, or fitted implementation revision to use as a guide for implementation.                                                                                                                                                                   |

### **Software Manuals and Online Help**

Xilinx provides software manuals and online help for its graphical user interface (GUI) tools and associated EDA software interfaces. You can access the online help with the Help → Help Topics menu option in each software tool. The following sections provide information on accessing and using the online software manuals.

#### **Online Software Manuals**

**Note** Complete directions for installing the online manuals and the Alliance Implementation software are located in the *Alliance 3.1i* Release Notes and Installation Guide.

The software manuals are provided on the Web and on your Documentation CD-ROM. You can install the manuals locally, read them from the CD-ROM, or read them on the Xilinx Web site. To view the online documentation, you must use a Java compatible internet browser. The online manuals include a powerful search function, as well as easy print options.

**Note** For best performance, Xilinx recommends that you use Netscape Navigator<sup>™</sup> version 4.5 (or higher) or Microsoft Internet Explorer version 5.0 (or higher) browser. You can install the Netscape browser from your software CD-ROM.

#### Software Manuals on the Web

The 3.1i software manuals are accessible from the Xilinx support Web site at the following location.

http://support.xilinx.com/support/sw\_manuals/3\_1i/

index.htm

#### **Online Help for Software Manuals**

Online help instructions for reading, browsing, and searching the online manuals are available through the Web browser interface. Click the **Help** button in the upper left-hand corner of the browser window to access the help topics.

### **Printing Software Manuals**

You can print the software manuals with the graphics and text inline. PDF format files of each of the software manuals are provided on the 3.1i Software Documentation CD-ROM and at http://support.xilinx.com/support/sw\_manuals/3\_1i/index.htm.

#### **Printing PDF Files**

To access and print using the PDF files, use the following steps.

1. Verify that you have Adobe Acrobat Reader (version 3.0 or above) installed on your network or local area.

You can install Acrobat from the Alliance 3.1i Implementation tools software CD-ROM by selecting the Core Generator option, or from the Documentation CD.

- 2. Start Acrobat Reader

- UNIX users

Run the following command to start this tool.

```

/usr/bin/path_to_directory/acrobat

```

*Path\_to\_directory* is the directory where your Acrobat program files are located.

PC users

$Select Start \rightarrow Programs \rightarrow Acrobat Reader$

- Insert the Xilinx 3.1i Software Documentation CD-ROM into your drive.

- 4. Access your CD-ROM directory.

- UNIX users

Enter the following command.

/usr/bin/path\_to\_CD-ROM\_directory

Path\_to\_CD-ROM\_directory is your mounted CD-ROM drive.

Enter the **ls** command to view the contents of the CD-ROM directory.

PC users

Select  $\mathtt{Start} \to \mathtt{Programs} \to \mathtt{Windows}$  Explorer and select your CD-ROM drive to display the contents of the CD-ROM.

- 5. Open the Print directory or folder from the CD-ROM contents. This directory contains the PDF files.

- 6. Select a book and open it in Acrobat.

The following table lists the book titles and corresponding PDF file names.

Table 1-4 List of Alliance 3.1i Software Manuals

| Manual Title                       | PDF File Name |  |

|------------------------------------|---------------|--|

| Xilinx/Concept-HDL Interface Guide | docchdl.pdf   |  |

| Constraints Editor Guide           | cst_edit.pdf  |  |

| CORE Generator Guide               | coregen.pdf   |  |

| CPLD Schematic Design Guide        | sdg_alli.pdf  |  |

| CPLD Synthesis Design Guide        | syn_cpld.pdf  |  |

| Design Manager/Flow Engine Guide   | dmfe.pdf      |  |

| Development System Reference Guide | dev_ref.pdf   |  |

| FPGA Editor Guide                  | fpedit.pdf    |  |

| Floorplanner Guide                 | fplan.pdf     |  |

| Hardware Debugger Guide            | hdebug.pdf    |  |

| Hardware User Guide                | huguide.pdf   |  |

Table 1-4 List of Alliance 3.1i Software Manuals

| Manual Title                           | PDF File Name |

|----------------------------------------|---------------|

| JTAG Programmer Guide                  | jtag.pdf      |

| Libraries Guide                        | libguide.pdf  |

| LogiBLOX Guide                         | lblox.pdf     |

| Mentor Graphics Interface Guide        | mentor.pdf    |

| PROM File Formatter Guide              | prom_fmt.pdf  |

| Alliance Series 3.1i Quick Start Guide | docaqsg.pdf   |

| Synthesis and Simulation Design Guide  | gensim.pdf    |

| Xilinx/Synopsys Interface Guide        | xsi_int.pdf   |

| Timing Analyzer Guide                  | timing.pdf    |

| Viewlogic Interface Guide              | vlifg.pdf     |

Print the book using the File → Print command from the Adobe Acrobat reader window.

#### **Printing from the Online Document Viewer**

You can print individual pages of the software manuals directly from your internet browser window. For example, if you are using a Netscape browser, use the File → Print Frame menu option in the browser window. (Make sure you clicked in the right-hand book view frame to select it for printing.)

Xilinx recommends that you use the online books for quick information access and searching, and the PDF files for best print quality. Many of the graphics in the Web-based manuals are not inline and will not print automatically. They are also sized for optimal online viewing and may not fit on a printed page.

If you do not have access to your Documentation CD-ROM, you can also access the software manuals in PDF format on the Web. You can FTP each manual to your local area.

**Note** This process is slower than accessing the PDF files directly from your CD-ROM.

### **EDA and Third Party Interface Support**

The Alliance 3.1i software supports various third party interfaces. For the most current information on the latest vendor version support in the Alliance EDA partner program, refer to  $\verb|http://$

www.xilinx.com/programs/alliance/alligen.htm.

Software manuals for EDA interface users are provided on your software documentation CD-ROM. You can also access the manuals on the Web, from support.xilinx.com.

### Software Installation and Licensing

**Note** Complete software installation instructions are located in the *Alliance 3.1i Release Notes and Installation Guide.*

You must register your software before you can complete the installation. Before you register, make sure you have the serial number from your software package available. You can register by telephone, fax, e-mail, or online.

# **Support and Services**

This section provides information for contacting your technical support and customer service representatives.

### **Technical Support**

If you experience problems with your software installation or operation, you can look for solutions and answers at http://support.xilinx.com. This support page contains thousands of online technical solutions and product information for Xilinx software and devices. The Xilinx Answers Database is updated daily with the latest patches, problem resolutions, application notes, and data sheets. You can receive immediate answers 24 hours a day.

If you cannot find your answers at http://support.xilinx.com, open a support case on the Web to access Xilinx application engineers worldwide. You can also use telephone hotlines, e-mail, or fax to open a support case.

If you need additional support, contact the Xilinx Technical Support hotline by phone or fax.

**Note** When e-mailing or faxing inquiries, provide your complete name, company name, and phone number. Also, provide a complete problem description including your design entry software and design stage. In North America, call 1-800-255-7778 if you cannot open a support case on the Web.

| Location       | Telephone         | Electronic Mail     | Facsimile (Fax)   |

|----------------|-------------------|---------------------|-------------------|

| United Kingdom | 44-870-7350-610   | ukhelp@xilinx.com   | 44-870-7350-620   |

| France         | 33-1-3463-0100    | frhelp@xilinx.com   | 33-1-3463-0959    |

| Germany        | 49-89-93088-130   | dlhelp@xilinx.com   | 49-89-93088-188   |

| Japan          | local distributor | jhotline@xilinx.com | local distributor |

| Korea          | local distributor | korea@xilinx.com    | local distributor |

| Hong Kong      | local distributor | hongkong@xilinx.com | local distributor |

| Taiwan         | local distributor | taiwan@xilinx.com   | local distributor |

#### **Customer Service**

Refer to the Xilinx Web site at http://support.xilinx.com/support/custserv.htm for customer service information. The customer service toll-free number for North America is 1-800-624-4782.

# **Architecture Support**

The software supports the following architecture families in this release. Refer to the Programmable Logic Data Book for more information on these devices. The online version of the Data Book is at <a href="http://www.xilinx.com/partinfo/databook.htm">http://www.xilinx.com/partinfo/databook.htm</a>. For updated information regarding speed grades and package support, search the Xilinx Answers Database and the latest Application Notes. You can search the technical documentation at <a href="http://www.xilinx.com/support/searchtd.htm">http://www.xilinx.com/support/searchtd.htm</a>.

- Spartan<sup>TM</sup>/XL/-II

- Virtex<sup>TM</sup>/-E/-II

- XC9500™/XL/XV

- XC4000<sup>TM</sup>E/L/EX/XL/XV/XLA

- XC3000™A/L

- XC3100™A/L

- XC5200™

# Chapter 2

# **Implementation Tools Tutorial**

This chapter provides a step-by-step tutorial that covers many functions of the Alliance 3.1i implementation tools. This tutorial is a good way to learn how the Alliance design flow works with basic designs. For detailed information on using the Xilinx Design Manager, see the Design Manager/Flow Engine Guide.

Note An updated version of this tutorial will be available after May 21, 2000 from the Xilinx Support web site as well as on the AppLINX CD. The web site location is http://support.xilinx.com/support/techsup/tutorials/index.htm. Contact your local sales representative to obtain a copy of the AppLINX CD.

For additional information on the Xilinx tools, see http://www.support.xilinx.com/support/training/training.htm and http://www.support.xilinx.com/support/techsup/journals/index.htm.

#### This chapter contains the following sections.

- "Installing the Tutorial Files"

- "Step 1: Creating an Implementation Project"

- "Step 2: Specifying Options"

- "Step 3: Translating the Design"

- "Step 4: Using the Constraints Editor"

- "Step 5: Mapping the Design"

- "Step 6: Using Timing Analysis to Evaluate Block Delays After Mapping"

- "Step 7: Placing and Routing the Design"

- "Step 8: Evaluating Post Layout Timing"

- "Step 9: Creating Timing Simulation Data"

- "Step 10: Creating Configuration Data"

- "Step 11: Using the PROM File Formatter"

# **Installing the Tutorial Files**

This tutorial demonstrates the Alliance design implementation tools flow. The front end design has already been compiled for you in an EDA interface tool and is described by an EDIF Netlist File (EDF). For a listing of EDA Interface tutorials, see the Xilinx Support area at http://support.xilinx.com/support/techsup/tuto-rials/index.htm.

This tutorial passes an input netlist from the front end tool to the back-end Alliance 3.1i design implementation tools, and incorporates placement constraints through a User Constraints File (UCF). Timing constraints are added with the Constraints Editor tool.

The tutorial design is named stopwatch and is designed to perform like a track coach's stopwatch. There are two inputs to the system, RESET and SRTSTP, and the configuration clock on the device is used as a ten Hz clock signal. Three seven bit outputs are generated by this system for output to three seven segment LED displays.

Before proceeding to Step 1 in the tutorial, create a working directory with the tutorial files as follows.

- 1. Create an empty working directory named Watch.

- Copy the following files from the \$XILINX/tutorial/qstart/ directory or from http://support.xilinx.com/support/ techsup/tutorials/ to your newly created working directory.

**Note** In order for the \$XILINX/tutorial/qstart directory to be present in your root Xilinx directory, you must first install the Userware Tutorial files from the Alliance Series 3.1i design implementation tools CD-ROM.

| File Name     | Description                         |

|---------------|-------------------------------------|

| stopwatch.edn | Input netlist file (EDIF)           |

| tenths.edn    | Coregen Counter netlist file (EDIF) |

| stopwatch.ucf | User constraints file               |

### **Step 1: Creating an Implementation Project**

The design implementation tools are organized under a single program called the Design Manager. The Design Manager helps you manage the design flow process by keeping track of design versions and the implementation revisions within each version. The Design Manager also provides access to the entire suite of Xilinx implementation tools needed to complete a design.

While the Design Manager manages your design, the Flow Engine implements it. The Flow Engine is closely integrated with the Design Manager and shares many of the same menus and dialog boxes.

Use the following steps to create an implementation project.

1. On a workstation, enter the following to start the Design Manager.

xilinx &

On a PC, select  $\mathtt{Start} \to \mathtt{Programs} \to \mathtt{Xilinx} \to \mathtt{Design}$ Manager to start the Design Manager.

When you open the Design Manager for the first time, you must create a new project for your design. A project includes all design versions, implementation revisions, reports, and any data created while you work with a design.

The Design Manager graphically displays information about these items in the project view. When you create a new project, you specify a design to open and a directory for the project. You can create as many projects as you want, but you can only work with one at a time.

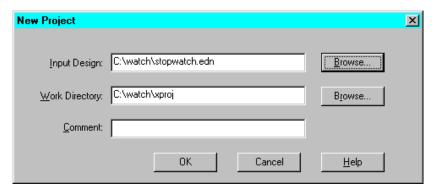

To create a new implementation project for the tutorial design, select File → New Project from the Design Manager menu. The New Project dialog box appears.

Figure 2-1 New Project Dialog Box

This dialog box contains the following fields.

Table 2-1 New Project Dialog Box Fields

| Field          | Description                                                                       |

|----------------|-----------------------------------------------------------------------------------|

| Input Design   | Top level netlist file containing the design definition                           |

| Work Directory | Directory used to store the implementation data created as the design is compiled |

| Comment        | Use this field to enter any optional notation for the design                      |

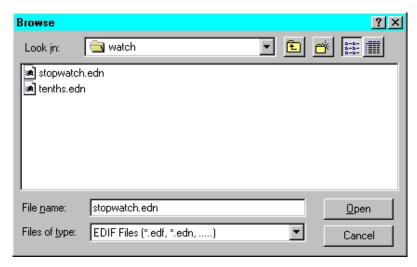

3. To specify your input design, click **Browse** next to the Input Design field to display the Browse dialog box.

Figure 2-2 Browse Dialog Box

- 4. Select the appropriate file type from the pull-down list in the Files of Type field. For the tutorial design, EDIF is selected.

- 5. Select the stopwatch.edn file. The file name appears in the File Name field. Click Open.

The Browse dialog box closes and the New Project dialog box is updated to include the specified input netlist. By default, the Work Directory field is set to the directory containing the input design. If preferred, you can set this to another directory. Because the files were previously copied to the Watch directory, this directory is used for the implementation project and resulting output files.

6. In the Comment field, enter the following.

-tutorial

Both the new version and new revision will be created

Version Name: ver1

Version Comment:

Part: XCV50-6-BG256

Select...

Revision Name: rev1

Revision Comment:

Copy Persistent Data

Constraints File: None

7. Click OK to close the New Project dialog box. The New Version dialog box appears.

Figure 2-3 New Version Dialog Box

0K

Guide File(s): None

When initially creating a project, the New Version dialog box automatically appears to allow you to enter the information necessary to define the new design version. Also, if your input netlist changes as a result of changes made in the front-end tool, you are prompted by the Design Manager to generate a new design version.

Cancel

<u>H</u>elp

Once a design version is created, you can try different implementation strategies on your design. The data associated with each of these implementation strategies is called an implementation revision. Because a new implementation revision is automatically created when you create a new version, the Version Name and Revision Name fields are already defined in the New Version dialog box.

The Version Name field shows ver1 as the default version, and the Revision Name field shows rev1 as the default revision. Comments on the options and strategies can be entered in the Version and Revision Comment fields.

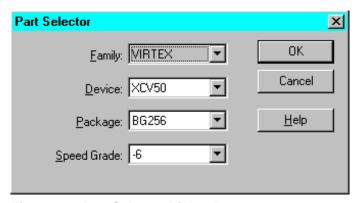

8. The Part field automatically contains a part number if you specified the target device in your design entry tool. For the tutorial design, this field is empty and must be defined. Click Select to display the Part Selector dialog box.

Figure 2-4 Part Selector Dialog Box

- 9. Use the pull-down lists for the fields in the Part Selector dialog box to enter the Family, Device, Package, and Speed Grade for the design. This design targets a Virtex XCV50-6-BG256. Click OK. The part number appears in the Part field in the New Version dialog box.

- 10. The Copy Persistent Data area of the dialog box allows you to copy constraint, guide, or floorplan data to the new revision that is about to be created. You can copy data from a custom file, or select None if you do not want to copy data. For this tutorial, None is selected for all three fields.

**Note** By default, the Design Manager copies floorplan and constraints file data from the "last" revision. The "last" revision is the final revision in the Design Manager project view. When initially creating a project, the Design Manager copies any existing constraints and floorplan file data from the project directory to the revision directory.

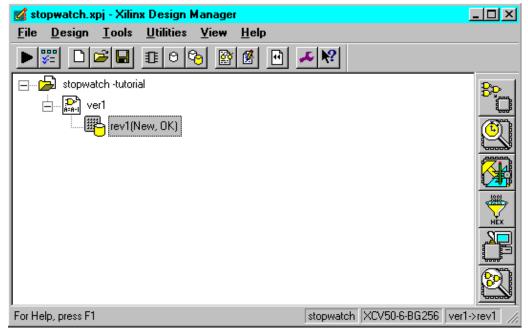

11. Click **OK** in the New Version dialog box.

The Design Manager loads the design and displays a new design version and implementation revision in the project view as shown in the following figure.

Figure 2-5 Stopwatch Project in Design Manager

#### **Design Manager Status Bar**

The status bar is located at the bottom of the Design Manager window. The status bar lists the current project, target device, and currently selected version/revision pair.

Figure 2-6 Design Manager Status Bar

#### **Design Manager Toolbox**

The toolbox, located on the right side of the Design Manager window, becomes active when a revision is selected. Icons in the toolbox (shown in the following figure) represent the Flow Engine, Timing Analyzer, Floorplanner, PROM File Formatter, Hardware Debugger, FPGA Editor, and JTAG Programmer tools.

**Note** The toolbox has drag and drop capability.

Figure 2-7 Design Manager Toolbox

# **Step 2: Specifying Options**

An implementation revision contains data files and reports that are created based on a specific set of implementation strategies. Implementation strategies are defined by specifying a set of options. You can specify options that control how the Flow Engine implements a design, creates timing simulation data, creates netlist files, generates reports, and creates configuration data. The options available depend on the target device family.

You can create as many implementation revisions as you want for a design version. For example, if you want to try various implementation strategies on a netlist, several revisions can be created for a single design version. However, by default the Design Manager recompiles within the current revision.

In the Design Manager, notice how the project view displays rev1 under the initial version of the stopwatch project. The status of the revision is noted as (New, OK). *New* refers to the state of the design and is updated throughout the tutorial as the different compilation stages are completed. *OK* is the status of the current state and indicates there are no errors in the design processing.

Use the following steps to specify options for the tutorial design.

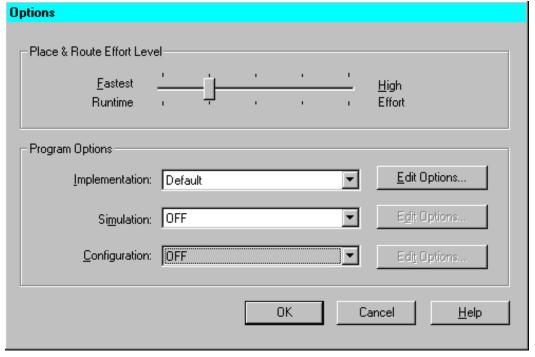

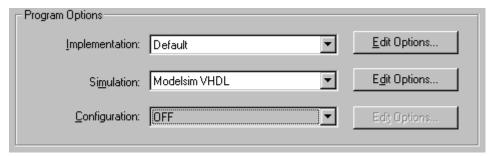

1. Select  $\mathtt{Design} \to \mathtt{Options}$  to open the Options dialog box as shown in the following figure.

Figure 2-8 Options Dialog Box

This dialog box allows you to set options used in the implementation, simulation, and configuration flow. Changes made in this dialog box apply to the selected implementation revision. The dialog box above appears if you are targeting an FPGA. A slightly different Options dialog box is displayed if you are targeting a CPLD.

For more information on the fields in this dialog box, select Help.

2. Select **Edit Options** next to Implementation in the Program Options area of the dialog box.

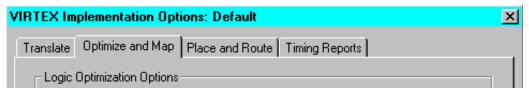

The following figure shows the top portion of the dialog box that appears. The implementation options control how the software maps, places, routes, and optimizes a design.

Figure 2-9 Top Portion of Virtex Implementation Options Dialog Box

- 3. Select the Timing Reports tab.

- 4. Select the Produce Logic Level Timing Report option. The Produce a Post Layout Timing Report option should already be selected by default. For both reports, select Report Paths in Timing Constraints.

- Timing reports are useful for evaluating design performance. These reports are analyzed later in this tutorial.

- 5. Click **OK** to save the Implementation options and return to the Options dialog box.

- Select OFF from the Configuration Program Options pull-down list to disable bitstream generation for the design. This option is described later in this tutorial (after the evaluation of design performance is finished).

- 7. Click **OK** to exit the Options dialog box.

As previously mentioned, an implementation revision is created based on a specific set of implementation strategies. In addition to the program options that were just set, an implementation strategy is defined by the constraints applied to the design.

In this tutorial, the User Constraints File (UCF) is named stopwatch.ucf and is located in your design directory. By default, the Design Manager copies your constraints information into the new revision. You can use a text editor to open the stopwatch.ucf file in the newly created rev1 directory and view the location constraints that are specified for the design.

The UCF provides a mechanism for constraining a logical design without returning to the design entry tools. However, it requires an understanding of the exact syntax needed to define constraints. Alternatively, the Xilinx Constraints Editor is a graphical tool that allows you to enter timing and pin location constraints. The Constraints Editor is used in this tutorial to view the current constraints specified in the stopwatch.ucf file, and to specify additional timing constraints.

To continue with the tutorial, select  $\mathtt{Utilities} \to \mathtt{Constraints}$  Editor in the Design Manager.

You are prompted to run the Translate step before launching the Constraints Editor. The next step in the tutorial provides information on translating your design.

### Step 3: Translating the Design

The Design Manager manages the files created during the implementation process while the Flow Engine controls the implementation process. The programs run by the Flow Engine use the settings specified by you in the Options dialog box. The Flow Engine gives you complete control over how a design is processed. Typically, you should set all of your options first, and then run through the entire flow by selecting the Implement command from the Design menu.

In this tutorial, you are attempting to further define the design by setting constraints after having defined options. To run the Constraints Editor, you must first run the Translate step.

Select Yes in the message dialog box to continue with the flow.

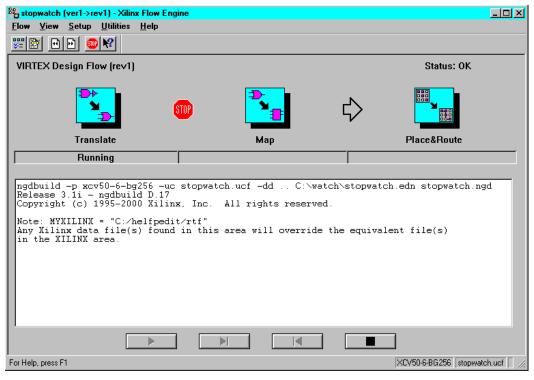

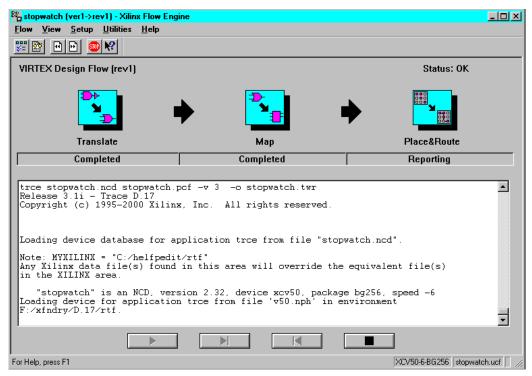

The Flow Engine is invoked for the first time. The steps in the design flow are graphically represented in the upper half of the Flow Engine window, and the status of each stage is also shown. Refer to the following figure.

Figure 2-10 Translating Design

Notice the STOP sign placed between the Translate and MAP steps. This breakpoint has been automatically set to instruct the Flow Engine to stop after the Translate step is complete.

During translation, the NGDBuild program is launched, and performs the following functions.

- Converts input design netlists and writes results to a single merged NGD netlist. The merged netlist describes the logic in the design as well as any location and timing constraints.

- Performs timing specification and logical design rule checks

- · Adds the UCF to the merged netlist

Once complete, the Flow Engine stops and the Constraints Editor is launched.

# **Step 4: Using the Constraints Editor**

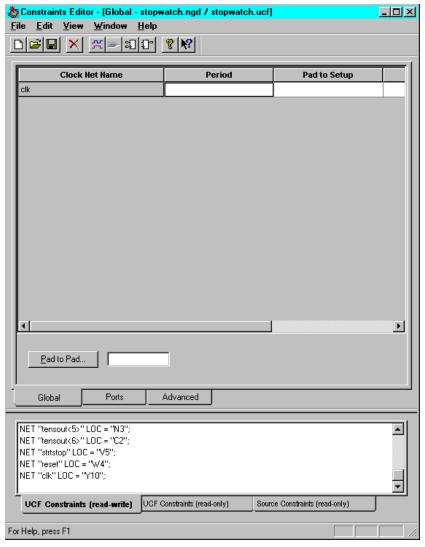

The Constraints Editor (see following figure) allows you to edit constraints previously defined (through a UCF), and to add new constraints to your design.

Figure 2-11 Constraints Editor Global Tab

Input files to the Constraints Editor include the following.

NGD (Native Generic Database) file

This file is input to the Map program, which then outputs the physical design database, an NCD (Native Circuit Description) file.

Corresponding UCF

By default, when the NGD file is opened, an existing UCF file with the same base name as the NGD file is used. Alternatively, you can specify the name of the UCF file.

Upon successful completion, the Constraints Editor writes out a valid UCF file. NGDBuild uses the UCF file, along with design source netlists to produce a newer NGD file that incorporates the changes made. The NGD is then read by the MAP program (the next step in the design flow). In this tutorial, the stopwatch.ngd file and stopwatch.ucf file are automatically read into the Constraints Editor.

The Global tab appears in the foreground of the Constraints Editor window. This window automatically displays all of the clock nets in a design, and allows you to define the associated period, pad to setup, and/or clock to pad values.

Perform the following steps in the Constraints Editor.

- Select the Period cell in the row associated with the clk clock net. Double-click the left mouse button to open the Clock Period dialog box.

- In the Clock Signal Definition area of the dialog box, select the **Specific Time** option to define an explicit period for the clock.

- 2. Enter 18.5 in the Time field. Verify that ns is selected from the Units pull-down list. Click **OK**.

- The period cell is updated with the newly defined global clock period constraint (with a default 50% duty cycle).

- **Note** In this tutorial, the Clock Period dialog box is used to specify constraints values. Alternatively, you can click once on a cell and directly enter constraints.

- 3. Select the Ports tab from the Constraints Editor main window.

| Port Name  | Port Direction | Location | Pad to Setup | Clock to Pad |

|------------|----------------|----------|--------------|--------------|

| clk        | INPUT          | Y10      | N/A          | N/A          |

| onesout<0> | OUTPUT         | M2       | N/A          |              |

| onesout<1> | OUTPUT         | P1       | N/A          |              |

| onesout<2> | OUTPUT         | мз       | N/A          |              |

| onesout<3> | OUTPUT         | N2       | N/A          |              |

| onesout<4> | OUTPUT         | M1       | N/A          |              |

| onesout<5> | OUTPUT         | R3       | N/A          |              |

| onesout<6> | OUTPUT         | N1       | N/A          |              |

| reset      | INPUT          | VV4      |              | N/A          |

Figure 2-12 Constraints Editor Ports Tab

The left hand side displays a listing of the current user-defined ports. Notice that certain cells in the Location column contain device pins locking down ports to actual pins on the target device. This information is obtained by the Constraints Editor from the stopwatch.ucf file.

4. Enter the following pin locations by selecting the Location text box associated with each of the following signals.

| Port Name  | Location |

|------------|----------|

| onesout<0> | M2       |

| onesout<1> | P1       |

| onesout<2> | M3       |

| onesout<3> | N2       |

| onesout<4> | M1       |

| onesout<5> | R3       |

| onesout<6> | N1       |

5. Select File  $\rightarrow$  Save.

The changes made in the Constraints Editor are now saved to the stopwatch.ucf file in your current revision directory.

- 6. You are prompted to repeat the Translate step. Click OK.

- 7. Select File  $\rightarrow$  Exit

#### Caution

Read the following procedure before you start to implement the design.

#### How to Stop the Design Processing Flow

Before continuing with the next step in the tutorial, review the procedure described in this section for stopping the processing of the design after the MAP step. Because the steps for the tutorial design often finish quickly, you should be familiar with this procedure before you start the Flow Engine.

Setting a break point to stop the design processing is useful for evaluating design performance before going on to the next step in the design flow. You can set a break point at any time during the processing of a design by the Flow Engine. For example, setting a break point after the Translate step is useful when you want to perform a functional simulation of a design and copy the resulting design.ngd file to your working directory. After copying the design.ngd file, you can run the appropriate NGD2XXX program on the file to create functional simulation data. For more information on the NGD2XXX programs, see the appropriate chapter in the *Develop*ment System Reference Guide.

- In this tutorial, you want to stop processing the design after the MAP step. To do this, you must set a break point to stop the Flow Engine. To stop after the MAP step from within the Flow Engine, click the stop sign toolbar icon while MAP is running.

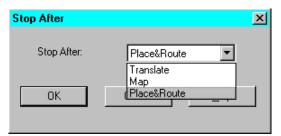

- The Stop After dialog box is displayed. The pull-down list box displays the break point appropriate for the current state of the design.

Figure 2-13 Stop After Dialog Box

- 3. Select Map in the list box and click OK.

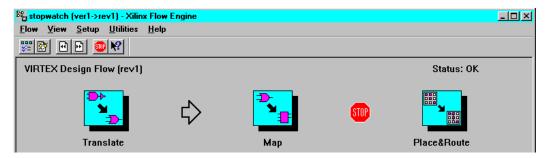

- 4. The stop sign is added to the design flow between the Map and Place and Route steps as shown in the following figure.

**Note** The status bar at the bottom of the Flow Engine window is updated with the specified user constraints file (stopwatch.ucf).

Figure 2-14 Mapping Design

### Step 5: Mapping the Design

Now that all implementation strategies have been defined (options and constraints), the next step is implementing the design.

- 1. Select Design  $\rightarrow$  Implement from the Design Manager.

- 2. The Flow Engine automatically detects that changes were made to your constraints file, and displays a message box indicating that the Translate step should be run again. Select **YES**.

- 3. The Flow Engine is invoked. Perform the procedure previously described in the "How to Stop the Design Processing Flow" section to stop the processing of the design after the Map step.

At this point, the input netlist is translated again, merged into a single design file, and mapped to CLBs and IOBs.

The Map program performs the following functions.

- Allocates CLB and IOB resources for all basic logic elements in the design.

- Processes all location and timing constraints, performs target device optimizations, and runs a design rule check on the resulting mapped netlist.

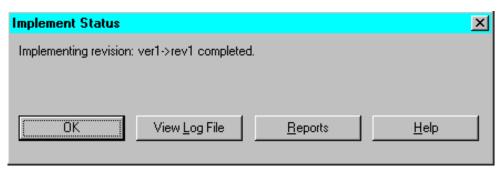

After the MAP step is done, the Flow Engine closes and the Implement Status dialog box appears.

Figure 2-15 Implement Status Dialog Box

Follow these steps to view the generated reports.

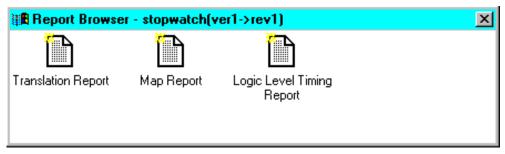

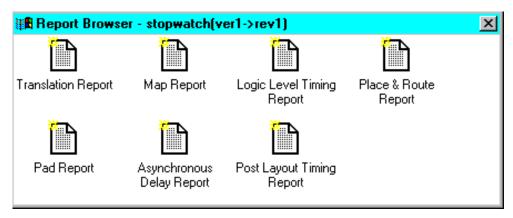

Select Reports to invoke the Report Browser window. The Translation Report appears as the first report generated. The Map Report and Logic Level Timing Report files are created by the Map step. New reports that have not been read are denoted with a gold star in the upper left corner of the file icon.

Figure 2-16 Report Browser after Running Map

2. Double-click on a report to review its output. The following table lists the types of reports available.

**Table 2-2 Report Browser Reports**

| Report                       | Description                                                                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Translation Report           | Includes warning and error messages from the translation process.                                                                                                                                                        |

| Map Report                   | Includes information on how the target device resources are allocated, references to trimmed logic, and device utilization. For detailed information on the Map report, refer to the Development System Reference Guide. |

| Logic Level Timing<br>Report | Provides a summary analysis of your timing constraints based on block delays and estimates of route delays. This report is produced after Map and prior to PAR (Place And Route).                                        |

3. Select OK to close the Implement Status dialog. Keep the Report Browser open for now. Some of these reports are evaluated in more detail later in the tutorial.

Notice that the Design Manager project view displays the status of the revision as (Mapped, OK). "Mapped" refers to the state of the design and is updated throughout the tutorial as the different compilation stages are completed. "OK" refers to the status of the current state and indicates there are no errors in the design processing.

The design has now been mapped to the target architecture. The next step involves checking the design paths for block delays.

# **Step 6: Using Timing Analysis to Evaluate Block Delays After Mapping**

After the design is mapped, you can use the Logic Level Timing Report to evaluate the logical paths in the design. Because the design is not placed and routed yet, actual routing delay information is not yet available. The timing report describes the logical block delays and estimated routing delays. The net delays that are provided are based

on an optimal distance between blocks (also referred to as *unplaced floors*).

#### **Estimating Timing Goals With 50/50 Rule**

You can get a preliminary idea of how realistic your timing goals are by evaluating a design after the Map step. A rough guideline (known as the 50/50 rule) specifies that the block delays in any single path make up approximately 50% of the total path delay after the design is routed. For example, a path with 10 ns of block delay should meet a 20 ns timing constraint after it is placed and routed. If your design is extremely dense, or if you are using an architecture with fewer routing resources (for example, a 4025E device versus a 4028XL), your net delays can be more than 50% of the total path delay.

#### **Report Paths In Timing Constraints Option**

Because timing constraints were defined for this tutorial design, the Report Paths in Timing Constraints option was selected. This option forces the Logic Level Timing Report to provide a period and path analysis on the constraints specified. Double-click on this report in the Report Browser. In the report, the period timing constraint is listed on top, as is the minimum period obtained by the tools after mapping. Because the report is limited to one path per timing constraint, there is a breakdown of a single path that contains 4 levels of logic. Notice the percentage of block (logic) delay versus routing delay for this calculation. The unplaced floors listed are estimates (indicated by the letter "e" next to the net delay) based on optimal placement of blocks.

If you do not generate a Logical Level Timing Report, the Place and Route (PAR) program still processes a design based on the relationship between the block delays, floors, and timing specifications for the design. For example, if a PERIOD constraint of 8 ns is specified for a path, and there are block delays of 7 ns and unplaced floor net delays of 3 ns, PAR stops and generates an error message. In this example, PAR fails because it determines that the total delay (10 ns) is greater than the constraint placed on the design (8 ns).

Review the Logic Level Timing Report to determine any timing violations that occurred prior to running PAR.

# **Step 7: Placing and Routing the Design**

After the mapped design is evaluated to verify that block delays are reasonable given the design specifications, the design can be placed and routed. The Flow Engine can perform the following place and route algorithms.

- Timing Driven run PAR with timing constraints specified from within the input netlist or from a constraints file

- Non-Timing Driven run PAR and ignore all timing constraints

In this tutorial, timing driven placement and timing driven routing are automatically performed by PAR because timing constraints are specified for the design.

Close any open reports and the Report Browser.

To place and route the design, perform the following procedure.

1. In the Design Manager window, select  $\mathtt{Design} \to \mathtt{Implement}$  to run the implementation flow.

The Flow Engine is launched again. The Status:OK message in the upper right corner indicates that no errors are generated by PAR at this point.

Figure 2-17 Placing and Routing Design

2. After the Flow Engine closes, select Reports in the Implement Status dialog box to display the Report Browser.

Four new reports are created in the Report Browser: the Place and Route Report, the Pad Report, the Asynchronous Delay Report, and the Post Layout Timing Report.

Review the reports generated to make sure the place and route process finished as expected.

Figure 2-18 Reports Available After Place and Route

Table 2-3 Description of Reports Available After Place and

Route

| Report                       | Description                                                                                                                                              |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Place & Route Report         | Provides a device utilization and delay summary. Use this report to verify that the design successfully routed and that all timing constraints were met. |

| Pad Report                   | Contains a report of the location of the device pins. Use this report to verify that pins locked down were placed in the correct location.               |

| Asynchronous Delay<br>Report | Lists all nets in the design and the delays of all loads on the net.                                                                                     |

| Post Layout Timing<br>Report | Incorporates both the logic and routing delays to generate an evaluation of the design's timing constraints, clock frequencies, and path delays.         |

**Note** In the Design Manager window, the status of the current version/revision is now (Routed, OK).

# **Step 8: Evaluating Post Layout Timing**

After the design is placed and routed, a Post Layout Timing Report is generated by default to verify that the design meets your specified

timing goals. This report evaluates the logical block delays and the routing delays. The net delays are now reported as actual routing delays after the place and route process (indicated by the letter "R" next to the net delay).

Double-click on the Post Layout Timing Report to open it. Following is a summary of this report.

- The minimum period value increased due to the actual routing delays.

- After the Map step, logic delay contributed to about 80% of the minimum period attained. The post layout report indicates that the logical delay value decreased somewhat. The total unplaced floors estimate changed as well. Routing delay after PAR now equals about 31% of the period; a true report of net delays after the place and route step.

- The post layout result does not necessarily follow the 50/50 rule previously described because the worst case path includes primarily component delays. After the design was mapped, block delays constituted about 80% of the period. After place and route, the majority of the worst case path is still made up of logic delay. Since total routing delay makes up only a small percentage of the total path delay, spread out across three nets, expecting this to be reduced any further is unrealistic. In general, you can reduce excessive block delays and improve design performance by decreasing the number of logic levels in the design.

# **Step 9: Creating Timing Simulation Data**

After your design is placed and routed and the timing is statically verified, the next step is to create timing simulation data. To create timing simulation data, perform the following steps in the Design Manager.

- 1. Select  $\mathtt{Design} \to \mathtt{Options}$  to open the Options dialog box.

- 2. Select the simulator that corresponds to your design entry tool from the Simulation pull-down list in the Program Options section of the dialog box.

Figure 2-19 Options Dialog Box for Simulation

- 3. Click **OK** to close the Options dialog box.

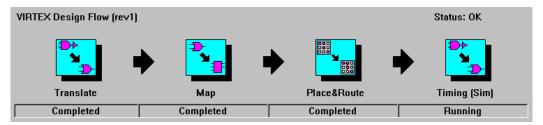

- 4. Select Design  $\rightarrow$  Implement.

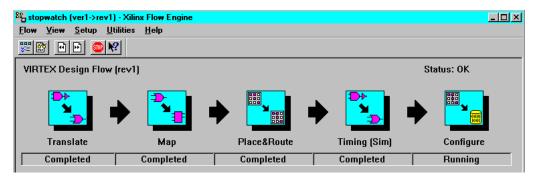

In the Flow Engine, a new stage appears directly after Place & Route called Timing(Sim). This new stage produces timing simulation data. This stage did not appear originally because a specific simulator was not selected in the initial pass. By default, this option is set to OFF. For your designs, you can select all options at the beginning of the design processing, or you can set them later.

Figure 2-20 Flow Engine with Timing Simulation

During the Timing(Sim) step, the Flow Engine runs the NGDAnno program to create a back-annotated NGD file. The NGD file is then used as input to one of the NGD2XXX programs to produce the preferred simulation file format. By default, the files created are named *time\_sim*. To make it easy to find the output files for your third-party simulation environment, the files are automatically copied to your working directory.

#### **Step 10: Creating Configuration Data**

To create a bitstream for the target device, follow these steps.

- 1. Select  $\texttt{Design} \rightarrow \texttt{Options}$  to open the Options dialog box.

- 2. Select **Default** from the pull-down list for Configuration Program Options.

- Click the Edit Options button corresponding to Configuration.

The Virtex Configuration Options dialog box appears. The configuration templates set options that define the initial configuration parameters, start-up sequence, readback capabilities, and other advanced features.

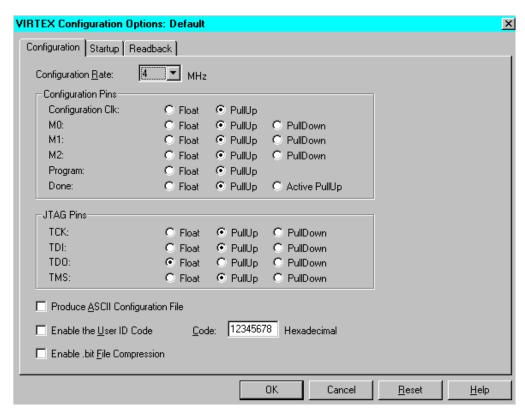

Figure 2-21 Virtex Configuration Options Tab

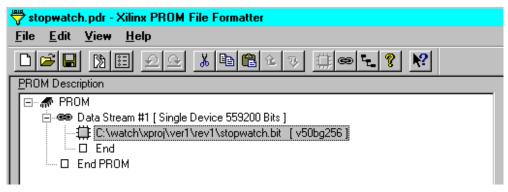

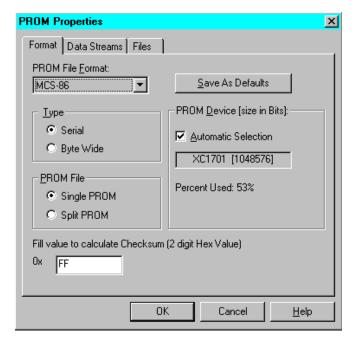

- 4. In the Configuration tab, verify that PullUp is selected for the Done pin.